#### Details

**X** F

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                           |

|---------------------------------|-----------------------------------------------------------|

| Product Status                  | Obsolete                                                  |

| Core Processor                  | 68030                                                     |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                            |

| Speed                           | 25MHz                                                     |

| Co-Processors/DSP               | -                                                         |

| RAM Controllers                 | -                                                         |

| Graphics Acceleration           | No                                                        |

| Display & Interface Controllers | -                                                         |

| Ethernet                        | -                                                         |

| SATA                            | -                                                         |

| USB                             | -                                                         |

| Voltage - I/O                   | 5.0V                                                      |

| Operating Temperature           | 0°C ~ 70°C (TA)                                           |

| Security Features               | -                                                         |

| Package / Case                  | 132-BCQFP                                                 |

| Supplier Device Package         | 132-CQFP (24x24)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mc68030fe25c |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **TABLE OF CONTENTS (Continued)**

| Paragrap<br>Number                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page<br>Number                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Number<br>11.6<br>11.6.1<br>11.6.2<br>11.6.3<br>11.6.4<br>11.6.5<br>11.6.6<br>11.6.7<br>11.6.8<br>11.6.9<br>11.6.10<br>11.6.10<br>11.6.11<br>11.6.12<br>11.6.13<br>11.6.15<br>11.6.16<br>11.6.17<br>11.6.18 | Title         Instruction Timing Tables         Fetch Effective Address (fea)         Fetch Immediate Effective Address (fiea)         Calculate Effective Address (cea)         Calculate Immediate Effective Address Mode (ciea)         Jump Effective Address         MOVE Instruction         Special-Purpose MOVE Instructions         Arithmetical/Logical Instructions         Immediate Arithmetical/Logical Instructions         Binary-Coded Decimal and Extended Instructions         Single Operand Instructions         Bit Manipulation Instructions         Bit Field Manipulation Instructions         Conditional Branch Instructions         Exception-Related Instructions and Operations         Save and Restore Operations | Number<br>                       |

| 11.7<br>11.7.1<br>11.7.2<br>11.8<br>11.9                                                                                                                                                                    | Address Translation Tree Search Timing<br>MMU Effective Address Calculation<br>MMU Instruction Timing<br>Interrupt Latency<br>Bus Arbitration Latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11-51<br>11-58<br>11-60<br>11-61 |

# Section 12

# **Applications Information**

| 12.1   | Adapting the MC68030 to MC68020 Designs         | 12-1  |

|--------|-------------------------------------------------|-------|

| 12.1.1 | Signal Routing                                  | 12-2  |

| 12.1.2 | Hardware Differences                            | 12-3  |

| 12.1.3 | Software Differences                            | 12-4  |

| 12.2   | Floating-Point Units                            | 12-5  |

| 12.3   | Byte Select Logic for the MC68030               | 12-9  |

| 12.4   | Memory Interface                                | 12-11 |

| 12.4.1 | Access Time Calculations                        | 12-14 |

| 12.4.2 | Burst Mode Cycles                               | 12-17 |

| 12.5   | Static RAM Memory Banks                         | 12-18 |

| 12.5.1 | A Two Clock Synchronous Memory Bank Using SRAMs | 12-18 |

# PREFACE

The *MC68030 User's Manual* describes the capabilities, operation, and programming of the MC68030 32-bit second-generation enhanced microprocessor. The manual consists of the following sections and appendix. For detailed information on the MC68030 instruction set refer to M68000PM/AD, *M68000 Family Programmer's Reference Manual.*

Section 1. Introduction

Section 2. Data Organization and Addressing Capabilities

Section 3. Instruction Set Summary

Section 4. Processing States

Section 5. Signal Description

Section 6. On-Chip Cache Memories

Section 7. Bus Operation

Section 8. Exception Processing

Section 9. Memory Management Unit

Section 10. Coprocessor Interface Description

Section 11. Instruction Execution Timing

Section 12. Applications Information

Section 13. Electrical Characteristics

Section 14. Ordering Information and Mechanical Data Appendix A. M68000 Family Summary

Index

#### NOTE

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

The audience of this manual includes systems designers, systems programmers, and applications programmers. Systems designers need some knowledge of all sections, with particular emphasis on Sections 1, 5, 6, 7, 13, 14, and Appendix A. Designers who implement a coprocessor for their system also need a thorough knowledge of Section 10. Systems programmers should

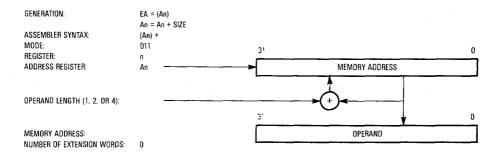

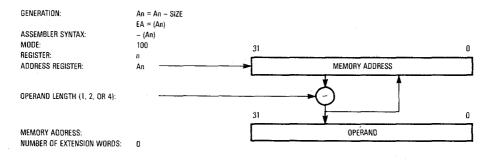

# 2.4.5 Address Register Indirect with Predecrement Mode

In the address register indirect with predecrement mode, the operand is in memory, and the address of the operand is in the address register specified by the register field. Before the operand address is used, it is decremented by one, two, or four depending on the operand size: byte, word, or long word. Coprocessors may support decrementing for any operand size up to 255 bytes. If the address register is the stack pointer and the operand size is byte, the address is decremented by two rather than one to keep the stack pointer aligned to a word boundary.

X = extend (X) bit in CCR

N = negative (N) bit in CCR

- Z = Zero (Z) bit in CCR

- V = overflow (V) bit in CCR

- C = carry (C) bit in CCR

- + = arithmetic addition or postincrement indicator

- = arithmetic subtraction or predecrement indicator

- $\times =$  arithmetic multiplication

- ÷ = arithmetic division or conjunction symbol

- $\sim$  = invert; operand is logically complemented

- $\Lambda = \text{logical AND}$

- V = logical OR

- $\oplus$  = logical exclusive OR

- Dc = data register, D7-D0 used during compare

- Du = data register, D7-D0 used during update

- Dr, Dq = data registers, remainder or quotient of divide

- Dh, DI = data registers, high- or low-order 32 bits of product

- MSW = most significant word

- LSW = least significant word

- MSB = most significant bit

- FC = function code

- $\{R/W\}$  = read or write indicator

- [An] = address extensions

## 3.2.1 Data Movement Instructions

The MOVE instructions with their associated addressing modes are the basic means of transferring and storing addresses and data. MOVE instructions transfer byte, word, and long-word operands from memory to memory, memory to register, register to memory, and register to register. Address movement instructions (MOVE or MOVEA) transfer word and long-word operands and ensure that only valid address manipulations are executed. In addition to the general MOVE instructions, there are several special data movement instructions: move multiple registers (MOVEM), move peripheral data (MOVEP), move quick (MOVEQ), exchange registers (EXG), load effective address (LEA), push effective address (PEA), link stack (LINK), and unlink stack (UNLK).

# 3.3.2 Conditional Tests

Table 3-13 lists the condition names, encodings, and tests for the conditional branch and set instructions. The test associated with each condition is a logical formula using the current states of the condition codes. If this formula evaluates to one, the condition is true. If the formula evaluates to zero, the condition is false. For example, the T condition is always true, and the EQ condition is true only if the Z bit condition code is currently true.

| Mnemonic | Condition        | Encoding | Test                                                                                |

|----------|------------------|----------|-------------------------------------------------------------------------------------|

| Т*       | True             | 0000     | 1                                                                                   |

| F*       | False            | 0001     | 0                                                                                   |

| н        | High             | 0010     | Ē•Ī                                                                                 |

| LS       | Low or Same      | 0011     | C+Z                                                                                 |

| CC(HS)   | Carry Clear      | 0100     | Ē                                                                                   |

| CS(LO)   | Carry Set        | 0101     | С                                                                                   |

| NE       | Not Equal        | 0110     | Z                                                                                   |

| EQ       | Equal            | 0111     | Z                                                                                   |

| VC       | Overflow Clear   | 1000     | ⊽                                                                                   |

| VS       | Overflow Set     | 1001     | V.                                                                                  |

| PL.      | Plus             | 1010     | Ň                                                                                   |

| MI       | Minus            | 1011     | N                                                                                   |

| GE       | Greater or Equal | 1100     | N•V+Ñ•V                                                                             |

| LT       | Less Than        | 1101     | $N \cdot \overline{V} + \overline{N} \cdot V$                                       |

| GŤ       | Greater Than     | 1110     | $N \cdot V \cdot \overline{Z} + \overline{N} \cdot \overline{V} \cdot \overline{Z}$ |

| LE       | Less or Equal    | 1111     | $Z + N \cdot \overline{V} + \overline{N} \cdot V$                                   |

## Table 3-13. Conditional Tests

• = Boolean AND

$\pm$  = Boolean OR

$\overline{N}$  = Boolean NOT N

\*Not available for the Bcc instruction.

**6.1.2.1 WRITE ALLOCATION.** The supervisor program can configure the data cache for either of two types of allocation for data cache entries that miss on write cycles. The state of the write allocation (WA) bit in the cache control register specifies either no write allocation or write allocation with partial validation of the data entries in the cache on writes.

When no write allocation is selected (WA = 0), write cycles that miss do not alter the data cache contents. In this mode, the processor does not replace entries in the cache during write operations. The cache is updated only during a write hit.

When write allocation is selected (WA = 1), the processor always updates the data cache on cachable write cycles, but only validates an updated entry that hits or an entry that is updated with long-word data that is long-word aligned. When a tag miss occurs on a write of long-word data that is long-word aligned, the corresponding tag is replaced, and only the long word being written is marked as valid. The other three entries in the cache line are invalidated when a tag miss occurs on a misaligned long-word write or on a byte or word write, the data is not written in the cache, the tag is unaltered, and the valid bit(s) are cleared. Thus, an aligned long-word data write or a write of data that is not long word may invalidate a previously valid entry or entries.

Write allocation eliminates stale data that may reside in the cache because of either of two unique situations: multiple mapping of two or more logical addresses to one physical address within the same task or allowing the same physical location to be accessed by both supervisor and user mode cycles. Stale data conditions can arise when operating in the no-write-allocation mode and all the following conditions are satisfied:

- Multiple mapping (object aliasing) is allowed by the operating system.

- A read cycle loads a value for an "aliased" physical address into the data cache.

- A write cycle occurs, referencing the same aliased physical object as above but using a different logical address, causing a cache miss and no update to the cache (has the same page offset).

- The physical object is then read using the first alias, which provides stale data from the cache.

Figure 6-10. Single Entry Mode Operation — Misaligned Long Word and 32-Bit DSACKx Port

If all bytes of a long word are cachable, CIIN must be negated for all bus cycles required to fill the entry. If any byte is not cachable, CIIN must be asserted for all corresponding bus cycles. The assertion of the CIIN signal prevents the caches from being updated during read cycles. Write cycles (including the write portion of a read-modify-write cycle) ignore the assertion of the CIIN signal and may cause the data cache to be altered, depending on the state of the cache (whether or not the write cycle hits), the state of the WA bit in the CACR, and the conditions indicated by the MMU.

The occurrence of a bus error while attempting to load a cache entry aborts the entry fill operation but does not necessarily cause a bus error exception. If the bus error occurs on a read cycle for a portion of the required operand (not the remaining bytes of the cache entry) to be loaded into the data cache, the processor immediately takes a bus error exception. If the read cycle in error is made only to fill the data cache (the data is not part of the target operand), no exception occurs, but the corresponding entry is marked invalid. For the instruction cache, the processor marks the entry as invalid, but only takes an exception if the execution unit attempts to use the instruction word(s).

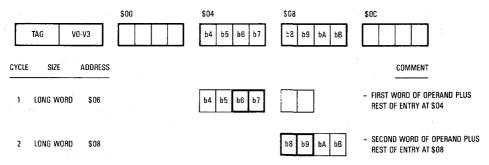

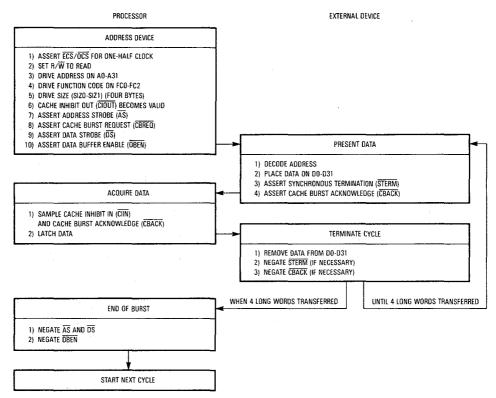

- **6.1.3.2 BURST MODE FILLING.** Burst mode filling is enabled by bits in the cache control register. The data burst enable bit must be set to enable burst filling of the data cache. Similarly, the instruction burst enable bit must be set to enable burst filling of the instruction cache. When burst filling is enabled and the corresponding cache is enabled, the bus controller requests a burst mode fill operation in either of these cases:

- A read cycle for either the instruction or data cache misses due to the indexed tag not matching.

- A read cycle tag matches, but all long words in the line are invalid.

Figure 7-37. Burst Operation Flowchart — Four Long Words Transferred

#### State 2

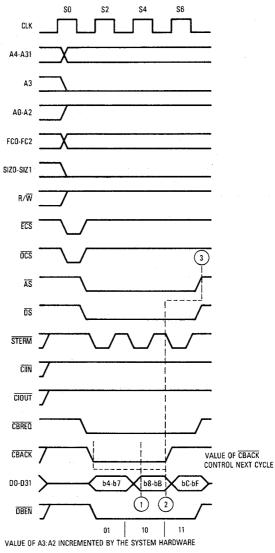

The selected device uses R/W, SIZ0–SIZ1, A0–A1, and  $\overline{CIOUT}$  to place the data on the data bus. (The first cycle must supply the long word at the corresponding long-word boundary.) All of the byte sections (D24–D31, D16–D23, D8–D15, and D0–D7) of the data bus must be driven since the burst operation latches 32 bits on every cycle. During S2, the processor drives DBEN active to enable external data buffers. In systems that use two-clock synchronous bus cycles, the timing of DBEN may prevent its use. At the beginning of S2, the processor tests the level of STERM. If STERM is recognized, the processor latches the incoming data at the end of S2. For the burst operation to proceed, CBACK must be asserted when STERM is recognized. If the data for the current cycle is not to be cached, CIIN must be asserted at the same time as STERM. The assertion of CIIN also has the effect of aborting the burst operation.

MOTOROLA

NOTES:

Assertion of CBACK causes data to be placed on D0-D31.

Continued assertion of CBACK causes data to be placed on D0-D31.

Negation of CBACK cause AS to be negated.

Figure 7-39. Long-Word Operand Request from \$07 with Burst Request — CBACK Negated Early

MC68030 USER'S MANUAL

MOTOROLA

- 0-15 Upper Logical Address Bits Can Be Ignored (Using Initial Shift)

- Portions of Tables Can Be Undefined (Using Limits)

- Write Protection and Supervisor Protection

- History Bits Automatically Maintained in Page Descriptors

- Cache Inhibit Output (CIOUT) Signal Asserted on Page Basis

- External Translation Disable Input Signal (MMUDIS)

- Subset of Instruction Set Defined by MC68851

The MMU completely overlaps address translation time with other processing activity when the translation is resident in the ATC. ATC accesses operate in parallel with the on-chip instruction and data caches.

Figure 9-1 is a block diagram of the MC68030 showing the relationship of the MMU to the execution unit and the bus controller. For an instruction or operand access, the MC68030 simultaneously searches the caches and searches for a physical address in the ATC. If the translation is available, the MMU provides the physical address to the bus controller and allows the bus cycle to continue. When the instruction or operand is in either of the on-chip caches on a read cycle, the bus controller aborts the bus cycle before address strobe is asserted. Similarly, the MMU causes a bus cycle to abort before the assertion of address strobe when a valid translation is not available in the ATC or when an invalid access is attempted.

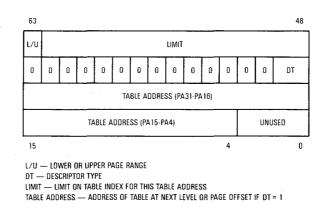

An MMU disable input signal (MMUDIS) is provided that dynamically disables address translation for emulation, diagnostic, or other purposes.

The programming model of the MMU (see Figure 9-2) consists of two root pointer registers, a control register, two transparent translation registers, and a status register. These registers can only be accessed by supervisor programs. The CPU root pointer register points to an address translation tree structure in memory that describes the logical-to-physical mapping for user accesses or for both user and supervisor accesses. The supervisor root pointer register optionally points to an address translation tree structure for supervisor mappings. The translation control register is comprised of fields that control the translation operation. Each transparent translation register can define a block of logical addresses that are used as physical addresses (without translation). The MMU status register contains accumulated status information from a translation performed as a part of a PTEST instruction.

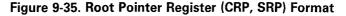

### 9.7.2 Translation Control Register

The translation control register (TC) is a 32-bit register that contains the control fields for address translation. All unimplemented fields of this register are read as zeros and must always be written as zeros.

Writing to this register optionally causes a flush of the entire ATC. When written with the E bit (bit 31) set (translation enabled), a consistency check is performed on the values of PS, IS, and TIx as follows. The TIx fields are added together until a zero field is reached, and this sum is added to PS and IS. The total must be 32, or an MMU configuration exception (refer to **9.7.5.3 MMU CONFIGURATON EXCEPTION**) is taken. If an MMU configuration exception occurs, the TC register is updated with the data, and the E bit is cleared. The translation control register is shown in Figure 9-36.

Figure 9-36. Translation Control Register (TC) Format

An operating system can use an early termination page descriptor to map a contiguous block of memory for each task (both program and data). The tasks can be relocated by changing the physical address portion of the descriptor. This scheme is useful when the tasks in a system consist of one or a few sequential blocks of memory that can be swapped as a group. The operating system memory map can treat the entire address space within these blocks as a uniform virtual space available for all tasks. The system only requires one translation table; by the use of limit fields and early termination page descriptors, it maps complete segments of memory.

- **9.9.3.5 INDIRECT DESCRIPTORS.** An indirect descriptor is a table descriptor residing in a page table. It points to another page descriptor in the translation tree. Using an indirect descriptor for a page makes the page common to several tasks. History information for a common page is maintained in only one descriptor. Access to the page sets the used (U) bit, and a write operation to the page sets the M (modified) bit for that page. When the operating system is searching for an available page, it simply checks the page table containing the descriptor for the common page to determine its status. With other methods of page sharing, the system would have to check page tables for all sharing tasks to determine the status of the common page.

- **9.9.3.6 USING UNUSED DESCRIPTOR BITS.** In general, the bits in the unused fields of many types of descriptors are available to the operating system for its own purposes. The invalid descriptor, in particular, uses only two bits of the 32 (short) or 64 (long) bits available with that format. An operating system typically uses these fields for the software flags, indicating whether the virtual address space is allocated and whether an image resides on the paging device. Also, these fields often contain the physical address of the image.

The operating system often maintains information in an unused field about a page resident in memory. This information may be an aging counter or some other indication of the page's frequency of use. This information helps the operating system to identify the pages that are least likely to impact system performance if they are reallocated. The system should first use physical page frames that are not allocated to a virtual page. Next it should use pages with the longest time since the most recent access. Pages that do not have the M (modified) bit set should be taken first, since they do not need to be copied to the paging device (the existing image remains valid).

the table size). By convention, the first entry maps the supervisor address space and has supervisor protection. The routine never modifies this first entry. The 31 entries after the first are available to be allocated as user address space.

A routine similar to this that linearly extends (grows) a previously allocated memory block could be written. A stack is a good example. The operating system can allocate the top of the memory (the thirty-second upper level table entry) as a stack that grows downward from the highest address. If a task needs several large stacks, a 16-Mbyte block can be used for each stack, with a software flag set to indicate growth in a downward direction.

The logic of Vallocate is:

- 1. Validate the request and calculate number of pages required.

- 2. Scan each upper table entry's lower page tables (where they exist) looking for an adequate group of unallocated pages.

- 3. If no space is found, see if the lower table is less than its maximum size and if the block can be allocated by expanding it at the end.

- 4. If still no space is found, use the next free upper table entry and initialize its new lower level page table to allocate the block here.

- 5. Set allocated page entries to indicate virgin status (allocated, invalid, and not swapped out).

- 6. Return status. If status is OK, also return virtual address.

The code for Vallocate is:

#### Vallocate (SizeInBytes, VirtualAddressReturned, Status);

| /* The following are global to all routines                                                                                                                  |                                                                                                                                                                       | */                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| /* Symbolicly define the upper level pointer table                                                                                                           |                                                                                                                                                                       | •/                   |

| Declare Upper_Table[32] Record of<br>Status=(unallocated, allocated),<br>Limit_Field=(0 to 4k),<br>Pointer;                                                  | /* lower table here or not<br>/* limit for lower page table<br>/*address of lower page table if allocated                                                             | */<br>*/<br>*/       |

| /* Symbolicly define the lower level page table                                                                                                              |                                                                                                                                                                       | •/                   |

| Declare Lower_Table[0 to Limit_Field] Based Record<br>Status=(invalid_unallocated,<br>invalid_paged_out,<br>invalid_virgin,<br>valid_in_memory),<br>Pointer; | of<br>/*not allocated to User<br>/*allocated but paged out<br>/*allocated but not yet used<br>/*allocated and in memory<br>/*physical address or disk address of page | •/<br>•/<br>•/<br>•/ |

## IV.H.I ScanPC

Several of the response primitives involve the scanPC, and many of them require the main processor to use it while performing services requested. These paragraphs describe the scanPC and tell how it operates.

During the execution of a coprocessor instruction, the program counter in the MC68030 contains the address of the F-line operation word of that instruction. A second register, called the scanPC, sequentially addresses the remaining words of the instruction.

If the main processor requires extension words to calculate an effective address or destination address of a branch operation, it uses the scanPC to address these extension words in the instruction stream. Also, if a coprocessor requests the transfer of extension words, the scanPC addresses the extension words during the transfer. As the processor references each word, it increments the scanPC to point to the next word in the instruction stream. When an instruction is completed, the processor transfers the value in the scanPC to the program counter to address the operation word of the next instruction.

The value in the scanPC when the main processor reads the first response primitive after beginning to execute an instruction depends on the instruction being executed. For a cpGEN instruction, the scanPC points to the word following the coprocessor command word. For the cpBcc instructions, the scanPC points to the word following the instruction F-line operation word. For the cpScc, cpTRAPcc, and cpDBcc instructions, the scanPC points to the word following the coprocessor condition specifier word.

If a coprocessor implementation uses optional instruction extension words with a general or conditional instruction, the coprocessor must use these words consistently so that the scanPC is updated accordingly during the instruction execution. Specifically, during the execution of general category instructions, when the coprocessor terminates the instruction protocol, the MC68030 assumes that the scanPC is pointing to the operation word of the next instruction to be executed. During the execution of conditional category instructions, when the coprocessor terminates the instruction protocol, the MC68030 assumes that the scanPC is pointing to the word following the last of any coprocessor-defined extension words in the instruction format.

tions. If the coprocessor issues this primitive during the execution of a conditional category instruction, the main processor initiates protocol violation exception processing. Figure 10-37 shows the format of the transfer multiple coprocessor registers primitive.

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7      | 0 |

|----|----|----|----|----|----|---|---|--------|---|

| CA | PC | DR | 0  | 0  | 0  | 0 | 1 | LENGTH |   |

### Figure 10-37. Transfer Multiple Coprocessor Registers Primitive Format

This primitive uses the CA, PC, and DR bits as previously described.

Bits [7–0] of the primitive format indicate the length in bytes of each operand transferred. The operand length must be an even number of bytes; odd length operands cause the MC68030 to initiate protocol violation exception processing (refer to **10.5.2.1 PROTOCOL VIOLATIONS**).

When the main processor reads this primitive, it calculates the effective address specified in the coprocessor instruction. The scanPC should be pointing to the first of any necessary effective address extension words when this primitive is read from the response CIR; the scanPC is incremented by two for each extension word referenced during the effective address calculation. For transfers from the effective address to the coprocessor (DR = 0), the control addressing modes and the postincrement addressing mode are valid. For transfers from the coprocessor to the effective address (DR = 1), the control alterable and predecrement addressing modes are valid. Invalid addressing modes cause the MC68030 to abort the instruction by writing an abort mask (refer to 10.3.2 Control CIR) to the control CIR and to initiate F-line emulator exception processing (refer to 10.5.2.2 F-LINE EMULATOR EXCEPTIONS).

After performing the effective address calculation, the MC68030 reads a 16-bit register select mask from the register select CIR. The coprocessor uses the register select mask to specify the number of operands to transfer; the MC68030 counts the number of ones in the register select mask to determine the number of operands. The order of the ones in the register select mask is not relevant to the operation of the main processor. As many as 16 operands can be transferred by the main processor in response to this primitive. The total number of bytes transferred is the product of the number of operands transferred and the length of each operand specified in bits [0–7] of the primitive format.

| Primitive                                                                                                                                                                                                                                  | Protocol | F-Line | Other |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|-------|

| Transfer Status and/or ScanPC<br>Protocol: If Used with Conditional Instruction<br>Other:<br>1. Trace — Trace Made Pending if MC68020 in "Trace on Change<br>of Flow" Mode and DR = 1<br>2. Address Error — If Odd value Written to ScanPC | X        |        | x     |

| Take Pre-Instruction, Mid-Instruction, or Post-Instruction Exception<br>Exception Depends on Vector Supplies in Primitive                                                                                                                  | ×        | х      | х     |

#### Table 10-6. Exceptions Related to Primitive Processing (Sheet 2 of 2)

\*Use of this primitive with CA=0 will cause protocol violation on conditional instructions. Abbreviations:

EA = Effective Address CP = Coprocessor

When the MC68030 detects a protocol violation, it does not automatically notify the coprocessor of the resulting exception by writing to the control CIR. The exception handling routine may, however, use the MOVES instruction to read the response CIR and thus determine the primitive that caused the MC68030 to initiate protocol violation exception processing. The main processor initiates exception processing using the mid-instruction stack frame (refer to Figure 10-43) and the coprocessor protocol violation exception vector number 13. If the exception handler does not modify the stack frame, the main processor reads the response CIR again following the execution of an RTE instruction to return from the exception handler. This protocol allows extensions to the M68000 coprocessor interface to be emulated in software by a main processor that does not provide hardware support for these extensions. Thus, the protocol violation is transparent to the coprocessor if the primitive execution can be emulated in software by the main processor.

# 11.6.1 Fetch Effective Address (fea)

The fetch effective address table indicates the number of clock periods needed for the processor to calculate and fetch the specified effective address. The effective addresses are divided by their formats (refer to **2.5 Effective Address Encoding Summary**). For instruction-cache case and for no-cache case, the total number of clock cycles is outside the parentheses. The number of read, prefetch, and write cycles is given inside the parentheses as (r/p/w). The read, prefetch, and write cycles are included in the total clock cycle number.

All timing data assumes two-clock reads and writes.

| 1 |              |      |          |             |                 |

|---|--------------|------|----------|-------------|-----------------|

|   | Address Mode | Head | Tail     | LCacho Caso | No-Cache Case   |

|   | Address mode | neau | 1 1 4 11 |             | INU-Cacile Case |

|   |              |      |          |             | L               |

#### SINGLE EFFECTIVE ADDRESS INSTRUCTION FORMAT

| % Dn                                           | -   | - | 0(0/0/0) | <b>0</b> (0/0/0) |

|------------------------------------------------|-----|---|----------|------------------|

| % An                                           |     | - | 0(0/0/0) | 0(0/0/0)         |

| (An)                                           | 1   | 1 | 3(1/0/0) | 3(1/0/0)         |

| (An) +                                         | 0   | 1 | 3(1/0/0) | 3(1/0/0)         |

| - (An)                                         | 2   | 2 | 4(1/0/0) | 4(1/0/0)         |

| (d <sub>16</sub> ,An) or (d <sub>16</sub> ,PC) | 2   | 2 | 4(1/0/0) | 4(1/1/0)         |

| (xxx).W                                        | 2   | 2 | 4(1/0/0) | 4(1/1/0)         |

| (xxx).L                                        | . 1 | 0 | 4(1/0/0) | 5(1/1/0)         |

| #(data).B                                      | 2   | 0 | 2(0/0/0) | 2(0/1/0)         |

| #(data).W                                      | 2   | 0 | 2(0/0/0) | <b>2</b> (0/1/0) |

| #(data).L                                      | 4   | 0 | 4(0/0/0) | 4(0/1/0)         |

#### **BRIEF FORMAT EXTENSION WORD**

|                          |   |   | And a second | The second se |

|--------------------------|---|---|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| (dg,An,Xn) or (dg,PC,Xn) | 4 | 2 | 6(1/0/0)                                                                                                       | <b>6(1</b> /1/0)                                                                                                |

11-26

# 11.6.3 Calculate Effective Address (cea) (Continued)

| Address Mode                                                                               | Head                                   | Tail | I-Cache Case      | No-Cache Case     |

|--------------------------------------------------------------------------------------------|----------------------------------------|------|-------------------|-------------------|

| SINGLE EFFECTIVE ADDRESS INSTRUCTION FO                                                    | ORMAT                                  |      |                   |                   |

| % Dn                                                                                       | 1 - 1                                  |      | 0(0/0/0)          | 0(0/0/0)          |

| % An                                                                                       |                                        |      | 0(0/0/0)          | <b>0</b> (0/0/0)  |

| (An)                                                                                       | 2+op head                              | 0    | 2(0/0/0)          | 2(0/0/0)          |

| (An) +                                                                                     | 0                                      | 0    | 2(0/0/0)          | 2(0/0/0)          |

| – (An)                                                                                     | 2+op head                              | 0    | 2(0/0/0)          | 2(0/0/0)          |

| (d <sub>16</sub> ,An) or (d <sub>16</sub> ,PC)                                             | 2+op head                              | 0    | 2(0/0/0)          | 2(0/1/0)          |

| (xxx).W                                                                                    | 2+op head                              | 0    | 2(0/0/0)          | 2(0/1/0)          |

| (xxx).L                                                                                    | 4+op head                              | 0    | 4(0/0/0)          | 4(0/1/0)          |

| BRIEF FORMAT EXTENSION WORD                                                                | ······································ |      |                   |                   |

| (dg,An,Xn) or (dg,PC,Xn)                                                                   | 4+op head                              | 0    | 4(0/0/0)          | <b>4</b> (0/1/0)  |

| FULL FORMAT EXTENSION WORD(S)                                                              |                                        |      |                   |                   |

| (d <sub>16</sub> ,An) or (d <sub>16</sub> ,PC)                                             | 2                                      | 0    | 6(0/0/0)          | 6(0/1/0)          |

| (d <sub>16</sub> ,An,Xn) or (d <sub>16</sub> ,PC,Xn)                                       | 6+op head                              | 0    | <b>6</b> (0/0/0)  | <b>6</b> (0/1/0)  |

| ([d <sub>16</sub> ,An]) or ([d <sub>16</sub> ,PC])                                         | 2                                      | 0    | <b>10</b> (1/0/0) | <b>10</b> (1/1/0) |

| ([d <sub>16</sub> ,An],Xn) or ([d <sub>16</sub> ,PC],Xn)                                   | 2                                      | 0    | 10(1/0/0)         | <b>10</b> (1/1/0) |

| ([d16,An],d16) or ([d16,PC],d16)                                                           | 2                                      | 0    | 12(1/0/0)         | <b>13</b> (1/2/0) |

| ([d <sub>16</sub> ,An],Xn,d <sub>16</sub> ) or ([d <sub>16</sub> ,PC],Xn,d <sub>16</sub> ) | 2                                      | 0    | <b>12</b> (1/0/0) | 13(1/2/0)         |

| ([d16,An],d32) or ([d16,PC],d32)                                                           | 2                                      | 0    | 12(1/0/0)         | 13(1/2/0)         |

| ([d <sub>16</sub> ,An],Xn,d <sub>32</sub> ) or ([d <sub>16</sub> ,PC],Xn,d <sub>32</sub> ) | 2                                      | 0    | <b>12</b> (1/0/0) | <b>13</b> (1/2/0) |

| (B)                                                                                        | 6+op head                              | 0    | 6(0/0/0)          | <b>6</b> (0/1/0)  |

| (d <sub>16</sub> ,B)                                                                       | 4                                      | 0    | 8(0/0/0)          | <b>9</b> (0/1/0)  |

| (d <sub>32</sub> ,B)                                                                       | 4                                      | 0    | 12(0/0/0)         | <b>12</b> (0/2/0) |

| ([B])                                                                                      | 4                                      | 0    | <b>10</b> (1/0/0) | <b>10(</b> 1/1/0) |

| ([B],I)                                                                                    | 4                                      | 0    | <b>10</b> (1/0/0) | <b>10</b> (1/1/0) |

| ([B],d <sub>16</sub> )                                                                     | 4                                      | 0    | <b>12</b> (1/0/0) | <b>13</b> (1/1/0) |

| ([B],I,d <sub>16</sub> )                                                                   | 4                                      | 0    | 12(1/0/0)         | <b>13</b> (1/1/0) |

| ([B],d <sub>32</sub> )                                                                     | 4                                      | 0    | 12(1/0/0)         | 13(1/2/0)         |

| ([B],I,d <sub>32</sub> )                                                                   | 4                                      | 0    | 12(2/0/0)         | 13(1/2/0)         |

| ([d <sub>16</sub> ,B])                                                                     | 4                                      | 0    | <b>12</b> (1/0/0) | 13(1/1/0)         |

| ([d <sub>16</sub> ,B],I)                                                                   | 4                                      | 0    | 12(1/0/0)         | 13(1/1/0)         |

| ([d <sub>16</sub> ,B],d <sub>16</sub> )                                                    | 4                                      | 0    | 14(1/0/0)         | <b>16</b> (1/2/0) |

| ([d <sub>16</sub> ,B],I,d <sub>16</sub> )                                                  | 4                                      | 0    | <b>14</b> (1/0/0) | <b>16</b> (1/2/0) |

1

# INDEX

Abort Task Routine, 9-86 Absolute Long Address Mode, 2-20 Absolute Short Address Mode, 2-20 Access Time Calculations, Memory, 12-14-12-17 Accesses, Read-Modify-Write, 6-10 Acknowledge, Breakpoint, 8-10 Activity, Data Bus, 12-11 Processor, Even Alignment, 11-9 Odd Alignment, 11-10 Actual Instruction Cache Case, 11-11 Adapter Board, MC68020, 12-1 Signal Routing, 12-1 Address Bus, 5-4, 7-4, 7-30ff, 12-4 Address Encoding, CPU Space, 7-68 Address Error Exception, 8-9, 10-72 Address Offset Encoding, 7-9 Address Register Direct Mode, 2-10 Indirect Displacement Mode, 2-12 Indirect Index (Base Displacement) Mode, 2-13 Indirect Index (8-Bit Displacement) Mode, 2-12 Indirect Mode, 2-10 Indirect Postincrement Mode, 2-10 Indirect Predecrement Mode, 2-11 Address Registers, 1-6, 2-3 Address Space Types, 4-3 Address Strobe Signal, 5-5, 7-3, 7-4, 7-26ff Address Translation, 9-13 Cache, 7-3, 9-4, 9-17 Cache Entry, 9-18 General Flowchart, 9-14 Addressing, Capabilities, 2-25 Compatibility, M68000, 2-36 Indexed, 2-26 Indirect, 2-28 Indirect Absolute Memory, 2-28 Mode Summary, 2-31 Modes, 1-10, 2-8 Structure, 2-36 Aids, Debugging, 12-35 Arbitration, Bus, 7-96 Arithmetic/Logical Instruction, Immediate, Timing Table, 11-42 Timing Table, 11-40 AS Signal, 5-5, 7-3, 7-4, 7-26ff

- Δ -

Assignment, Pin, 14-2, 14-3 Assignments, Exception Vector, 8-2 Asynchronous Bus Operation, 7-27 Bvte Read Cycle, 32-Bit Port, Timing, 7-33 Read Cycle Flowchart, 7-32 Read-Modify-Write Cycle, 32-Bit Port, Timing, 7-45 Write Cycle, 32-Bit Port, Timing, 7-38 Cycle Signal Assertion Results, 7-78, 7-79 Long-Word Read Cycle Flowchart, 7-32 Read Cycle, 7-31 32-Bit Port, Timing, 7-33 Read-Modify-Write Cycle, 7-45 Flowchart, 7-44 Sample Window, 7-3 Word Read Cycle, 32-Bit Port, Timing, 7-33 Write Cycle, 32-Bit Port, Timing, 7-39 Write Cycle, 7-37 32-Bit Port, Timing, 7-38 Flowchart, 7-37 ATC, 7-3, 9-4, 9-17 Entry, 9-17 Creation Flowchart, 9-42 Autovector Interrupt Acknowledge Cycle, 7-71 Timing, 7-72 Autovector Signal, 5-8, 7-6, 7-29, 7-71ff, 8-20 AVEC Signal, 5-8, 7-6, 7-29, 7-71ff, 8-20 Average No Cache Case, 11-8 A0-A1 Signals, 7-8, 7-9, 7-22ff A0-A31 Signals, 5-4, 7-4, 7-31ff A0-A7, 1-6

#### — B —

BERR Signal, 5-9, 6-11, 7-6, 7-27ff, 8-7, 8-22, 8-26,

Best Case, 11-7

BG Signal, 5-9, 7-43, 7-96ff

BGACK Signal, 5-9, 7-97ff

Binary-Coded Decimal Instruction Timing Table,

11-43

Binary-Coded Decimal Instructions, 3-10

Bit,

CA, 10-35

CD, 6-21

CEI, 6-22

CI, 6-22

Clear Data Cache, 6-21

#### MC68030 USER'S MANUAL

Timing (Continued) Write Cycle, Wait States, CIOUT Asserted, 7-53 Table Search, 11-39 Write, Long-Word, 7-12 Write, Word, 7-14 Timing Table, Arithmetic/Logical Instruction, 11-40 Immediate, 11-42 Binary Coded Decimal Instruction, 11-43 Bit Field Instruction, 11-47 Bit Manipulation Instruction, 11-46 Calculate Effective Address, 11-30 Calculate Immediate Effective Address, 11-32 Conditional Branch Instruction, 11-48 Control Instruction, 11-49 **Exception Related** Instruction, 11-50 Operation, 11-50 Extended Instruction, 11-43 Fetch Effective Address, 11-26 Fetch Immediate Effective Address, 11-28 Jump Effective Address, 11-35 MMU Effective Address, 11-58 Instruction, 11-60 MOVE Instruction, 11-37 Special Purpose, 11-39 Restore Operation, 11-51 Save Operation, 11-51 Shift/Rotate Instruction, 11-45 Single Operand Instruction, 11-44 Table Search, 11-51 Trace Exception, 8-12, 10-70 Signals, 12-38 Tradeoffs, Performance, 11-1 Transfer, Long Word to Long Word, Misaligned Cachable, 7-20 Long Word to Word, 7-11 Misaligned Cachable Word to Long Word, 7-17 Cachable Word to Word, 7-20 Long Word to Long Word, 7-20 Long Word to Word, 7-17 Word to Word, 7-17 Word to Word, Timing, 7-18 Word to Byte, 7-13 Transfer Main Processor Control Register Primitive, 10-50Transfer Multiple Coprocessor Registers Primitive, 10-52 Transfer Multiple Main Processor Registers Primitive, 10-52 Transfer Operation Word Primitive, 10-40 Transfer Single Main Processor Register Primitive, 10-50 Transfer Size Signals, 5-4, 7-4, 7-8, 7-9-7-14, 7-22ff Transfer Status Register and ScanPC Primitive, 10-55

Transfer to/from Top of Stack Primitive, 10-49 Translation, Address, 9-13 Translation Control Register, 1-9, 2-5, 9-8, 9-54 Translation Table Descriptors, 9-10, 9-20 Translation Table Tree, 9-5, 9-7, 9-8, 9-12, 9-30, 9-47, 9-48, 9-65 Translation Tree, Supervisor, 9-48 Protection Example, 9-50 Transparent Translation Registers, 1-9, 2-5, 9-16, 9-55 Tree, Translation Table, 9-5, 9-7, 9-8, 9-12, 9-30, 9-47, 9-48, 9-65 TT0, 1-9, 2-5, 9-16, 9-57 TT1, 1-9, 2-5, 9-16, 9-57 Two Clock Synchronous Static RAM, 12-18-12-20 Types, Address Space, 4-3 Data, 1-10

#### \_ U \_

Unimplemented Instruction Exception, 8-9 Unit, Execution, 6-16 Memory Management, 1-15, 7-3, 7-36, 7-43, 9-1, 11-5, 12-4 Units, Floating Point, 12-5 Unused Descriptor Bits, 9-71 User Privilege Level, 4-2, 4-4 User Program Stack, 2-38

#### -- V --

Valid Format Word, 10-24 Vallocate Routine, 9-78 VBR, 1-8, 2-5 V<sub>CC</sub> Pin Assignments, 12-46 Vector Base Register, 1-8, 2-5 Numbers, Exception, 8-1 Vectors, Exception, 4-6 Virtual Machine, 1-12 Virtual Memory, 1-12, 9-77

#### — W —

WA Bit, 6-21 Wait States, 11-18 Window, Asynchronous Sample, 7-3 Word, Special Status, 8-28 Word Read Cycle, Asynchronous, 32-Bit Port, Timing, 7-33 Word to Byte Transfer, 7-13 Word to Long-Word Transfer, Misaligned, 7-17 Word to Word Transfer, Misaligned Cachable, 7-20