Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

#### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

E·XFI

| 2014110                 |                                                                   |

|-------------------------|-------------------------------------------------------------------|

| Product Status          | Obsolete                                                          |

| Architecture            | MCU, FPGA                                                         |

| Core Processor          | ARM® Cortex®-M3                                                   |

| Flash Size              | 128KB                                                             |

| RAM Size                | 16KB                                                              |

| Peripherals             | DMA, POR, WDT                                                     |

| Connectivity            | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                        |

| Speed                   | 100MHz                                                            |

| Primary Attributes      | ProASIC®3 FPGA, 60K Gates, 1536D-Flip-Flops                       |

| Operating Temperature   | -55°C ~ 125°C (TJ)                                                |

| Package / Case          | 256-LBGA                                                          |

| Supplier Device Package | 256-FPBGA (17x17)                                                 |

| Purchase URL            | https://www.e-xfl.com/product-detail/microsemi/a2f060m3e-1fgg256m |

|                         |                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Power per I/O Pin

#### Table 2-10 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

|                            | VCCFPGAIOBx (V) | Static Power<br>PDC7 (mW) | Dynamic Power PAC9<br>(µW/MHz) |

|----------------------------|-----------------|---------------------------|--------------------------------|

| Single-Ended               |                 |                           |                                |

| 3.3 V LVTTL / 3.3 V LVCMOS | 3.3             | _                         | 17.55                          |

| 2.5 V LVCMOS               | 2.5             | _                         | 5.97                           |

| 1.8 V LVCMOS               | 1.8             | _                         | 2.88                           |

| 1.5 V LVCMOS (JESD8-11)    | 1.5             | _                         | 2.33                           |

| 3.3 V PCI                  | 3.3             | _                         | 19.21                          |

| 3.3 V PCI-X                | 3.3             | _                         | 19.21                          |

| Differential               | <b>_</b>        |                           |                                |

| LVDS                       | 2.5             | 2.25                      | 0.82                           |

| LVPECL                     | 3.3             | 5.74                      | 1.16                           |

## Table 2-11 • Summary of I/O Input Buffer Power (per pin) – Default I/O Software Settings Applicable to MSS I/O Banks

|                                               | VCCMSSIOBx (V) | Static Power<br>PDC7 (mW) | Dynamic Power<br>PAC9 (µW/MHz) |

|-----------------------------------------------|----------------|---------------------------|--------------------------------|

| Single-Ended                                  |                |                           | 1                              |

| 3.3 V LVTTL / 3.3 V LVCMOS                    | 3.3            | _                         | 17.21                          |

| 3.3 V LVCMOS / 3.3 V LVCMOS – Schmitt trigger | 3.3            | _                         | 20.00                          |

| 2.5 V LVCMOS                                  | 2.5            | _                         | 5.55                           |

| 2.5 V LVCMOS – Schmitt trigger                | 2.5            | _                         | 7.03                           |

| 1.8 V LVCMOS                                  | 1.8            | _                         | 2.61                           |

| 1.8 V LVCMOS – Schmitt trigger                | 1.8            | _                         | 2.72                           |

| 1.5 V LVCMOS (JESD8-11)                       | 1.5            | _                         | 1.98                           |

| 1.5 V LVCMOS (JESD8-11) – Schmitt trigger     | 1.5            | _                         | 1.93                           |

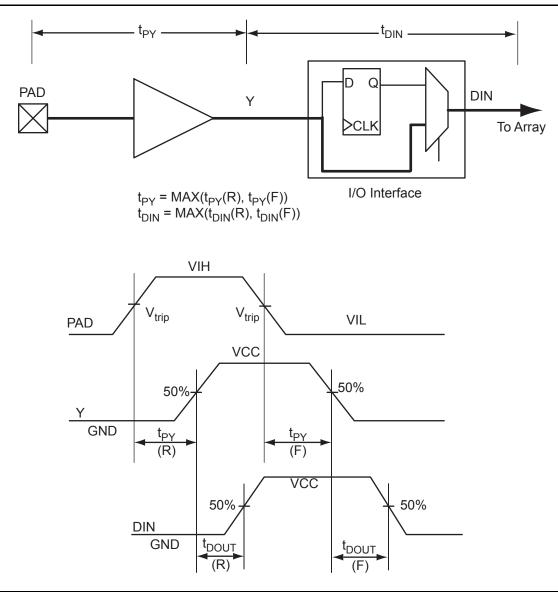

Figure 2-4 • Input Buffer Timing Model and Delays (example)

## **Overview of I/O Performance**

# Summary of I/O DC Input and Output Levels – Default I/O Software Settings

#### Table 2-19 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Military Conditions—Software Default Settings Applicable to FPGA I/O Banks

|                               |                        |                          |      | VIL                   | VIH                  |           | VOL                   | VOH                   | IOL <sup>1</sup> | IOH <sup>1</sup> |

|-------------------------------|------------------------|--------------------------|------|-----------------------|----------------------|-----------|-----------------------|-----------------------|------------------|------------------|

| I/O Standard                  | Drive<br>Strgth.       |                          |      | Max.<br>V             | Min.<br>V            | Max.<br>V | Max.<br>V             | Min.<br>V             | mA               | mA               |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 12 mA                  | High                     | -0.3 | 0.8                   | 2                    | 3.6       | 0.4                   | 2.4                   | 12               | 12               |

| 2.5 V LVCMOS                  | 12 mA                  | High                     | -0.3 | 0.7                   | 1.7                  | 3.6       | 0.7                   | 1.7                   | 12               | 12               |

| 1.8 V LVCMOS                  | 12 mA                  | High                     | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                  | VCCxxxxIOBx<br>- 0.45 | 12               | 12               |

| 1.5 V LVCMOS                  | 12 mA                  | High                     | -0.3 | 0.35 *<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25 *<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 12               | 12               |

| 3.3 V PCI                     | Per PCI specifications |                          |      |                       |                      |           |                       |                       |                  |                  |

| 3.3 V PCI-X                   |                        | Per PCI-X specifications |      |                       |                      |           |                       |                       |                  |                  |

Notes:

1. Currents are measured at 125°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

# Table 2-20 • Summary of Maximum and Minimum DC Input and Output Levels Applicable to Military Conditions—Software Default Settings Applicable to MSS I/O Banks

|                               |                  |              | VIL  |                      | VIH                  |           | VOL                  | VOH                   | IOL <sup>1</sup> | IOH <sup>1</sup> |

|-------------------------------|------------------|--------------|------|----------------------|----------------------|-----------|----------------------|-----------------------|------------------|------------------|

| I/O Standard                  | Drive<br>Strgth. | Slew<br>Rate |      | Max.<br>V            | Min.<br>V            | Max.<br>V | Max.<br>V            | Min.<br>V             | mA               | mA               |

| 3.3 V LVTTL /<br>3.3 V LVCMOS | 8 mA             | High         | -0.3 | 0.8                  | 2                    | 3.6       | 0.4                  | 2.4                   | 8                | 8                |

| 2.5 V LVCMOS                  | 8 mA             | High         | -0.3 | 0.7                  | 1.7                  | 3.6       | 0.7                  | 1.7                   | 8                | 8                |

| 1.8 V LVCMOS                  | 4 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.45                 | VCCxxxxIOBx<br>- 0.45 | 4                | 4                |

| 1.5 V LVCMOS                  | 2 mA             | High         | -0.3 | 0.35*<br>VCCxxxxIOBx | 0.65*<br>VCCxxxxIOBx | 3.6       | 0.25*<br>VCCxxxxIOBx | 0.75*<br>VCCxxxxIOBx  | 2                | 2                |

Notes:

1. Currents are measured at 125°C junction temperature.

2. Output slew rate can be extracted by the IBIS Models.

|                            | Drive Strength              | IOSL (mA) <sup>*</sup> | IOSH (mA) <sup>*</sup> |

|----------------------------|-----------------------------|------------------------|------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 2 mA                        | 27                     | 25                     |

|                            | 4 mA                        | 27                     | 25                     |

|                            | 6 mA                        | 54                     | 51                     |

|                            | 8 mA                        | 54                     | 51                     |

|                            | 12 mA                       | 109                    | 103                    |

|                            | 16 mA                       | 127                    | 132                    |

|                            | 24 mA                       | 181                    | 268                    |

| 2.5 V LVCMOS               | 2 mA                        | 18                     | 16                     |

|                            | 4 mA                        | 18                     | 16                     |

|                            | 6 mA                        | 37                     | 32                     |

|                            | 8 mA                        | 37                     | 32                     |

|                            | 12 mA                       | 74                     | 65                     |

|                            | 16 mA                       | 87                     | 83                     |

|                            | 24 mA                       | 124                    | 169                    |

| 1.8 V LVCMOS               | 2 mA                        | 11                     | 9                      |

|                            | 4 mA                        | 22                     | 17                     |

|                            | 6 mA                        | 44                     | 35                     |

|                            | 8 mA                        | 51                     | 45                     |

|                            | 12 mA                       | 74                     | 91                     |

|                            | 16 mA                       | 74                     | 91                     |

| 1.5 V LVCMOS               | 2 mA                        | 16                     | 13                     |

|                            | 4 mA                        | 33                     | 25                     |

|                            | 6 mA                        | 39                     | 32                     |

|                            | 8 mA                        | 55                     | 66                     |

|                            | 12 mA                       | 55                     | 66                     |

| 3.3 V PCI/PCI-X            | Per PCI/PCI-X specification | 109                    | 103                    |

## Table 2-30 • I/O Short Currents IOSH/IOSL Applicable to FPGA I/O Banks

*Note:*  $*T_J = 100^{\circ}C$ .

## Table 2-31 • I/O Short Currents IOSH/IOSL Applicable to MSS I/O Banks

|                            | Drive Strength | I <sub>OSL</sub> (mA)* | I <sub>OSH</sub> (mA)* |

|----------------------------|----------------|------------------------|------------------------|

| 3.3 V LVTTL / 3.3 V LVCMOS | 8 mA           | 54                     | 51                     |

| 2.5 V LVCMOS               | 8 mA           | 37                     | 32                     |

| 1.8 V LVCMOS               | 4 mA           | 22                     | 17                     |

| 1.5 V LVCMOS               | 2 mA           | 16                     | 13                     |

*Note:*  $^{*}T_{J} = 100^{\circ}C$

## 🌜 Microsemi.

SmartFusion DC and Switching Characteristics

# Table 2-53 • 1.8 V LVCMOS High Slew<br/>Worst Military-Case Conditions: T<sub>J</sub> = 125°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCxxxxIOBx = 1.7 V<br/>Applicable to MSS I/O Banks

| Drive<br>Strength | Speed<br>Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | t <sub>PYS</sub> | t <sub>EOUT</sub> | t <sub>ZL</sub> | t <sub>zH</sub> | t <sub>LZ</sub> | t <sub>HZ</sub> | Units |

|-------------------|----------------|-------------------|-----------------|------------------|-----------------|------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-------|

| 4 mA              | Std.           | 0.23              | 2.97            | 0.09             | 1.17            | 1.75             | 0.23              | 3.02            | 2.92            | 2.36            | 2.41            | ns    |

|                   | -1             | 0.19              | 2.47            | 0.08             | 0.98            | 1.46             | 0.19              | 2.52            | 2.43            | 1.97            | 2.00            | ns    |

Notes:

1. Software default selection highlighted in gray.

2. For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

SmartFusion DC and Switching Characteristics

## **Differential I/O Characteristics**

#### Physical Implementation

Configuration of the I/O modules as a differential pair is handled by SoC Products Group Designer software when the user instantiates a differential I/O macro in the design.

Differential I/Os can also be used in conjunction with the embedded Input Register (InReg), Output Register (OutReg), Enable Register (EnReg), and Double Data Rate (DDR). However, there is no support for bidirectional I/Os or tristates with the LVPECL standards.

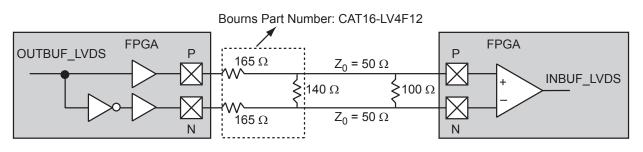

### LVDS

Low-Voltage Differential Signaling (ANSI/TIA/EIA-644) is a high-speed, differential I/O standard. It requires that one data bit be carried through two signal lines, so two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-12. The building blocks of the LVDS transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVPECL implementation because the output standard specifications are different.

Along with LVDS I/O, SmartFusion cSoCs also support bus LVDS structure and multipoint LVDS (M-LVDS) configuration (up to 40 nodes).

Figure 2-12 • LVDS Circuit Diagram and Board-Level Implementation

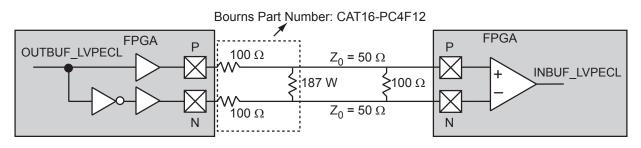

### LVPECL

Low-Voltage Positive Emitter-Coupled Logic (LVPECL) is another differential I/O standard. It requires that one data bit be carried through two signal lines. Like LVDS, two pins are needed. It also requires external resistor termination.

The full implementation of the LVDS transmitter and receiver is shown in an example in Figure 2-14. The building blocks of the LVPECL transmitter-receiver are one transmitter macro, one receiver macro, three board resistors at the transmitter end, and one resistor at the receiver end. The values for the three driver resistors are different from those used in the LVDS implementation because the output standard specifications are different.

#### Figure 2-14 • LVPECL Circuit Diagram and Board-Level Implementation

| Table 2-67 • Minimum and Maximum DC Input and Output Levels |             |      |      |      |   |  |  |  |

|-------------------------------------------------------------|-------------|------|------|------|---|--|--|--|

| DC Parameter                                                | Description | Min. | Max. | Min. | Μ |  |  |  |

| DC Parameter | Description                    | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

|--------------|--------------------------------|-------|------|-------|------|-------|------|-------|

| VCCFPGAIOBx  | Supply Voltage                 | 3.    | 3.0  |       | 3.3  |       | 3.6  |       |

| VOL          | Output Low Voltage             | 0.96  | 1.27 | 1.06  | 1.43 | 1.30  | 1.57 | V     |

| VOH          | Output High Voltage            | 1.8   | 2.11 | 1.92  | 2.28 | 2.13  | 2.41 | V     |

| VIL, VIH     | Input Low, Input High Voltages | 0     | 3.6  | 0     | 3.6  | 0     | 3.6  | V     |

| VODIFF       | Differential Output Voltage    | 0.625 | 0.97 | 0.625 | 0.97 | 0.625 | 0.97 | V     |

| VOCM         | Output Common-Mode Voltage     | 1.762 | 1.98 | 1.762 | 1.98 | 1.762 | 1.98 | V     |

| VICM         | Input Common-Mode Voltage      | 1.01  | 2.57 | 1.01  | 2.57 | 1.01  | 2.57 | V     |

| VIDIFF       | Input Differential Voltage     | 300   |      | 300   |      | 300   |      | mV    |

#### Table 2-68 • AC Waveforms, Measuring Points, and Capacitive Loads

| Input Low (V) | Input High (V) | Measuring Point* (V) | V <sub>REF</sub> (typ.) (V) |

|---------------|----------------|----------------------|-----------------------------|

| 1.64          | 1.94           | Cross point          | -                           |

*Note:* \**Measuring point = Vtrip* See Table 2-22 on page 2-25 for a complete table of trip points.

#### **Timing Characteristics**

# Table 2-69 • LVPECL<br/>Worst Military-Case Conditions: TJ = 125°C, Worst-Case VCC = 1.425 V,<br/>Worst-Case VCCFPGAIOBx = 3.0 V<br/>Applicable to FPGA I/O Banks, I/O Assigned to EMC I/O Pins

| Speed Grade | t <sub>DOUT</sub> | t <sub>DP</sub> | t <sub>DIN</sub> | t <sub>PY</sub> | Units |

|-------------|-------------------|-----------------|------------------|-----------------|-------|

| Std.        | 0.62              | 1.88            | 0.04             | 1.38            | ns    |

| -1          | 0.52              | 1.57            | 0.03             | 1.15            | ns    |

Note: For the derating values at specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

## **Microsemi**.

SmartFusion DC and Switching Characteristics

## Main and Lower Power Crystal Oscillator

The tables below describes the electrical characteristics of the main and low power crystal oscillator.

#### Table 2-84 • Electrical Characteristics of the Main Crystal Oscillator

| Parameter | Description                           | Condition                    | Min.             | Тур. | Max.             | Units  |

|-----------|---------------------------------------|------------------------------|------------------|------|------------------|--------|

|           | Operating frequency                   | Using external crystal       | 0.032            |      | 20               | MHz    |

|           |                                       | Using ceramic resonator      | 0.5              |      | 8                | MHz    |

|           |                                       | Using RC Network             | 0.032            |      | 4                | MHz    |

|           | Output duty cycle                     |                              |                  | 50   |                  | %      |

|           | Output jitter                         | With 10 MHz crystal          |                  | 1    |                  | ns RMS |

| IDYNXTAL  | Operating current                     | RC                           |                  | 0.6  |                  | mA     |

|           |                                       | 0.032–0.2                    |                  | 0.6  |                  | mA     |

|           |                                       | 0.2–2.0                      |                  | 0.6  |                  | mA     |

|           |                                       | 2.0–20.0                     |                  | 0.6  |                  | mA     |

| ISTBXTAL  | Standby current of crystal oscillator |                              |                  | 10   |                  | μA     |

| PSRRXTAL  | Power supply noise tolerance          |                              |                  | 0.5  |                  | Vp-p   |

| VIHXTAL   | Input logic level High                |                              | 90%<br>of<br>VCC |      |                  | V      |

| VILXTAL   | Input logic level Low                 |                              |                  |      | 10%<br>of<br>VCC | V      |

|           | Startup time                          | RC [tested at 3.24 MHz]      |                  | 300  | 550              | ns     |

|           |                                       | 0.032–0.2 [tested at 32 KHz] |                  | 500  | 3,000            | ms     |

|           |                                       | 0.2-2.0 [tested at 2 MHz]    |                  | 8    | 15               | ms     |

|           |                                       | 2.0–20.0 [tested at 20 MHz]  |                  | 160  | 180              | ns     |

#### Table 2-85 • Electrical Characteristics of the Low Power Oscillator

| Parameter | Description                           | Condition             | Min.       | Тур. | Max.       | Units  |

|-----------|---------------------------------------|-----------------------|------------|------|------------|--------|

|           | Operating frequency                   |                       |            | 32   |            | KHz    |

|           | Output duty cycle                     |                       |            | 50   |            | %      |

|           | Output jitter                         |                       |            | 30   |            | ns RMS |

| IDYNXTAL  | Operating current                     | 32 KHz                |            | 10   |            | μA     |

| ISTBXTAL  | Standby current of crystal oscillator |                       |            | 2    |            | μA     |

| PSRRXTAL  | Power supply noise tolerance          |                       |            | 0.5  |            | Vp-р   |

| VIHXTAL   | Input logic level High                |                       | 90% of VCC |      |            | V      |

| VILXTAL   | Input logic level Low                 |                       |            |      | 10% of VCC | V      |

|           | Startup time                          | Test load used: 20 pF |            | 2.5  |            | S      |

|           |                                       | Test load used: 30 pF |            | 3.7  | 13         | S      |

## Embedded FlashROM (eFROM)

## **Electrical Characteristics**

Table 2-91 describes the eFROM maximum performance

| Table 2-01 . | ElashPOM Access Time | Worso Militar   | Caso Conditions: T   | 」= 125°C, VCC = 1.425 V  |

|--------------|----------------------|-----------------|----------------------|--------------------------|

|              | FIASHRUW ACCess Time | , worse williar | y-case conultions. I | j - 125 C, VCC - 1.425 V |

| Parameter        | Description             | -1    | Std.  | Units |

|------------------|-------------------------|-------|-------|-------|

| F <sub>max</sub> | Maximum Clock frequency | 15.00 | 15.00 | MHz   |

## **JTAG 1532 Characteristics**

JTAG timing delays do not include JTAG I/Os. To obtain complete JTAG timing, add I/O buffer delays to the corresponding standard selected; refer to the I/O timing characteristics in the "User I/O Characteristics" section on page 2-20 for more details.

### Timing Characteristics

#### *Table 2-92* • JTAG 1532

#### Worst Military-Case Conditions: T<sub>J</sub> = 125°C, Worst-Case VCC = 1.425 V

| Parameter            | Description                 | -1    | Std.  | Units |

|----------------------|-----------------------------|-------|-------|-------|

| t <sub>DISU</sub>    | Test Data Input Setup Time  | 0.53  | 0.63  | ns    |

| t <sub>DIHD</sub>    | Test Data Input Hold Time   | 1.07  | 1.25  | ns    |

| t <sub>TMSSU</sub>   | Test Mode Select Setup Time | 0.53  | 0.63  | ns    |

| t <sub>TMDHD</sub>   | Test Mode Select Hold Time  | 1.07  | 1.25  | ns    |

| t <sub>TCK2Q</sub>   | Clock to Q (data out)       | 5.33  | 6.27  | ns    |

| t <sub>RSTB2Q</sub>  | Reset to Q (data out)       | 21.31 | 25.07 | ns    |

| F <sub>TCKMAX</sub>  | TCK Maximum Frequency       | 26.00 | 30.59 | MHz   |

| t <sub>TRSTREM</sub> | ResetB Removal Time         | 0.00  | 0.00  | ns    |

| t <sub>TRSTREC</sub> | ResetB Recovery Time        | 0.21  | 0.25  | ns    |

| t <sub>TRSTMPW</sub> | ResetB Minimum Pulse        | TBD   | TBD   | ns    |

Note: For specific junction temperature and voltage supply levels, refer to Table 2-7 on page 2-9 for derating values.

## Analog Bipolar Prescaler (ABPS)

With the ABPS set to its high range setting (GDEC = 00), a hypothetical input voltage in the range -15.36 V to +15.36 V is scaled and offset by the ABPS input amplifier to match the ADC full range of 0 V to 2.56 V using a nominal gain of -0.08333 V/V. However, due to reliability considerations, the voltage applied to the ABPS input should never be outside the range of -11.5 V to +14.4 V, restricting the usable ADC input voltage to 2.238 V to 0.080 V and the corresponding 12-bit output codes to the range of 3581 to 128 (decimal), respectively.

Unless otherwise noted, ABPS performance is specified at 25°C with nominal power supply voltages, with the output measured using the internal voltage reference with the internal ADC in 12-bit mode and 100 KHz sampling frequency, after trimming and digital compensation; and applies to all ranges.

| Specification                        | Test Conditions                            | Min.  | Тур.       | Max. | Units |

|--------------------------------------|--------------------------------------------|-------|------------|------|-------|

| Input voltage range (for driving ADC | GDEC[1:0] = 11                             |       | ±2.56      |      | V     |

| over its full range)                 | GDEC[1:0] = 10                             |       | ±5.12      |      | V     |

|                                      | GDEC[1:0] = 01                             |       | ±10.24     |      | V     |

|                                      | GDEC[1:0] = 00 (limited by maximum rating) |       | See note 1 |      | V     |

| Analog gain (from input pad to ADC   | GDEC[1:0] = 11                             |       | -0.5       |      | V/V   |

| input)                               | GDEC[1:0] = 10                             |       | -0.25      |      | V/V   |

|                                      | GDEC[1:0] = 01                             |       | -0.125     |      | V/V   |

|                                      | GDEC[1:0] = 00                             |       | -0.0833    |      | V/V   |

| Gain error                           |                                            | -2.8  | -0.4       | 0.7  | %     |

|                                      | –40°C to +100°C                            | -2.8  | -0.4       | 0.7  | %     |

|                                      | –55°C to +125°C                            | -4    | -0.4       | 4    | %     |

| Input referred offset voltage        |                                            |       |            |      |       |

|                                      | GDEC[1:0] = 11                             | -0.31 | -0.07      | 0.31 | % FS* |

|                                      | –55°C to +125°C                            | -1.7  |            | 1.7  | % FS* |

|                                      | GDEC[1:0] = 10                             | -0.34 | -0.07      | 0.34 | % FS* |

|                                      | –55°C to +125°C                            | -1.6  |            | 1.6  | % FS* |

|                                      | GDEC[1:0] = 01                             | -0.61 | -0.07      | 0.35 | % FS* |

|                                      | –55°C to +125°C                            | -1.6  |            | 1.6  | % FS* |

|                                      | GDEC[1:0] = 00                             | -0.39 | -0.07      | 0.35 | % FS* |

|                                      | –55°C to +125°C                            | -1.6  |            | 1.6  | % FS* |

| SINAD                                |                                            | 53    | 56         |      | dB    |

| Non-linearity                        | RMS deviation from BFSL                    |       |            | 0.5  | % FS* |

Note: \*FS is full-scale error, defined as the difference between the actual value that triggers the transition to full-scale and the ideal analog full-scale transition value. Full-scale error equals offset error plus gain error. Refer to the Analog-to-Digital Converter chapter of the SmartFusion Programmable Analog User's Guide for more information.

## **Microsemi**.

SmartFusion DC and Switching Characteristics

## Inter-Integrated Circuit (I<sup>2</sup>C) Characteristics

This section describes the DC and switching of the  $I^2C$  interface. Unless otherwise noted, all output characteristics given are for a 100 pF load on the pins. For timing parameter definitions, refer to Figure 2-48 on page 2-93.

#### Table 2-102 • I<sup>2</sup>C Characteristics

#### Military-Case Conditions: T<sub>J</sub> = 125°C, VDD = 1.425 V, –1 Speed Grade

| Parameter              | Definition                                                  | Condition                                    | Value                       | Unit        |

|------------------------|-------------------------------------------------------------|----------------------------------------------|-----------------------------|-------------|

| V <sub>IL</sub>        | Minimum input low voltage                                   | _                                            | SeeTable 2-37 on page 2-31  | -           |

|                        | Maximum input low voltage                                   | _                                            | See Table 2-37              | -           |

| V <sub>IH</sub>        | Minimum input high voltage                                  | -                                            | See Table 2-37              | -           |

|                        | Maximum input high voltage                                  | -                                            | See Table 2-37              | -           |

| V <sub>OL</sub>        | Maximum output voltage low                                  | I <sub>OL</sub> = 8 mA                       | See Table 2-37              | -           |

| IIL                    | Input current high                                          | _                                            | See Table 2-37              | _           |

| I <sub>IH</sub>        | Input current low                                           | _                                            | See Table 2-37              | _           |

| V <sub>hyst</sub>      | Hysteresis of Schmitt trigger inputs                        | _                                            | See Table 2-33 on page 2-30 | V           |

| T <sub>FALL</sub>      | Fall time <sup>2</sup>                                      | VIHmin to VILMax, C <sub>load</sub> = 400 pF | 15.0                        | ns          |

|                        |                                                             | VIHmin to VILMax, C <sub>load</sub> = 100 pF | 4.0                         | ns          |

| T <sub>RISE</sub>      | Rise time <sup>2</sup>                                      | VILMax to VIHmin, C <sub>load</sub> = 400pF  | 19.5                        | ns          |

|                        |                                                             | VILMax to VIHmin, C <sub>load</sub> = 100pF  | 5.2                         | ns          |

| Cin                    | Pin capacitance                                             | VIN = 0, f = 1.0 MHz                         | 8.0                         | pF          |

| R <sub>pull-up</sub>   | Output buffer maximum pull-<br>down Resistance <sup>1</sup> | -                                            | 50                          | Ω           |

| R <sub>pull-down</sub> | Output buffer maximum pull-up<br>Resistance <sup>1</sup>    | _                                            | 150                         | Ω           |

| D <sub>max</sub>       | Maximum data rate                                           | Fast mode                                    | 400                         | Kbps        |

| t <sub>LOW</sub>       | Low period of I2C_x_SCL <sup>3</sup>                        | _                                            | 1                           | pclk cycles |

| t <sub>HIGH</sub>      | High period of I2C_x_SCL <sup>3</sup>                       | _                                            | 1                           | pclk cycles |

| t <sub>HD;STA</sub>    | START hold time <sup>3</sup>                                | _                                            | 1                           | pclk cycles |

| t <sub>SU;STA</sub>    | START setup time <sup>3</sup>                               | _                                            | 1                           | pclk cycles |

| t <sub>HD;DAT</sub>    | DATA hold time <sup>3</sup>                                 | _                                            | 1                           | pclk cycles |

| t <sub>SU;DAT</sub>    | DATA setup time <sup>3</sup>                                | _                                            | 1                           | pclk cycles |

Notes:

<sup>1.</sup> These maximum values are provided for information only. Minimum output buffer resistance values depend on VCCxxxxIOBx, drive strength selection, temperature, and process. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/soc/download/ibis/default.aspx.

These values are provided for a load of 100 pF and 400 pF. For board design considerations and detailed output buffer resistances, use the corresponding IBIS models located on the SoC Products Group website at http://www.microsemi.com/soc/download/ibis/default.aspx.

<sup>3.</sup> For allowable Pclk configurations, refer to the Inter-Integrated Circuit (I<sup>2</sup>C) Peripherals section in the SmartFusion Microcontroller Subsystem User's Guide.

🌜 🤇 Microsemi.

## **3 – SmartFusion Development Tools**

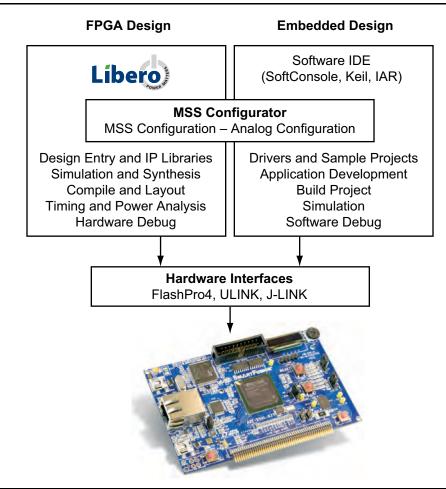

Designing with SmartFusion cSoCs involves three different types of design: FPGA design, embedded design and analog design. These roles can be filled by three different designers, two designers or even a single designer, depending on company structure and project complexity.

## **Types of Design Tools**

Microsemi has developed design tools and flows to meet the needs of these three types of designers so they can work together smoothly on a single project (Figure 3-1).

Figure 3-1 • Three Design Roles

## **FPGA** Design

Libero System-on-Chip (SoC) software is Microsemi's comprehensive software toolset for designing with all Microsemi FPGAs and cSoCs. Libero SoC includes industry-leading synthesis, simulation and debug tools from Synopsys<sup>®</sup> and Mentor Graphics<sup>®</sup>, as well as innovative timing and power optimization and analysis.

## **Special Function Pins**

| Name     | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC       |      |                   | No connect<br>This pin is not connected to circuitry within the device. These pins can<br>be driven to any voltage or can be left floating with no effect on the<br>operation of the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DC       |      |                   | Do not connect.<br>This pin should not be connected to any signals on the PCB. These<br>pins should be left unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| LPXIN    | In   | 1                 | Low power 32 KHz crystal oscillator.<br>Input from the 32 KHz oscillator. Pin for connecting a low power 32 KHz watch crystal. If not used, the LPXIN pin can be left floating. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .                                                                                                                                                                                                                                                                                      |

| LPXOUT   | In   | 1                 | Low power 32 KHz crystal oscillator.<br>Output to the 32 KHz oscillator. Pin for connecting a low power 32 KHz<br>watch crystal. If not used, the LPXOUT pin can be left floating. For<br>more information, see the PLLs, Clock Conditioning Circuitry, and On-<br>Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller</i><br><i>Subsystem User's Guide</i> .                                                                                                                                                                                                                                                                  |

| MAINXIN  | In   | 1                 | Main crystal oscillator circuit.<br>Input to the crystal oscillator circuit. Pin for connecting an external crystal, ceramic resonator, or RC network. When using an external crystal or ceramic oscillator, external capacitors are also recommended. Refer to documentation from the crystal oscillator manufacturer for proper capacitor value.<br>If using an external RC network or clock input, MAINXIN should be grounded for better noise immunity. For more information, see the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> .          |

| MAINXOUT | Out  | 1                 | Main crystal oscillator circuit.<br>Output from the crystal oscillator circuit. Pin for connecting external<br>crystal or ceramic resonator. When using an external crystal or ceramic<br>oscillator, external capacitors are also recommended. Refer to<br>documentation from the crystal oscillator manufacturer for proper<br>capacitor value.<br>If using external RC network or clock input, MAINXIN should be<br>grounded and MAINXOUT left unconnected. For more information, see<br>the PLLs, Clock Conditioning Circuitry, and On-Chip Crystal Oscillators<br>section in the <i>SmartFusion Microcontroller Subsystem User's Guide</i> . |

| NCAP     |      | 1                 | Negative capacitor connection.<br>This is the negative terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. Analog charge pump capacitors are not needed if none of the analog SCB features are used and none of the SDDs are used. In that case it should be left unconnected.                                                                                                                                                                                                                                                                                          |

Pin Descriptions

| Name        | Туре | Polarity/Bus Size | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------|------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCAP        |      | 1                 | Positive Capacitor connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             |      |                   | This is the positive terminal of the charge pump. A capacitor, with a 2.2 $\mu$ F recommended value, is required to connect between PCAP and NCAP. If this pin is not used, it must be left unconnected/floating. In this case, no capacitor is needed. Analog charge pump capacitors are not needed if none of the analog SCB features are used, and none of the SDDs are used.                                                                                                                                                                                                                                             |

| PTBASE      |      | 1                 | Pass transistor base connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             |      |                   | This is the control signal of the voltage regulator. This pin should be connected to the base of an external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PTEM        |      | 1                 | Pass transistor emitter connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |      |                   | This is the feedback input of the voltage regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |      |                   | This pin should be connected to the emitter of an external pass transistor used with the 1.5 V internal voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| MSS_RESET_N |      | Low               | Low Reset signal which can be used as an external reset and can also<br>be used as a system level reset under control of the Cortex-M3<br>processor. MSS_RESET_N is an output asserted low after power-on<br>reset. The direction of MSS_RESET_N changes during the execution<br>of the Microsemi System Boot when chip-level reset is enabled. The<br>Microsemi System Boot reconfigures MSS_RESET_N to become a<br>reset input signal when chip-level reset is enabled. It has an internal<br>pull-up so it can be left floating. In the current software, the<br>MSS_RESET_N is modeled as an external input signal only. |

| PU_N        | In   | Low               | Push-button is the connection for the external momentary switch used to turn on the 1.5 V voltage regulator and can be floating if not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|         | FG256                   |                              |  |  |

|---------|-------------------------|------------------------------|--|--|

| Pin No. | A2F060 Function         | A2F500 Function              |  |  |

| C2      | VCCPLL0                 | VCCPLL0                      |  |  |

| C3      | EMC_BYTEN[0]/IO02NDB0V0 | EMC_BYTEN[0]/GAC0/IO07NDB0V0 |  |  |

| C4      | VCCFPGAIOB0             | VCCFPGAIOB0                  |  |  |

| C5      | EMC_CS0_N/IO01NDB0V0    | EMC_CS0_N/GAB0/IO05NDB0V0    |  |  |

| C6      | EMC_CS1_N/IO01PDB0V0    | EMC_CS1_N/GAB1/IO05PDB0V0    |  |  |

| C7      | GND                     | GND                          |  |  |

| C8      | EMC_AB[8]/IO08NDB0V0    | EMC_AB[8]/IO13NDB0V0         |  |  |

| C9      | EMC_AB[11]/IO09PDB0V0   | EMC_AB[11]/IO11PDB0V0        |  |  |

| C10     | VCCFPGAIOB0             | VCCFPGAIOB0                  |  |  |

| C11     | EMC_AB[17]/IO12PDB0V0   | EMC_AB[17]/IO17PDB0V0        |  |  |

| C12     | EMC_AB[19]/IO13PDB0V0   | EMC_AB[19]/IO18PDB0V0        |  |  |

| C13     | GND                     | GND                          |  |  |

| C14     | GCC0/IO18NPB0V0         | GBA2/IO27PPB1V0              |  |  |

| C15     | GCB0/IO19NDB0V0         | GCA2/IO28PDB1V0              |  |  |

| C16     | GCB1/IO19PDB0V0         | IO28NDB1V0                   |  |  |

| D1      | VCCFPGAIOB5             | VCCFPGAIOB5                  |  |  |

| D2      | VCOMPLA0                | VCOMPLA0                     |  |  |

| D3      | GND                     | GND                          |  |  |

| D4      | GNDQ                    | GNDQ                         |  |  |

| D5      | EMC_CLK/IO00NDB0V0      | EMC_CLK/GAA0/IO02NDB0V0      |  |  |

| D6      | EMC_RW_N/IO00PDB0V0     | EMC_RW_N/GAA1/IO02PDB0V0     |  |  |

| D7      | EMC_AB[6]/IO07NDB0V0    | EMC_AB[6]/IO12NDB0V0         |  |  |

| D8      | EMC_AB[7]/IO07PDB0V0    | EMC_AB[7]/IO12PDB0V0         |  |  |

| D9      | EMC_AB[10]/IO09NDB0V0   | EMC_AB[10]/IO11NDB0V0        |  |  |

| D10     | EMC_AB[22]/IO15NDB0V0   | EMC_AB[22]/IO19NDB0V0        |  |  |

| D11     | EMC_AB[23]/IO15PDB0V0   | EMC_AB[23]/IO19PDB0V0        |  |  |

| D12     | GNDQ                    | GNDQ                         |  |  |

| D13     | GCC1/IO18PPB0V0         | GBB2/IO27NPB1V0              |  |  |

| D14     | GCA0/IO20NDB0V0         | GCB2/IO33PDB1V0              |  |  |

| D15     | GCA1/IO20PDB0V0         | IO33NDB1V0                   |  |  |

| D16     | VCCFPGAIOB1             | VCCFPGAIOB1                  |  |  |

| E1      | EMC_DB[13]/IO44PDB5V0   | EMC_DB[13]/GAC2/IO87PDB5V0   |  |  |

| E2      | EMC_DB[12]/IO44NDB5V0   | EMC_DB[12]/IO87NDB5V0        |  |  |

|         |                         |                              |  |  |

*Note:* Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

|         | FG256            |                  |  |  |

|---------|------------------|------------------|--|--|

| Pin No. | A2F060 Function  | A2F500 Function  |  |  |

| N7      | NC               | GND33ADC0        |  |  |

| N8      | VCC33ADC0        | VCC33ADC1        |  |  |

| N9      | ADC8 ADC5        |                  |  |  |

| N10     | CM0 CM3          |                  |  |  |

| N11     | GNDAQ            | GNDAQ            |  |  |

| N12     | VAREFOUT         | VAREFOUT         |  |  |

| N13     | NC               | GNDSDD1          |  |  |

| N14     | NC               | VCC33SDD1        |  |  |

| N15     | GND              | GND              |  |  |

| N16     | SPI_0_DO/GPIO_16 | SPI_0_DO/GPIO_16 |  |  |

| P1      | GNDSDD0          | GNDSDD0          |  |  |

| P2      | VCC33SDD0        | VCC33SDD0        |  |  |

| P3      | VCC33N           | VCC33N           |  |  |

| P4      | GNDA             | GNDA             |  |  |

| P5      | GNDAQ            | GNDAQ            |  |  |

| P6      | NC               | CM1              |  |  |

| P7      | NC               | ADC2             |  |  |

| P8      | NC               | VCC15ADC0        |  |  |

| P9      | ADC9             | ADC6             |  |  |

| P10     | TM0              | TM3              |  |  |

| P11     | GNDA             | GNDA             |  |  |

| P12     | VCCMAINXTAL      | VCCMAINXTAL      |  |  |

| P13     | GNDLPXTAL        | GNDLPXTAL        |  |  |

| P14     | VDDBAT           | VDDBAT           |  |  |

| P15     | PTEM             | PTEM             |  |  |

| P16     | PTBASE           | PTBASE           |  |  |

| R1      | PCAP             | PCAP             |  |  |

| R2      | SDD0             | SDD0             |  |  |

| R3      | ADC0             | ABPS0            |  |  |

| R4      | ADC3             | TM0              |  |  |

| R5      | NC               | ABPS2            |  |  |

| R6      | NC               | ADC1             |  |  |

| R7      | NC               | VCC33ADC0        |  |  |

*Note:* Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

|         | FG256           |                 |  |  |

|---------|-----------------|-----------------|--|--|

| Pin No. | A2F060 Function | A2F500 Function |  |  |

| R8      | VCC15ADC0       | VCC15ADC1       |  |  |

| R9      | ADC10           | ADC7            |  |  |

| R10     | ABPS1           | ABPS7           |  |  |

| R11     | NC              | ABPS4           |  |  |

| R12     | MAINXIN         | MAINXIN         |  |  |

| R13     | MAINXOUT        | MAINXOUT        |  |  |

| R14     | LPXIN           | LPXIN           |  |  |

| R15     | LPXOUT          | LPXOUT          |  |  |

| R16     | VCC33A          | VCC33A          |  |  |

| T1      | NCAP            | NCAP            |  |  |

| T2      | ADC1            | ABPS1           |  |  |

| T3      | ADC2            | CM0             |  |  |

| T4      | NC              | GNDTM0          |  |  |

| T5      | NC              | ADC0            |  |  |

| T6      | NC              | VAREF0          |  |  |

| T7      | NC              | GND33ADC0       |  |  |

| T8      | GND15ADC0       | GND15ADC1       |  |  |

| Т9      | VAREF0          | VAREF1          |  |  |

| T10     | ABPS0           | ABPS6           |  |  |

| T11     | NC              | ABPS5           |  |  |

| T12     | NC              | SDD1            |  |  |

| T13     | GNDVAREF        | GNDVAREF        |  |  |

| T14     | GNDMAINXTAL     | GNDMAINXTAL     |  |  |

| T15     | VCCLPXTAL       | VCCLPXTAL       |  |  |

| T16     | PU_N            | PU_N            |  |  |

*Note:* Shading denotes pins that do not have completely identical functions from density to density. For example, the bank assignment can be different for an I/O, or the function might be available only on a larger density device.

| FG484         |                       |               | FG484                 |  |  |

|---------------|-----------------------|---------------|-----------------------|--|--|

| Pin<br>Number | A2F500 Function       | Pin<br>Number | A2F500 Function       |  |  |

| R19           | NC                    | U12           | ADC4                  |  |  |

| R20           | NC                    | U13           | GNDTM2                |  |  |

| R21           | VCCFPGAIOB1           | U14           | ADC11                 |  |  |

| R22           | NC                    | U15           | GNDVAREF              |  |  |

| T1            | GND                   | U16           | VCC33SDD1             |  |  |

| T2            | VCCMSSIOB4            | U17           | SPI_0_DO/GPIO_16      |  |  |

| Т3            | GPIO_8/IO48RSB4V0     | U18           | UART_0_RXD/GPIO_21    |  |  |

| T4            | GPIO_11/IO66RSB4V0    | U19           | VCCMSSIOB2            |  |  |

| T5            | GND                   | U20           | I2C_1_SCL/GPIO_31     |  |  |

| T6            | MAC_CLK               | U21           | I2C_0_SCL/GPIO_23     |  |  |

| T7            | VCCMSSIOB4            | U22           | GND                   |  |  |

| Т8            | VCC33SDD0             | V1            | GPIO_0/IO56RSB4V0     |  |  |

| Т9            | VCC15A                | V2            | GPIO_6/IO50RSB4V0     |  |  |

| T10           | GNDAQ                 | V3            | GPIO_9/IO47RSB4V0     |  |  |

| T11           | GND33ADC0             | V4            | MAC_MDIO/IO58RSB4V0   |  |  |

| T12           | ADC7                  | V5            | MAC_RXD[0]/IO63RSB4V0 |  |  |

| T13           | TM4                   | V6            | GND                   |  |  |

| T14           | VAREF2                | V7            | SDD0                  |  |  |

| T15           | VAREFOUT              | V8            | ABPS1                 |  |  |

| T16           | VCCMSSIOB2            | V9            | ADC2                  |  |  |

| T17           | SPI_1_DO/GPIO_24      | V10           | VCC33ADC0             |  |  |

| T18           | GND                   | V11           | ADC6                  |  |  |

| T19           | NC                    | V12           | ADC5                  |  |  |

| T20           | NC                    | V13           | ABPS5                 |  |  |

| T21           | VCCMSSIOB2            | V14           | ADC8                  |  |  |

| T22           | GND                   | V15           | GND33ADC2             |  |  |

| U1            | GND                   | V16           | NC                    |  |  |

| U2            | GPIO_5/IO51RSB4V0     | V17           | GND                   |  |  |

| U3            | GPIO_10/IO67RSB4V0    | V18           | SPI_0_DI/GPIO_17      |  |  |

| U4            | VCCMSSIOB4            | V19           | SPI_1_DI/GPIO_25      |  |  |

| U5            | MAC_RXD[1]/IO62RSB4V0 | V20           | UART_1_TXD/GPIO_28    |  |  |

| U6            | NC                    | V21           | I2C_0_SDA/GPIO_22     |  |  |

| U7            | VCC33AP               | V22           | I2C_1_SDA/GPIO_30     |  |  |

| U8            | VCC33N                | W1            | GPIO_2/IO54RSB4V0     |  |  |

| U9            | CM1                   | W2            | GPIO_7/IO49RSB4V0     |  |  |

| U10           | VAREF0                | W3            | GND                   |  |  |

| U11           | GND33ADC1             | W4            | MAC_CRSDV/IO60RSB4V0  |  |  |

# 6 – Datasheet Information

## **List of Changes**

The following table lists critical changes that were made in each revision of the SmartFusion datasheet.

| Revision | Changes                                                                                                                                | Page |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|------|

|          | Updated information about unused MSS I/O configuration in "User I/O Naming Conventions" (SAR 62994).                                   | 5-6  |

|          | The status was changed from Preliminary to Production for A2F060 and A2F500 in the "SmartFusion cSoC Device Status" table (SAR 41135). | III  |