Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 50MHz                                                                               |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, LVD, POR, PWM, WDT                                          |

| Number of I/O              | 24                                                                                  |

| Program Memory Size        | 32KB (32K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 4K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                         |

| Data Converters            | A/D 5x12b                                                                           |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 32-WFQFN Exposed Pad                                                                |

| Supplier Device Package    |                                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/m058zan |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## NuMicro<sup>™</sup> M058/M0516 Data Sheet

## nuvoTon

#### LIST OF FIGURES

| Figure 3–1 NuMicro™ M051 Series Block Diagram                          | 11 |

|------------------------------------------------------------------------|----|

| Figure 4–1 NuMicro M051™ Naming Rule                                   | 12 |

| Figure 5-1 NuMicro™ M051 Series QFN33 Pin Diagram                      | 13 |

| Figure 5-2 NuMicro™ M051 Series LQFP-48 Pin Diagram                    | 14 |

| Figure 6-1 Functional Block Diagram                                    | 18 |

| Figure 6-2 NuMicro M051 <sup>™</sup> Series Power Architecture Diagram | 21 |

| Figure 6-3 Whole Chip Clock generator block diagram                    | 28 |

| Figure 6-4 Clock generator block diagram                               | 29 |

| Figure 6-5 System Clock Block Diagram                                  | 30 |

| Figure 6-6 SysTick clock Control Block Diagram                         | 30 |

| Figure 6-7 AHB Clock Source for HCLK                                   | 31 |

| Figure 6-8 Peripherals Clock Source Select for PCLK                    | 32 |

| Figure 6-9 Clock Source of Frequency Divider                           | 34 |

| Figure 6-10 Block Diagram of Frequency Divider                         | 34 |

| Figure 6-11 Push-Pull Output                                           | 35 |

| Figure 6-12 Open-Drain Output                                          | 36 |

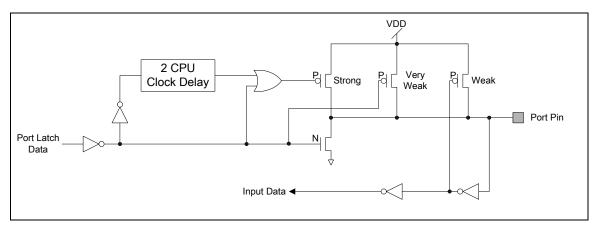

| Figure 6-13 Quasi-bidirectional I/O Mode                               | 36 |

| Figure 6-14 I <sup>2</sup> C Bus Timing                                | 37 |

| Figure 6-15 Timing of Interrupt and Reset Signal                       | 45 |

| Figure 8-1 Typical Crystal Application Circuit                         | 61 |

| Figure 8-2 SPI Master timing                                           | 67 |

| Figure 8-3 SPI Slave timing                                            | 67 |

## NuMicro<sup>™</sup> M058/M0516 Data Sheet

## nuvoTon

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin can be configured as interrupt source with edge/level setting

- Supports high driver and high sink IO mode

- Timer

- Provides four channel 32-bit timers, one 8-bit pre-scale counter with 24-bit up-timer for each timer.

- Independent clock source for each timer.

- 24-bit timer value is readable through TDR (Timer Data Register)

- Provides one-shot, periodic and toggle operation modes.

- Watchdog Timer

- Multiple clock sources

- Supports wake-up from power down or idle mode

- Interrupt or reset selectable on watchdog time-out

- PWM

- Built-in up to four 16-bit PWM generators; providing eight PWM outputs or four complementary paired PWM outputs

- Individual clock source, clock divider, 8-bit pre-scalar and dead-zone generator for each PWM generator

- PWM interrupt synchronized to PWM period

- 16-bit digital Capture timers (shared with PWM timers) with rising/falling capture inputs

- Supports capture interrupt

- UART

- Up to two sets of UART device

### **4 SELECTION TABLE**

NuMicro M051<sup>™</sup> Series Selection Guide

| <b>D</b> (1) | 10001 |     | Data  |       |     |          | Cor  | nectiv | /ity |     |          |     | ISP |         |

|--------------|-------|-----|-------|-------|-----|----------|------|--------|------|-----|----------|-----|-----|---------|

| Part No.     | APROM | RAM | Flash | LDROM | 1/0 | Timer    | UART | SPI    | I2C  | PWM | ADC      | EBI | ICP | Package |

| M058LAN      | 32KB  | 4KB | 4KB   | 4KB   | 40  | 4x32-bit | 2    | 2      | 1    | 8   | 8x12-bit | v   | v   | LQFP48  |

| M058ZAN      | 32KB  | 4KB | 4KB   | 4KB   | 24  | 4x32-bit | 2    | 1      | 1    | 5   | 5x12-bit |     | v   | QFN 33  |

| M0516LAN     | 64KB  | 4KB | 4KB   | 4KB   | 40  | 4x32-bit | 2    | 2      | 1    | 8   | 8x12-bit | v   | v   | LQFP48  |

| M0516ZAN     | 64KB  | 4KB | 4KB   | 4KB   | 24  | 4x32-bit | 2    | 1      | 1    | 5   | 5x12-bit |     | v   | QFN 33  |

Table 4–1 NuMicro™ M051 Series Product Selection Guide

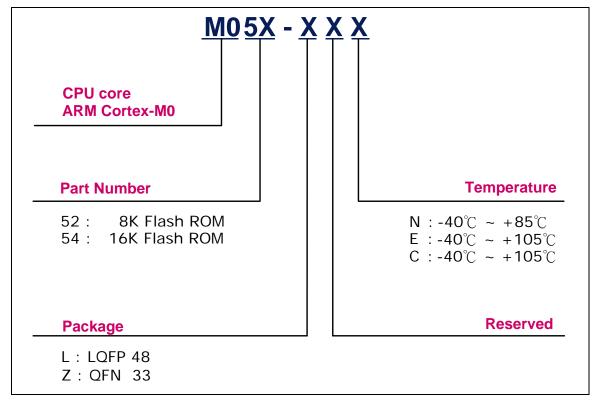

Figure 4–1 NuMicro M051™ Naming Rule

### **5 PIN CONFIGURATION**

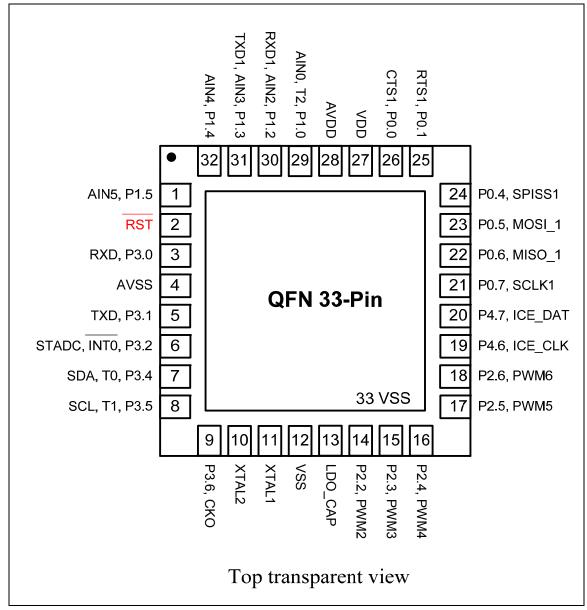

### 5.1 QFN 33 pin

nuvoTon

Figure 5-1 NuMicro™ M051 Series QFN33 Pin Diagram

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling.

- C Application Binary Interface compliant exception model. This is the ARMv6-M, C Application Binary Interface(C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers.

- Low power sleep mode entry using Wait For Interrupt (WFI), Wait For Event(WFE) instructions, or the return from interrupt sleep-on-exit feature.

#### **NVIC** features:

- 32 external interrupt inputs, each with four levels of priority.

- Dedicated non-Maskable Interrupt (NMI) input.

- Support for both level-sensitive and pulse-sensitive interrupt lines

- Wake-up Interrupt Controller (WIC), supports ultra-low power sleep mode.

#### Debug support:

- Four hardware breakpoints.

- Two watchpoints.

- Program Counter Sampling Register (PCSR) for non-intrusive code profiling.

- Single step and vector catch capabilities.

#### **Bus interfaces:**

- Single 32-bit AMBA-3 AHB-Lite system interface that provides simple integration to all system peripherals and memory.

- Single 32-bit slave port that supports the DAP (Debug Access Port).

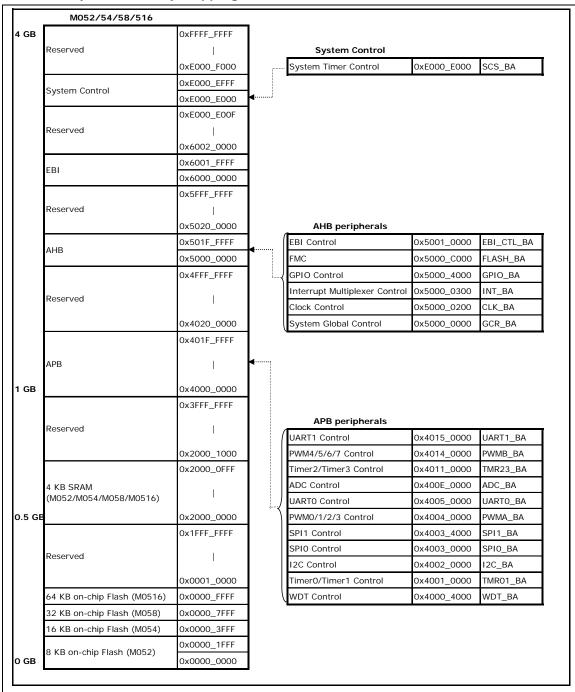

#### 6.2.4 Whole System Memory Map

NuMicro M051<sup>™</sup> series provides a 4G-byte address space. The memory locations assigned to each on-chip modules are shown in Table 6-1. The detailed register memory addressing and programming will be described in the following sections for individual on-chip peripherals. NuMicro M051<sup>™</sup> series only supports little-endian data format.

| Address Space                     | Token               | Modules                                           |  |  |  |  |  |

|-----------------------------------|---------------------|---------------------------------------------------|--|--|--|--|--|

| Flash and SRAM Memory Space       |                     |                                                   |  |  |  |  |  |

| 0x0000_0000 – 0x0000_FFFF         | FLASH_BA            | FLASH Memory Space (64KB)                         |  |  |  |  |  |

| 0x2000_0000 – 0x2000_0FFF         | SRAM_BA             | SRAM Memory Space (4KB)                           |  |  |  |  |  |

| AHB Modules Space (0x5000_0000    |                     |                                                   |  |  |  |  |  |

| 0x5000_0000 – 0x5000_01FF         | GCR_BA              | System Global Control Registers                   |  |  |  |  |  |

| 0x5000_0200 – 0x5000_02FF         | CLK_BA              | Clock Control Registers                           |  |  |  |  |  |

| 0x5000_0300 – 0x5000_03FF         | INT_BA              | Interrupt Multiplexer Control Registers           |  |  |  |  |  |

| 0x5000_4000 – 0x5000_7FFF         | GPIO_BA             | GPIO (P0~P4) Control Registers                    |  |  |  |  |  |

| 0x5000_C000 – 0x5000_FFFF         | FMC_BA              | Flash Memory Control Registers                    |  |  |  |  |  |

| 0x5001_0000 – 0x5001_3FFF         | EBI_CTL_BA          | EBI Control Registers (128KB)                     |  |  |  |  |  |

| EBI Space (0x6000_0000 ~ 0x6001_l | FFFF)               |                                                   |  |  |  |  |  |

| 0x6000_0000 – 0x6001_FFFF         | EBI_BA              | EBI Space                                         |  |  |  |  |  |

| APB Modules Space (0x4000_0000 ·  | -<br>~ 0x400F_FFFF) |                                                   |  |  |  |  |  |

| 0x4000_4000 – 0x4000_7FFF         | WDT_BA              | Watch-Dog Timer Control Registers                 |  |  |  |  |  |

| 0x4001_0000 – 0x4001_3FFF         | TMR01_BA            | Timer0/Timer1 Control Registers                   |  |  |  |  |  |

| 0x4002_0000 – 0x4002_3FFF         | I2C_BA              | I <sup>2</sup> C Interface Control Registers      |  |  |  |  |  |

| 0x4003_0000 – 0x4003_3FFF         | SPI0_BA             | SPI0 with master/slave function Control Registers |  |  |  |  |  |

| 0x4003_4000 – 0x4003_7FFF         | SPI1_BA             | SPI1 with master/slave function Control Registers |  |  |  |  |  |

| 0x4004_0000 – 0x4004_3FFF         | PWMA_BA             | PWM0/1/2/3 Control Registers                      |  |  |  |  |  |

| 0x4005_0000 – 0x4005_3FFF         | UART0_BA            | UART0 Control Registers                           |  |  |  |  |  |

Publication Release Date: May 30, 2011 Revision V2.00

| 0x400E_0000 – 0x400E_FFFF                        | ADC_BA            | Analog-Digital-Converter (ADC) Control Registers                                  |  |  |  |  |

|--------------------------------------------------|-------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| 0x4011_0000 – 0x4011_3FFF                        | TMR23_BA          | Timer2/Timer3 Control Registers                                                   |  |  |  |  |

| 0x4014_0000 – 0x4014_3FFF                        | PWMB_BA           | PWM4/5/6/7 Control Registers                                                      |  |  |  |  |

| 0x4015_0000 – 0x4015_3FFF                        | UART1_BA          | UART1 Control Registers                                                           |  |  |  |  |

| System Control Space (0xE000_E000 ~ 0xE000_EFFF) |                   |                                                                                   |  |  |  |  |

| System Control Space (0xE000_E00                 | 00 ~ 0xE000_EFFF) |                                                                                   |  |  |  |  |

| System Control Space (0xE000_E00                 | _ ,               | System Timer Control Registers                                                    |  |  |  |  |

|                                                  | SCS_BA            | System Timer Control Registers<br>External Interrupt Controller Control Registers |  |  |  |  |

Table 6-1 Address Space Assignments for On-Chip Modules

### 6.2.5 Whole System Memory Mapping Table

nuvoTon

NUVOTON

### 6.2.7 Nested Vectored Interrupt Controller (NVIC)

Cortex-M0 provides an interrupt controller as an integral part of the exception mode, named as "Nested Vectored Interrupt Controller (NVIC)". It is closely coupled to the processor kernel and provides following features:

- Nested and Vectored interrupt support

- Automatic processor state saving and restoration

- Dynamic priority changing

- Reduced and deterministic interrupt latency

The NVIC prioritizes and handles all supported exceptions. All exceptions are handled in "Handler Mode". This NVIC architecture supports 32 (IRQ[31:0]) discrete interrupts with 4 levels of priority. All of the interrupts and most of the system exceptions can be configured to different priority levels. When an interrupt occurs, the NVIC will compare the priority of the new interrupt to the current running one's priority. If the priority of the new interrupt is higher than the current one, the new interrupt handler will override the current handler.

When any interrupts is accepted, the starting address of the interrupt service routine (ISR) is fetched from a vector table in memory. There is no need to determine which interrupt is accepted and branch to the starting address of the correlated ISR by software. While the starting address is fetched, NVIC will also automatically save processor state including the registers "PC, PSR, LR, R0~R3, R12" to the stack. At the end of the ISR, the NVIC will restore the mentioned registers from stack and resume the normal execution. Thus it will take less and deterministic time to process the interrupt request.

The NVIC supports "Tail Chaining" which handles back-to-back interrupts efficiently without the overhead of states saving and restoration and therefore reduces delay time in switching to pending ISR at the end of current ISR. The NVIC also supports "Late Arrival" which improves the efficiency of concurrent ISRs. When a higher priority interrupt request occurs before the current ISR starts to execute (at the stage of state saving and starting address fetching), the NVIC will give priority to the higher one without delay penalty. Thus it advances the real-time capability.

For more detailed information, please refer to the documents "ARM<sup>®</sup> Cortex™-M0 Technical Reference Manual" and "ARM<sup>®</sup> v6-M Architecture Reference Manual".

# ηυνοΤοη

### 6.3 Clock Controller

#### 6.3.1 Overview

The clock controller generates the clocks for the whole chip, including system clocks and all peripheral clocks. The clock controller also implements the power control function with the individually clock ON/OFF control, clock source selection and clock divider. The chip will not enter power down mode until CPU sets the power down enable bit (PWR\_DOWN\_EN) and Cortex-M0 core executes the WFI instruction. After that, chip enters power down mode and wait for wake-up interrupt source triggered to leave power down mode. In the power down mode, the clock controller turns off the external 4~24 MHz high speed crystal and internal 22.1184 MHz high speed oscillator to reduce the overall system power consumption.

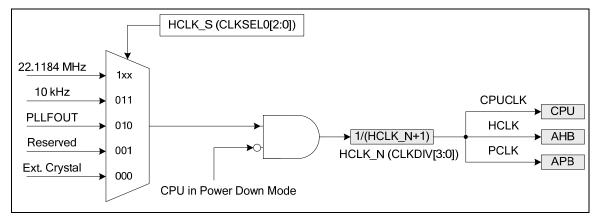

#### 6.3.2 Clock Generator Block Diagram

The clock generator consists of 4 sources which list below:

- One external 4~24 MHz high speed crystal

- One internal 22.1184 MHz high speed oscillator

- One programmable PLL FOUT(PLL source consists of external 4~24 MHz high speed crystal and internal 22.1184 MHz high speed oscillator)

- One internal 10 kHz low speed oscillator

#### 6.3.3 System Clock and SysTick Clock

nuvoton

The system clock has 4 clock sources which were generated from clock generator block. The clock source switch depends on the register HCLK\_S(CLKSEL0[2:0]). The block diagram is shown in the Figure 6-5.

Figure 6-5 System Clock Block Diagram

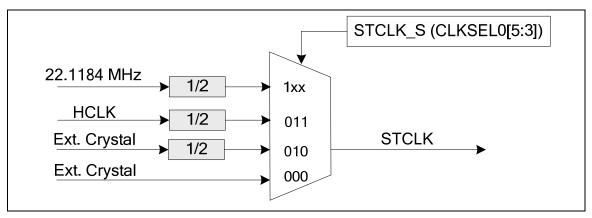

The clock source of SysTick in Cortex-M0 core can use CPU clock or external clock (SYST\_CSR[2]). If using external clock, the SysTick clock (STCLK) has 4 clock sources. The clock source switch depends on the setting of the register STCLK\_S (CLKSEL0[5:3]. The block diagram is shown in the Figure 6-6.

Figure 6-6 SysTick clock Control Block Diagram

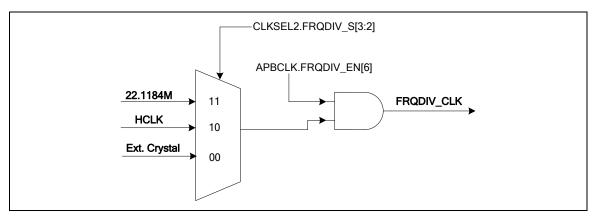

### 6.3.7 Frequency Divider Output

nuvoTon

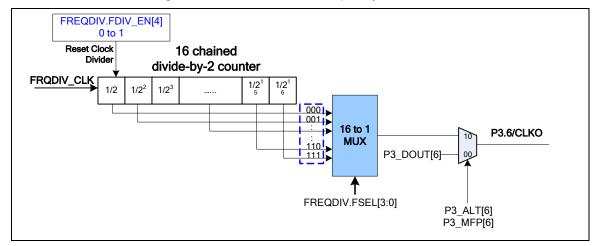

This device is equipped a power-of-2 frequency divider which is composed by16 chained divideby-2 shift registers. One of the 16 shift register outputs selected by a sixteen to one multiplexer is reflected to P3.6. Therefore there are 16 options of power-of-2 divided clocks with the frequency from  $F_{in}/2^{1}$  to  $F_{in}/2^{17}$  where Fin is input clock frequency to the clock divider.

The output formula is  $F_{out} = F_{in}/2^{(N+1)}$ , where  $F_{in}$  is the input clock frequency,  $F_{out}$  is the clock divider output frequency and N is the 4-bit value in FREQDIV.FSEL[3:0].

When write 1 to DIVIDER\_EN (FRQDIV[4]), the chained counter starts to count. When write 0 to DIVIDER\_EN (FRQDIV[4]), the chained counter continuously runs till divided clock reaches low state and stay in low state.

Figure 6-9 Clock Source of Frequency Divider

Figure 6-10 Block Diagram of Frequency Divider

Publication Release Date: May 30, 2011 Revision V2.00

#### 6.4.1.3 Open-Drain Mode Explanation

NUVOTON

Set Px\_PMD(PMDn[1:0]) to 10b the Px[n] pin is in Open-Drain mode and the I/O pin supports digital output function but only with sink current capability, an additional pull-up resister is needed for driving high state. If the bit value in the corresponding bit [n] of Px\_DOUT is "0", the pin drive a "low" output on the pin. If the bit value in the corresponding bit [n] of Px\_DOUT is "1", the pin output drives high that is controlled by the internal pull-up resistor or the external pull high resistor.

Figure 6-12 Open-Drain Output

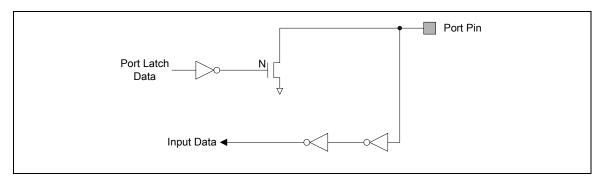

#### 6.4.1.4 Quasi-bidirectional Mode Explanation

Set Px\_PMD(PMDn[1:0]) to 11b the Px[n] pin is in Quasi-bidirectional mode and the I/O pin supports digital output and input function at the same time but the source current is only up to hundreds uA. Before the digital input function is performed the corresponding bit in Px\_DOUT must be set to 1. The quasi-bidirectional output is common on the 80C51 and most of its derivatives. If the bit value in the corresponding bit [n] of Px\_DOUT is "0", the pin drive a "low" output on the pin. If the bit value in the corresponding bit [n] of Px\_DOUT is "1", the pin will check the pin value. If pin value is high, no action takes. If pin state is low, then pin will drive strong high with 2 clock cycles on the pin and then disable the strong output drive and then the pin status is control by internal pull-up resistor. Note that the source current capability in quasi-bidirectional mode is only about 200uA to 30uA for VDD is form 5.0V to 2.5V

Publication Release Date: May 30, 2011 Revision V2.00

## 6.8 Timer Controller

#### 6.8.1 Overview

nuvoTon

The timer controller includes four 32-bit timers, TIMER0~TIMER3, which allows user to easily implement a timer control for applications. The timer can perform functions like frequency measurement, interval measurement, clock generation, delay timing, and so on. The timer can generates an interrupt signal upon timeout, or provide the current value of count during operation.

#### 6.8.2 Features

- 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit pre-scale counter

- Independent clock source for each timer.

- 24-bit timer value is readable through TDR (Timer Data Register)

- Provides one-shot, periodic, toggle and continuous counting operation modes.

- Time out period = (Period of timer clock input) \* (8-bit pre-scale counter + 1) \* (24-bit TCMP)

- Maximum counting cycle time = (1 / T MHz) \* (2^8) \* (2^24), T is the period of timer clock

control provided by RTS pin or can program GPIO (P0.3 for RTS0 and P0.1 for RTS 1) to implement the function by software. The RS-485 mode is selected by setting the UA\_FUN\_SEL register to select RS-485 function. The RS-485 driver control is implemented using the RTS control signal from an asynchronous serial port to enable the RS-485 driver. In RS-485 mode, many characteristics of the RX and TX are same as UART.

#### 6.10.2 Features

- Full duplex, asynchronous communications

- Separate receive / transmit 15 bytes (UART0/UART1) entry FIFO for data payloads

- Support hardware auto flow control/flow control function (CTS, RTS) and programmable RTS flow control trigger level (UART0 and UART1 support)

- Programmable receiver buffer trigger level

- Support programmable baud-rate generator for each channel individually

- Support CTS wake up function (UART0 and UART1 support)

- Support 7 bit receiver buffer time out detection function

- Programmable transmitting data delay time between the last stop and the next start bit by setting UA\_TOR [DLY] register

- Support break error, frame error, and parity error detect function

- Fully programmable serial-interface characteristics

- Programmable number of data bit, 5, 6, 7, 8 bit character

- Programmable parity bit, even, odd, no parity or stick parity bit generation and detection

- Programmable stop bit, 1, 1.5, or 2 stop bit generation

- Support IrDA SIR function mode

- Support for 3/16 bit duration for normal mode

- Support RS-485 function mode.

- Support RS-485 9bit mode

- Support hardware or software direct enable control provided by RTS pin

### 6.13 Flash Memory Controller (FMC)

#### 6.13.1 Overview

NuMicro M051<sup>™</sup> series equips with 64K/32K/16K/8K bytes on chip embedded Flash for application program memory (APROM) that can be updated through ISP/IAP procedure. In System Programming (ISP) function enables user to update program memory when chip is soldered on PCB. After chip power on Cortex-M0 CPU fetches code from APROM or LDROM decided by boot select (CBS) in Config0. By the way, NuMicro M051<sup>™</sup> series also provide additional 4K bytes DATA Flash for user to store some application depended data before chip power off in 64/32/16/8K bytes APROM model.

#### 6.13.2 Features

- Run up to 50 MHz with zero wait state for continuous address read access

- 64/32/16/8KB application program memory (APROM)

- 4KB in system programming (ISP) loader program memory (LDROM)

- Fixed 4KB data flash with 512 bytes page erase unit

- In System Program (ISP)/In Application Program (IAP) to update on chip Flash

- In Circuit Program (ICP) via serial wire debug interface (SWD)

### 8 ELECTRICAL CHARACTERISTICS

### 8.1 Absolute Maximum Ratings

nuvoton

| SYMBOL                                       | PARAMETER           | MIN     | MAX     | UNIT |

|----------------------------------------------|---------------------|---------|---------|------|

| DC Power Supply                              | VDD-VSS             | -0.3    | +7.0    | V    |

| Input Voltage                                | VIN                 | VSS-0.3 | VDD+0.3 | V    |

| Oscillator Frequency                         | 1/t <sub>CLCL</sub> | 0       | 40      | MHz  |

| Operating Temperature                        | ТА                  | -40     | +85     | °C   |

| Storage Temperature                          | TST                 | -55     | +150    | °C   |

| Maximum Current into V <sub>DD</sub>         |                     | -       | 120     | mA   |

| Maximum Current out of V <sub>SS</sub>       |                     |         | 120     | mA   |

| Maximum Current sunk by a I/O pin            |                     |         | 35      | mA   |

| Maximum Current sourced by a I/O pin         |                     |         | 35      | mA   |

| Maximum Current sunk by total I/O pins       |                     |         | 100     | mA   |

| Maximum Current sourced by total<br>I/O pins |                     |         | 100     | mA   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the lift and reliability of the device.

| PARAMETER                                                  | CONDITION                                  | MIN. | TYP.    | MAX. | UNIT |

|------------------------------------------------------------|--------------------------------------------|------|---------|------|------|

| Supply voltage <sup>[1]</sup>                              | -                                          | 2.5  | -       | 5.5  | V    |

| Center Frequency                                           | -                                          | -    | 22.1184 |      | MHz  |

| Colibrate d Internal Occillator                            | +25 C; V <sub>DD</sub> =5V                 | -1   | -       | +1   | %    |

| Calibrated Internal Oscillator<br>Frequency                | -40 C~+85 C;<br>V <sub>DD</sub> =2.5V~5.5V | -3   | -       | +3   | %    |

| Accuracy of Un-calibrated<br>Internal Oscillator Frequency | -40 C~+85 C;<br>V <sub>DD</sub> =2.5V~5.5V | -25  | -       | +25  | %    |

| Operating current                                          | V <sub>DD</sub> =5V                        | -    | 500     | -    | uA   |

### 8.3.4 Internal 22.1184 MHz High Speed Oscillator

#### 8.3.5 Internal 10 kHz Low Speed Oscillator

| PARAMETER                                   | CONDITION                                  | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------------|--------------------------------------------|------|------|------|------|

| Supply voltage <sup>[1]</sup>               | -                                          | 2.5  | -    | 5.5  | V    |

| Center Frequency                            | -                                          | -    | 10   | -    | kHz  |

| Calibrated Internal Oscillator<br>Frequency | +25 C; V <sub>DD</sub> =5V                 | -30  | -    | +30  | %    |

|                                             | -40 C~+85 C;<br>V <sub>DD</sub> =2.5V~5.5V | -50  | -    | +50  | %    |

| Operating current                           | V <sub>DD</sub> =5V                        | -    | 5    | -    | uA   |

Notes:

1. Internal operation voltage comes form LDO.

### **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice. All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.