#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                              |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | H8SX                                                                             |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 50MHz                                                                            |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SCI, SmartCard, USB                             |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 92                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 56K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 8x10b; D/A 2x8b                                                              |

| Oscillator Type            | External                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LFQFP (20x20)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f61668rd50fpv |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         | 17.3.3    | EXCKSN=0 Operation                                            |     |

|---------|-----------|---------------------------------------------------------------|-----|

| 17.4    | Interrupt | Source                                                        |     |

| 17.5    | Usage N   | otes                                                          |     |

|         | 17.5.1    | Changing Values of Bits EXCKSN, CKS1, and CKS0                |     |

|         | 17.5.2    | Note on Register Initialization                               |     |

|         | 17.5.3    | Usage Notes on 32K Timer                                      | 854 |

| Section | on 18 V   | Vatchdog Timer (WDT)                                          | 855 |

| 18.1    |           |                                                               |     |

| 18.2    |           | itput Pin                                                     |     |

| 18.3    | -         | Descriptions                                                  |     |

| 10.5    | 18.3.1    | Timer Counter (TCNT)                                          |     |

|         | 18.3.2    | Timer Control/Status Register (TCSR)                          |     |

|         | 18.3.3    | Reset Control/Status Register (RSTCSR)                        |     |

| 18.4    |           | n                                                             |     |

| 10.1    | 18.4.1    | Watchdog Timer Mode                                           |     |

|         | 18.4.2    | Interval Timer Mode                                           |     |

| 18.5    |           | Source                                                        |     |

| 18.6    | -         | otes                                                          |     |

| 10.0    | 18.6.1    | Notes on Register Access                                      |     |

|         | 18.6.2    | Conflict between Timer Counter (TCNT) Write and Increment     |     |

|         | 18.6.3    | Changing Values of Bits CKS2 to CKS0                          |     |

|         | 18.6.4    | Switching between Watchdog Timer Mode and Interval Timer Mode |     |

|         | 18.6.5    | Internal Reset in Watchdog Timer Mode                         |     |

|         | 18.6.6    | System Reset by $\overline{WDTOVF}$ Signal                    |     |

|         | 18.6.7    | Transition to Watchdog Timer Mode or Software Standby Mode    |     |

|         | 10.0.7    | Transition to watchabg Timer Mode of Software Standby Mode    |     |

| Section | on 19 S   | Serial Communication Interface (SCI, IrDA, CRC)               | 867 |

| 19.1    | Features  |                                                               |     |

| 19.2    | Input/Ou  | tput Pins                                                     |     |

| 19.3    | Register  | Descriptions                                                  |     |

|         | 19.3.1    | Receive Shift Register (RSR)                                  |     |

|         | 19.3.2    | Receive Data Register (RDR)                                   |     |

|         | 19.3.3    | Transmit Data Register (TDR)                                  |     |

|         | 19.3.4    | Transmit Shift Register (TSR)                                 |     |

|         | 19.3.5    | Serial Mode Register (SMR)                                    |     |

|         | 19.3.6    | Serial Control Register (SCR)                                 |     |

|         | 19.3.7    | Serial Status Register (SSR)                                  |     |

|         | 19.3.8    | Smart Card Mode Register (SCMR)                               |     |

|         | 19.3.9    | Bit Rate Register (BRR)                                       | 895 |

|         |           |                                                               |     |

| Function      |           | H8SX/1668R Group | H8SX/1668M Group |

|---------------|-----------|------------------|------------------|

| DMAC          |           | 0                | 0                |

| DTC           |           | 0                | 0                |

| PPG           |           | 0                | 0                |

| UBC           |           | 0                | 0                |

| SCI           |           | 0                | 0                |

| IIC2          |           | 0                | 0                |

| TMR           |           | 0                | 0                |

| WDT           |           | 0                | 0                |

| 10-bit ADC    |           | 0                | 0                |

| 8-bit DAC     |           | 0                | 0                |

| EXDMAC        |           | 0                | 0                |

| SDRAM interfa | ice       | 0                | 0                |

| 32K timer     |           | 0                | 0                |

| POR/LVD       |           | —                | 0                |

| Package       | LQFP-144  | 0                | 0                |

|               | LFBGA-176 | 0                | 0                |

| Table 1.2 | Comparison of Support Functions in the H8SX/1668R Group and H8SX/1668M |

|-----------|------------------------------------------------------------------------|

|           | Group                                                                  |

# 2.7.1 Instructions and Addressing Modes

Table 2.2 indicates the combinations of instructions and addressing modes that the H8SX CPU can use.

#### Table 2.2 Combinations of Instructions and Addressing Modes (1)

|                     |                    |       |     |     |      | Add      | ressing l | Mode                                |       |                   |      |

|---------------------|--------------------|-------|-----|-----|------|----------|-----------|-------------------------------------|-------|-------------------|------|

| Classifi-<br>cation | Instruction        | Size  | #xx | Rn  | @ERn | @(d,ERn) | Rn.W/     | @-ERn/<br>@ERn+/<br>@ERn-/<br>@+ERn | @aa:8 | @aa:16/<br>@aa:32 | _    |

| Data                | MOV                | B/W/L | S   | SD  | SD   | SD       | SD        | SD                                  |       | SD                |      |

| transfer            |                    | В     |     | S/D |      |          |           |                                     | S/D   |                   |      |

|                     | MOVFPE,<br>MOVTPE  | В     |     | S/D |      |          |           |                                     |       | S/D*1             |      |

|                     | POP, PUSH          | W/L   |     | S/D |      |          |           | S/D*2                               |       |                   |      |

|                     | LDM, STM           | L     |     | S/D |      |          |           | S/D*2                               |       |                   |      |

|                     | MOVA* <sup>4</sup> | B/W   |     | S   | S    | S        | S         | S                                   |       | S                 |      |

| Block               | EEPMOV             | В     |     |     |      |          |           |                                     |       |                   | SD*3 |

| transfer            | MOVMD              | B/W/L |     |     |      |          |           |                                     |       |                   | SD*3 |

|                     | MOVSD              | В     |     |     |      |          |           |                                     |       |                   | SD*3 |

| Arithmetic          | ADD, CMP           | В     | S   | D   | D    | D        | D         | D                                   | D     | D                 |      |

| operations          |                    | В     |     | S   | D    | D        | D         | D                                   | D     | D                 |      |

|                     |                    | В     |     | D   | S    | S        | S         | S                                   | S     | S                 |      |

|                     |                    | В     |     |     | SD   | SD       | SD        | SD                                  |       | SD                |      |

|                     |                    | W/L   | S   | SD  | SD   | SD       | SD        | SD                                  |       | SD                |      |

|                     | SUB                | В     | S   |     | D    | D        | D         | D                                   | D     | D                 |      |

|                     |                    | В     |     | S   | D    | D        | D         | D                                   | D     | D                 |      |

|                     |                    | В     |     | D   | S    | S        | S         | S                                   | S     | S                 |      |

|                     |                    | В     |     |     | SD   | SD       | SD        | SD                                  |       | SD                |      |

|                     |                    | W/L   | S   | SD  | SD   | SD       | SD        | SD                                  |       | SD                |      |

|                     | ADDX, SUBX         | B/W/L | S   | SD  |      |          |           |                                     |       |                   |      |

|                     |                    | B/W/L | S   |     | SD   |          |           |                                     |       |                   |      |

|                     |                    | B/W/L | S   |     |      |          |           | SD*⁵                                |       |                   |      |

|                     | INC, DEC           | B/W/L |     | D   |      |          |           |                                     |       |                   |      |

|                     | ADDS, SUBS         | L     |     | D   |      |          |           |                                     |       |                   |      |

|                     | DAA, DAS           | В     |     | D   |      |          |           |                                     |       |                   |      |

|                     | MULXU,<br>DIVXU    | B/W   | S:4 | SD  |      |          |           |                                     |       |                   | _    |

|                     | MULU, DIVU         | W/L   | S:4 | SD  |      |          |           |                                     |       |                   |      |

|                     |                    |       |     |    |      | Add      | dressing                          | Mode             |       |                   |   |

|---------------------|--------------------|-------|-----|----|------|----------|-----------------------------------|------------------|-------|-------------------|---|

| Classifi-<br>cation | Instruction        | Size  | #xx | Rn | @ERn | @(d,ERn) | @(d,<br>RnL.B/<br>Rn.W/<br>ERn.L) | @ERn-/           | @aa:8 | @aa:16/<br>@aa:32 | _ |

| Bit                 | BFLD               | В     |     | D  | S    |          |                                   |                  | S     | S                 |   |

| manipu-<br>lation   | BFST               | В     |     | S  | D    |          |                                   |                  | D     | D                 |   |

| Branch              | BRA/BS, BRA/BC*8   | В     |     |    | S    |          |                                   |                  | S     | S                 |   |

|                     | BSR/BS, BSR/BC*8   | В     |     |    | S    |          |                                   |                  | S     | S                 |   |

| System control      | LDC<br>(CCR, EXR)  | B/W*9 | S   | S  | S    | S        |                                   | S* <sup>10</sup> |       | S                 |   |

|                     | LDC<br>(VBR, SBR)  | L     |     | S  |      |          |                                   |                  |       |                   |   |

|                     | STC<br>(CCR, EXR)  | B/W*9 |     | D  | D    | D        |                                   | D* <sup>11</sup> |       | D                 |   |

|                     | STC<br>(VBR, SBR)  | L     |     | D  |      |          |                                   |                  |       |                   |   |

|                     | ANDC, ORC,<br>XORC | В     | S   |    |      |          |                                   |                  |       |                   |   |

|                     | SLEEP              | _     |     |    |      |          |                                   |                  |       |                   | 0 |

|                     | NOP                | _     |     |    |      |          |                                   |                  |       |                   | 0 |

[Legend]

- d: d:16 or d:32

- S: Can be specified as a source operand.

- D: Can be specified as a destination operand.

- SD: Can be specified as either a source or destination operand or both.

- S/D: Can be specified as either a source or destination operand.

- S:4: 4-bit immediate data can be specified as a source operand.

- Notes: 1. Only @aa:16 is available.

- 2. @ERn+ as a source operand and @-ERn as a destination operand

- 3. Specified by ER5 as a source address and ER6 as a destination address for data transfer.

- 4. Size of data to be added with a displacement

- 5. Only @ERn- is available

- 6. When the number of bits to be shifted is 1, 2, 4, 8, or 16

- 7. When the number of bits to be shifted is specified by 5-bit immediate data or a general register

- 8. Size of data to specify a branch condition

- 9. Byte when immediate or register direct, otherwise, word

- 10. Only @ERn+ is available

- 11. Only @-ERn is available

- 12. Only when the multiplier is available.

# 4.3 **Register Descriptions**

This LSI has the following registers for resets.

- Reset status register (RSTSR)

- Reset control/status register (RSTCSR)

#### 4.3.1 Reset Status Register (RSTSR)

RSTSR indicates a source for generating an internal reset and voltage monitoring interrupt.

| Bit            | 7       | 6 | 5 | 4 | 3 | 2      | 1    | 0      |

|----------------|---------|---|---|---|---|--------|------|--------|

| Bit name       | DPSRSTF | _ | _ | — | _ | LVDF*2 | _    | PORF*2 |

| Initial value: | 0       | 0 | 0 | 0 | 0 | 0.02   | 0.02 | 0.42   |

| initial ratio  | 0       | 0 | 0 | 0 | 0 | 0*3    | 0*3  | 0*3    |

Notes: 1. Only 0 can be written to clear the flag.

2. Supported only by the H8SX/1668M Group.

3. Initial value is undefined in the H8SX/1668M Group.

4. Only 0 can be written to clear the flag in the H8SX/1668M Group.

5. Only read is possible in the H8SX/1668M Group.

| Bit    | Bit Name | Initial<br>Value | R/W                 | Description                                                                                                                                             |

|--------|----------|------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | DPSRSTF  | 0                | R/(W)* <sup>1</sup> | Deep Software Standby Reset Flag                                                                                                                        |

|        |          |                  |                     | Indicates that deep software standby mode is canceled<br>by an interrupt source specified with DPSIER or<br>DPSIEGR and an internal reset is generated. |

|        |          |                  |                     | [Setting condition]                                                                                                                                     |

|        |          |                  |                     | When deep software standby mode is canceled by an interrupt source.                                                                                     |

|        |          |                  |                     | [Clearing conditions]                                                                                                                                   |

|        |          |                  |                     | • When this bit is read as 1 and then written by 0.                                                                                                     |

|        |          |                  |                     | <ul> <li>When a pin reset, power-on reset*<sup>2</sup> or voltage-<br/>monitoring reset*<sup>2</sup> is generated.</li> </ul>                           |

| 6 to 3 | _        | All 0            | R/W                 | Reserved                                                                                                                                                |

|        |          |                  |                     | These bits are always read as 0. The write value should always be 0.                                                                                    |

When an address error occurs, the following is performed to halt the DTC, DMAC, and EXDMAC.

- The ERR bit of DTCCR in the DTC is set to 1.

- The ERRF bit of DMDR\_0 in the DMAC is set to 1.

- The ERRF bit of EDMDR\_0 in the EXDMAC is set to 1.

- The DTE bits of DMDRs for all channels in the DMAC are cleared to 0 to forcibly terminate transfer.

- The DTE bits of EDMDRs for all channels in the EXDMAC are cleared to 0 to forcibly terminate transfer.

Table 6.6 shows the state of CCR and EXR after execution of the address error exception handling.

#### Table 6.6 Status of CCR and EXR after Address Error Exception Handling

|                        |   | CCR | EXR |          |  |

|------------------------|---|-----|-----|----------|--|

| Interrupt Control Mode | I | UI  | т   | l2 to l0 |  |

| 0                      | 1 |     |     | —        |  |

| 2                      | 1 |     | 0   | 7        |  |

[Legend]

1: Set to 1

0: Cleared to 0

--: Retains the previous value.

#### Wait Control Registers A and B (WTCRA, WTCRB) 9.2.3

WTCRA and WTCRB select the number of program wait cycles for each area in the external address space.

| • WTCRA       |    |     |     |     |    |     |     |     |

|---------------|----|-----|-----|-----|----|-----|-----|-----|

| Bit           | 15 | 14  | 13  | 12  | 11 | 10  | 9   | 8   |

| Bit Name      | _  | W72 | W71 | W70 |    | W62 | W61 | W60 |

| Initial Value | 0  | 1   | 1   | 1   | 0  | 1   | 1   | 1   |

| R/W           | R  | R/W | R/W | R/W | R  | R/W | R/W | R/W |

| Bit           | 7  | 6   | 5   | 4   | 3  | 2   | 1   | 0   |

| Bit Name      | _  | W52 | W51 | W50 |    | W42 | W41 | W40 |

| Initial Value | 0  | 1   | 1   | 1   | 0  | 1   | 1   | 1   |

| R/W           | R  | R/W | R/W | R/W | R  | R/W | R/W | R/W |

| • WTCRB       |    |     |     |     |    |     |     |     |

| Bit           | 15 | 14  | 13  | 12  | 11 | 10  | 9   | 8   |

| Bit Name      | —  | W32 | W31 | W30 | —  | W22 | W21 | W20 |

| Initial Value | 0  | 1   | 1   | 1   | 0  | 1   | 1   | 1   |

| R/W           | R  | R/W | R/W | R/W | R  | R/W | R/W | R/W |

| Bit           | 7  | 6   | 5   | 4   | 3  | 2   | 1   | 0   |

| Bit Name      | —  | W12 | W11 | W10 | —  | W02 | W01 | W00 |

| Initial Value | 0  | 1   | 1   | 1   | 0  | 1   | 1   | 1   |

| R/W           | R  | R/W | R/W | R/W | R  | R/W | R/W | R/W |

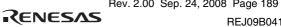

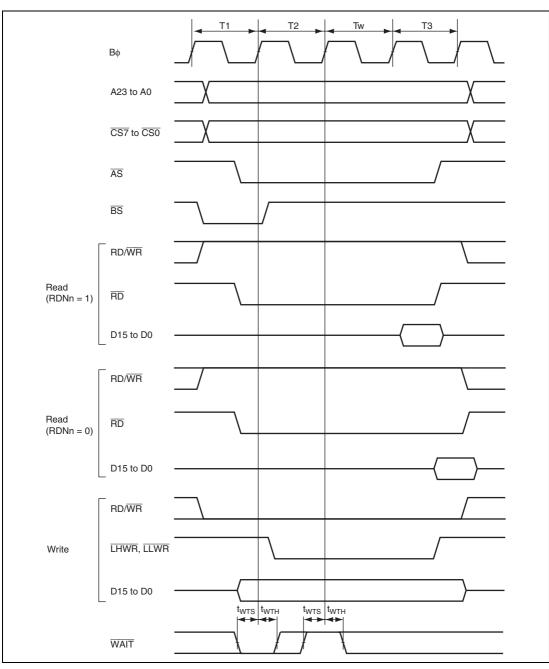

Figure 9.20 16-Bit 3-State Access Space Bus Timing (Word Access for Even Address)

#### 9.8.4 Basic Timing

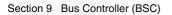

The number of access cycles in the initial cycle (full access) on the burst ROM interface is determined by the basic bus interface settings in ABWCR, ASTCR, WTCRA, WTCRB, and bits CSXHn in CSACR (n = 0 to 7). When area 0 or area 1 designated as burst ROM space is read by the CPU or EXDMAC cluster transfer, the settings in RDNCR and bits CSXTn in CSACR (n = 0 to 7) are ignored.

From one to eight cycles can be selected for the burst cycle, according to the settings of bits BSTS02 to BSTS00 and BSTS12 to BSTS10 in BROMCR. Wait cycles cannot be inserted. In addition, 4-word, 8-word, 16-word, or 32-word consecutive burst access can be performed according to the settings of BSTS01, BSTS00, BSTS11, and BSTS10 bits in BROMCR.

The basic access timing for burst ROM space is shown in figures 9.29 and 9.30.

Figure 9.29 Example of Burst ROM Access Timing (ASTn = 1, Two Burst Cycles)

#### • DMDR\_1 to DMDR\_3

| Bit           | 31    | 30    | 29    | 28   | 27    | 26    | 25     | 24     |

|---------------|-------|-------|-------|------|-------|-------|--------|--------|

| Bit Name      | DTE   | DACKE | TENDE | _    | DREQS | NRD   | _      | —      |

| Initial Value | 0     | 0     | 0     | 0    | 0     | 0     | 0      | 0      |

| R/W           | R/W   | R/W   | R/W   | R/W  | R/W   | R/W   | R      | R      |

| Bit           | 23    | 22    | 21    | 20   | 19    | 18    | 17     | 16     |

| Bit Name      | ACT   | _     | —     | _    | —     | _     | ESIF   | DTIF   |

| Initial Value | 0     | 0     | 0     | 0    | 0     | 0     | 0      | 0      |

| R/W           | R     | R     | R     | R    | R     | R     | R/(W)* | R/(W)* |

| Bit           | 15    | 14    | 13    | 12   | 11    | 10    | 9      | 8      |

| Bit Name      | DTSZ1 | DTSZ0 | MDS1  | MDS0 | TSEIE | _     | ESIE   | DTIE   |

| Initial Value | 0     | 0     | 0     | 0    | 0     | 0     | 0      | 0      |

| R/W           | R/W   | R/W   | R/W   | R/W  | R/W   | R     | R/W    | R/W    |

| Bit           | 7     | 6     | 5     | 4    | 3     | 2     | 1      | 0      |

| Bit Name      | DTF1  | DTF0  | DTA   | _    | _     | DMAP2 | DMAP1  | DMAP0  |

| Initial Value | 0     | 0     | 0     | 0    | 0     | 0     | 0      | 0      |

| R/W           | R/W   | R/W   | R/W   | R    | R     | R/W   | R/W    | R/W    |

Note: \* Only 0 can be written to this bit after having been read as 1, to clear the flag.

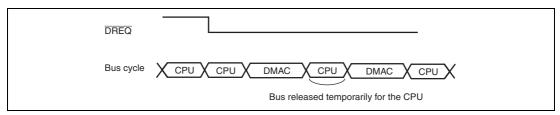

Figure 10.13 shows an example of timing in cycle stealing mode. The transfer conditions are as follows:

- Address mode: Single address mode

- Sampling method of the DREQ signal: Low level detection

#### (2) Burst Access Mode

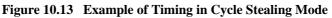

In burst mode, once it takes the bus, the DMAC continues a transfer without releasing the bus until the transfer end condition is satisfied. Even if a transfer is requested from another channel having priority, the transfer is not stopped once it is started. The DMAC releases the bus in the next cycle after the transfer for the channel in burst mode is completed. This is similarly to operation in cycle stealing mode. However, setting the IBCCS bit in BCR2 of the bus controller makes the DMAC release the bus to pass the bus to another bus master.

In block transfer mode, the burst mode setting is ignored (operation is the same as that in burst mode during one block of transfers). The DMAC is always operated in cycle stealing mode.

Clearing the DTE bit in DMDR stops a DMA transfer. A transfer requested before the DTE bit is cleared to 0 by the DMAC is executed. When an interrupt by a transfer size error, a repeat size end, or an extended repeat area overflow occurs, the DTE bit is cleared to 0 and the transfer ends.

Figure 10.14 shows an example of timing in burst mode.

Figure 10.14 Example of Timing in Burst Mode

### 13.3.1 Port Function Control Register 0 (PFCR0)

PFCR0 enables/disables the  $\overline{\text{CS}}$  output.

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0          |

|---------------|------|------|------|------|------|------|------|------------|

| Bit Name      | CS7E | CS6E | CS5E | CS4E | CS3E | CS2E | CS1E | CS0E       |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | Undefined* |

| R/W           | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W        |

Note: \* 1 in external extended mode; 0 in other modes.

| Bit | Bit Name | Initial<br>Value | R/W | Description                                         |

|-----|----------|------------------|-----|-----------------------------------------------------|

| 7   | CS7E     | 0                | R/W | CS7 to CS0 Enable                                   |

| 6   | CS6E     | 0                | R/W | These bits enable/disable the corresponding CSn     |

| 5   | CS5E     | 0                | R/W | output.                                             |

| 4   | CS4E     | 0                | R/W | O: Pin functions as I/O port                        |

| 3   | CS3E     | 0                | R/W | $-$ 1: Pin functions as $\overline{CSn}$ output pin |

| 2   | CS2E     | 0                | R/W | -(n = 7  to  0)                                     |

| 1   | CS1E     | 0                | R/W | _                                                   |

| 0   | CS0E     | Undefined*       | R/W | —                                                   |

Note: \* 1 in external extended mode, 0 in other modes.

### 13.3.9 Port Function Control Register A (PFCRA)

PFCRA selects the multiple functions for the TPU I/O pins.

| Bit        | 7          | 6                | 5       | 4                                                                    | 3           | 2          | 1       | 0      |

|------------|------------|------------------|---------|----------------------------------------------------------------------|-------------|------------|---------|--------|

| Bit Nam    | ne TPUMS11 | TPUMS10          | TPUMS9A | TPUMS9A TPUMS9B                                                      |             | TPUMS7     | TPUMS6A | TPUM6B |

| Initial Va | alue 0     | 0                | 0       | 0                                                                    | 0           | 0          | 0       | 0      |

| R/W        | R/W        | R/W              | R/W     | R/W                                                                  | R/W         | R/W        | R/W     | R/W    |

| Bit        | Bit Name   | Initial<br>Value | R/W I   | Description                                                          |             |            |         |        |

| 7          | TPUMS11    | 0                | R/W     | rpu I/o Pin                                                          | Multiplex F | unction Se | lect    |        |

|            |            |                  | 9       | Selects TIOC                                                         | CA11 functi | on.        |         |        |

|            |            |                  | (       | 0: Specifies pin PK6 as output compare output and input capture      |             |            |         |        |

|            |            |                  | -       | 1: Specifies PK7 as input capture input and PK6 as<br>output compare |             |            |         |        |

| 6          | TPUMS10    | 0                | R/W     | TPU I/O Pin Multiplex Function Select                                |             |            |         |        |

|            |            |                  | 9       | Selects TIOCA10 function.                                            |             |            |         |        |

|            |            |                  | (       | 0: Specifies PK4 as output compare output and input<br>capture       |             |            |         |        |

|            |            |                  | -       | 1: Specifies PK5 as input capture input and PK4 as<br>output compare |             |            | PK4 as  |        |

| 5          | TPUMS9A    | 0                | R/W     | TPU I/O Pin Multiplex Function Select                                |             |            |         |        |

|            |            |                  | 9       | Selects TIOC                                                         | CA9 functio | n.         |         |        |

|   |         |   |     | 0: Specifies PK0 as output compare output and input capture          |

|---|---------|---|-----|----------------------------------------------------------------------|

|   |         |   |     | 1: Specifies PK1 as input capture input and PK0 as<br>output compare |

| 4 | TPUMS9B | 0 | R/W | TPU I/O Pin Multiplex Function Select                                |

|   |         |   |     | Selects TIOCC9 function.                                             |

|   |         |   |     | 0: Specifies PK2 as output compare output and input capture          |

|   |         |   |     | 1: Specifies PK3 as input capture input and PK2 as<br>output compare |

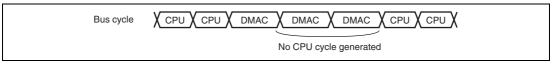

#### (b) When TGR is an input capture register

Figure 14.17 shows an operation example in which TGRA has been designated as an input capture register, and buffer operation has been designated for TGRA and TGRC.

Counter clearing by TGRA input capture has been set for TCNT, and both rising and falling edges have been selected as the TIOCA pin input capture input edge.

As buffer operation has been set, when the TCNT value is stored in TGRA upon occurrence of input capture A, the value previously stored in TGRA is simultaneously transferred to TGRC.

Figure 14.17 Example of Buffer Operation (2)

# 14.10 Usage Notes

#### 14.10.1 Module Stop Function Setting

Operation of the TPU can be disabled or enabled using the module stop control register. The initial setting is for operation of the TPU to be halted. Register access is enabled by clearing module stop state. For details, see section 28, Power-Down Modes.

#### 14.10.2 Input Clock Restrictions

The input clock pulse width must be at least 1.5 states in the case of single-edge detection, and at least 2.5 states in the case of both-edge detection. The TPU will not operate properly with a narrower pulse width.

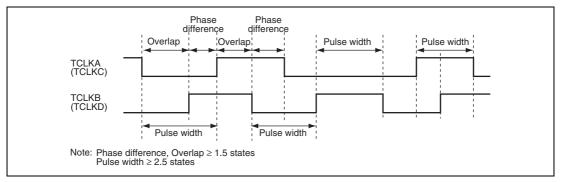

In phase counting mode, the phase difference and overlap between the two input clocks must be at least 1.5 states, and the pulse width must be at least 2.5 states. Figure 14.46 shows the input clock conditions in phase counting mode.

Figure 14.46 Phase Difference, Overlap, and Pulse Width in Phase Counting Mode

Section 19 Serial Communication Interface (SCI, IrDA, CRC)

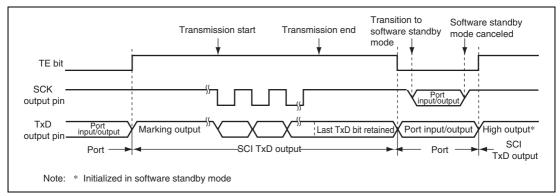

#### Figure 19.41 Port Pin States during Software Standby Mode Transition (Internal Clock, Clocked Synchronous Transmission) (Setting is Prohibited in SCI\_5 and SCI\_6)

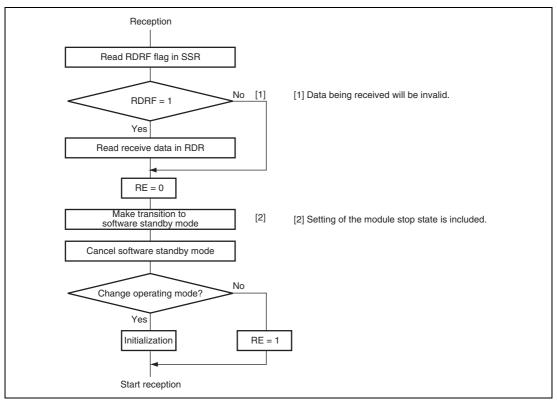

Figure 19.42 Sample Flowchart for Software Standby Mode Transition during Reception

#### 20.3.8 Interrupt Enable Register 1 (IER1)

IER1 enables the interrupt requests of interrupt flag register 1 (IFR1). When an interrupt flag is set to 1 while the corresponding bit of each interrupt is set to 1, an interrupt request is sent to the CPU. The interrupt vector number is determined by the contents of interrupt select register 1 (ISR1).

| Bit           | 7 | 6 | 5 | 4 | 3 | 2      | 1      | 0     |

|---------------|---|---|---|---|---|--------|--------|-------|

| Bit Name      | _ | — | — | — | — | EP3 TR | EP3 TS | VBUSF |

| Initial Value | 0 | 0 | 0 | 0 | 0 | 0      | 0      | 0     |

| R/W           | R | R | R | R | R | R/W    | R/W    | R/W   |

| Bit | Bit Name | Initial<br>Value | R/W | Description                                      |

|-----|----------|------------------|-----|--------------------------------------------------|

| 7   | _        | 0                | R   | Reserved                                         |

| 6   | _        | 0                | R   | These bits are always read as 0. The write value |

| 5   | _        | 0                | R   | should always be 0.                              |

| 4   | _        | 0                | R   |                                                  |

| 3   | —        | 0                | R   |                                                  |

| 2   | EP3 TR   | 0                | R/W | EP3 Transfer Request                             |

| 1   | EP3 TS   | 0                | R/W | EP3 Transmission Complete                        |

| 0   | VBUSF    | 0                | R/W | USB Bus Connect                                  |

#### 20.3.9 Interrupt Enable Register 2 (IER2)

IER2 enables the interrupt requests of interrupt flag register 2 (IFR2). When an interrupt flag is set to 1 while the corresponding bit of each interrupt is set to 1, an interrupt request is sent to the CPU. The interrupt vector number is determined by the contents of interrupt select register 2 (ISR2).

| Bit           | 7      | 6 | 5 | 4     | 3    | 2 | 1     | 0     |

|---------------|--------|---|---|-------|------|---|-------|-------|

| Bit Name      | SSRSME | _ | _ | SURSE | CFDN | — | SETCE | SETIE |

| Initial Value | 0      | 0 | 0 | 0     | 0    | 0 | 0     | 0     |

| R/W           | R/W    | R | R | R/W   | R/W  | R | R/W   | R/W   |

#### (f) Operating Clock Frequency Inquiry

The boot program will return the number of operating clock frequencies, and the maximum and minimum values.

Command

H'23

• Command, H'23, (one byte): Inquiry regarding operating clock frequencies

| Response | H'33                         | Size                  | Number of operating<br>clock frequencies   |  |  |  |

|----------|------------------------------|-----------------------|--------------------------------------------|--|--|--|

|          | Minimum val<br>operating clo | ue of<br>ck frequency | Maximum value of operating clock frequency |  |  |  |

|          |                              |                       |                                            |  |  |  |

|          | SUM                          |                       | <b>.</b>                                   |  |  |  |

- Response, H'33, (one byte): Response to operating clock frequency inquiry

- Size (one byte): The number of bytes that represents the minimum values, maximum values, and the number of frequencies.

- Number of operating clock frequencies (one byte): The number of supported operating clock frequency types

(e.g. when there are two operating clock frequency types, which are the main and peripheral clocks, the number of types will be H'02.)

• Minimum value of operating clock frequency (two bytes): The minimum value of the multiplied or divided clock frequency.

The minimum and maximum values of the operating clock frequency represent the values in MHz, valid to the hundredths place of MHz, and multiplied by 100. (e.g. when the value is 17.00 MHz, it will be 2000, which is H'07D0.)

• Maximum value (two bytes): Maximum value among the multiplied or divided clock frequencies.

There are as many pairs of minimum and maximum values as there are operating clock frequencies.

• SUM (one byte): Checksum

Clock oscillation and internal power supply start as soon as the signal on the  $\overline{\text{RES}}$  pin is driven low. At the same time, clock signals are supplied to the LSI. In this case, the  $\overline{\text{RES}}$  pin has to be held low until the clock oscillation has become stable. Once the signal on the  $\overline{\text{RES}}$  pin is driven high, the CPU starts reset exception handling.

- Exit from deep software standby mode by the signal on the STBY pin When the STBY pin is driven low, a transition is made to hardware standby mode.

- Note: \* Supported only by the H8SX/1668M Group.

Figure 30.10 Basic Bus Timing: Three-State Access, One Wait