#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | LINbus, SCI, SPI                                                       |

| Peripherals                | POR, PWM                                                               |

| Number of I/O              | 24                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908ey16acfje |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

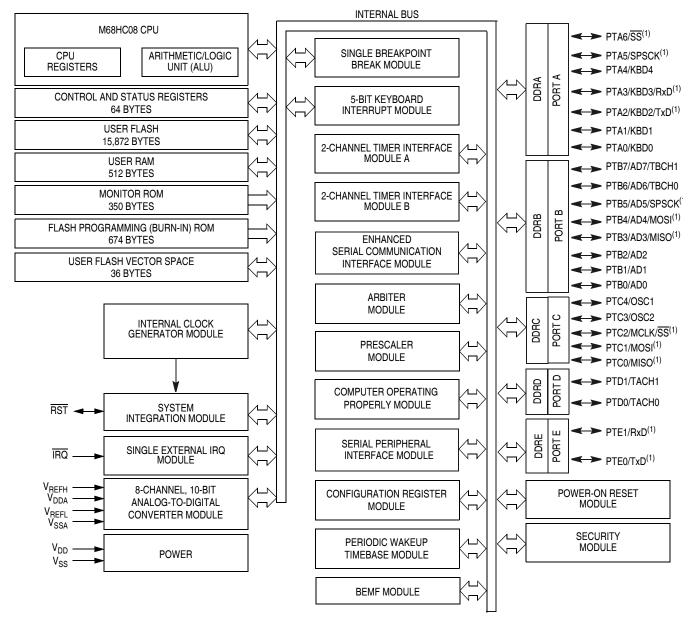

# Chapter 1 General Description

| 1.1     | Introduction                                                                                                          | 9 |

|---------|-----------------------------------------------------------------------------------------------------------------------|---|

| 1.2     | Features                                                                                                              | 9 |

| 1.3     | MCU Block Diagram                                                                                                     | 0 |

| 1.4     | Pin Assignments                                                                                                       | 2 |

| 1.5     | Pin Functions                                                                                                         |   |

| 1.5.1   | Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> )                                                              | 2 |

| 1.5.2   | Oscillator Pins (PTC4/OSC1 and PTC3/OSC2)                                                                             | 3 |

| 1.5.3   | External Reset Pin (RST)                                                                                              | 3 |

| 1.5.4   | External Interrupt Pin (IRQ) 23                                                                                       | 3 |

| 1.5.5   | Analog Power Supply/Reference Pins (V <sub>DDA</sub> , V <sub>REFH</sub> , V <sub>SSA</sub> , and V <sub>REFL</sub> ) |   |

| 1.5.6   | Port A I/O Pins (PTA6/SS, PTA5/SPSCK, PTA4/KBD4, PTA3/KBD3/RxD, PTA2/KBD2/TxD,                                        |   |

| PTA1/   | (BD1, and PTA0/KBD0)                                                                                                  | 4 |

| 1.5.7   | Port B I/O Pins (PTB7/AD7/TBCH1, PTB6/AD6/TBCH0, PTB5/AD5/SPSCK, PTB4/AD4/MO                                          | - |

| SI, PTE | 33/AD3/MISO, PTB2/AD2–PTB0/AD0)                                                                                       | 4 |

| 1.5.8   | Port C I/O Pins (PTC4/OSC1, PTC3/OSC2, PTC2/MCLK/SS, PTC1/MOSI, PTC0/MISO). 24                                        | 4 |

| 1.5.9   | Port D I/O Pins (PTD1/TACH1–PTD0/TACH0) 24                                                                            | 4 |

| 1.5.10  | Port E I/O Pins (PTE1/RxD–PTE0/TxD) 24                                                                                | 4 |

| 1.6     | Pin Summary                                                                                                           |   |

| 1.7     | Priority of Shared Pins                                                                                               | 7 |

# Chapter 2 Memory

| 2.1   | Introduction                   | 29 |

|-------|--------------------------------|----|

| 2.2   | Unimplemented Memory Locations | 29 |

| 2.3   | Reserved Memory Locations      | 29 |

| 2.4   | Input/Output (I/O) Section     | 29 |

| 2.5   | Random Access Memory (RAM)     | 39 |

| 2.6   | FLASH Memory (FLASH)           | 39 |

| 2.6.1 | FLASH Control Register.        | 40 |

| 2.6.2 | FLASH Page Erase Operation     |    |

| 2.6.3 | FLASH Mass Erase Operation     | 42 |

| 2.6.4 | FLASH Program/Read Operation   | 43 |

| 2.6.5 | FLASH Block Protection.        |    |

| 2.6.6 | FLASH Block Protect Register   | 45 |

| 2.6.7 | Wait Mode                      | 46 |

| 2.6.8 | Stop Mode                      | 46 |

#### **Chapter 3**

#### NOTE:

1. The locations of the ESCI and SPI pins are user selectable using CONFIG3 option bits.

#### Figure 1-1. MCU Block Diagram

### Chapter 3 Analog-to-Digital Converter (ADC10) Module

#### 3.1 Introduction

This section describes the 10-bit successive approximation analog-to-digital converter (ADC10).

The ADC10 module shares its pins with general-purpose input/output (I/O) port pins. See Figure 3-1 for port location of these shared pins. The ADC10 on this MCU uses  $V_{DDA}$  and  $V_{SSA}$  as its supply pins and  $V_{REFH}$  and  $V_{REFL}$  as its reference pins. This MCU uses CGMXCLK as its alternate clock source for the ADC. This MCU does not have a hardware conversion trigger.

#### 3.2 Features

Features of the ADC10 module include:

- Linear successive approximation algorithm with 10-bit resolution

- Output formatted in 10- or 8-bit right-justified format

- Single or continuous conversion (automatic power-down in single conversion mode)

- Configurable sample time and conversion speed (to save power)

- Conversion complete flag and interrupt

- Input clock selectable from up to three sources

- Operation in wait and stop modes for lower noise operation

### 3.3 Functional Description

The ADC10 uses successive approximation to convert the input sample taken from ADVIN to a digital representation. The approximation is taken and then rounded to the nearest 10- or 8-bit value to provide greater accuracy and to provide a more robust mechanism for achieving the ideal code-transition voltage.

Figure 3-2 shows a block diagram of the ADC10.

For proper conversion, the voltage on ADVIN must fall between  $V_{REFH}$  and  $V_{REFL}$ . If ADVIN is equal to or exceeds  $V_{REFH}$ , the converter circuit converts the signal to \$3FF for a 10-bit representation or \$FF for a 8-bit representation. If ADVIN is equal to or less than  $V_{REFL}$ , the converter circuit converts it to \$000. Input voltages between  $V_{REFH}$  and  $V_{REFL}$  are straight-line linear conversions.

#### NOTE

Input voltage must not exceed the analog supply voltages.

EXTXTALEN, when set, also configures the external clock stabilization divider in the clock monitor for a 4096-cycle timeout to allow the proper stabilization time for a crystal. When EXTXTALEN is clear, the stabilization divider is configured to 16 cycles since an external clock source does not need a startup time.

1 = Allows PTC3/OSC2 to be an external crystal connection.

0 = PTC3/OSC2 functions as an I/O port pin (default).

#### EXTSLOW — Slow External Crystal Enable Bit

The EXTSLOW bit has two functions. It configures the ICG module for a fast (1 MHz to 32 MHz) or slow (30 kHz to 100 kHz) speed crystal. The option also configures the clock monitor operation in the ICG module to expect an external frequency higher (307.2 kHz to 32 MHz) or lower (60 Hz to 307.2 kHz) than the base frequency of the internal oscillator. See Chapter 8 Internal Clock Generator (ICG) Module.

1 = ICG set for slow external crystal operation

0 = ICG set for fast external crystal operation

| External Clock<br>Configuration Bits |           | Pin Fu    | inction   | Description                                                                                                                                                        |  |

|--------------------------------------|-----------|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EXTCLKEN                             | EXTXTALEN | PTC4/OSC1 | PTC3/OSC2 |                                                                                                                                                                    |  |

| 0                                    | 0         | PTC4      | PTC3      | Default setting — external<br>oscillator disabled                                                                                                                  |  |

| 0                                    | 1         | PTC4      | PTC3      | External oscillator disabled since<br>EXTCLKEN not set                                                                                                             |  |

| 1                                    | 0         | OSC1      | PTC3      | External oscillator configured for<br>an external clock source input<br>(square wave) on OSC1                                                                      |  |

| 1                                    | 1         | OSC1      | OSC2      | External oscillator configured for<br>an external crystal configuration<br>on OSC1 and OSC2. System will<br>also operate with square-wave<br>clock source in OSC1. |  |

#### Table 5-1. External Clock Option Settings

#### EXTCLKEN — External Clock Enable Bit

EXTCLKEN enables an external clock source or crystal/ceramic resonator to be used as a clock input. Setting this bit enables PTC4/OSC1 pin to be a clock input pin. Clearing this bit (default setting) allows the PTC4/OSC1 and PTC3/OSC2 pins to function as general-purpose input/output (I/O) pins. Refer to Table 5-1 for configuration options for the external source. See Chapter 8 Internal Clock Generator (ICG) Module for a more detailed description of the external clock operation.

1 = Allows PTC4/OSC1 to be an external clock connection

0 = PTC4/OSC1 and PTC3/OSC2 function as I/O port pins (default).

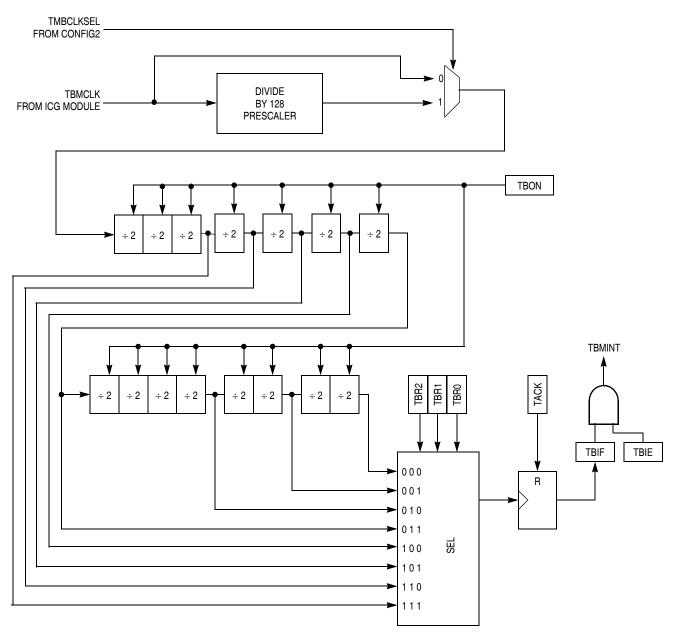

#### TMBCLKSEL — Timebase Clock Select Bit

TMBCLKSEL enables an enable the extra divide by 128 prescaler in the timebase module. Setting this bit enables the extra prescaler and clearing this bit disables it. Refer to Table 16-1 for timebase divider selection details.

1 = Enables extra divide by 128 prescaler in timebase module.

0 = Disables extra divide by 128 prescaler in timebase module.

#### 8.4.4.1 Digitally Controlled Oscillator

The digitally controlled oscillator (DCO) is an inaccurate oscillator which generates the internal clock (ICLK), whose clock period is dependent on the digital loop filter outputs (DSTG[7:0] and DDIV[3:0]). Because of the digital nature of the DCO, the clock period of ICLK will change in quantized steps. This will create a clock period difference or quantization error (Q-ERR) from one cycle to the next. Over several cycles or for longer periods, this error is divided out until it reaches a minimum error of 0.202 percent to 0.368 percent. The dependence of this error on the DDIV[3:0] value and the number of cycles the error is measured over is shown in Table 8-2.

#### 8.4.4.2 Binary Weighted Divider

The binary weighted divider divides the output of the ring oscillator by a power of two, specified by the DCO divider control bits (DDIV[3:0]). DDIV maximizes at %1001 (values of %1010 through %1111 are interpreted as %1001), which corresponds to a divide by 512. When DDIV is %0000, the ring oscillator's output is divided by 1. Incrementing DDIV by one will double the period; decrementing DDIV will halve the period. The DLF cannot directly increment or decrement DDIV; DDIV is only incremented or decremented when an addition or subtraction to DSTG carries or borrows.

| DDIV[3:0]         | ICLK Cycles | Bus Cycles | τ <sub>ICLK</sub> Q-ERR |

|-------------------|-------------|------------|-------------------------|

| %0000 (min)       | 1           | NA         | 6.45%-11.8%             |

| %0000 (min)       | 4           | 1          | 1.61%-2.94%             |

| %0000 (min)       | ≥ 32        | ≥ 8        | 0.202%-0.368%           |

| %0001             | 1           | NA         | 3.23%-5.88%             |

| %0001             | 4           | 1          | 0.806%-1.47%            |

| %0001             | ≥ 16        | ≥ 4        | 0.202%-0.368%           |

| %0010             | 1           | NA         | 1.61%-2.94%             |

| %0010             | 4           | 1          | 0.403%-0.735%           |

| %0010             | ≥ 8         | ≥ 2        | 0.202%-0.368%           |

| %0011             | 1           | NA         | 0.806%-1.47%            |

| %0011             | ≥ 4         | ≥ 1        | 0.202%-0.368%           |

| %0100             | 1           | NA         | 0.403%-0.735%           |

| %0100             | ≥2          | ≥ 1        | 0.202%-0.368%           |

| %0101-%1001 (max) | ≥ 1         | ≥ 1        | 0.202%-0.368%           |

#### Table 8-2. Quantization Error in ICLK

#### 8.4.4.3 Variable-Delay Ring Oscillator

The variable-delay ring oscillator's period is adjustable from 17 to 31 stage delays, in increments of two, based on the upper three DCO stage control bits (DSTG[7:5]). A DSTG[7:5] of %000 corresponds to 17 stage delays; DSTG[7:5] of %111 corresponds to 31 stage delays. Adjusting the DSTG[5] bit has a 6.45 percent to 11.8 percent effect on the output frequency. This also corresponds to the size correction made when the frequency error is greater than  $\pm$ 15 percent. The value of the binary weighted divider does not affect the relative change in output clock period for a given change in DSTG[7:5].

| •                            | Register Bit Results for Given Condition |     |      |     |       |      |       |     |        |           |           |           |

|------------------------------|------------------------------------------|-----|------|-----|-------|------|-------|-----|--------|-----------|-----------|-----------|

| Condition                    | CMIE                                     | CMF | CMON | CS  | ICGON | ICGS | ECQON | ECQ | N[6:0] | TRIM[7:0] | DDIV[3:0] | DSTQ[7:0] |

| Reset                        | 0                                        | 0   | 0    | 0   | 1     | 0    | 0     | 0   | \$15   | \$80      |           | _         |

| OSCENINSTOP = 0,<br>STOP = 1 | 0                                        | 0   | 0    | _   | _     | 0    | _     | 0   | _      | _         |           |           |

| EXTCLKEN = 0                 | 0                                        | 0   | 0    | 0   | 1     | _    | 0     | 0   | _      | _         | uw        | uw        |

| CMF = 1                      | _                                        | (1) | 1    |     | 1     | _    | 1     | _   | uw     | uw        | uw        | uw        |

| CMON = 0                     | 0                                        | 0   | (0)  | —   |       | _    | _     |     | _      | _         |           |           |

| CMON = 1                     | _                                        |     | (1)  |     | 1     | —    | 1     | _   | uw     | uw        | uw        | uw        |

| CS = 0                       | _                                        | _   | _    | (0) | 1     |      | _     | _   |        | _         | uw        | uw        |

| CS = 1                       | _                                        |     | _    | (1) |       | —    | 1     | _   | _      | —         |           |           |

| ICGON = 0                    | 0                                        | 0   | 0    | 1   | (0)   | 0    | 1     | _   | _      | —         |           |           |

| ICGON = 1                    | _                                        | _   | _    |     | (1)   | _    | _     | _   | _      | —         | uw        | uw        |

| ICGS = 0                     | us                                       |     | us   | uc  |       | (0)  | _     | _   | _      | —         |           |           |

| ECGON = 0                    | 0                                        | 0   | 0    | 0   | 1     | —    | (0)   | 0   | _      | —         | uw        | uw        |

| ECGS = 0                     | us                                       | _   | us   | us  | _     |      | _     | (0) | _      | _         | _         | _         |

| IOFF = 1                     |                                          | 1*  | (1)  | 1   | (1)   | 0    | (1)   |     | uw     | uw        | uw        | uw        |

| EOFF = 1                     | _                                        | 1*  | (1)  | 0   | (1)   | _    | (1)   | 0   | uw     | uw        | uw        | uw        |

| N = written                  | (0)                                      | (0) | (0)  | —   |       | 0*   |       | —   | —      | —         | _         | _         |

| TRIM = written               | (0)                                      | (0) | (0)  | —   | _     | 0*   | —     | —   | —      | —         | _         | _         |

| Table 8-4. ICG Module Register Bit Interaction Summary | Table 8-4. | ICG Modul | e Register Bi | t Interaction | Summary |

|--------------------------------------------------------|------------|-----------|---------------|---------------|---------|

|--------------------------------------------------------|------------|-----------|---------------|---------------|---------|

0, 1 0\*, 1\*

(0), (1)

Register bit is unaffected by the given condition. Register bit is forced clear or set (respectively) in the given condition. Register bit is temporarily forced clear or set (respectively) in the given condition. Register bit must be clear or set (respectively) for the given condition to occur. Register bit cannot be set, cleared, or written (respectively) in the given condition. us, uc, uw

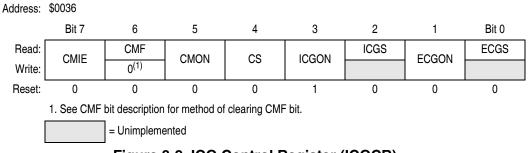

#### 8.7.1 ICG Control Register

The ICG control register (ICGCR) contains the control and status bits for the internal clock generator, external clock generator, and clock monitor as well as the clock select and interrupt enable bits.

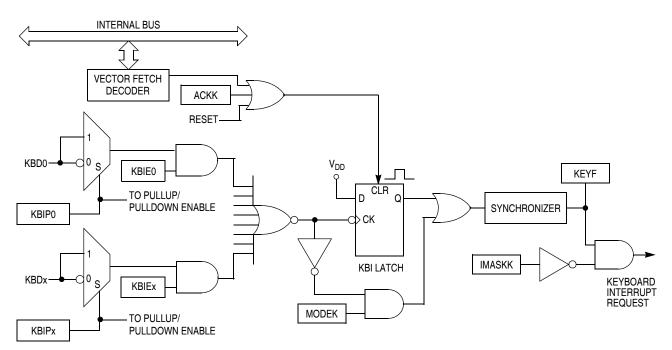

## Chapter 10 Keyboard Interrupt (KBI) Module

#### **10.1 Introduction**

The keyboard interrupt module (KBI) provides independently maskable external interrupts.

The KBI shares its pins with general-purpose input/output (I/O) port pins. See Figure 10-1 for port location of these shared pins.

### 10.2 Features

Features of the keyboard interrupt module include:

- Keyboard interrupt pins with separate keyboard interrupt enable bits and one keyboard interrupt mask

- Programmable edge-only or edge and level interrupt sensitivity

- Edge sensitivity programmable for rising or falling edge

- Level sensitivity programmable for high or low level

- Pullup or pulldown device automatically enabled based on the polarity of edge or level detect

- Exit from low-power modes

### **10.3 Functional Description**

The keyboard interrupt module controls the enabling/disabling of interrupt functions on the KBI pins. These pins can be enabled/disabled independently of each other.

#### 10.3.1 Keyboard Operation

Writing to the KBIEx bits in the keyboard interrupt enable register (KBIER) independently enables or disables each KBI pin. The polarity of the keyboard interrupt is controlled using the KBIPx bits in the keyboard interrupt polarity register (KBIPR). Edge-only or edge and level sensitivity is controlled using the MODEK bit in the keyboard status and control register (KBISCR).

Enabling a keyboard interrupt pin also enables its internal pullup or pulldown device based on the polarity enabled. On falling edge or low level detection, a pullup device is configured. On rising edge or high level detection, a pulldown device is configured.

The keyboard interrupt latch is set when one or more enabled keyboard interrupt inputs are asserted.

- If the keyboard interrupt sensitivity is edge-only, for KBIPx = 0, a falling (for KBIPx = 1, a rising) edge on a keyboard interrupt input does not latch an interrupt request if another enabled keyboard pin is already asserted. To prevent losing an interrupt request on one input because another input remains asserted, software can disable the latter input while it is asserted.

- If the keyboard interrupt is edge and level sensitive, an interrupt request is present as long as any enabled keyboard interrupt input is asserted.

Figure 10-2. Keyboard Interrupt Block Diagram

#### 10.3.1.1 MODEK = 1

If the MODEK bit is set, the keyboard interrupt inputs are both edge and level sensitive. The KBIPx bit will determine whether a edge sensitive pin detects rising or falling edges and on level sensitive pins whether the pin detects low or high levels. With MODEK set, both of the following actions must occur to clear a keyboard interrupt request:

- Return of all enabled keyboard interrupt inputs to a deasserted level. As long as any enabled keyboard interrupt pin is asserted, the keyboard interrupt remains active.

- Vector fetch or software clear. A KBI vector fetch generates an interrupt acknowledge signal to clear the KBI latch. Software generates the interrupt acknowledge signal by writing a 1 to ACKK in KBSCR. The ACKK bit is useful in applications that poll the keyboard interrupt inputs and require software to clear the KBI latch. Writing to ACKK prior to leaving an interrupt service routine can also prevent spurious interrupts due to noise. Setting ACKK does not affect subsequent transitions on the keyboard interrupt inputs. An edge detect that occurs after writing to ACKK latches another interrupt request. If the keyboard interrupt mask bit, IMASKK, is clear, the CPU loads the program counter with the KBI vector address.

The KBI vector fetch or software clear and the return of all enabled keyboard interrupt pins to a deasserted level may occur in any order.

Reset clears the keyboard interrupt request and the MODEK bit, clearing the interrupt request even if a keyboard interrupt input stays asserted.

#### 10.3.1.2 MODEK = 0

If the MODEK bit is clear, the keyboard interrupt inputs are edge sensitive. The KBIPx bit will determine whether an edge sensitive pin detects rising or falling edges. A KBI vector fetch or software clear immediately clears the KBI latch.

When bit DDRCx is a 1, reading address \$0002 reads the PTCx data latch. When bit DDRCx is a 0, reading address \$0002 reads the voltage level on the pin. The data latch can always be written, regardless of the state of its data direction bit. Table 12-3 summarizes the operation of the port C pins.

| DDRC | PTC | I/O Pin         | Accesses to DDRC | Access   | es to PTC               |

|------|-----|-----------------|------------------|----------|-------------------------|

| Bit  | Bit | Mode Read/Write |                  | Read     | Write                   |

| 0    | 2   | Input, Hi-Z     | DDRC[7]          | Pin      | PTC2                    |

| 1    | 2   | Output          | DDRC[7]          | 0        | _                       |

| 0    | Х   | Input, Hi-Z     | DDRC[4:0]        | Pin      | PTC[4:0] <sup>(1)</sup> |

| 1    | Х   | Output          | DDRC[4:0]        | PTC[4:0] | PTC[4:0]                |

Table 12-3. Port C Pin Functions

X = don't care

Hi-Z = high impedance

1. Writing affects data register, but does not affect input.

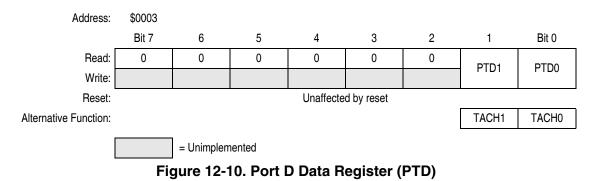

### 12.5 Port D

Port D is a 2-bit special function port that shares its pins with the timer interface module (TIMA).

#### 12.5.1 Port D Data Register

The port D data register contains a data latch for each of the two port D pins.

#### PTD[1:0] — Port D Data Bits

PTD[1:0] are read/write, software programmable bits. Data direction of each port D pin is under the control of the corresponding bit in data direction register D.

#### 12.5.2 Data Direction Register D

Data direction register D determines whether each port D pin is an input or an output. Writing a 1 to a DDRD bit enables the output buffer for the corresponding port D pin; a 0 disables the output buffer.

the IDLE bit has been cleared, a valid character must again set the SCRF bit before an idle condition can set the IDLE bit. Reset clears the IDLE bit.

1 = Receiver input idle

0 = Receiver input active (or idle since the IDLE bit was cleared)

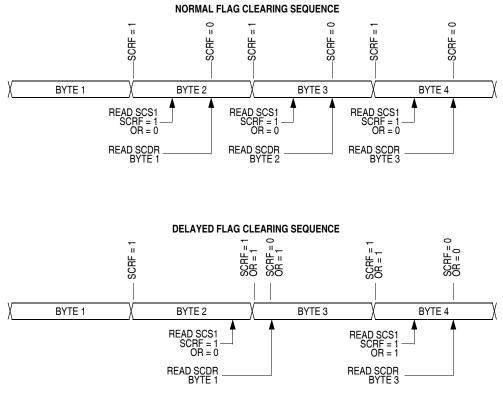

#### OR — Receiver Overrun Bit

This clearable, read-only bit is set when software fails to read the SCDR before the receive shift register receives the next character. The OR bit generates an ESCI error CPU interrupt request if the ORIE bit in SCC3 is also set. The data in the shift register is lost, but the data already in the SCDR is not affected. Clear the OR bit by reading SCS1 with OR set and then reading the SCDR. Reset clears the OR bit.

1 = Receive shift register full and SCRF = 1

0 = No receiver overrun

Software latency may allow an overrun to occur between reads of SCS1 and SCDR in the flag-clearing sequence. Figure 13-13 shows the normal flag-clearing sequence and an example of an overrun caused by a delayed flag-clearing sequence. The delayed read of SCDR does not clear the OR bit because OR was not set when SCS1 was read. Byte 2 caused the overrun and is lost. The next flag-clearing sequence reads byte 3 in the SCDR instead of byte 2.

Figure 13-13. Flag Clearing Sequence

In applications that are subject to software latency or in which it is important to know which byte is lost due to an overrun, the flag-clearing routine can check the OR bit in a second read of SCS1 after reading the data register.

#### **RPF** — Reception in Progress Flag Bit

This read-only bit is set when the receiver detects a 0 during the RT1 time period of the start bit search. RPF does not generate an interrupt request. RPF is reset after the receiver detects false start bits (usually from noise or a baud rate mismatch), or when the receiver detects an idle character. Polling RPF before disabling the ESCI module or entering stop mode can show whether a reception is in progress.

- 1 = Reception in progress

- 0 = No reception in progress

#### 13.8.6 ESCI Data Register

The ESCI data register (SCDR) is the buffer between the internal data bus and the receive and transmit shift registers. Reset has no effect on data in the ESCI data register.

| Address: | \$0015              |    |    |    |    |    |    |       |

|----------|---------------------|----|----|----|----|----|----|-------|

|          | Bit 7               | 6  | 5  | 4  | 3  | 2  | 1  | Bit 0 |

| Read:    | R7                  | R6 | R5 | R4 | R3 | R2 | R1 | R0    |

| Write:   | T7                  | T6 | T5 | T4 | T3 | T2 | T1 | T0    |

| Reset:   | Unaffected by Reset |    |    |    |    |    |    |       |

Figure 13-15. ESCI Data Register (SCDR)

#### R7/T7:R0/T0 — Receive/Transmit Data Bits

Reading address \$0018 accesses the read-only received data bits, R7:R0. Writing to address \$0018 writes the data to be transmitted, T7:T0. Reset has no effect on the ESCI data register.

| N | 0 | T | Έ |

|---|---|---|---|

|   | - |   | _ |

Do not use read-modify-write instructions on the ESCI data register.

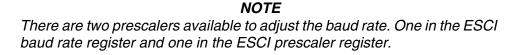

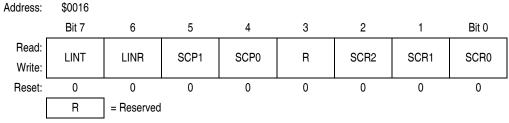

#### 13.8.7 ESCI Baud Rate Register

The ESCI baud rate register (SCBR) together with the ESCI prescaler register selects the baud rate for both the receiver and the transmitter.

#### Figure 13-16. ESCI Baud Rate Register (SCBR)

#### LINT — LIN Break Symbol Transmit Enable

This read/write bit selects the enhanced ESCI features for master nodes in the local interconnect network (LIN) protocol (version 1.2) as shown in Table 13-6. Reset clears LINT.

### Chapter 14 System Integration Module (SIM)

#### 14.1 Introduction

This section describes the system integration module (SIM), which supports up to 24 external and/or internal interrupts. The SIM is a system state controller that coordinates the central processor unit (CPU) and exception timing. Together with the CPU, the SIM controls all microcontroller unit (MCU) activities. A block diagram of the SIM is shown in Figure 14-1.

The SIM is responsible for:

- Bus clock generation and control for CPU and peripherals:

- Stop/wait/reset entry and recovery

- Internal clock control

- Master reset control, including power-on reset (POR) and computer operating properly (COP) timeout

- Interrupt control:

- Acknowledge timing

- Arbitration control timing

- Vector address generation

- CPU enable/disable timing

- Modular architecture expandable to 128 interrupt sources

Table 14-1 shows the internal signal names used in this section.

| Signal Name | Description                                                      |

|-------------|------------------------------------------------------------------|

| CGMXCLK     | Selected clock source from internal clock generator module (ICG) |

| CGMOUT      | Clock output from ICG module (bus clock = CGMOUT divided by two) |

| IAB         | Internal address bus                                             |

| IDB         | Internal data bus                                                |

| PORRST      | Signal from the power-on reset (POR) module to the SIM           |

| IRST        | Internal reset signal                                            |

| R/W         | Read/write signal                                                |

#### **Table 14-1. Signal Name Conventions**

### 14.2 SIM Bus Clock Control and Generation

The bus clock generator provides system clock signals for the CPU and peripherals on the MCU. The system clocks are generated from an incoming clock, CGMOUT, as shown in Figure 14-2. This clock originates from either an external oscillator or from the internal clock generator.

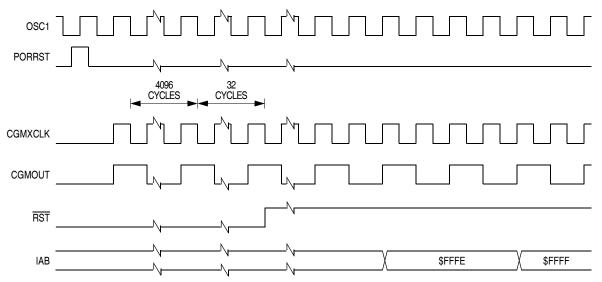

Figure 14-6. POR Recovery

#### 14.3.2.2 Computer Operating Properly (COP) Reset

An input to the SIM is reserved for the COP reset signal. The overflow of the COP counter causes an internal reset and sets the COP bit in the reset status register (SRSR).

To prevent a COP module timeout, write any value to location \$FFFF. Writing to location \$FFFF clears the COP counter and stages 12–5 of the SIM counter. The SIM counter output, which occurs at least every 4080 CGMXCLK cycles, drives the COP counter. The COP should be serviced as soon as possible out of reset to guarantee the maximum amount of time before the first timeout.

The COP module is disabled if the  $\overline{IRQ}$  pin is held at V<sub>TST</sub> while the MCU is in monitor mode. The COP module can be disabled only through combinational logic conditioned with the high-voltage signal on the IRQ pin. This prevents the COP from becoming disabled as a result of external noise.

#### 14.3.2.3 Illegal Opcode Reset

The SIM decodes signals from the CPU to detect illegal instructions. An illegal instruction sets the ILOP bit in the SIM reset status register (SRSR) and causes a reset.

If the stop enable bit, STOP, in the configuration register (CONFIG1) is 0, the SIM treats the STOP instruction as an illegal opcode and causes an illegal opcode reset.

#### 14.3.2.4 Illegal Address Reset

An opcode fetch from an unmapped address generates an illegal address reset. The SIM verifies that the CPU is fetching an opcode prior to asserting the ILAD bit in the SIM reset status register (SRSR) and resetting the MCU. A data fetch from an unmapped address does not generate a reset.

#### 14.3.2.5 Forced Monitor Mode Entry Reset (MENRST)

The MENRST module is monitoring the reset vector fetches and will assert an internal reset if it detects that the reset vectors are erased (\$00). When the MCU comes out of reset, it is forced into monitor mode. See 19.3 Monitor Module (MON).

#### 16.5 TBM Interrupt Rate

The interrupt rate is determined by the equation:

$$t_{\text{TBMRATE}} = \frac{1}{f_{\text{TBMRATE}}} = \frac{\text{Divider}}{f_{\text{TBMCLK}}}$$

where:

$f_{TBMCLK}$  = Frequency supplied from the internal clock generator (ICG) module

Divider = Divider value as determined by TBR2–TBR0 settings. See Table 16-1.

### 18.8 I/O Registers

These I/O registers control and monitor TIMB operation:

- TIMB status and control register, TBSC

- TIMB control registers, TBCNTH-TBCNTL

- TIMB counter modulo registers, TBMODH-TBMODL

- TIMB channel status and control registers, TBSC0 and TBSC1

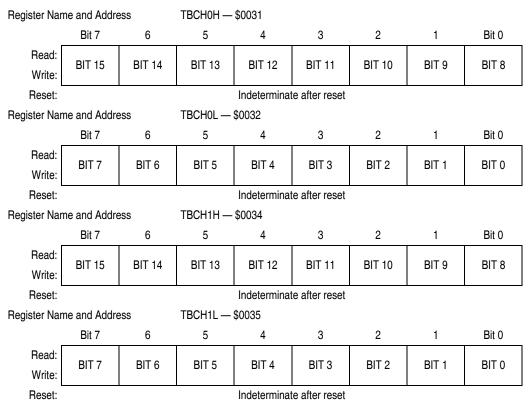

- TIMB channel registers, TBCH0H–TBCH0L and TBCH1H–TBCH1L

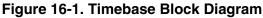

#### 18.8.1 TIMB Status and Control Register

The TIMB status and control register:

- Enables TIMB overflow interrupts

- Flags TIMB overflows

- Stops the TIMB counter

- Resets the TIMB counter

- Prescales the TIMB counter clock

#### Figure 18-4. TIMB Status and Control Register (TBSC)

#### TOF — TIMB Overflow Flag Bit

This read/write flag is set when the TIMB counter reaches the modulo value programmed in the TIMB counter modulo registers. Clear TOF by reading the TIMB status and control register when TOF is set and then writing a 0 to TOF. If another TIMB overflow occurs before the clearing sequence is complete, then writing 0 to TOF has no effect. Therefore, a TOF interrupt request cannot be lost due to inadvertent clearing of TOF. Reset clears the TOF bit. Writing a 1 to TOF has no effect.

- 1 = TIMB counter has reached modulo value

- 0 = TIMB counter has not reached modulo value

#### **TOIE** — TIMB Overflow Interrupt Enable Bit

This read/write bit enables TIMB overflow interrupts when the TOF bit becomes set. Reset clears the TOIE bit.

- 1 = TIMB overflow interrupts enabled

- 0 = TIMB overflow interrupts disabled

#### 18.8.5 TIMB Channel Registers

These read/write registers contain the captured TIMB counter value of the input capture function or the output compare value of the output compare function. The state of the TIMB channel registers after reset is unknown.

In input capture mode (MSxB-MSxA = 0:0), reading the high byte of the TIMB channel x registers (TBCHxH) inhibits input captures until the low byte (TBCHxL) is read.

In output compare mode (MSxB–MSxA  $\neq$  0:0), writing to the high byte of the TIMB channel x registers (TBCHxH) inhibits output compares and the CHxF bit until the low byte (TBCHxL) is written.

Figure 18-9. TIMB Channel Registers (TBCH0H/L-TBCH1H/L)

|                                                          | GetByte                                                                                 | PutByte                                                                         | Verify                                                                                                                                                                                                                                                                                                                                                                                      | fProgram                                                                                                                                                                                | fErase                                                                                                                                            |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Jump Table<br>Address                                    | \$1000                                                                                  | \$100C                                                                          | \$1003                                                                                                                                                                                                                                                                                                                                                                                      | \$1009                                                                                                                                                                                  | \$1006                                                                                                                                            |

| Routine<br>Description                                   | Get a data byte<br>serially through<br>PTA0                                             | Send a data byte<br>serially through<br>PTA0                                    | Read and/or<br>compare a<br>FLASH range                                                                                                                                                                                                                                                                                                                                                     | Program a FLASH<br>range                                                                                                                                                                | Erase a PAGE or<br>entire array                                                                                                                   |

| Internal<br>Operating<br>Frequency<br>(f <sub>op</sub> ) | N/A                                                                                     | N/A                                                                             | N/A                                                                                                                                                                                                                                                                                                                                                                                         | 1.0 MHz to<br>8.0 MHz                                                                                                                                                                   | 1.0 MHz to<br>8.0 MHz                                                                                                                             |

| Hardware<br>Requirement                                  | Pullup on PTA0                                                                          | Pullup on PTA0                                                                  | For send-out option, pullup on PTA0                                                                                                                                                                                                                                                                                                                                                         | N/A                                                                                                                                                                                     | N/A                                                                                                                                               |

| Entry<br>Conditions                                      | PTA0: Input<br>(DDRA0 = 0)                                                              | PTA0: Input and 0<br>data bit<br>(DDRA0 = 0,<br>PTA0 = 0)<br>A: data to be sent | <ul> <li>H:X: First address<br/>of range</li> <li>LADDR: Last<br/>address of range</li> <li>A: A = \$00 for<br/>send-out option or<br/>A ≠ \$00 for<br/>compare option.</li> <li>For send-out option,<br/>PTA0: Input and 0<br/>data bit<br/>(DDRA0 = 0,<br/>PTA0 = 0)</li> <li>For compare option,<br/>DATA array: Load<br/>data to be<br/>compared against<br/>FLASH read data</li> </ul> | H:X: First address<br>of range<br>LADDR: Last<br>address of range<br>CPUSPD: the<br>nearest integer f <sub>op</sub><br>(in MHz) times 4<br>Data array:<br>Load data to be<br>programmed | H:X: Page erase —<br>an address within<br>the page<br>Mass erase =<br>FLBPR<br>CPUSPD: the<br>nearest integer f <sub>op</sub><br>(in MHz) times 4 |

| Exit<br>Conditions                                       | A: Data received<br>through PTA0<br>C-bit: Framing error<br>indicator<br>(error: C = 0) | A, X: No change<br>PTA0: Input and 0<br>data bit<br>(DDRA0 = 0,<br>PTA0 = 0)    | A: Checksum<br>H:X: Next FLASH<br>address<br>C-bit: Verify result<br>indicator<br>(success:<br>C = 1)<br>DATA array: Data<br>replaced with<br>FLASH read data<br>(compare option)                                                                                                                                                                                                           | H:X: Next FLASH<br>address                                                                                                                                                              | H:X: No change                                                                                                                                    |

| l Bit                                                    | I bit is preserved                                                                      | I bit is preserved                                                              | I bit is preserved                                                                                                                                                                                                                                                                                                                                                                          | I bit is set, then<br>restored to entry<br>condition on exit                                                                                                                            | I bit is set, then<br>restored to entry<br>condition on exit                                                                                      |

| COP                                                      | Not Serviced                                                                            | Not Serviced                                                                    | Serviced                                                                                                                                                                                                                                                                                                                                                                                    | Serviced                                                                                                                                                                                | Serviced                                                                                                                                          |

| Table 19-10. Summa | y of On-Chip FLASH Support Routines |

|--------------------|-------------------------------------|

|--------------------|-------------------------------------|

Continued on next page

#### 20.7 3V DC Electrical Characteristics

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                                             | Symbol                              | Min                                                                  | Typ <sup>(2)</sup>                        | Max                                    | Unit                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------|-------------------------------------------|----------------------------------------|----------------------------------|

| Output high voltage<br>$I_{Load} = -0.6$ mA, all I/O pins<br>$I_{Load} = -4.0$ mA, all I/O pins<br>$I_{Load} = -10.0$ mA, PTA0–PTA6/SS, PTC0–PTC1 only                                                                                                                                                    | V <sub>OH</sub>                     | V <sub>DD</sub> -0.3<br>V <sub>DD</sub> -1.0<br>V <sub>DD</sub> -0.8 |                                           |                                        | v                                |

| Output low voltage<br>$I_{Load} = 0.5$ mA, all I/O pins<br>$I_{Load} = 6.0$ mA, all I/O pins<br>$I_{Load} = 10.0$ mA, PTA0–PTA6/SS, PTC0–PTC1 only                                                                                                                                                        | V <sub>OL</sub>                     | <br>                                                                 |                                           | 0.3<br>1.0<br>0.8                      | v                                |

| Input high voltage — all ports, IRQ, RST                                                                                                                                                                                                                                                                  | V <sub>IH</sub>                     | 0.7 x V <sub>DD</sub>                                                | —                                         | V <sub>DD</sub> + 0.3                  | V                                |

| Input low voltage — all ports, IRQ, RST                                                                                                                                                                                                                                                                   | V <sub>IL</sub>                     | V <sub>SS</sub>                                                      | —                                         | 0.3 x V <sub>DD</sub>                  | V                                |

| DC injection current, all ports                                                                                                                                                                                                                                                                           | I <sub>INJ</sub>                    | -2                                                                   | —                                         | +2                                     | mA                               |

| Total dc current injection (sum of all I/O)                                                                                                                                                                                                                                                               | I <sub>INJTOT</sub>                 | -25                                                                  | —                                         | +25                                    | mA                               |

| $\begin{split} &V_{DD} + V_{DDA} \text{ supply current} \\ &Run^{(3),(4)} \\ &Wait^{(4), (5)} \\ &Stop (LVI off) @ 25^{\circ}C^{(4), (6)} \\ &Stop (LVI on) @ 25^{\circ}C \\ &Stop (LVI off), -40^{\circ}C \text{ to } 125^{\circ}C \\ &Stop (LVI on), -40^{\circ}C \text{ to } 125^{\circ}C \end{split}$ | I <sub>DD</sub>                     |                                                                      | 5.7<br>1.8<br>0.52<br>0.15<br>1.6<br>0.15 | TBD<br>TBD<br>TBD<br>TBD<br>TBD<br>TBD | mA<br>mA<br>μA<br>mA<br>μA<br>mA |

| Ports Hi-Z leakage current                                                                                                                                                                                                                                                                                | IIL                                 | -1                                                                   | ±0.1                                      | +1                                     | mA                               |

| Input current – RST, OSC1                                                                                                                                                                                                                                                                                 | I <sub>In</sub>                     | -1                                                                   | —                                         | +1                                     | μA                               |

| Capacitance<br>Ports (as input or output)                                                                                                                                                                                                                                                                 | C <sub>IN</sub><br>C <sub>OUT</sub> |                                                                      |                                           | 12<br>8                                | pF                               |

| POR rearm voltage                                                                                                                                                                                                                                                                                         | V <sub>POR</sub>                    | 750                                                                  | —                                         | —                                      | mV                               |

| POR rise time ramp rate                                                                                                                                                                                                                                                                                   | R <sub>POR</sub>                    | 0.035                                                                | —                                         | —                                      | V/ms                             |

| Monitor mode entry voltage                                                                                                                                                                                                                                                                                | V <sub>TST</sub>                    | V <sub>DD</sub> + 2.5                                                | —                                         | 9.1                                    | V                                |

| Low-voltage inhibit reset, trip falling voltage <sup>(7)</sup>                                                                                                                                                                                                                                            | V <sub>TRIPF</sub>                  | 2.35                                                                 | 2.60                                      | 2.70                                   | V                                |

| Low-voltage inhibit reset, trip rising voltage <sup>(7)</sup>                                                                                                                                                                                                                                             | V <sub>TRIPR</sub>                  | 2.45                                                                 | 2.66                                      | 2.80                                   | V                                |

| Low-voltage inhibit reset/recover hysteresis <sup>(7)</sup>                                                                                                                                                                                                                                               | V <sub>HYS</sub>                    | —                                                                    | 60                                        | _                                      | mV                               |

| Pullup resistor — PTA0–PTA6/SS, IRQ, RST <sup>(8)</sup>                                                                                                                                                                                                                                                   | R <sub>PU</sub>                     | 16                                                                   | 26                                        | 36                                     | kΩ                               |

| Pulldown resistor — PTA0–PTA4 <sup>(9)</sup>                                                                                                                                                                                                                                                              | R <sub>PD</sub>                     | 16                                                                   | 26                                        | 36                                     | kΩ                               |

1.  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ , unless otherwise noted.

2. Typical values reflect average measurements at midpoint of voltage range, 25•C only.

Run (operating) I<sub>DD</sub> measured using internal oscillator at its 16-MHz rate. V<sub>DD</sub> = 3.0 Vdc. All inputs 0.2 V from rail. No dc loads. Less than 100 pF on all outputs. All ports configured as inputs. Measured with all modules enabled.

4. All measurements taken with LVI enabled.

5. Wait I<sub>DD</sub> measured using internal oscillator at its 16-MHz rate. All inputs 0.2 V from rail; no dc loads; less than 100 pF on all outputs. All ports configured as inputs.

6. Stop I<sub>DD</sub> is measured with no port pin sourcing current; all modules are disabled. OSCSTOPEN option is not selected.

7. These values assume the LVI is operating in 3-V mode (i.e. LVI5OR3 bit is set to 0)

8.  $R_{PU}$  is measured at  $V_{DD}$  = 3.0 V.

9. Pulldown resistors available only when KBIx is enabled with KBIPx = 1.

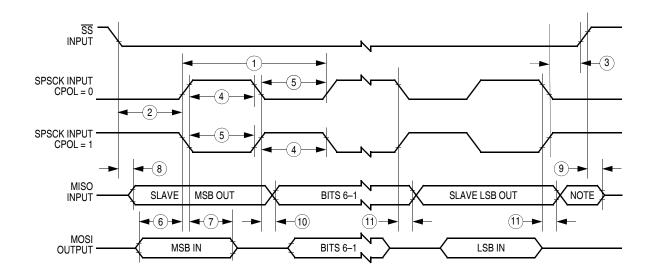

Note: Not defined but normally MSB of character just received

a) SPI Slave Timing (CPHA = 0)

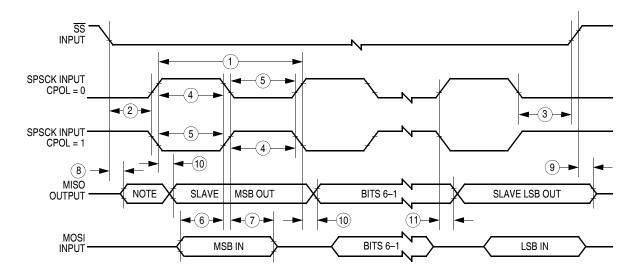

Note: Not defined but normally LSB of character previously transmitted

b) SPI Slave Timing (CPHA = 1)

Figure 20-4. SPI Slave Timing

#### 20.17.2 Conducted Transient Susceptibility

Microcontroller transient conducted susceptibility is measured in accordance with an internal Freescale test method. The measurement is performed with the microcontroller installed on a custom EMC evaluation board and running specialized EMC test software designed in compliance with the test method. The conducted susceptibility is determined by injecting the transient susceptibility signal on each pin of the microcontroller. The transient waveform and injection methodology are in accordance with IEC 61000-4-2 (ESD) and IEC 61000-4-4 (EFT/B). The transient voltage required to cause performance degradation on any pin in the tested configuration is greater than or equal to the reported levels unless otherwise indicated by footnotes below the table.

| Parameter                                                         | Symbol              | Conditions                                                | f <sub>OSC</sub> /f <sub>CPU</sub> | Result | Amplitude <sup>(1)</sup><br>(Min) | Unit |

|-------------------------------------------------------------------|---------------------|-----------------------------------------------------------|------------------------------------|--------|-----------------------------------|------|

| Conducted susceptibility, electrical fast transient/burst (EFT/B) | V <sub>CS_EFT</sub> | V <sub>DD</sub> = 5 V<br>T <sub>A</sub> = +25°C<br>32 QFP | 4/8                                | А      | TBD                               | kV   |

|                                                                   |                     |                                                           |                                    | В      | TBD                               |      |

|                                                                   |                     |                                                           |                                    | С      | TBD                               |      |

|                                                                   |                     |                                                           |                                    | D      | TBD                               |      |

| Conducted susceptibility,<br>electrostatic discharge (ESD)        | V <sub>CS_ESD</sub> | V <sub>DD</sub> = 5 V<br>T <sub>A</sub> = +25°C<br>32 QFP | 4/8                                | A      | TBD                               |      |

|                                                                   |                     |                                                           |                                    | В      | TBD                               | kV   |

|                                                                   |                     |                                                           |                                    | С      | TBD                               | τV   |

|                                                                   |                     |                                                           |                                    | D      | TBD                               |      |

1. Data based on qualification test results. Not tested in production.

2. These pins demonstrate particularly low levels of performance:

#### The susceptibility performance classification is described in the following table.

| Result | Performance Criteria    |                                                                                                                                                                                         |  |

|--------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A      | No failure              | The MCU performs as designed during and after exposure.                                                                                                                                 |  |

| В      | Self-recovering failure | The MCU does not perform as designed during exposure. The MCU returns automatically to normal operation after exposure is removed.                                                      |  |

| с      | Soft failure            | The MCU does not perform as designed during exposure. The MCU does not return to normal operation until exposure is removed and the RESET pin is asserted.                              |  |

| D      | Hard failure            | The MCU does not perform as designed during exposure. The MCU does not return to normal operation until exposure is removed and the power to the MCU is cycled.                         |  |

| E      | Damage                  | The MCU does not perform as designed during and after exposure. The MCU cannot<br>be returned to proper operation due to physical damage or other permanent<br>performance degradation. |  |