Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

|                            |                                                                        |

| Core Processor             | HC08                                                                   |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | LINbus, SCI, SPI                                                       |

| Peripherals                | POR, PWM                                                               |

| Number of I/O              | 24                                                                     |

| Program Memory Size        | 16KB (16K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 512 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-LQFP                                                                |

| Supplier Device Package    | 32-LQFP (7x7)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc908ey16avfje |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## MC68HC908EY16A MC68HC908EY8A

**Data Sheet**

M68HC08 Microcontrollers

MC68HC908EY16A Rev. 2 09/2010

## **Table of Contents**

## Chapter 1 General Description

| 1.1              | Introduction                                                                                                          | 19 |

|------------------|-----------------------------------------------------------------------------------------------------------------------|----|

| 1.2              | Features                                                                                                              | 19 |

| 1.3              | MCU Block Diagram                                                                                                     | 20 |

| 1.4              | Pin Assignments                                                                                                       | 22 |

| 1.5              | Pin Functions                                                                                                         | 22 |

| 1.5.1            | Power Supply Pins (V <sub>DD</sub> and V <sub>SS</sub> )                                                              | 22 |

| 1.5.2            | Oscillator Pins (PTC4/OSC1 and PTC3/OSC2)                                                                             | 23 |

| 1.5.3            | External Reset Pin (RST)                                                                                              |    |

| 1.5.4            | External Interrupt Pin (IRQ)                                                                                          |    |

| 1.5.5            | Analog Power Supply/Reference Pins (V <sub>DDA</sub> , V <sub>REFH</sub> , V <sub>SSA</sub> , and V <sub>REFL</sub> ) | 23 |

| 1.5.6            | Port A I/O Pins (PTA6/SS, PTA5/SPSCK, PTA4/KBD4, PTA3/KBD3/RxD, PTA2/KBD2/TxI                                         |    |

|                  | KBD1, and PTA0/KBD0)                                                                                                  |    |

| 1.5.7            | Port B I/O Pins (PTB7/AD7/TBCH1, PTB6/AD6/TBCH0, PTB5/AD5/SPSCK, PTB4/AD4/M0                                          |    |

| 51, PTI<br>1.5.8 | B3/AD3/MISO, PTB2/AD2–PTB0/AD0)Port C I/O Pins (PTC4/OSC1, PTC3/OSC2, PTC2/MCLK/SS, PTC1/MOSI, PTC0/MISO).            |    |

| 1.5.9            | Port D I/O Pins (PTD1/TACH1–PTD0/TACH0)                                                                               |    |

| 1.5.10           | Port E I/O Pins (PTE1/RxD–PTE0/TxD)                                                                                   |    |

| 1.6              | Pin Summary                                                                                                           |    |

| 1.7              | Priority of Shared Pins                                                                                               |    |

| 1.7              | rionty of Shared Fins                                                                                                 | 21 |

|                  | Chapter 2                                                                                                             |    |

|                  | Memory                                                                                                                |    |

| 2.1              | Introduction                                                                                                          | 29 |

| 2.2              | Unimplemented Memory Locations                                                                                        | 29 |

| 2.3              | Reserved Memory Locations                                                                                             | 29 |

| 2.4              | Input/Output (I/O) Section                                                                                            |    |

| 2.5              | Random Access Memory (RAM)                                                                                            |    |

| 2.6              | FLASH Memory (FLASH)                                                                                                  |    |

| 2.6.1            | FLASH Control Register.                                                                                               |    |

| 2.6.2            | FLASH Page Erase Operation                                                                                            |    |

| 2.6.3            | FLASH Mass Erase Operation                                                                                            | 42 |

| 2.6.4            | FLASH Program/Read Operation                                                                                          | 43 |

| 2.6.5            | FLASH Block Protection.                                                                                               |    |

| 2.6.6            | FLASH Block Protect Register                                                                                          |    |

| 2.6.7            | Wait Mode                                                                                                             |    |

| 2.6.8            | Stop Mode                                                                                                             | 46 |

|                  |                                                                                                                       |    |

Chapter 3

MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2

# Chapter 2 Memory

#### 2.1 Introduction

The M68HC08 central processor unit (CPU08) can address 64 Kbytes of memory space. The memory map, shown in Figure 2-1, includes:

- 16 Kbytes of FLASH memory, 15,872 bytes of user space

- 512 bytes of random-access memory (RAM)

- 36 bytes of user-defined vectors

- 350 bytes of monitor routines in read-only memory (ROM)

- 674 bytes of integrated FLASH burn-in routines in ROM

## 2.2 Unimplemented Memory Locations

Accessing an unimplemented location can cause an illegal address reset. In the memory map (Figure 2-1) and in register figures in this document, unimplemented locations are shaded.

## 2.3 Reserved Memory Locations

Accessing a reserved location can have unpredictable effects on microcontroller unit (MCU) operation. In the Figure 2-1 and in register figures in this document, reserved locations are marked with the word reserved or with the letter R.

## 2.4 Input/Output (I/O) Section

Most of the control, status, and data registers are in the zero page area of \$0000–\$003F. Additional I/O registers have these addresses:

- \$FE00; SIM break status register, SBSR

- \$FE01; SIM reset status register, SRSR

- \$FE03; SIM break flag control register, SBFCR

- \$FE04; interrupt status register 1, INT1

- \$FE05; interrupt status register 2, INT2

- \$FE06; interrupt status register 3, INT3

- \$FE08; FLASH control register, FLCR

- \$FE09; break address register high, BRKH

- \$FE0A; break address register low, BRKL

- \$FE0B; break status and control register, BRKSCR

- \$FE0C; LVI status register, LVISR

- \$FF7E; FLASH block protect register, FLBPR

- \$FF80; 5V internal oscillator trim value (optional), ICGT5V

- \$FF81; 3V internal oscillator trim value (optional), ICGT3V

MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2

**Table 2-2. Examples of Protect Address Ranges**

| BPR[7:0]                  | Addresses of Protect Range                                                        |

|---------------------------|-----------------------------------------------------------------------------------|

| \$00                      | The entire FLASH memory is protected.                                             |

| \$01 ( <b>0000 0001</b> ) | \$C040 (1 <b>100 0000 01</b> 00 0000) — \$FFFF                                    |

| \$02 ( <b>0000 0010</b> ) | \$C080 (1 <b>100 0000 10</b> 00 0000) — \$FFFF                                    |

| \$03 ( <b>0000 0011</b> ) | \$C0C0 (11 <b>00 0000 11</b> 00 0000) — \$FFFF                                    |

| \$04 ( <b>0000 0100</b> ) | \$C100 (11 <b>00 0001 00</b> 00 0000) — \$FFFF                                    |

|                           | and so on                                                                         |

| \$FC (1111 1100)          | \$FF00 (11 <b>11 1111 00</b> 00 0000) — FFFF                                      |

| \$FD ( <b>1111 1101</b> ) | \$FF40 (11 <b>11 1111 01</b> 00 0000) — \$FFFF<br>FLBPR and vectors are protected |

| \$FE (1111 1110)          | \$FF80 (1 <b>111 1111 10</b> 00 0000) — FFFF<br>Vectors are protected             |

| \$FF                      | The entire FLASH memory is not protected.                                         |

#### 2.6.7 Wait Mode

Putting the microcontroller unit (MCU) into wait mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The WAIT instruction should not be executed while performing a program or erase operation on the FLASH, or the operation will discontinue and the FLASH will be on standby mode.

#### 2.6.8 Stop Mode

Putting the MCU into stop mode while the FLASH is in read mode does not affect the operation of the FLASH memory directly, but there will not be any memory activity since the CPU is inactive.

The STOP instruction should not be executed while performing a program or erase operation on the FLASH, or the operation will discontinue and the FLASH will be on standby mode

#### NOTE

Standby mode is the power-saving mode of the FLASH module in which all internal control signals to the FLASH are inactive and the current consumption of the FLASH is at a minimum.

When a conversion is aborted, the contents of the data registers, ADRH and ADRL, are not altered but continue to be the values transferred after the completion of the last successful conversion. In the case that the conversion was aborted by a reset, ADRH and ADRL return to their reset states.

Upon reset or when a conversion is otherwise aborted, the ADC10 module will enter a low power, inactive state. In this state, all internal clocks and references are disabled. This state is entered asynchronously and immediately upon aborting of a conversion.

#### 3.3.3.4 Total Conversion Time

The total conversion time depends on many factors such as sample time, bus frequency, whether ACLKEN is set, and synchronization time. The total conversion time is summarized in Table 3-1.

**Table 3-1. Total Conversion Time versus Control Conditions**

| Conversion Mode                                                                                                                                          | ACLKEN      | Maximum Conversion Time                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------|

| 8-Bit Mode (short sample — ADLSMP = 0): Single or 1st continuous Single or 1st continuous Subsequent continuous (f <sub>Bus</sub> ≥ f <sub>ADCK</sub> )  | 0<br>1<br>x | 18 ADCK + 3 bus clock<br>18 ADCK + 3 bus clock + 5 μs<br>16 ADCK |

| 8-Bit Mode (long sample — ADLSMP = 1): Single or 1st continuous Single or 1st continuous Subsequent continuous (f <sub>Bus</sub> ≥ f <sub>ADCK</sub> )   | 0<br>1<br>x | 38 ADCK + 3 bus clock<br>38 ADCK + 3 bus clock + 5 μs<br>36 ADCK |

| 10-Bit Mode (short sample — ADLSMP = 0): Single or 1st continuous Single or 1st continuous Subsequent continuous (f <sub>Bus</sub> ≥ f <sub>ADCK</sub> ) | 0<br>1<br>x | 21 ADCK + 3 bus clock<br>21 ADCK + 3 bus clock + 5 μs<br>19 ADCK |

| 10-Bit Mode (long sample — ADLSMP = 1): Single or 1st continuous Single or 1st continuous Subsequent continuous (f <sub>Bus</sub> ≥ f <sub>ADCK</sub> )  | 0<br>1<br>x | 41 ADCK + 3 bus clock<br>41 ADCK + 3 bus clock + 5 μs<br>39 ADCK |

The maximum total conversion time for a single conversion or the first conversion in continuous conversion mode is determined by the clock source chosen and the divide ratio selected. The clock source is selectable by the ADICLK and ACLKEN bits, and the divide ratio is specified by the ADIV bits. For example, if the alternate clock source is 16 MHz and is selected as the input clock source, the input clock divide-by-8 ratio is selected and the bus frequency is 4 MHz, then the conversion time for a single 10-bit conversion is:

Maximum Conversion time =

$$\frac{21 \text{ ADCK cycles}}{16 \text{ MHz/8}} + \frac{3 \text{ bus cycles}}{4 \text{ MHz}} = 11.25 \,\mu\text{s}$$

Number of bus cycles =  $11.25 \mu s \times 4 MHz = 45 cycles$

#### NOTE

The ADCK frequency must be between  $f_{ADCK}$  minimum and  $f_{ADCK}$  maximum to meet A/D specifications.

MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2

### 3.4 Interrupts

When AIEN is set, the ADC10 is capable of generating a CPU interrupt after each conversion. A CPU interrupt is generated when the conversion completes (indicated by COCO being set). COCO will set at the end of a conversion regardless of the state of AIEN.

#### 3.5 Low-Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 3.5.1 Wait Mode

The ADC10 will continue the conversion process and will generate an interrupt following a conversion if AIEN is set. If the ADC10 is not required to bring the MCU out of wait mode, ensure that the ADC10 is not in continuous conversion mode by clearing ADCO in the ADC10 status and control register before executing the WAIT instruction. In single conversion mode the ADC10 automatically enters a low-power state when the conversion is complete. It is not necessary to set the channel select bits (ADCH[4:0]) to all 1s to enter a low power state.

#### 3.5.2 Stop Mode

If ACLKEN is clear, executing a STOP instruction will abort the current conversion and place the ADC10 in a low-power state. Upon return from stop mode, a write to ADCSC is required to resume conversions, and the result stored in ADRH and ADRL will represent the last completed conversion until the new conversion completes.

If ACLKEN is set, the ADC10 continues normal operation during stop mode. The ADC10 will continue the conversion process and will generate an interrupt following a conversion if AIEN is set. If the ADC10 is not required to bring the MCU out of stop mode, ensure that the ADC10 is not in continuous conversion mode by clearing ADC0 in the ADC10 status and control register before executing the STOP instruction. In single conversion mode the ADC10 automatically enters a low-power state when the conversion is complete. It is not necessary to set the channel select bits (ADCH[4:0]) to all 1s to enter a low-power state.

If ACLKEN is set, a conversion can be initiated while in stop using the external hardware trigger ADEXTCO when in external convert mode. The ADC10 will operate in a low-power mode until the trigger is asserted, at which point it will perform a conversion and assert the interrupt when complete (if AIEN is set).

## 3.6 ADC10 During Break Interrupts

The system integration module (SIM) controls whether status bits in other modules can be cleared during the break state. BCFE in the break flag control register (BFCR) enables software to clear status bits during the break state. See BFCR in the SIM section of this data sheet.

To allow software to clear status bits during a break interrupt, write a 1 to BCFE. If a status bit is cleared during the break state, it remains cleared when the MCU exits the break state.

To protect status bits during the break state, write a 0 to BCFE. With BCFE cleared (its default state), software can read and write registers during the break state without affecting status bits. Some status bits have a two-step read/write clearing procedure. If software does the first step on such a bit before the

# **Chapter 4 BEMF Counter Module (BEMF)**

#### 4.1 Introduction

This section describes the BEMF module. The BEMF counter integrates over time, while the PTD0/TACH0 pin is active. This function is useful for measuring recirculation currents in motors occurring on switching of inductive loads.

BEMF is the abbreviation for **Back ElectroMagnetic Force**.

## 4.2 Functional Description

The 8-bit BEMF counter runs at the internal bus frequency divided by 64. Whenever PTD0/TACH0 is a logic 1, the counter increments by 1 with each period.

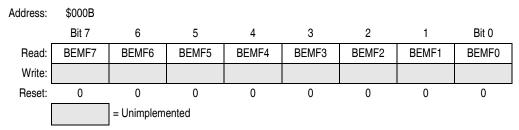

## 4.3 BEMF Register

The BEMF register contains the eight read-only bits of the BEMF counter, showing its actual value. A read access to the BEMF register resets all counter bits to 0.

Figure 4-1. BEMF Register (BEMF)

## 4.4 Input Signal

Port D shares the PTD0/TACH0 pin with the BEMF module. To measure an external signal with the BEMF module, PTD0/TACH0 must be configured as an input (DDRD0 = 0).

#### 4.5 Low Power Modes

The WAIT and STOP instructions put the MCU in low power-consumption standby modes.

#### 4.5.1 Wait Mode

The BEMF module remains active after execution of the WAIT instruction. In wait mode the BEMF register is not accessible by the CPU.

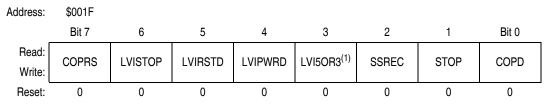

1. The LVI5OR3 bit is cleared only by a power-on reset (POR).

Figure 5-1. Configuration Register 1 (CONFIG1)

#### COPRS — COP Rate Select Bit

COPRS selects the COP timeout period. Reset clears COPRS. See Chapter 6 Computer Operating Properly.

- 1 = COP timeout period = 8176 CGMXCLK cycles

- 0 = COP timeout period = 262,128 CGMXCLK cycles

#### LVISTOP — LVI Enable in Stop Mode Bit

When the LVIPWRD bit is clear, setting the LVISTOP bit enables the LVI to operate during stop mode. Reset clears LVISTOP.

- 1 = LVI enabled during stop mode

- 0 = LVI disabled during stop mode

#### LVIRSTD — LVI Reset Disable Bit

LVIRSTD disables the reset signal from the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI) Module.

- 1 = LVI module resets disabled

- 0 = LVI module resets enabled

#### LVIPWRD — LVI Power Disable Bit

LVIPWRD disables the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI) Module.

- 1 = LVI module power disabled

- 0 = LVI module power enabled

#### LVI5OR3 — LVI 5-V or 3-V Operating Mode Bit

LVI5OR3 selects the voltage operating mode of the LVI module. See Chapter 11 Low-Voltage Inhibit (LVI) Module. The voltage mode selected for the LVI will typically be 5 V. However, users may choose to operate the LVI in 3-V mode if desired. See Chapter 20 Electrical Specifications for the LVI's voltage trip points for each of the modes.

- 1 = LVI operates in 5-V mode.

- 0 = LVI operates in 3-V mode.

#### NOTE

The LVI5OR3 bit is cleared by a power-on reset (POR) only. Other resets will leave this bit unaffected.

#### SSREC — Short Stop Recovery Bit

SSREC enables the CPU to exit stop mode with a delay of 32 CGMXCLK cycles instead of a 4096-CGMXCLK cycle delay.

- 1 = Stop mode recovery after 32 CGMXCLK cycles

- 0 = Stop mode recovery after 4096 CGMXCLCK cycles

#### NOTE

Exiting stop mode by an LVI reset will result in the long stop recovery.

#### MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2

#### OSCENINSTOP — Oscillator Enable In Stop Mode Bit

OSCENINSTOP, when set, will enable the internal clock generator module to continue to generate clocks (either internal, ICLK, or external, ECLK) in stop mode. See Chapter 8 Internal Clock Generator (ICG) Module. This function is used to keep the timebase running while the rest of the microcontroller stops. When clear, all clock generation will cease and both ICLK and ECLK will be forced low during stop mode. The default state for this option is clear, disabling the ICG in stop mode.

- 1 = Oscillator enabled to operate during stop mode

- 0 = Oscillator disabled during stop mode (default)

#### SSBPUENB — SS Pullup Enable Bit

Clearing SSBPUENB enables the SS pullup resistor.

- $1 = Disables \overline{SS}$  pullup resistor.

- $0 = \text{Enables } \overline{\text{SS}} \text{ pullup resistor.}$

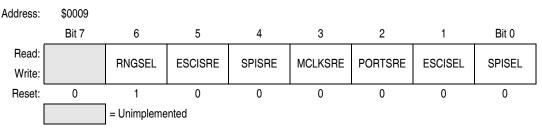

Figure 5-3. Configuration Register 3 (CONFIG3)

#### RNGSEL — External Oscillator Frequency Range Select

RNGSEL works in conjunction with EXTSLOW to enable the amplifiers for the crystal oscillator.

Table 5-2. External Crystal Frequency Range Selection

| EXTSLOW | RNGSEL | Frequency Range |

|---------|--------|-----------------|

| 0       | 0      | 8–32 MHz        |

| 0       | 1      | 1–8 MHz         |

| 1       | 0      | 32–100 kHz      |

| 1       | 1      | Reserved        |

Setting EXTSLOW will force RNGSEL to a 0. RNGSEL cannot be written if EXTSLOW = 1.

#### ESCISRE — Slew Rate Enable for ESCI

- 1 = Slew rate controlled output for TxD

- 0 = Normal output

#### SPISRE — Slew Rate Enable for SPI

- 1 = Slew rate controlled output for MISO, MOSI, and SCK

- 0 = Normal outputs

#### MCLKSRE — Slew Rate Enable for MCLK

- 1 = Slew rate controlled output for MCLK

- 0 = Normal output

#### PORTSRE — Slew Rate Enable for Ports

- 1 = Slew rate controlled output for all ports

- 0 = Normal output

#### **ESCISEL** — **ESCI Pin Selection Bit**

ESCISEL is used to select the pins to be used as ESCI pins when the ESCI is enabled. For more information on the ESCI, see Chapter 13 Enhanced Serial Communications Interface (ESCI) Module.

- 1 = TxD on PTA2 RxD on PTA3

- 0 = TxD on PTE0 RxD on PTE1

#### SPISEL — SPI Pin Selection Bit

SPISEL is used to select the pins to be used as SPI pins when the SPI is enabled. For more information on the SPI, see Chapter 15 Serial Peripheral Interface (SPI) Module.

- 1 = MISO on PTB3 MOSI on PTB4 SPSCK on PTB5  $\overline{SS}$  on PTC2

- 0 = MISO on PTC0 MOSI on PTC1 SPSCK on PTA5 SS on PTA6

# **Chapter 6 Computer Operating Properly**

#### 6.1 Introduction

The computer operating properly (COP) module contains a free-running counter that generates a reset if allowed to overflow. The COP module helps software recover from runaway code. Prevent a COP reset by periodically clearing the COP counter.

## 6.2 Functional Description

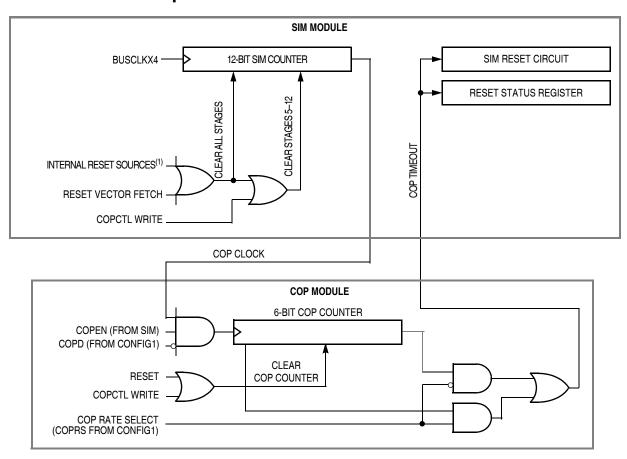

1. See Chapter 14 System Integration Module (SIM) for more details.

Figure 6-1. COP Block Diagram

The COP counter is a free-running 6-bit counter preceded by a 12-bit prescaler. If not cleared by software, the COP counter overflows and generates an asynchronous reset after 8176 or 262,128 CGMXCLK cycles, depending on the state of the COP rate select bit, COPRS, in the CONFIG1. When COPRS = 0, a 4.9152-MHz crystal gives a COP timeout period of 53.3 ms. Writing any value to location \$FFFF before

## 7.7 Instruction Set Summary

Table 7-1 provides a summary of the M68HC08 instruction set.

Table 7-1. Instruction Set Summary (Sheet 1 of 6)

| Source                                                                                         | Operation                                            | Description                                              |           |   | Eff<br>n ( |          |           |           | Address<br>Mode                                                                              | Opcode                                           | Operand                                         | les                                  |

|------------------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------|-----------|---|------------|----------|-----------|-----------|----------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------|--------------------------------------|

| Form                                                                                           | - Political                                          |                                                          | ٧         | Н | I          | N        | Z         | С         | Add                                                                                          | Opc                                              | Ope                                             | Cycles                               |

| ADC #opr<br>ADC opr<br>ADC opr<br>ADC opr,X<br>ADC opr,X<br>ADC, X<br>ADC opr,SP<br>ADC opr,SP | Add with Carry                                       | A ← (A) + (M) + (C)                                      | 1         | ‡ |            | 1        | 1         | 1         | IMM DIR EXT IX2 IX1 IX SP1 SP2                                                               | A9<br>B9<br>C9<br>D9<br>E9<br>F9<br>9EE9<br>9ED9 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ee ff       | 2 3 4 4 3 2 4 5                      |

| ADD #opr<br>ADD opr<br>ADD opr,X<br>ADD opr,X<br>ADD opr,X<br>ADD opr,SP<br>ADD opr,SP         | Add without Carry                                    | $A \leftarrow (A) + (M)$                                 | 1         | Î | _          | 1        | 1         | 1         | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | AB<br>BB<br>CB<br>DB<br>EB<br>FB<br>9EEB<br>9EDB |                                                 | 2<br>3<br>4<br>4<br>3<br>2<br>4<br>5 |

| AIS #opr                                                                                       | Add Immediate Value (Signed) to SP                   | SP ← (SP) + (16 « M)                                     | -         | _ | _          | _        | -         | -         | IMM                                                                                          | A7                                               | ii                                              | 2                                    |

| AIX #opr                                                                                       | Add Immediate Value (Signed) to H:X                  | $H:X \leftarrow (H:X) + (16 \ll M)$                      | _         | _ | -          | _        | _         | _         | IMM                                                                                          | AF                                               | ii                                              | 2                                    |

| AND #opr<br>AND opr<br>AND opr,<br>AND opr,X<br>AND opr,X<br>AND,X<br>AND opr,SP<br>AND opr,SP | Logical AND                                          | A ← (A) & (M)                                            | 0         | - | -          | 1        | 1         | _         | IMM<br>DIR<br>EXT<br>IX2<br>IX1<br>IX<br>SP1<br>SP2                                          | A4<br>B4<br>C4<br>D4<br>E4<br>F4<br>9EE4<br>9ED4 | ii<br>dd<br>hh II<br>ee ff<br>ff<br>ff<br>ee ff | 23443245                             |

| ASL opr<br>ASLA<br>ASLX<br>ASL opr,X<br>ASL ,X<br>ASL opr,SP                                   | Arithmetic Shift Left<br>(Same as LSL)               | © <b>→</b> 0 b7 b0                                       | 1         | _ | -          | <b>1</b> | 1         | 1         | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 38<br>48<br>58<br>68<br>78<br>9E68               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| ASR opr<br>ASRA<br>ASRX<br>ASR opr,X<br>ASR opr,X<br>ASR opr,SP                                | Arithmetic Shift Right                               | b7 b0                                                    | ţ         | _ | -          | <b>‡</b> | ţ         | Į.        | DIR<br>INH<br>INH<br>IX1<br>IX<br>SP1                                                        | 37<br>47<br>57<br>67<br>77<br>9E67               | dd<br>ff<br>ff                                  | 4<br>1<br>1<br>4<br>3<br>5           |

| BCC rel                                                                                        | Branch if Carry Bit Clear                            | $PC \leftarrow (PC) + 2 + rel ? (C) = 0$                 | _         | _ | _          | _        | _         | _         | REL                                                                                          | 24                                               | rr                                              | 3                                    |

| BCLR n, opr                                                                                    | Clear Bit n in M                                     | Mn ← 0                                                   | _         | _ | _          | _        | _         | _         | DIR (b0)<br>DIR (b1)<br>DIR (b2)<br>DIR (b3)<br>DIR (b4)<br>DIR (b5)<br>DIR (b6)<br>DIR (b7) | 11<br>13<br>15<br>17<br>19<br>1B<br>1D<br>1F     | dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd<br>dd    | 4<br>4<br>4<br>4<br>4<br>4           |

| BCS rel                                                                                        | Branch if Carry Bit Set (Same as BLO)                | PC ← (PC) + 2 + rel? (C) = 1                             | -         | - | -          | -        | -         | -         | REL                                                                                          | 25                                               | rr                                              | 3                                    |

| BEQ rel                                                                                        | Branch if Equal                                      | $PC \leftarrow (PC) + 2 + rel? (Z) = 1$                  | _         | _ | _          | _        | -         | _         | REL                                                                                          | 27                                               | rr                                              | 3                                    |

| BGE opr                                                                                        | Branch if Greater Than or Equal To (Signed Operands) | $PC \leftarrow (PC) + 2 + rel? (N \oplus V) = 0$         | _         | - | _          | _        | _         | _         | REL                                                                                          | 90                                               | rr                                              | 3                                    |

| BGT opr                                                                                        | Branch if Greater Than (Signed Operands)             | $PC \leftarrow (PC) + 2 + rel?(Z) \mid (N \oplus V) = 0$ | _         | - | _          | _        | _         | _         | REL                                                                                          | 92                                               | rr                                              | 3                                    |

| BHCC rel                                                                                       | Branch if Half Carry Bit Clear                       | $PC \leftarrow (PC) + 2 + rel? (H) = 0$                  | _         | _ | _          | _        | _         | _         | REL                                                                                          | 28                                               | rr                                              | 3                                    |

| BHCS rel                                                                                       | Branch if Half Carry Bit Set                         | PC ← (PC) + 2 + <i>rel</i> ? (H) = 1                     | <u> -</u> | _ | _          | _        | <u> -</u> | <u> -</u> | REL                                                                                          | 29                                               | rr                                              | 3                                    |

| BHI rel                                                                                        | Branch if Higher                                     | $PC \leftarrow (PC) + 2 + rel? (C)   (Z) = 0$            | -         | — | _          | _        | -         | -         | REL                                                                                          | 22                                               | rr                                              | 3                                    |

## Table 7-2. Opcode Map

|            | Bit Mani             | pulation            | Branch             |                    |                    | Read-Mo             | dify-Write         |                    |                    | Cor                | ntrol             | Register/Memory   |                   |                   |                   |                   |                   |                   |                  |

|------------|----------------------|---------------------|--------------------|--------------------|--------------------|---------------------|--------------------|--------------------|--------------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|

|            | DIR                  | DIR                 | REL                | DIR                | INH                | INH                 | IX1                | SP1                | IX                 | INH                | INH               | IMM               | DIR               | EXT               | IX2               | SP2               | IX1               | SP1               | IX               |

| MSB<br>LSB | 0                    | 1                   | 2                  | 3                  | 4                  | 5                   | 6                  | 9E6                | 7                  | 8                  | 9                 | Α                 | В                 | С                 | D                 | 9ED               | E                 | 9EE               | F                |

| 0          | 5<br>BRSET0<br>3 DIR | 4<br>BSET0<br>2 DIR |                    |                    | 1<br>NEGA<br>1 INH | 1<br>NEGX<br>1 INH  | 4<br>NEG<br>2 IX1  |                    | 3<br>NEG<br>1 IX   | 7<br>RTI<br>1 INH  |                   | 2<br>SUB<br>2 IMM |                   | 4<br>SUB<br>3 EXT | 4<br>SUB<br>3 IX2 | 5<br>SUB<br>4 SP2 |                   | 4<br>SUB<br>3 SP1 | SUB<br>1 IX      |

| 1          | 5<br>BRCLR0<br>3 DIR | 4<br>BCLR0<br>2 DIR | 3<br>BRN<br>2 REL  | 5<br>CBEQ<br>3 DIR |                    | CBEQX<br>3 IMM      |                    | 6<br>CBEQ<br>4 SP1 | CBEQ<br>2 IX+      | 4<br>RTS<br>1 INH  | 3<br>BLT<br>2 REL | 2<br>CMP<br>2 IMM |                   | 4<br>CMP<br>3 EXT | 4<br>CMP<br>3 IX2 | 5<br>CMP<br>4 SP2 | 3<br>CMP<br>2 IX1 | 4<br>CMP<br>3 SP1 | 2<br>CMP<br>1 IX |

| 2          | 5<br>BRSET1<br>3 DIR | 4<br>BSET1<br>2 DIR | 3<br>BHI<br>2 REL  |                    | 5<br>MUL<br>1 INH  | 7<br>DIV<br>1 INH   | 3<br>NSA<br>1 INH  |                    | 2<br>DAA<br>1 INH  |                    | 3<br>BGT<br>2 REL | SBC<br>2 IMM      |                   | 4<br>SBC<br>3 EXT | 4<br>SBC<br>3 IX2 | 5<br>SBC<br>4 SP2 | 3<br>SBC<br>2 IX1 | 4<br>SBC<br>3 SP1 | 2<br>SBC<br>1 IX |

| 3          | 5<br>BRCLR1<br>3 DIR | 4<br>BCLR1<br>2 DIR |                    | COM<br>2 DIR       | COMA<br>1 INH      | COMX<br>1 INH       | 4<br>COM<br>2 IX1  | 5<br>COM<br>3 SP1  | COM<br>1 IX        | 9<br>SWI<br>1 INH  |                   | CPX<br>2 IMM      |                   | 4<br>CPX<br>3 EXT |                   | 5<br>CPX<br>4 SP2 |                   | 4<br>CPX<br>3 SP1 | CPX<br>1 IX      |

| 4          | 5<br>BRSET2<br>3 DIR |                     |                    | 4<br>LSR<br>2 DIR  | 1<br>LSRA<br>1 INH | 1<br>LSRX<br>1 INH  |                    | 5<br>LSR<br>3 SP1  | 3<br>LSR<br>1 IX   | 2<br>TAP<br>1 INH  | 2<br>TXS<br>1 INH |                   | 3<br>AND<br>2 DIR |                   | 4<br>AND<br>3 IX2 | 5<br>AND<br>4 SP2 |                   | 4<br>AND<br>3 SP1 | 2<br>AND<br>1 IX |

| 5          | 5<br>BRCLR2<br>3 DIR |                     | 3<br>BCS<br>2 REL  |                    | 3<br>LDHX<br>3 IMM | 4<br>LDHX<br>2 DIR  | 3<br>CPHX<br>3 IMM |                    | 4<br>CPHX<br>2 DIR | 1<br>TPA<br>1 INH  | 2<br>TSX<br>1 INH | 2<br>BIT<br>2 IMM |                   | 4<br>BIT<br>3 EXT |                   | 5<br>BIT<br>4 SP2 |                   | 4<br>BIT<br>3 SP1 | 2<br>BIT<br>1 IX |

| 6          | 5<br>BRSET3<br>3 DIR | BSET3<br>2 DIR      |                    |                    | 1<br>RORA<br>1 INH | 1<br>RORX<br>1 INH  | 4<br>ROR<br>2 IX1  | 5<br>ROR<br>3 SP1  | 3<br>ROR<br>1 IX   | 2<br>PULA<br>1 INH |                   | 2<br>LDA<br>2 IMM |                   |                   |                   | 5<br>LDA<br>4 SP2 |                   | 4<br>LDA<br>3 SP1 | 2<br>LDA<br>1 IX |

| 7          | 5<br>BRCLR3<br>3 DIR | 4<br>BCLR3<br>2 DIR | 3<br>BEQ<br>2 REL  |                    | 1<br>ASRA<br>1 INH | 1<br>ASRX<br>1 INH  |                    | 5<br>ASR<br>3 SP1  | 3<br>ASR<br>1 IX   | 2<br>PSHA<br>1 INH | 1<br>TAX<br>1 INH | AIS<br>2 IMM      |                   | 4<br>STA<br>3 EXT | 4<br>STA<br>3 IX2 | 5<br>STA<br>4 SP2 |                   | 4<br>STA<br>3 SP1 | 2<br>STA<br>1 IX |

| 8          | 5<br>BRSET4<br>3 DIR |                     | 3<br>BHCC<br>2 REL | 4<br>LSL<br>2 DIR  | 1<br>LSLA<br>1 INH | 1<br>LSLX<br>1 INH  |                    | 5<br>LSL<br>3 SP1  | 3<br>LSL<br>1 IX   | 2<br>PULX<br>1 INH | 1<br>CLC<br>1 INH | EOR<br>2 IMM      |                   |                   | 4<br>EOR<br>3 IX2 | 5<br>EOR<br>4 SP2 |                   | 4<br>EOR<br>3 SP1 | 2<br>EOR<br>1 IX |

| 9          | 5<br>BRCLR4<br>3 DIR | 4<br>BCLR4<br>2 DIR |                    | 4<br>ROL<br>2 DIR  | 1<br>ROLA<br>1 INH | 1<br>ROLX<br>1 INH  | 4<br>ROL<br>2 IX1  | 5<br>ROL<br>3 SP1  | 3<br>ROL<br>1 IX   | PSHX<br>1 INH      | SEC<br>1 INH      | ADC<br>2 IMM      |                   |                   | 4<br>ADC<br>3 IX2 | 5<br>ADC<br>4 SP2 |                   | 4<br>ADC<br>3 SP1 | 2<br>ADC<br>1 IX |

| A          | 5<br>BRSET5<br>3 DIR | 4<br>BSET5<br>2 DIR |                    | 4<br>DEC<br>2 DIR  | 1<br>DECA<br>1 INH | DECX<br>1 INH       |                    | 5<br>DEC<br>3 SP1  | 3<br>DEC<br>1 IX   | 2<br>PULH<br>1 INH | 2<br>CLI<br>1 INH | ORA<br>2 IMM      |                   |                   |                   | 5<br>ORA<br>4 SP2 |                   | 4<br>ORA<br>3 SP1 | 2<br>ORA<br>1 IX |

| В          | 5<br>BRCLR5<br>3 DIR | 4<br>BCLR5<br>2 DIR |                    | 5<br>DBNZ<br>3 DIR |                    | 3<br>DBNZX<br>2 INH |                    | 6<br>DBNZ<br>4 SP1 | 4<br>DBNZ<br>2 IX  | 2<br>PSHH<br>1 INH | 2<br>SEI<br>1 INH | 2<br>ADD<br>2 IMM |                   |                   |                   | 5<br>ADD<br>4 SP2 |                   | 4<br>ADD<br>3 SP1 | 2<br>ADD<br>1 IX |

| С          | 5<br>BRSET6<br>3 DIR | BSET6<br>2 DIR      | 3<br>BMC<br>2 REL  |                    | 1<br>INCA<br>1 INH | 1<br>INCX<br>1 INH  |                    | 5<br>INC<br>3 SP1  | INC<br>1 IX        | 1<br>CLRH<br>1 INH | 1<br>RSP<br>1 INH |                   | 2<br>JMP<br>2 DIR |                   | 4<br>JMP<br>3 IX2 |                   | 3<br>JMP<br>2 IX1 |                   | JMP<br>1 IX      |

| D          | 5<br>BRCLR6<br>3 DIR | 4<br>BCLR6<br>2 DIR |                    | 3<br>TST<br>2 DIR  |                    |                     |                    | 4<br>TST<br>3 SP1  | 2<br>TST<br>1 IX   |                    | 1<br>NOP<br>1 INH | 4<br>BSR<br>2 REL |                   |                   |                   |                   | 5<br>JSR<br>2 IX1 |                   | JSR<br>1 IX      |

| E          | 5<br>BRSET7<br>3 DIR |                     | 3<br>BIL<br>2 REL  |                    | 5<br>MOV<br>3 DD   | 4<br>MOV<br>2 DIX+  | 4<br>MOV<br>3 IMD  |                    | 4<br>MOV<br>2 IX+D | STOP<br>1 INH      | *                 |                   | 3<br>LDX<br>2 DIR |                   | 4<br>LDX<br>3 IX2 | 5<br>LDX<br>4 SP2 |                   | 4<br>LDX<br>3 SP1 | 2<br>LDX<br>1 IX |

| F          | 5<br>BRCLR7<br>3 DIR | 4<br>BCLR7<br>2 DIR | 3<br>BIH<br>2 REL  | 3<br>CLR<br>2 DIR  | 1<br>CLRA<br>1 INH | 1<br>CLRX<br>1 INH  | 3<br>CLR<br>2 IX1  | 4<br>CLR<br>3 SP1  | 2<br>CLR<br>1 IX   | 1<br>WAIT<br>1 INH | 1<br>TXA<br>1 INH | AIX<br>2 IMM      | 3<br>STX<br>2 DIR | STX<br>3 EXT      | 4<br>STX<br>3 IX2 | 5<br>STX<br>4 SP2 | 3<br>STX<br>2 IX1 | 4<br>STX<br>3 SP1 | STX<br>1 IX      |

REL Relative IX Indexed, No Offset IX1 Indexed, 8-Bit Offset IX2 Indexed, 16-Bit Offset INH Inherent IMM Immediate DIR Direct EXT Extended DD Direct-Direct IMD Immediate-Direct IX+D Indexed-Direct DIX+ Direct-Indexed

\*Pre-byte for stack pointer indexed instructions

MSB

Low Byte of Opcode in Hexadecimal

SP1 Stack Pointer, 8-Bit Offset SP2 Stack Pointer, 16-Bit Offset IX+ Indexed, No Offset with Post Increment IX1+ Indexed, 1-Byte Offset with Post Increment

High Byte of Opcode in Hexadecimal LSB 5 Cycles

BRSET0 Opcode Mnemonic

3 DIR Number of Bytes / Addressing Mode

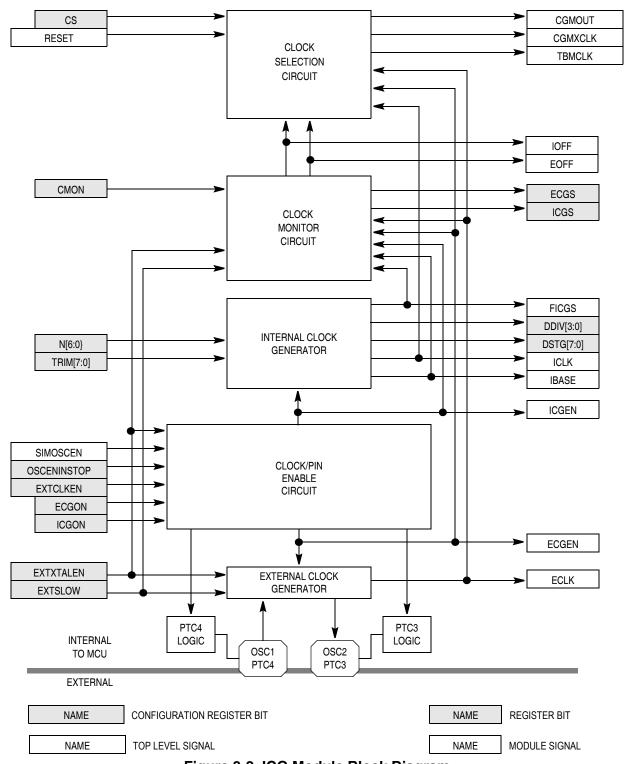

Figure 8-2. ICG Module Block Diagram

#### 8.3.4.1 Clock Monitor Reference Generator

The clock monitor uses a reference based on one clock source to monitor the other clock source. The clock monitor reference generator generates the external reference clock (EREF) based on the external clock (ECLK) and the internal reference clock (IREF) based on the internal clock (ICLK). To simplify the circuit, the low-frequency base clock (IBASE) is used in place of ICLK because it always operates at or near 307.2 kHz. For proper operation, EREF must be at least twice as slow as IBASE and IREF must be at least twice as slow as ECLK.

To guarantee that IREF is slower than ECLK and EREF is slower than IBASE, one of the signals is divided down. Which signal is divided and by how much is determined by the external slow (EXTSLOW) and external crystal enable (EXTXTALEN) bits in the CONFIG, according to the rules in Table 8-2.

#### NOTE

Each signal (IBASE and ECLK) is always divided by four. A longer divider is used on either IBASE or ECLK based on the EXTSLOW bit.

To conserve size, the long divider (divide by 4096) is also used as an external crystal stabilization divider. The divider is reset when the external clock generator is turned off or in stop mode (ECGEN is clear). When the external clock generator is first turned on, the external clock generator stable bit (ECGS) will be clear. This condition automatically selects ECLK as the input to the long divider. The external stabilization clock (ESTBCLK) will be ECLK divided by 16 when EXTXTALEN is low or 4096 when EXTXTALEN is high. This timeout allows the crystal to stabilize. The falling edge of ESTBCLK is used to set ECGS, which will set after a full 16 or 4096 cycles. When ECGS is set, the divider returns to its normal function. ESTBCLK may be generated by either IBASE or ECLK, but any clocking will only reinforce the set condition. If ECGS is cleared because the clock monitor determined that ECLK was inactive, the divider will revert to a stabilization divider. Since this will change the EREF and IREF divide ratios, it is important to turn the clock monitor off (CMON = 0) after inactivity is detected to ensure valid recovery.

#### 8.3.4.2 Internal Clock Activity Detector

The internal clock activity detector, shown in Figure 8-6, looks for at least one falling edge on the low-frequency base clock (IBASE) every time the external reference (EREF) is low. Since EREF is less than half the frequency of IBASE, this should occur every time. If it does not occur two consecutive times, the internal clock inactivity indicator (IOFF) is set. IOFF will be cleared the next time there is a falling edge of IBASE while EREF is low.

The internal clock stable bit (ICGS) is also generated in the internal clock activity detector. ICGS is set when the internal clock generator's filter stable signal (FICGS) indicates that IBASE is within about 5 percent of the target 307.2 kHz  $\pm$  25 percent for two consecutive measurements. ICGS is cleared when FICGS is clear, the internal clock generator is turned off or is in stop mode (ICGEN is clear), or when IOFF is set.

#### 8.3.4.3 External Clock Activity Detector

The external clock activity detector, shown in Figure 8-7, looks for at least one falling edge on the external clock (ECLK) every time the internal reference (IREF) is low. Since IREF is less than half the frequency of ECLK, this should occur every time. If it does not occur two consecutive times, the external clock inactivity indicator (EOFF) is set. EOFF will be cleared the next time there is a falling edge of ECLK while IREF is low.

MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2

#### 18.3.4.1 Unbuffered PWM Signal Generation

Any output compare channel can generate unbuffered PWM pulses as described in 18.3.4 Pulse Width Modulation (PWM). The pulses are unbuffered because changing the pulse width requires writing the new pulse width value over the value currently in the TIMB channel registers.

An unsynchronized write to the TIMB channel registers to change a pulse width value could cause incorrect operation for up to two PWM periods. For example, writing a new value before the counter reaches the old value but after the counter reaches the new value prevents any compare during that PWM period. Also, using a TIMB overflow interrupt routine to write a new, smaller pulse width value may cause the compare to be missed. The TIMB may pass the new value before it is written to the TIMB channel registers.

Use these methods to synchronize unbuffered changes in the PWM pulse width on channel x:

- When changing to a shorter pulse width, enable channel x output compare interrupts and write the

new value in the output compare interrupt routine. The output compare interrupt occurs at the end

of the current pulse. The interrupt routine has until the end of the PWM period to write the new

value.

- When changing to a longer pulse width, enable TIMB overflow interrupts and write the new value in the TIMB overflow interrupt routine. The TIMB overflow interrupt occurs at the end of the current PWM period. Writing a larger value in an output compare interrupt routine (at the end of the current pulse) could cause two output compares to occur in the same PWM period.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare also can cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

#### 18.3.4.2 Buffered PWM Signal Generation

Channels 0 and 1 can be linked to form a buffered PWM channel whose output appears on the PTB6/AD6/TBCH0 pin. The TIMB channel registers of the linked pair alternately control the pulse width of the output.

Setting the MS0B bit in TIMB channel 0 status and control register (TBSC0) links channel 0 and channel 1. The TIMB channel 0 registers initially control the pulse width on the PTB6/AD6/TBCH0 pin. Writing to the TIMB channel 1 registers enables the TIMB channel 1 registers to synchronously control the pulse width at the beginning of the next PWM period. At each subsequent overflow, the TIMB channel registers (0 or 1) that control the pulse width are the ones written to last. TBSC0 controls and monitors the buffered PWM function, and TIMB channel 1 status and control register (TBSC1) is unused. While the MS0B bit is set, the channel 1 pin, PTB7/AD7/TBCH1, is available as a general-purpose I/O pin.

#### NOTE

In buffered PWM signal generation, do not write new pulse width values to the currently active channel registers. User software should track the currently active channel to prevent writing a new value to the active channel. Writing to the active channel registers is the same as generating unbuffered PWM signals.

MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2

#### 18.3.4.3 PWM Initialization

To ensure correct operation when generating unbuffered or buffered PWM signals, use this initialization procedure:

- 1. In the TIMB status and control register (TBSC):

- a. Stop the TIMB counter by setting the TIMB stop bit, TSTOP.

- b. Reset the TIMB counter prescaler by setting the TIMB reset bit, TRST.

- 2. In the TIMB counter modulo registers (TBMODH–TBMODL), write the value for the required PWM period.

- 3. In the TIMB channel x registers (TBCHxH–TBCHxL), write the value for the required pulse width.

- 4. In TIMB channel x status and control register (TBSCx):

- a. Write 0:1 (for unbuffered output compare or PWM signals) or 1:0 (for buffered output compare or PWM signals) to the mode select bits, MSxB–MSxA. See Table 18-2.

- b. Write 1 to the toggle-on-overflow bit, TOVx.

- c. Write 1:0 (to clear output on compare) or 1:1 (to set output on compare) to the edge/level select bits, ELSxB–ELSxA. The output action on compare must force the output to the complement of the pulse width level. See Table 18-2.

#### NOTE

In PWM signal generation, do not program the PWM channel to toggle on output compare. Toggling on output compare prevents reliable 0% duty cycle generation and removes the ability of the channel to self-correct in the event of software error or noise. Toggling on output compare can also cause incorrect PWM signal generation when changing the PWM pulse width to a new, much larger value.

5. In the TIMB status control register (TBSC), clear the TIMB stop bit, TSTOP.

Setting MS0B links channels 0 and 1 and configures them for buffered PWM operation. The TIMB channel 0 registers (TBCH0H–TBCH0L) initially control the buffered PWM output. TIMB status control register 0 (TBSC0) controls and monitors the PWM signal from the linked channels. MS0B takes priority over MS0A.

Clearing the toggle-on-overflow bit, TOVx, inhibits output toggles on TIMB overflows. Subsequent output compares try to force the output to a state it is already in and have no effect. The result is a 0% duty cycle output.

Setting the channel x maximum duty cycle bit (CHxMAX) and setting the TOVx bit generates a 100% duty cycle output. See 18.8.4 TIMB Channel Status and Control Registers.

## 18.4 Interrupts

These TIMB sources can generate interrupt requests:

- TIMB overflow flag (TOF) The TOF bit is set when the TIMB counter reaches the modulo value programmed in the TIMB counter modulo registers. The TIMB overflow interrupt enable bit, TOIE, enables TIMB overflow CPU interrupt requests. TOF and TOIE are in the TIMB status and control register.

- TIMB channel flags (CH1F–CH0F) The CHxF bit is set when an input capture or output compare occurs on channel x. Channel x TIMB CPU interrupt requests are controlled by the channel x interrupt enable bit, CHxIE.

MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2

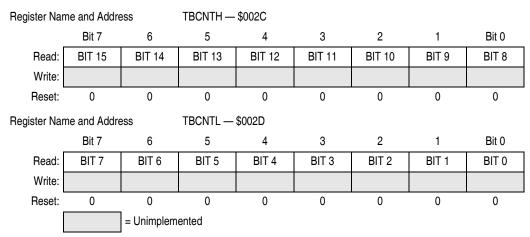

#### 18.8.2 TIMB Counter Registers

The two read-only TIMB counter registers contain the high and low bytes of the value in the TIMB counter. Reading the high byte (TBCNTH) latches the contents of the low byte (TBCNTL) into a buffer. Subsequent reads of TBCNTH do not affect the latched TBCNTL value until TBCNTL is read. Reset clears the TIMB counter registers. Setting the TIMB reset bit (TRST) also clears the TIMB counter registers.

#### NOTE

If TBCNTH is read during a break interrupt, be sure to unlatch TBCNTL by reading TBCNTL before exiting the break interrupt. Otherwise, TBCNTL retains the value latched during the break.

Figure 18-5. TIMB Counter Registers (TBCNTH and TBCNTL)

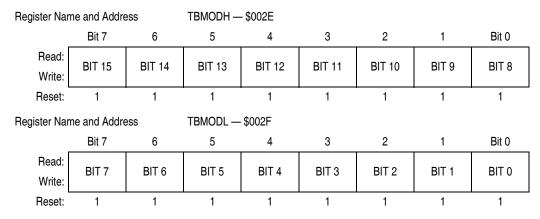

#### 18.8.3 TIMB Counter Modulo Registers

The read/write TIMB modulo registers contain the modulo value for the TIMB counter. When the TIMB counter reaches the modulo value, the overflow flag (TOF) becomes set, and the TIMB counter resumes counting from \$0000 at the next timer clock. Writing to the high byte (TMODH) inhibits the TOF bit and overflow interrupts until the low byte (TMODL) is written. Reset sets the TIMB counter modulo registers.

Figure 18-6. TIMB Counter Modulo Registers (TMODH and TMODL)

#### NOTE

Reset the TIMB counter before writing to the TIMB counter modulo registers.

MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2

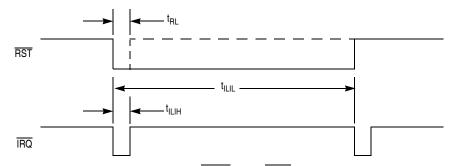

## 20.8 3V Control Timing

| Characteristic <sup>(1)</sup>                                                                                                                                                                                                                                                                                                   | Symbol            | Min                                         | Max                              | Unit                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------------------------------|----------------------------------|----------------------------------------|

| Frequency of operation <sup>(2)</sup> Crystal option (EXTSLOW = 1, RNGSEL = 0) Crystal option (EXTSLOW = 0, RNGSEL = 1) Crystal option (EXTSLOW = 0, RNGSEL = 0) External clock option (EXTSLOW = 1, RNGSEL = 0) <sup>(3)</sup> External clock option (EXTSLOW = 0, RNGSEL = 1) External clock option (EXTSLOW = 0, RNGSEL = 0) | fosc              | 32<br>1<br>8<br>dc <sup>(4)</sup><br>1<br>8 | 100<br>8<br>16<br>100<br>8<br>16 | kHz<br>MHz<br>MHz<br>kHz<br>MHz<br>MHz |

| Internal operating frequency                                                                                                                                                                                                                                                                                                    | f <sub>OP</sub>   | _                                           | 4                                | MHz                                    |

| Internal operating period (1/f <sub>OP</sub> )                                                                                                                                                                                                                                                                                  | t <sub>CYC</sub>  | 250                                         | _                                | ns                                     |

| RST input pulse width low <sup>(5)</sup>                                                                                                                                                                                                                                                                                        | t <sub>RL</sub>   | 200                                         | _                                | ns                                     |

| IRQ interrupt pulse width low <sup>(6)</sup> (edge-triggered)                                                                                                                                                                                                                                                                   | t <sub>ILIH</sub> | 200                                         | _                                | ns                                     |

| IRQ interrupt pulse period                                                                                                                                                                                                                                                                                                      | t <sub>ILIL</sub> | Note <sup>(7)</sup>                         | _                                | t <sub>CYC</sub>                       |

- 1.  $V_{DD}$  = 2.7 to 3.3 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  =  $T_L$  to  $T_H$ ; timing shown with respect to 20%  $V_{DD}$  and 70%  $V_{SS}$ , unless otherwise noted.

- 2. See Chapter 8 Internal Clock Generator (ICG) Module for more information.

- 3. No more than 10% duty cycle deviation from 50%

- 4. Some modules may require a minimum frequency greater than dc for proper operation. See appropriate table for this information.

- 5. Minimum pulse width reset is guaranteed to be recognized. It is possible for a smaller pulse width to cause a reset.

- 6. Minimum pulse width is for guaranteed interrupt. It is possible for a smaller pulse width to be recognized.

- 7. The minimum period is the number of cycles it takes to execute the interrupt service routine plus 1 t<sub>CYC</sub>.

Figure 20-2. RST and IRQ Timing

#### 20.9 Internal Oscillator Characteristics

| Characteristic <sup>(1)</sup>                          | Symbol               | Min             | Тур   | Max | Unit |

|--------------------------------------------------------|----------------------|-----------------|-------|-----|------|

| Internal oscillator base frequency <sup>(2), (3)</sup> | f <sub>INTOSC</sub>  | 230.4           | 307.2 | 384 | kHz  |

| Internal oscillator tolerance                          | f <sub>OSC_TOL</sub> | <del>-</del> 25 | _     | +25 | %    |

| Internal oscillator multiplier <sup>(4)</sup>          | N                    | 1               | _     | 127 | _    |

- 1.  $V_{DD}$  = 4.5 to 5.5 Vdc,  $V_{SS}$  = 0 Vdc,  $T_A$  = -40°C to +125°C, unless otherwise noted

- 2. Internal oscillator is selectable through software for a maximum frequency. Actual frequency will be multiplier (N) x base frequency.

- 3.  $f_{Bus} = (f_{INTOSC} / 4) \times N$  when internal clock source selected

- 4. Multiplier must be chosen to limit the maximum bus frequency of 8 MHz for 4.5-V operation.

#### MC68HC908EY16A • MC68HC908EY8A Data Sheet, Rev. 2