# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                                  |

| Speed                      | 80MHz                                                                                               |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SAI, SPI, SWPMI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, PWM, WDT                                                          |

| Number of I/O              | 83                                                                                                  |

| Program Memory Size        | 1MB (1M × 8)                                                                                        |

| Program Memory Type        | FLASH                                                                                               |

| EEPROM Size                | -                                                                                                   |

| RAM Size                   | 320К х 8                                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                                        |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                                               |

| Oscillator Type            | Internal                                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                   |

| Mounting Type              | Surface Mount                                                                                       |

| Package / Case             | 100-LQFP                                                                                            |

| Supplier Device Package    | 100-LQFP (14x14)                                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l496vgt6                               |

|                            |                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 6.3.19   | Voltage reference buffer characteristics                 | 190 |

|---|--------|----------|----------------------------------------------------------|-----|

|   |        | 6.3.20   | Comparator characteristics                               | 192 |

|   |        | 6.3.21   | Operational amplifiers characteristics                   |     |

|   |        | 6.3.22   | Temperature sensor characteristics                       | 197 |

|   |        | 6.3.23   | V <sub>BAT</sub> monitoring characteristics              | 197 |

|   |        | 6.3.24   | LCD controller characteristics                           | 198 |

|   |        | 6.3.25   | DFSDM characteristics                                    | 199 |

|   |        | 6.3.26   | Timer characteristics                                    | 201 |

|   |        | 6.3.27   | Communication interfaces characteristics                 | 203 |

|   |        | 6.3.28   | FSMC characteristics                                     | 215 |

|   |        | 6.3.29   | Camera interface (DCMI) timing specifications            | 232 |

|   |        | 6.3.30   | SWPMI characteristics                                    | 233 |

|   |        | 6.3.31   | SD/SDIO MMC card host interface (SDIO) characteristics . | 233 |

| 7 | Packa  | age info | rmation                                                  | 236 |

|   | 7.1    | UFBGA    | 169 package information                                  | 236 |

|   | 7.2    | LQFP14   | 14 package information                                   | 240 |

|   | 7.3    | UFBGA    | 132 package information                                  | 244 |

|   | 7.4    | LQFP10   | 00 package information                                   | 247 |

|   | 7.5    | WLCSF    | 2100 package information                                 | 250 |

|   | 7.6    | LQFP64   | 4 package information                                    | 254 |

|   | 7.7    | Therma   | I characteristics                                        | 257 |

|   |        | 7.7.1    | Reference document                                       |     |

|   |        | 7.7.2    | Selecting the product temperature range                  | 257 |

| 8 | Part r | numberi  | ng                                                       | 260 |

| 9 | Revis  | ion hist | tory                                                     | 261 |

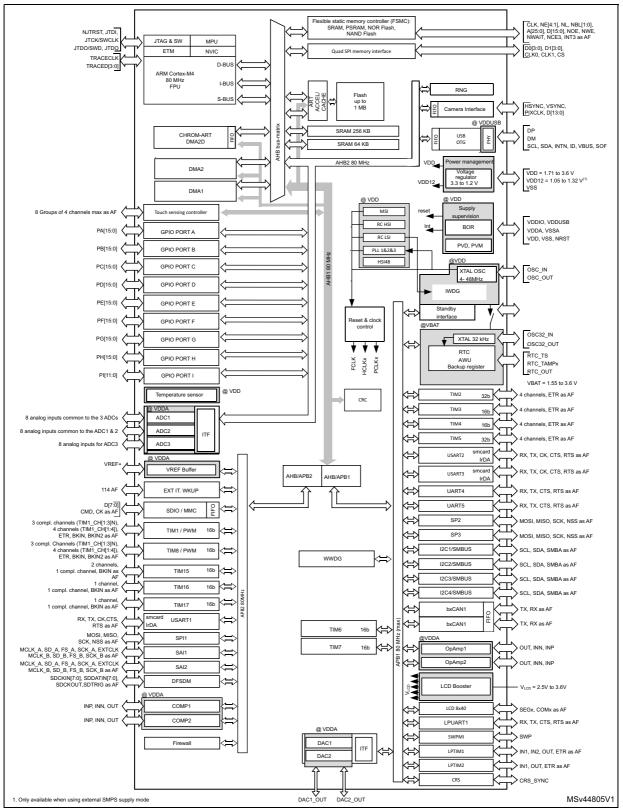

Figure 1. STM32L496xx block diagram

Note: AF: alternate function on I/O pins.

|                                   |                  |                  |                      |                        | Stop | o 0/1             | Sto | op 2              | Star | ndby              | Shut | down              |      |

|-----------------------------------|------------------|------------------|----------------------|------------------------|------|-------------------|-----|-------------------|------|-------------------|------|-------------------|------|

| Peripheral                        | Run              | Sleep            | Low-<br>power<br>run | Low-<br>power<br>sleep | -    | Wakeup capability | -   | Wakeup capability | -    | Wakeup capability | -    | Wakeup capability | VBAT |

| SysTick timer                     | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -    | -                 | -    | -                 | -    |

| Touch sensing<br>controller (TSC) | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -    | -                 | -    | -                 | -    |

| Random number<br>generator (RNG)  | O <sup>(8)</sup> | O <sup>(8)</sup> | -                    | -                      | -    | -                 | -   | -                 | -    | -                 | -    | -                 | -    |

| CRC calculation unit              | 0                | 0                | 0                    | 0                      | -    | -                 | -   | -                 | -    | -                 | -    | -                 | -    |

| GPIOs                             | 0                | 0                | 0                    | 0                      | 0    | 0                 | 0   | 0                 | (9)  | 5<br>pins<br>(10) | (11) | 5<br>pins<br>(10) | -    |

Table 5. Functionalities depending on the working mode<sup>(1)</sup> (continued)

1. Legend: Y = Yes (Enable). O = Optional (Disable by default. Can be enabled by software). - = Not available.

2. The Flash can be configured in power-down mode. By default, it is not in power-down mode.

3. The SRAM clock can be gated on or off.

4. SRAM2 content is preserved when the bit RRS is set in PWR\_CR3 register.

- Some peripherals with wakeup from Stop capability can request HSI16 to be enabled. In this case, HSI16 is woken up by the peripheral, and only feeds the peripheral which requested it. HSI16 is automatically put off when the peripheral does not need it anymore.

- 6. UART and LPUART reception is functional in Stop mode, and generates a wakeup interrupt on Start, address match or received frame event.

- 7. I2C address detection is functional in Stop mode, and generates a wakeup interrupt in case of address match.

- 8. Voltage scaling Range 1 only.

- 9. I/Os can be configured with internal pull-up, pull-down or floating in Standby mode.

- 10. The I/Os with wakeup from Standby/Shutdown capability are: PA0, PC13, PE6, PA2, PC5.

- 11. I/Os can be configured with internal pull-up, pull-down or floating in Shutdown mode but the configuration is lost when exiting the Shutdown mode.

#### 3.10.5 Reset mode

In order to improve the consumption under reset, the I/Os state under and after reset is "analog state" (the I/O schmitt trigger is disable). In addition, the internal reset pull-up is deactivated when the reset source is internal.

#### 3.10.6 VBAT operation

The VBAT pin allows to power the device VBAT domain from an external battery, an external supercapacitor, or from  $V_{DD}$  when no external battery and an external supercapacitor are present. The VBAT pin supplies the RTC with LSE and the backup registers. Three anti-tamper detection pins are available in VBAT mode.

VBAT operation is automatically activated when  $V_{DD}$  is not present.

DocID029173 Rev 1

This digital interface supports the following features:

- Up to two DAC output channels

- 8-bit or 12-bit output mode

- Buffer offset calibration (factory and user trimming)

- Left or right data alignment in 12-bit mode

- Synchronized update capability

- Noise-wave generation

- Triangular-wave generation

- Dual DAC channel independent or simultaneous conversions

- DMA capability for each channel

- External triggers for conversion

- Sample and hold low-power mode, with internal or external capacitor

The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

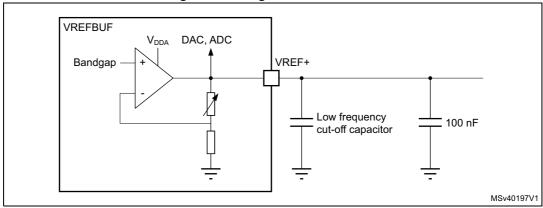

# 3.19 Voltage reference buffer (VREFBUF)

The STM32L496xx devices embed an voltage reference buffer which can be used as voltage reference for ADCs, DACs and also as voltage reference for external components through the VREF+ pin.

The internal voltage reference buffer supports two voltages:

- 2.048 V

- 2.5 V

An external voltage reference can be provided through the VREF+ pin when the internal voltage reference buffer is off.

The VREF+ pin is double-bonded with VDDA on some packages. In these packages the internal voltage reference buffer is not available.

Figure 5. Voltage reference buffer

| Timer type          | Timer        | Counter resolution | Counter<br>type | Prescaler<br>factor                   | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complementary<br>outputs |

|---------------------|--------------|--------------------|-----------------|---------------------------------------|------------------------------|---------------------------------|--------------------------|

| General-<br>purpose | TIM16, TIM17 | 16-bit             | Up              | Any integer<br>between 1<br>and 65536 | Yes                          | 1                               | 1                        |

| Basic               | TIM6, TIM7   | 16-bit             | Up              | Any integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                       |

Table 10. Timer feature comparison (continued)

## 3.27.1 Advanced-control timer (TIM1, TIM8)

The advanced-control timer can each be seen as a three-phase PWM multiplexed on 6 channels. They have complementary PWM outputs with programmable inserted dead-times. They can also be seen as complete general-purpose timers. The 4 independent channels can be used for:

- Input capture

- Output compare

- PWM generation (edge or center-aligned modes) with full modulation capability (0-100%)

- One-pulse mode output

In debug mode, the advanced-control timer counter can be frozen and the PWM outputs disabled to turn off any power switches driven by these outputs.

Many features are shared with those of the general-purpose TIMx timers (described in *Section 3.27.2*) using the same architecture, so the advanced-control timers can work together with the TIMx timers via the Timer Link feature for synchronization or event chaining.

The synchronization for this oscillator can also be taken from the USB data stream itself (SOF signalization) which allows crystal less operation.

The major features are:

- Combined Rx and Tx FIFO size of 1.25 KB with dynamic FIFO sizing

- Supports the session request protocol (SRP) and host negotiation protocol (HNP)

- 1 bidirectional control endpoint + 5 IN endpoints + 5 OUT endpoints

- 8 host channels with periodic OUT support

- HNP/SNP/IP inside (no need for any external resistor)

- Software configurable to OTG 1.3 and OTG 2.0 modes of operation

- OTG 2.0 Supports ADP (Attach detection Protocol)

- USB 2.0 LPM (Link Power Management) support

- Battery Charging Specification Revision 1.2 support

- Internal FS OTG PHY support

For OTG/Host modes, a power switch is needed in case bus-powered devices are connected.

# 3.38 Clock recovery system (CRS)

The STM32L496xx devices embed a special block which allows automatic trimming of the internal 48 MHz oscillator to guarantee its optimal accuracy over the whole device operational range. This automatic trimming is based on the external synchronization signal, which could be either derived from USB SOF signalization, from LSE oscillator, from an external signal on CRS\_SYNC pin or generated by user software. For faster lock-in during startup it is also possible to combine automatic trimming with manual trimming action.

# 3.39 Flexible static memory controller (FSMC)

The Flexible static memory controller (FSMC) includes two memory controllers:

- The NOR/PSRAM memory controller

- The NAND/memory controller

This memory controller is also named Flexible memory controller (FMC).

The main features of the FMC controller are the following:

- Interface with static-memory mapped devices including:

- Static random access memory (SRAM)

- NOR Flash memory/OneNAND Flash memory

- PSRAM (4 memory banks)

- NAND Flash memory with ECC hardware to check up to 8 Kbyte of data

- 8-,16- bit data bus width

- Independent Chip Select control for each memory bank

- Independent configuration for each memory bank

- Write FIFO

- The Maximum FMC\_CLK frequency for synchronous accesses is HCLK/2.

#### LCD parallel interface

The FMC can be configured to interface seamlessly with most graphic LCD controllers. It supports the Intel 8080 and Motorola 6800 modes, and is flexible enough to adapt to specific LCD interfaces. This LCD parallel interface capability makes it easy to build cost effective graphic applications using LCD modules with embedded controllers or high performance solutions using external controllers with dedicated acceleration.

# 3.40 Dual-flash Quad SPI memory interface (QUADSPI)

The Dual-flash Quad SPI is a specialized communication interface targeting single, dual or quad SPI flash memories. It can operate in any of the three following modes:

- Indirect mode: all the operations are performed using the QUADSPI registers

- Status polling mode: the external flash status register is periodically read and an interrupt can be generated in case of flag setting

- Memory-mapped mode: the external Flash is memory mapped and is seen by the system as if it were an internal memory

Both throughput and capacity can be increased two-fold using dual-flash mode, where two Quad SPI flash memories are accessed simultaneously.

The Dual-flash Quad SPI interface supports:

- Three functional modes: indirect, status-polling, and memory-mapped

- Dual-flash mode, where 8 bits can be sent/received simultaneously by accessing two flash memories in parallel.

- SDR and DDR support

- Fully programmable opcode for both indirect and memory mapped mode

- Fully programmable frame format for both indirect and memory mapped mode

- Each of the 5 following phases can be configured independently (enable, length, single/dual/quad communication)

- Instruction phase

- Address phase

- Alternate bytes phase

- Dummy cycles phase

- Data phase

- Integrated FIFO for reception and transmission

- 8, 16, and 32-bit data accesses are allowed

- DMA channel for indirect mode operations

- Programmable masking for external flash flag management

- Timeout management

- Interrupt generation on FIFO threshold, timeout, status match, operation complete, and access error

# Pinouts and pin description

|                                                                                                                                                                                                                                       | Figure 8. STM32L496Zx LQFP144 pinout <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                       | V VD<br>V VD<br>V VD<br>V VS<br>V VS<br>V VD<br>VS<br>VS<br>VD<br>V VS<br>VS<br>VD<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V<br>V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                      |

| PE2   1<br>PE3   2<br>PE4   3<br>PE5   4<br>PE6   5<br>VBAT   6<br>PC13   7<br>PC14-OSC32_IN   8<br>PC15-OSC32_OUT   9<br>PF0   10<br>PF1   11<br>PF2   12                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 108 VDD<br>107 VSS<br>106 VDDUSE<br>105 PA13<br>104 PA12<br>103 PA11<br>102 PA10<br>101 PA9<br>100 PA8<br>99 PC9<br>98 PC8<br>97 PC7 |

| PF3   13<br>PF4   14<br>PF5   15<br>VSS   16<br>VDD   17<br>PF6   18<br>PF7   19<br>PF8   20<br>PF9   21<br>PF10   22<br>PH0-OSC_IN   23<br>PH1-OSC_OUT   24                                                                          | LQFP144                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 96 PC6<br>95 VDDIO2<br>94 VSS<br>93 PG8<br>92 PG7<br>91 PG6<br>90 PG5<br>89 PG4<br>88 PG3<br>87 PG2<br>86 PD15<br>85 PD14            |

| NRST       25         PC0       26         PC1       27         PC2       28         PC3       29         VSSA       30         VREF-       31         VREF+       32         VDDA       33         PA0       34         PA1       35 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84 VDD<br>83 VSS<br>82 PD13<br>81 PD12<br>80 PD11<br>79 PD10<br>78 PD9<br>77 PD8<br>76 PB15<br>75 PB14<br>74 PB13                    |

| PA2 36                                                                                                                                                                                                                                | Page       Page | 73 D PB12<br>MSv38033V4                                                                                                              |

.**₊**(1) 8 STM321 /067v | OED1// pir \_..

1. The above figure shows the package top view.

81/262

| 2 |  |

|---|--|

|   |  |

### Table 15. STM32L496xx pin definitions (continued)

|        |          |               | Piı     | n Num    | ber     |              |          |               |                                       |          |               |       | Pin functions                                                                                                                                                |                         |

|--------|----------|---------------|---------|----------|---------|--------------|----------|---------------|---------------------------------------|----------|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| LQFP64 | WLCSP100 | WLCSP100_SMPS | LQFP100 | UFBGA132 | LQFP144 | LQFP144_SMPS | UFBGA169 | UFBGA169_SMPS | Pin name<br>(function after<br>reset) | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                          | Additional<br>functions |

| -      | -        | -             | -       | -        | -       | -            | C11      | C11           | PI8                                   | I/O      | FT            | -     | DCMI_D12, EVENTOUT                                                                                                                                           | -                       |

| -      | -        | -             | -       | -        | -       | -            | B11      | B11           | PI1                                   | I/O      | FT            | -     | SPI2_SCK, DCMI_D8, EVENTOUT                                                                                                                                  | -                       |

| -      | -        | -             | -       | -        | -       | -            | B10      | B10           | Pl2                                   | I/O      | FT            | -     | TIM8_CH4, SPI2_MISO, DCMI_D9,<br>EVENTOUT                                                                                                                    | -                       |

| -      | -        | -             | -       | -        | -       | -            | C10      | C10           | PI3                                   | I/O      | FT            | -     | TIM8_ETR, SPI2_MOSI, DCMI_D10,<br>EVENTOUT                                                                                                                   | -                       |

| -      | -        | -             | -       | -        | -       | -            | D10      | D10           | Pl4                                   | I/O      | FT            | -     | TIM8_BKIN, DCMI_D5, EVENTOUT                                                                                                                                 | -                       |

| -      | -        | -             | -       | -        | -       | -            | E10      | E10           | PI5                                   | I/O      | FT            | -     | TIM8_CH1, DCMI_VSYNC, EVENTOUT                                                                                                                               | -                       |

| -      | -        | -             | -       | -        | -       | -            | C9       | C9            | PH13                                  | I/O      | FT            | -     | TIM8_CH1N, CAN1_TX, EVENTOUT                                                                                                                                 | -                       |

| -      | -        | -             | -       | -        | -       | -            | В9       | B9            | PI6                                   | I/O      | FT            | -     | TIM8_CH2, DCMI_D6, EVENTOUT                                                                                                                                  | -                       |

| 49     | B2       | B2            | 76      | A10      | 109     | 109          | A10      | A10           | PA14<br>(JTCK/SWCLK)                  | I/O      | FT            | -     | JTCK/SWCLK, LPTIM1_OUT, I2C1_SMBA,<br>I2C4_SMBA, OTG_FS_SOF, SWPMI1_RX,<br>SAI1_FS_B, EVENTOUT                                                               | -                       |

| 50     | A2       | A2            | 77      | A9       | 110     | 110          | A9       | A9            | PA15 (JTDI)                           | I/O      | FT_I          | -     | JTDI, TIM2_CH1, TIM2_ETR, USART2_RX,<br>SPI1_NSS, SPI3_NSS, USART3_RTS_DE,<br>UART4_RTS_DE, TSC_G3_IO1,<br>LCD_SEG17, SWPMI1_SUSPEND,<br>SAI2_FS_B, EVENTOUT | -                       |

| 51     | D4       | C3            | 78      | B11      | 111     | 111          | D9       | D9            | PC10                                  | I/O      | FT_I          | -     | TRACED1, SPI3_SCK, USART3_TX,<br>UART4_TX, TSC_G3_IO2, DCMI_D8,<br>LCD_COM4/LCD_SEG28/LCD_SEG40,<br>SDMMC1_D2, SAI2_SCK_B, EVENTOUT                          | -                       |

Pinouts and pin description

STM32L496xx

|        |      | AF8                          | AF9        | AF10                             | AF11      | AF12                             | AF13        | AF14                     | AF15     |

|--------|------|------------------------------|------------|----------------------------------|-----------|----------------------------------|-------------|--------------------------|----------|

| Po     | ort  | UART4/5/<br>LPUART1/<br>CAN2 | CAN1/TSC   | CAN2/<br>OTG_FS/DCMI/<br>QUADSPI | LCD       | SDMMC/<br>COMP1/2/FM<br>C/SWPMI1 | SAI1/2      | TIM2/15/16/17/<br>LPTIM2 | EVENOUT  |

|        | PE0  | -                            | -          | DCMI_D2                          | LCD_SEG36 | FMC_NBL0                         | -           | TIM16_CH1                | EVENTOUT |

|        | PE1  | -                            | -          | DCMI_D3                          | LCD_SEG37 | FMC_NBL1                         | -           | TIM17_CH1                | EVENTOU  |

|        | PE2  | -                            | TSC_G7_IO1 | -                                | LCD_SEG38 | FMC_A23                          | SAI1_MCLK_A | -                        | EVENTOU  |

|        | PE3  | -                            | TSC_G7_IO2 | -                                | LCD_SEG39 | FMC_A19                          | SAI1_SD_B   | -                        | EVENTOU  |

|        | PE4  | -                            | TSC_G7_IO3 | DCMI_D4                          | -         | FMC_A20                          | SAI1_FS_A   | -                        | EVENTOU  |

| -      | PE5  | -                            | TSC_G7_IO4 | DCMI_D6                          | -         | FMC_A21                          | SAI1_SCK_A  | -                        | EVENTOU  |

|        | PE6  |                              |            | DCMI_D7                          | -         | FMC_A22                          | SAI1_SD_A   | -                        | EVENTOU  |

|        | PE7  | -                            | -          | -                                | -         | FMC_D4                           | SAI1_SD_B   | -                        | EVENTOU  |

| Port E | PE8  | -                            | -          | -                                | -         | FMC_D5                           | SAI1_SCK_B  | -                        | EVENTOU  |

|        | PE9  | -                            | -          | -                                | -         | FMC_D6                           | SAI1_FS_B   | -                        | EVENTOU  |

|        | PE10 | -                            | TSC_G5_IO1 | QUADSPI_CLK                      | -         | FMC_D7                           | SAI1_MCLK_B | -                        | EVENTOU  |

|        | PE11 | -                            | TSC_G5_IO2 | QUADSPI_BK1_NCS                  | -         | FMC_D8                           | -           | -                        | EVENTOU  |

|        | PE12 | -                            | TSC_G5_IO3 | QUADSPI_BK1_IO0                  | -         | FMC_D9                           | -           | -                        | EVENTOU  |

|        | PE13 | -                            | TSC_G5_IO4 | QUADSPI_BK1_IO1                  | -         | FMC_D10                          | -           | -                        | EVENTOU  |

|        | PE14 | -                            | -          | QUADSPI_BK1_IO2                  | -         | FMC_D11                          | -           | -                        | EVENTOU  |

|        | PE15 | -                            | -          | QUADSPI_BK1_IO3                  | -         | FMC_D12                          | -           | -                        | EVENTOU  |

5

STM32L496xx

Pinouts and pin description

|                           |                      |                                                     |                    | running           | g from | Flash, | ART di | sable  |        |       |       |                    |        |        |     |

|---------------------------|----------------------|-----------------------------------------------------|--------------------|-------------------|--------|--------|--------|--------|--------|-------|-------|--------------------|--------|--------|-----|

|                           |                      | Con                                                 | ditions            |                   |        |        | TYP    |        |        |       |       | MAX <sup>(1)</sup> |        |        |     |

| Symbol                    | Parameter            | -                                                   | Voltage<br>scaling | f <sub>HCLK</sub> | 25 °C  | 55 °C  | 85 °C  | 105 °C | 125 °C | 25 °C | 55 °C | 85 °C              | 105 °C | 125 °C | Uni |

|                           |                      |                                                     |                    | 26 MHz            | 3.1    | 3.14   | 3.28   | 3.51   | 3.98   | 3.5   | 3.6   | 3.8                | 4.3    | 5.3    |     |

|                           |                      |                                                     |                    | 16 MHz            | 2.19   | 2.23   | 2.36   | 2.59   | 3.05   | 2.5   | 2.6   | 2.8                | 3.3    | 4.3    |     |

|                           |                      |                                                     |                    | 8 MHz             | 1.22   | 1.26   | 1.39   | 1.61   | 2.07   | 1.4   | 1.5   | 1.7                | 2.2    | 3.2    |     |

|                           |                      |                                                     | Range 2            | 4 MHz             | 0.69   | 0.73   | 0.85   | 1.08   | 1.53   | 0.8   | 0.9   | 1.1                | 1.6    | 2.6    |     |

|                           |                      | f <sub>HCLK</sub> = f <sub>HSE</sub> up<br>to 48MHz |                    | 2 MHz             | 0.41   | 0.44   | 0.57   | 0.79   | 1.24   | 0.5   | 0.6   | 0.8                | 1.3    | 2.3    |     |

|                           | <b>.</b>             | included, bypass                                    |                    | 1 MHz             | 0.27   | 0.3    | 0.43   | 0.65   | 1.1    | 0.3   | 0.4   | 0.6                | 1.1    | 2.1    |     |

| I <sub>DD_ALL</sub> (Run) | Supply<br>current in | mode                                                |                    | 100 kHz           | 0.14   | 0.18   | 0.3    | 0.52   | 0.97   | 0.2   | 0.3   | 0.5                | 1.0    | 2.0    | mA  |

| DD_ALL(I (all)            | Run mode             | PLL ON above                                        |                    | 80 MHz            | 10     | 10.1   | 10.3   | 10.5   | 11.1   | 11.1  | 11.2  | 11.6               | 12.2   | 13.31  |     |

|                           |                      | 48 MHz all<br>peripherals                           |                    | 72 MHz            | 9.02   | 9.1    | 9.29   | 9.59   | 10.1   | 10    | 10.1  | 10.5               | 11.0   | 12.2   |     |

|                           |                      | disable                                             |                    | 64 MHz            | 8.94   | 9.02   | 9.2    | 9.48   | 10     | 9.9   | 10.1  | 10.4               | 11.0   | 12.1   |     |

|                           |                      |                                                     | Range 1            | 48 MHz            | 7.51   | 7.59   | 7.77   | 8.05   | 8.59   | 8.4   | 8.6   | 8.9                | 9.5    | 10.6   |     |

|                           |                      |                                                     |                    | 32 MHz            | 5.38   | 5.45   | 5.62   | 5.88   | 6.41   | 6.0   | 6.2   | 6.5                | 7.0    | 8.2    |     |

|                           |                      |                                                     |                    | 24 MHz            | 4.07   | 4.12   | 4.28   | 4.54   | 5.06   | 4.5   | 4.7   | 5.0                | 5.5    | 6.6    |     |

|                           |                      |                                                     |                    | 16 MHz            | 2.86   | 2.92   | 3.07   | 3.33   | 3.84   | 3.2   | 3.3   | 3.6                | 4.2    | 5.3    |     |

|                           | Cumple               |                                                     |                    | 2 MHz             | 378    | 412    | 549    | 782    | 1260   | 436   | 538   | 761                | 1287   | 2317   |     |

| I <sub>DD_ALL</sub>       | Supply<br>current in | f <sub>HCLK</sub> = f <sub>MSI</sub>                |                    | 1 MHz             | 213    | 246    | 381    | 618    | 1100   | 255   | 367   | 609.               | 1105   | 2138   | μA  |

| (LPRun)                   | Low-power<br>run     | all peripherals dis                                 | able               | 400 kHz           | 101    | 144    | 277    | 514    | 989    | 141   | 256   | 507                | 995    | 2033   | μΛ  |

|                           |                      |                                                     |                    | 100 kHz           | 62     | 95.8   | 228    | 463    | 939    | 85    | 201   | 454                | 947    | 1982   |     |

# Table 28. Current consumption in Run and Low-power run modes, code with data processing

1. Guaranteed by characterization results, unless otherwise specified.

| Symbol               | Parameter                                                          |                            | Conditions                  | Тур                                                                                                                                                                                                                                                                                                                                                                                                     | Max   | Unit |

|----------------------|--------------------------------------------------------------------|----------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

|                      |                                                                    | Danga 1                    | Wakeup clock MSI = 48 MHz   | 8.4                                                                                                                                                                                                                                                                                                                                                                                                     | 9.4   |      |

|                      |                                                                    | Range 1                    | Wakeup clock HSI16 = 16 MHz | 7.8                                                                                                                                                                                                                                                                                                                                                                                                     | 8.4   |      |

|                      | Wake up time from Stop 1<br>mode to Run mode in Flash              |                            | Wakeup clock MSI = 24 MHz   | 8.7                                                                                                                                                                                                                                                                                                                                                                                                     | 9.6   |      |

|                      |                                                                    | Range 2                    | Wakeup clock HSI16 = 16 MHz | 7.8                                                                                                                                                                                                                                                                                                                                                                                                     | 8.3   |      |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.4       9 $8.4$ 9 $4z$ $7.8$ $8.7$ $8.7$ 9 $4z$ $7.8$ $8.7$ $8.7$ $9.7$ $4z$ $7.8$ $8.7$ $8.0$ $12$ $5.5$ $5.7$ $4z$ $6.6$ $7.7$ $6.6$ $7.7$ $8.5$ $12$ $13.8$ $20$ $13.8$ $20$ $13.8$ $20$ $13.8$ $20$ $13.8$ $20$ $13.8$ $20$ $13.8$ $20$ $13.8$ $20$ $13.8$ $20$ $11.8$ $22$ $8.9$ $9.1$ $4z$ $8.2$ $9.3$ $10$ $4z$ $8.2$ $9.3$ $10$ $4z$ $7.2$ $8.4$ $16$ $15.3$ $23$ $21.3$ $30$ $15.3$ $23$ $2$ | 12.9  |      |

|                      |                                                                    | Dongo 1                    | Wakeup clock MSI = 48 MHz   | 5.5                                                                                                                                                                                                                                                                                                                                                                                                     | 5.9   |      |

|                      | Wake up time from Stop 1                                           | Range 1                    | Wakeup clock HSI16 = 16 MHz | 6.6                                                                                                                                                                                                                                                                                                                                                                                                     | 7.0   |      |

| t <sub>WUSTOP1</sub> | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 6.1                                                                                                                                                                                                                                                                                                                                                                                                     | 6.5   | μs   |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 6.6                                                                                                                                                                                                                                                                                                                                                                                                     | 7.0   |      |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.5                                                                                                                                                                                                                                                                                                                                                                                                     | 12.8  |      |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in Flash | Regulator in<br>low-power  |                             | 13.8                                                                                                                                                                                                                                                                                                                                                                                                    | 20.0  |      |

|                      | Wake up time from Stop 1<br>mode to Low-power run<br>mode in SRAM1 | mode (LPR=1<br>in PWR_CR1) | Wakeup clock MSI = 2 MHz    | 11.8                                                                                                                                                                                                                                                                                                                                                                                                    | 22.0  |      |

|                      |                                                                    | Danas 4                    | Wakeup clock MSI = 48 MHz   | 8.9                                                                                                                                                                                                                                                                                                                                                                                                     | 9.8   |      |

|                      |                                                                    | Range 1                    | Wakeup clock HSI16 = 16 MHz | 8.3                                                                                                                                                                                                                                                                                                                                                                                                     | 9.2   |      |

|                      | Wake up time from Stop 2<br>mode to Run mode in Flash              |                            | Wakeup clock MSI = 24 MHz   | 9.3                                                                                                                                                                                                                                                                                                                                                                                                     | 10.2  |      |

|                      |                                                                    | Range 2                    | Wakeup clock HSI16 = 16 MHz | 8.2                                                                                                                                                                                                                                                                                                                                                                                                     | 9.2   |      |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 14.2                                                                                                                                                                                                                                                                                                                                                                                                    | 16.1  |      |

| twustop2             |                                                                    | Danga 1                    | Wakeup clock MSI = 48 MHz   | 6.1                                                                                                                                                                                                                                                                                                                                                                                                     | 7.1   | μs   |

|                      | Wake up time from Stop 2                                           | Range 1                    | Wakeup clock HSI16 = 16 MHz | 7.2                                                                                                                                                                                                                                                                                                                                                                                                     | 8.1   |      |

|                      | mode to Run mode in                                                |                            | Wakeup clock MSI = 24 MHz   | 6.8                                                                                                                                                                                                                                                                                                                                                                                                     | 7.8   |      |

|                      | SRAM1                                                              | Range 2                    | Wakeup clock HSI16 = 16 MHz | 7.2                                                                                                                                                                                                                                                                                                                                                                                                     | 8.2   |      |

|                      |                                                                    |                            | Wakeup clock MSI = 4 MHz    | 8.4                                                                                                                                                                                                                                                                                                                                                                                                     | 16.7  |      |

| +                    | Wakeup time from Standby                                           | Range 1                    | Wakeup clock MSI = 8 MHz    | 15.3                                                                                                                                                                                                                                                                                                                                                                                                    | 23.2  | 110  |

| t <sub>WUSTBY</sub>  | mode to Run mode                                                   | Trange T                   | Wakeup clock MSI = 4 MHz    | 21.3                                                                                                                                                                                                                                                                                                                                                                                                    | 30.5  | μs   |

| t <sub>WUSTBY</sub>  | Wakeup time from Standby                                           | Range 1                    | Wakeup clock MSI = 8 MHz    | 15.3                                                                                                                                                                                                                                                                                                                                                                                                    | 23.1  | 118  |

| SRAM2                | with SRAM2 to Run mode                                             |                            | Wakeup clock MSI = 4 MHz    | 21.3                                                                                                                                                                                                                                                                                                                                                                                                    | 30.6  | μs   |

| t <sub>WUSHDN</sub>  | Wakeup time from<br>Shutdown mode to Run<br>mode                   | Range 1                    | Wakeup clock MSI = 4 MHz    | 305.9                                                                                                                                                                                                                                                                                                                                                                                                   | 322.3 | μs   |

Table 51. Low-power mode wakeup timings<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

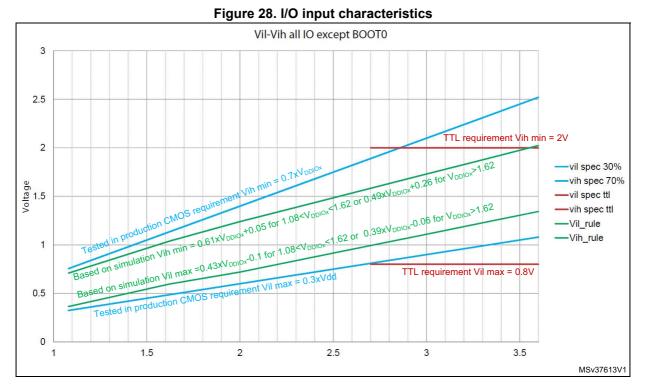

All I/Os are CMOS- and TTL-compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 28* for standard I/Os, and in *Figure 28* for 5 V tolerant I/Os.

#### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to ±8 mA, and sink or source up to ± 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 19: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 19: Voltage characteristics*).

|             | 145               | ne ou. Abo accuracy - m                        |                          |                          | nava | /   |     |      |

|-------------|-------------------|------------------------------------------------|--------------------------|--------------------------|------|-----|-----|------|

| Sym-<br>bol | Parameter         | C                                              | Conditions <sup>(4</sup> | )                        | Min  | Тур | Max | Unit |

|             |                   | ADC clock frequency ≤                          | Single                   | Fast channel (max speed) | -    | -71 | -69 |      |

| THD         | Total<br>harmonic | 26 MHz,<br>1.65 V ≤ V <sub>DDA</sub> = VREF+ ≤ | ended                    | Slow channel (max speed) | -    | -71 | -69 | dB   |

|             | distortion        | 3.6 V,                                         | Differential             | Fast channel (max speed) | -    | -73 | -72 | uВ   |

|             |                   | Voltage scaling Range 2                        | Differential             | Slow channel (max speed) | -    | -73 | -72 |      |

Table 80. ADC accuracy - limited test conditions  $4^{(1)(2)(3)}$  (continued)

1. Guaranteed by design.

2. ADC DC accuracy values are measured after internal calibration.

- 3. ADC accuracy vs. negative Injection Current: Injecting negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative current.

- 4. The I/O analog switch voltage booster is enable when V<sub>DDA</sub> < 2.4 V (BOOSTEN = 1 in the SYSCFG\_CFGR1 when V<sub>DDA</sub> < 2.4 V). It is disable when V<sub>DDA</sub>  $\geq$  2.4 V. No oversampling.

| Symbol                  | Parameter                                       | Co                       | onditions                                         | Min | Тур  | Max  | Unit |

|-------------------------|-------------------------------------------------|--------------------------|---------------------------------------------------|-----|------|------|------|

|                         |                                                 |                          | Static                                            | -   | 400  | 600  |      |

|                         |                                                 | Ultra-low-<br>power mode | With 50 kHz<br>±100 mV overdrive<br>square signal | -   | 1200 | -    | nA   |

|                         |                                                 |                          | Static                                            | -   | 5    | 7    |      |

| I <sub>DDA</sub> (COMP) | Comparator consumption<br>from V <sub>DDA</sub> | Medium mode              | With 50 kHz<br>±100 mV overdrive<br>square signal | -   | 6    | -    | μA   |

|                         |                                                 |                          | Static                                            | -   | 70   | 100  | μΛ   |

|                         |                                                 | High-speed<br>mode       | With 50 kHz<br>±100 mV overdrive<br>square signal | -   | 75   | -    |      |

| I <sub>bias</sub>       | Comparator input bias current                   |                          | -                                                 | -   | -    | _(4) | nA   |

| Table 84. COMF | characteristics <sup>(1)</sup> | (continued) |

|----------------|--------------------------------|-------------|

|----------------|--------------------------------|-------------|

1. Guaranteed by design, unless otherwise specified.

2. Refer to Table 25: Embedded internal voltage reference.

3. Guaranteed by characterization results.

4. Mostly I/O leakage when used in analog mode. Refer to  $I_{lkg}$  parameter in Table 70: I/O static characteristics.

## 6.3.21 Operational amplifiers characteristics

| Table 85. | OPAMP                                   | characteristics <sup>(1)</sup> |

|-----------|-----------------------------------------|--------------------------------|

|           | • • • • • • • • • • • • • • • • • • • • |                                |

| Symbol                       | Parameter                                                                        | Conditions                | Min | Тур | Мах              | Unit  |

|------------------------------|----------------------------------------------------------------------------------|---------------------------|-----|-----|------------------|-------|

| V <sub>DDA</sub>             | Analog supply voltage                                                            | -                         | 1.8 | -   | 3.6              | V     |

| CMIR                         | Common mode input range                                                          | -                         | 0   | -   | V <sub>DDA</sub> | V     |

| M                            | Input offset<br>voltage                                                          | 25 °C, No Load on output. | -   | -   | ±1.5             | mV    |

| VI <sub>OFFSET</sub>         |                                                                                  | All voltage/Temp.         | -   | -   | ±3               |       |

| ΔVI <sub>OFFSET</sub>        | Input offset<br>voltage drift                                                    | Normal mode               | -   | ±5  | -                | μV/°C |

|                              |                                                                                  | Low-power mode            | -   | ±10 | -                |       |

| TRIMOFFSETP<br>TRIMLPOFFSETP | Offset trim step<br>at low common<br>input voltage<br>(0.1 x V <sub>DDA</sub> )  | -                         | -   | 0.8 | 1.1              | mV    |

| TRIMOFFSETN<br>TRIMLPOFFSETN | Offset trim step<br>at high common<br>input voltage<br>(0.9 x V <sub>DDA</sub> ) | -                         | -   | 1   | 1.35             | ΠV    |

| Symbol                                  | Parameter                                     | Con            | Min                                         | Тур | Max | Unit |        |

|-----------------------------------------|-----------------------------------------------|----------------|---------------------------------------------|-----|-----|------|--------|

| en Voltage noise<br>density             |                                               | Normal mode    | at 1 kHz, Output loaded with 4 k $\Omega$   | -   | 500 | -    | nV/√Hz |

|                                         | Voltage noise                                 | Low-power mode | at 1 kHz, Output<br>loaded with 20 kΩ       | -   | 600 | -    |        |

|                                         | density                                       | Normal mode    | at 10 kHz, Output<br>loaded with 4 kΩ       | -   | 180 | -    |        |

|                                         |                                               | Low-power mode | at 10 kHz, Output loaded with 20 k $\Omega$ | -   | 290 | -    |        |

| I <sub>DDA</sub> (OPAMP) <sup>(2)</sup> | OPAMP<br>consumption<br>from V <sub>DDA</sub> | Normal mode    | no Load, quiescent mode                     | -   | 120 | 260  | μA     |

|                                         |                                               | Low-power mode |                                             | -   | 45  | 100  |        |

| Table 85. | OPAMP | characteristics <sup>(1)</sup> | (continued) |

|-----------|-------|--------------------------------|-------------|

|-----------|-------|--------------------------------|-------------|

1. Guaranteed by design, unless otherwise specified.

2. Guaranteed by characterization results.

3. Mostly I/O leakage, when used in analog mode. Refer to IIkg parameter in Table 70: I/O static characteristics.

4. R2 is the internal resistance between OPAMP output and OPAMP inverting input. R1 is the internal resistance between OPAMP inverting input and ground. The PGA gain =1+R2/R1

| Symbol                    | Parameter                                 | Min                     | Мах                     | Unit |

|---------------------------|-------------------------------------------|-------------------------|-------------------------|------|

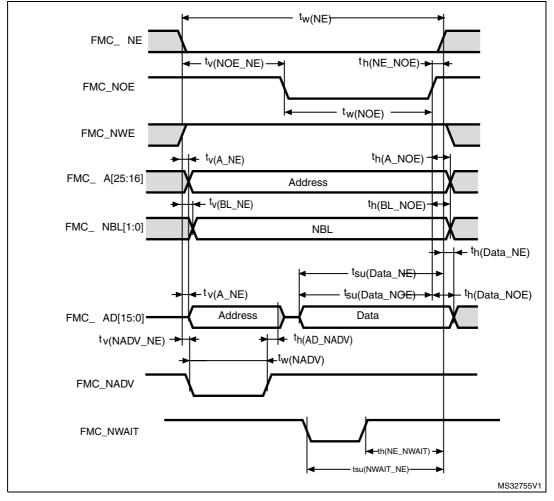

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> -1   | 8T <sub>HCLK</sub> +1   |      |

| t <sub>w(NWE)</sub>       | FMC_NWE low time                          | 6T <sub>HCLK</sub> -1.5 | 6T <sub>HCLK</sub> +0.5 |      |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 6T <sub>HCLK</sub> -1   | -                       | ns   |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> +2   | -                       |      |

Table 105. Asynchronous non-multiplexed SRAM/PSRAM/NOR write-NWAIT timings<sup>(1)(2)</sup>

1. CL = 30 pF.

2. Guaranteed by characterization results.

#### Figure 45. Asynchronous multiplexed PSRAM/NOR read waveforms

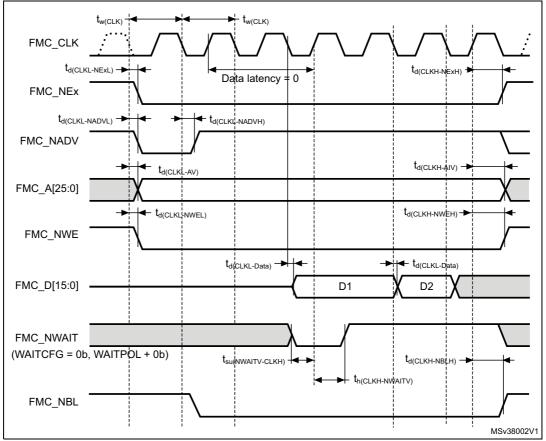

# Table 112. Synchronous non-multiplexed NOR/PSRAM read timings<sup>(1)(2)</sup> (continued)

| Symbol                      | Parameter                           | Min | Max | Unit |

|-----------------------------|-------------------------------------|-----|-----|------|

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high | 2   | -   | ns   |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high  | 3.5 | -   | 113  |

1. CL = 30 pF.

2. Guaranteed by characterization results.

#### Figure 50. Synchronous non-multiplexed PSRAM write timings

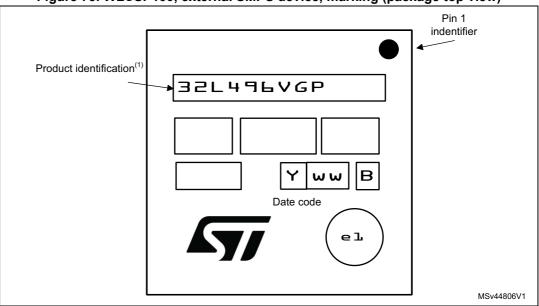

Figure 75. WLCSP100, external SMPS device, marking (package top view)

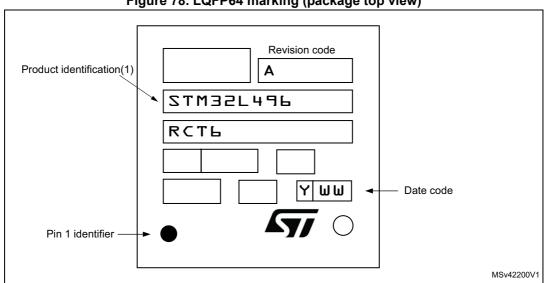

Figure 78. LQFP64 marking (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity. 1.