Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 34                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega32a4u-aur |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 12. System Control and Reset

## 12.1 Features

- Reset the microcontroller and set it to initial state when a reset source goes active

- Multiple reset sources that cover different situations

- Power-on reset

- External reset

- Watchdog reset

- Brownout reset

- PDI reset

- Software reset

- Asynchronous operation

- No running system clock in the device is required for reset

- Reset status register for reading the reset source from the application code

## 12.2 Overview

The reset system issues a microcontroller reset and sets the device to its initial state. This is for situations where operation should not start or continue, such as when the microcontroller operates below its power supply rating. If a reset source goes active, the device enters and is kept in reset until all reset sources have released their reset. The I/O pins are immediately tri-stated. The program counter is set to the reset vector location, and all I/O registers are set to their initial values. The SRAM content is kept. However, if the device accesses the SRAM when a reset occurs, the content of the accessed location can not be guaranteed.

After reset is released from all reset sources, the default oscillator is started and calibrated before the device starts running from the reset vector address. By default, this is the lowest program memory address, 0, but it is possible to move the reset vector to the lowest address in the boot section.

The reset functionality is asynchronous, and so no running system clock is required to reset the device. The software reset feature makes it possible to issue a controlled system reset from the user software.

The reset status register has individual status flags for each reset source. It is cleared at power-on reset, and shows which sources have issued a reset since the last power-on.

## 12.3 Reset Sequence

A reset request from any reset source will immediately reset the device and keep it in reset as long as the request is active. When all reset requests are released, the device will go through three stages before the device starts running again:

- Reset counter delay

- Oscillator startup

- Oscillator calibration

If another reset requests occurs during this process, the reset sequence will start over again.

## 12.4 Reset Sources

## 12.4.1 Power-on Reset

A power-on reset (POR) is generated by an on-chip detection circuit. The POR is activated when the  $V_{CC}$  rises and reaches the POR threshold voltage ( $V_{POT}$ ), and this will start the reset sequence.

The POR is also activated to power down the device properly when the  $V_{CC}$  falls and drops below the  $V_{POT}$  level.

The  $V_{POT}$  level is higher for falling  $V_{CC}$  than for rising  $V_{CC}$ . Consult the datasheet for POR characteristics data.

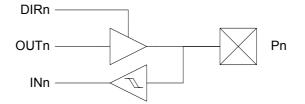

### 15.3.1 Push-pull

Figure 15-1. I/O configuration - Totem-pole.

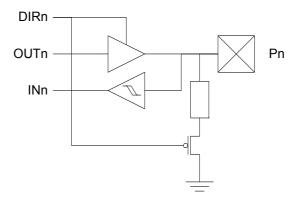

## 15.3.2 Pull-down

Figure 15-2. I/O configuration - Totem-pole with pull-down (on input).

#### 15.3.3 Pull-up

Figure 15-3. I/O configuration - Totem-pole with pull-up (on input).

#### 15.3.4 Bus-keeper

The bus-keeper's weak output produces the same logical level as the last output level. It acts as a pull-up if the last level was '1', and pull-down if the last level was '0'.

PORTC and PORTE each has one TWI. Notation of these peripherals are TWIC and TWIE.

# 23. SPI – Serial Peripheral Interface

## 23.1 Features

- Two Identical SPI peripherals

- Full-duplex, three-wire synchronous data transfer

- Master or slave operation

- Lsb first or msb first data transfer

- Eight programmable bit rates

- Interrupt flag at the end of transmission

- Write collision flag to indicate data collision

- Wake up from idle sleep mode

- Double speed master mode

## 23.2 Overview

The Serial Peripheral Interface (SPI) is a high-speed synchronous data transfer interface using three or four pins. It allows fast communication between an Atmel AVR XMEGA device and peripheral devices or between several microcontrollers. The SPI supports full-duplex communication.

A device connected to the bus must act as a master or slave. The master initiates and controls all data transactions.

PORTC and PORTD each has one SPI. Notation of these peripherals are SPIC and SPID.

# 24. USART

## 24.1 Features

- Five identical USART peripherals

- Full-duplex operation

- Asynchronous or synchronous operation

- Synchronous clock rates up to 1/2 of the device clock frequency

- Asynchronous clock rates up to 1/8 of the device clock frequency

- Supports serial frames with 5, 6, 7, 8, or 9 data bits and 1 or 2 stop bits

- Fractional baud rate generator

- Can generate desired baud rate from any system clock frequency

- No need for external oscillator with certain frequencies

- Built-in error detection and correction schemes

- Odd or even parity generation and parity check

- Data overrun and framing error detection

- Noise filtering includes false start bit detection and digital low-pass filter

- Separate interrupts for

- Transmit complete

- Transmit data register empty

- Receive complete

- Multiprocessor communication mode

- Addressing scheme to address a specific devices on a multidevice bus

- Enable unaddressed devices to automatically ignore all frames

- Master SPI mode

- Double buffered operation

- Operation up to 1/2 of the peripheral clock frequency

- IRCOM module for IrDA compliant pulse modulation/demodulation

## 24.2 Overview

The universal synchronous and asynchronous serial receiver and transmitter (USART) is a fast and flexible serial communication module. The USART supports full-duplex communication and asynchronous and synchronous operation. The USART can be configured to operate in SPI master mode and used for SPI communication.

Communication is frame based, and the frame format can be customized to support a wide range of standards. The USART is buffered in both directions, enabling continued data transmission without any delay between frames. Separate interrupts for receive and transmit complete enable fully interrupt driven communication. Frame error and buffer overflow are detected in hardware and indicated with separate status flags. Even or odd parity generation and parity check can also be enabled.

The clock generator includes a fractional baud rate generator that is able to generate a wide range of USART baud rates from any system clock frequencies. This removes the need to use an external crystal oscillator with a specific frequency to achieve a required baud rate. It also supports external clock input in synchronous slave operation.

When the USART is set in master SPI mode, all USART-specific logic is disabled, leaving the transmit and receive buffers, shift registers, and baud rate generator enabled. Pin control and interrupt generation are identical in both modes. The registers are used in both modes, but their functionality differs for some control settings.

An IRCOM module can be enabled for one USART to support IrDA 1.4 physical compliant pulse modulation and demodulation for baud rates up to 115.2Kbps.

PORTC and PORTD each has two USARTs. PORTE has one USART. Notation of these peripherals are USARTC0, USARTC1, USARTD0, USARTD1 and USARTE0, respectively.

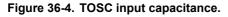

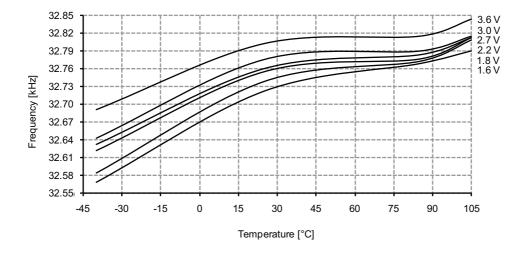

#### 36.1.14.8 External 32.768kHz crystal oscillator and TOSC characteristics

| Symbol             | Parameter                                              | Condition                                         | Min. | Тур. | Max. | Units |

|--------------------|--------------------------------------------------------|---------------------------------------------------|------|------|------|-------|

| ESR/R1             | Recommended crystal equivalent series resistance (ESR) | Crystal load capacitance 6.5pF                    |      |      | 60   | 1.0   |

|                    |                                                        | Crystal load capacitance 9.0pF                    |      |      | 35   | kΩ    |

| <u> </u>           | Parasitic capacitance TOSC1 pin                        |                                                   |      | 5.4  |      | pF    |

| C <sub>TOSC1</sub> |                                                        | Alternate TOSC location                           |      | 4.0  |      |       |

| C <sub>TOSC2</sub> | Parasitic capacitance TOSC2 pin                        |                                                   |      | 7.1  |      | pF    |

|                    |                                                        | Alternate TOSC location                           |      | 4.0  |      |       |

|                    | Recommended safety factor                              | capacitance load matched to crystal specification | 3    |      |      |       |

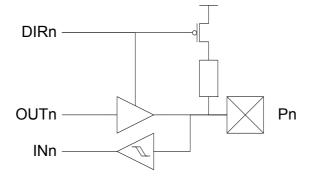

Note: 1. See Figure 36-4 for definition.

The parasitic capacitance between the TOSC pins is  $C_{L1} + C_{L2}$  in series as seen from the crystal when oscillating without external capacitors.

## 36.2.14.5 Internal Phase Locked Loop (PLL) characteristics

Table 36-58. Internal PLL characteristics.

| Symbo<br>I       | Parameter                       | Condition                                                 | Min. | Тур. | Max. | Units |

|------------------|---------------------------------|-----------------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>  | Input frequency                 | Output frequency must be within $\mathbf{f}_{\text{OUT}}$ | 0.4  |      | 64   | MHz   |

| f <sub>оит</sub> | Output frequency <sup>(1)</sup> | V <sub>CC</sub> = 1.6 - 1.8V                              | 20   |      | 48   | MHz   |

|                  |                                 | V <sub>CC</sub> = 2.7 - 3.6V                              | 20   |      | 128  |       |

|                  | Start-up time                   |                                                           |      | 25   |      | μs    |

|                  | Re-lock time                    |                                                           |      | 25   |      | μs    |

Note: 1. The maximum output frequency vs. supply voltage is linear between 1.8V and 2.7V, and can never be higher than four times the maximum CPU frequency.

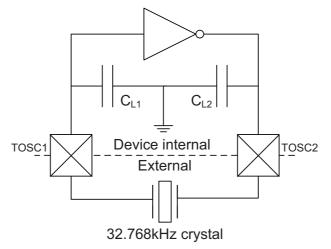

36.2.14.6 External clock characteristics

Table 36-59. External clock used as system clock without prescaling.

| Symbol              | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units |

|---------------------|---------------------------------------------------|------------------------------|------|------|------|-------|

| 1/t <sub>CK</sub> С | Clock Frequency <sup>(1)</sup>                    | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 12   | MHz   |

|                     | Clock Frequency W                                 | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 32   |       |

| +                   | Clock Period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 83.3 |      |      | ns    |

| t <sub>ск</sub>     | CIUCK FEIIOU                                      | V <sub>CC</sub> = 2.7 - 3.6V | 31.5 |      |      | - 115 |

| +                   | Clock High Time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      | 20    |

| t <sub>CH</sub>     |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | ns    |

| +                   | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      | 20    |

| t <sub>CL</sub>     |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | ns    |

| 4                   | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |       |

| t <sub>CR</sub>     |                                                   | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    | ns    |

| t <sub>CF</sub>     | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |       |

|                     |                                                   | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    | ns    |

| $\Delta t_{CK}$     | Change in period from one clock cycle to the next |                              |      |      | 10   | %     |

Note: 1. The maximum frequency vs. supply voltage is linear between 1.6V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

#### Table 36-106. Accuracy characteristics.

| Symbol             | Parameter                  | Condition <sup>(2)</sup>                                                            |                                                         | Min. | Тур.  | Max.   | Units     |

|--------------------|----------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------|------|-------|--------|-----------|

| RES                | Resolution                 | Programmable to 8 or 12 bit                                                         |                                                         | 8    | 12    | 12     | Bits      |

|                    | Integral non-linearity     | 500ksps                                                                             | $V_{\rm CC}$ -1.0V < $V_{\rm REF}$ < $V_{\rm CC}$ -0.6V |      | ±1.2  | ±2     | lsb       |

| INL <sup>(1)</sup> |                            |                                                                                     | All V <sub>REF</sub>                                    |      | ±1.5  | ±3     |           |

|                    |                            | 2000ksps                                                                            | $V_{\rm CC}$ -1.0V < $V_{\rm REF}$ < $V_{\rm CC}$ -0.6V |      | ±1.0  | ±2     |           |

|                    |                            | 20008505                                                                            | All V <sub>REF</sub>                                    |      | ±1.5  | ±3     |           |

| DNL <sup>(1)</sup> | Differential non-linearity | gu                                                                                  | aranteed monotonic                                      |      | <±0.8 | <±1    | lsb       |

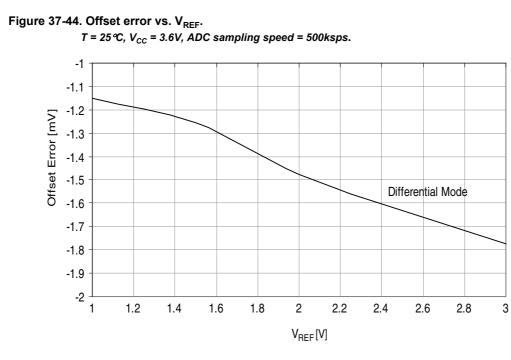

|                    |                            |                                                                                     |                                                         |      | -1.0  |        | mV        |

|                    | Offset error               | Temperature drift                                                                   |                                                         |      | <0.01 |        | mV/K      |

|                    |                            | Operating voltage drift                                                             |                                                         |      | <0.6  |        | mV/V      |

|                    |                            |                                                                                     | External reference                                      |      | -1    |        | mV        |

|                    |                            | Differential                                                                        | AV <sub>CC</sub> /1.6                                   |      | 10    |        |           |

|                    |                            | AV <sub>CC</sub> /2.0                                                               |                                                         | 8.0  |       | - 111V |           |

|                    |                            |                                                                                     | Bandgap                                                 |      | ±5    |        |           |

|                    |                            | Temperature drift                                                                   |                                                         |      | <0.02 |        | mV/K      |

|                    |                            | Operating voltage drift                                                             |                                                         |      | <0.5  |        | mV/V      |

|                    | Noise                      | Differential mode, shorted input 2msps, $V_{CC}$ = 3.6V, Clk <sub>PER</sub> = 16MHz |                                                         |      | 0.4   |        | mV<br>rms |

Notes: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

2. Unless otherwise noted all linearity, offset and gain error numbers are valid under the condition that external V<sub>REF</sub> is used.

## Table 36-107. Gain stage characteristics.

| Symbol              | Parameter              | Condition                                | Min.              | Тур. | Max.                  | Units                        |     |

|---------------------|------------------------|------------------------------------------|-------------------|------|-----------------------|------------------------------|-----|

| R <sub>in</sub>     | Input resistance       | Switched in normal mode                  |                   | 4.0  |                       | kΩ                           |     |

| C <sub>sample</sub> | Input capacitance      | Switched in normal mode                  |                   | 4.4  |                       | pF                           |     |

|                     | Signal range           | Gain stage output                        | 0                 |      | V <sub>CC</sub> - 0.6 | V                            |     |

|                     | Propagation delay      | ADC conversion rate                      |                   | 1.0  |                       | Clk <sub>ADC</sub><br>cycles |     |

|                     | Sample rate            | Same as ADC                              | 100               |      | 1000                  | kHz                          |     |

| INL <sup>(1)</sup>  | Integral Non-Linearity | 500ksps                                  | All gain settings |      | ±1.5                  | ±4.0                         | lsb |

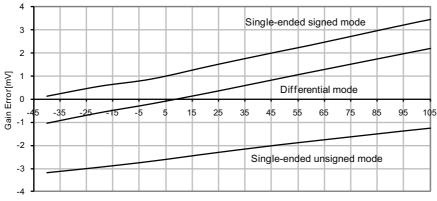

|                     |                        | 1x gain, normal mode8x gain, normal mode |                   |      | -0.8                  |                              |     |

|                     | Gain error             |                                          |                   |      | -2.5                  |                              | %   |

|                     |                        | 64x gain, normal mode                    |                   |      | -3.5                  |                              |     |

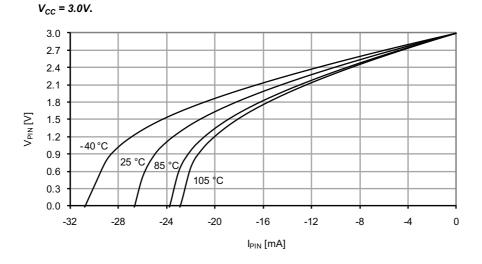

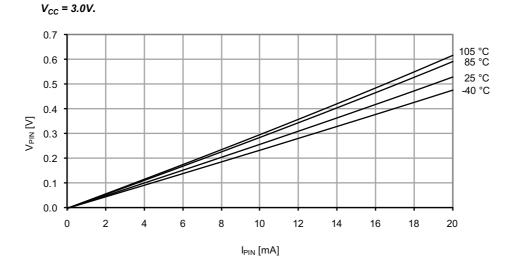

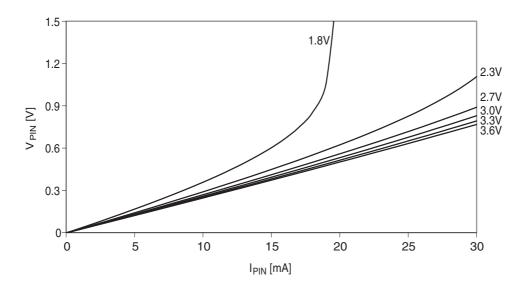

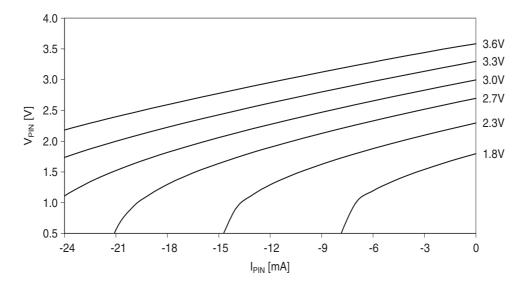

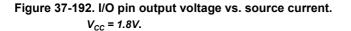

Figure 37-25. I/O pin output voltage vs. source current.

Figure 37-26. I/O pin output voltage vs. source current.

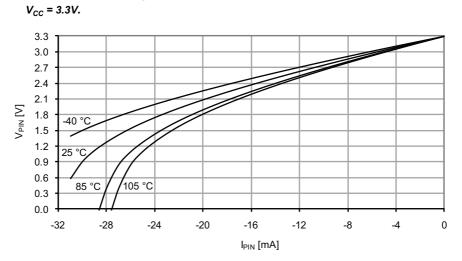

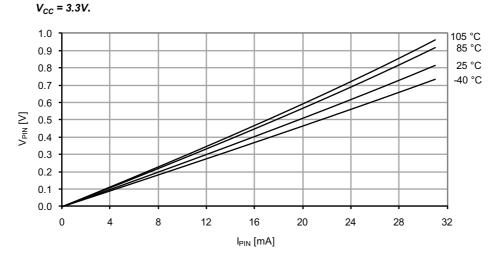

Figure 37-29. I/O pin output voltage vs. sink current.

Figure 37-30. I/O pin output voltage vs. sink current.

Figure 37-31. I/O pin output voltage vs. sink current.

Figure 37-45. Gain error vs. temperature.  $V_{CC}$  = 3.0V,  $V_{REF}$  = external 2.0V.

Temperature [°C]

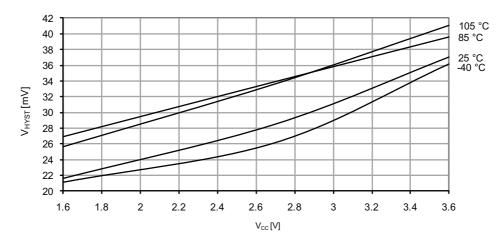

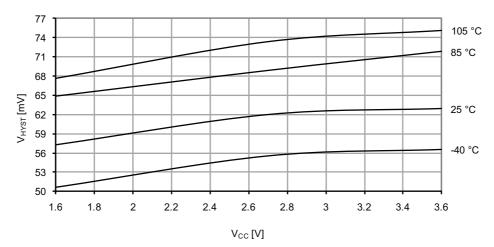

Figure 37-54. Analog comparator hysteresis vs. V<sub>CC</sub>. *High-speed mode, large hysteresis.*

Figure 37-55. Analog comparator hysteresis vs. V<sub>CC</sub>. Low power, large hysteresis.

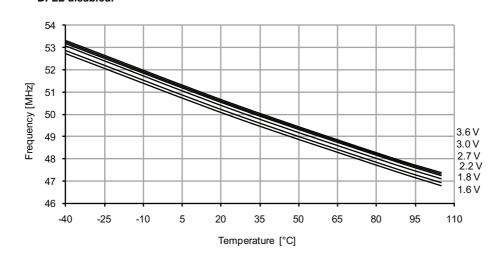

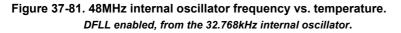

#### 37.1.10.5 32MHz internal oscillator calibrated to 48MHz

Figure 37-80. 48MHz internal oscillator frequency vs. temperature. DFLL disabled.

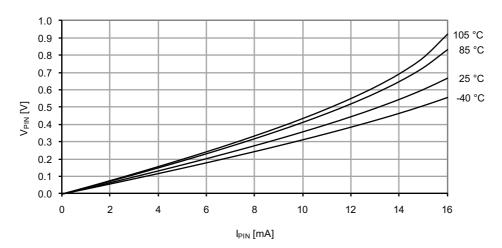

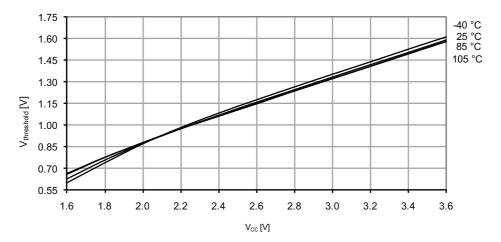

Figure 37-111. I/O pin output voltage vs. source current.

Figure 37-112. I/O pin output voltage vs. sink current.  $V_{CC} = 1.8V$ .

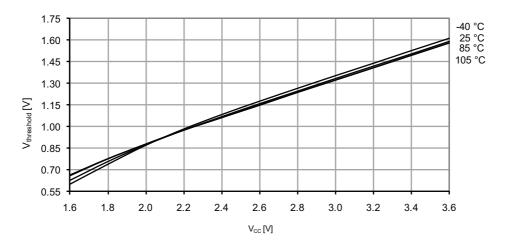

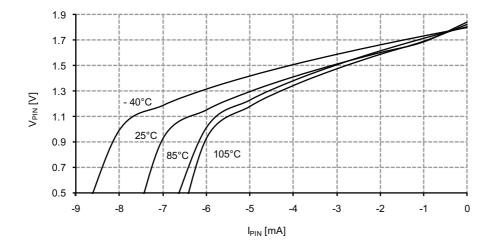

Figure 37-118. I/O pin input threshold voltage vs.  $V_{CC}$ .  $V_{IL}$  I/O pin read as "0".

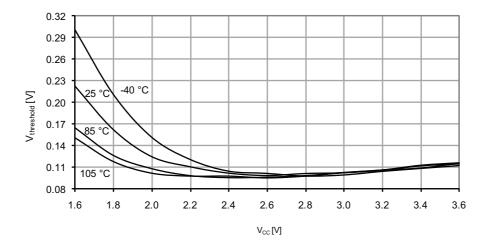

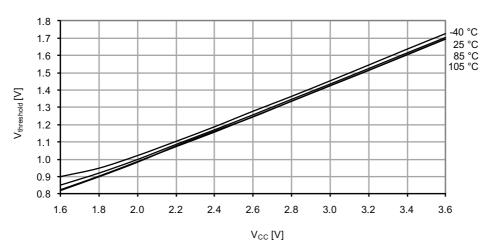

Figure 37-119. I/O pin input hysteresis vs.  $\rm V_{\rm CC}.$

#### 37.2.10.4 32MHz Internal Oscillator

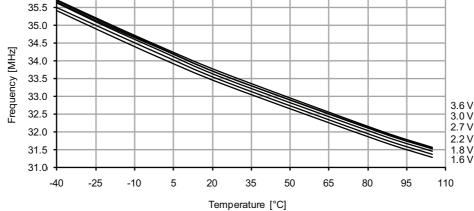

Figure 37-160. 32MHz internal oscillator frequency vs. temperature.

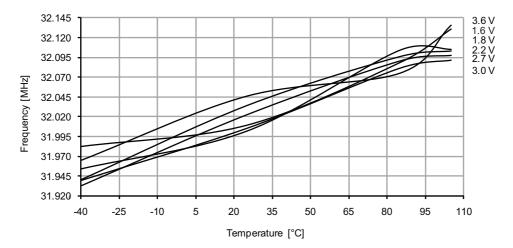

Figure 37-161. 32MHz internal oscillator frequency vs. temperature. DFLL enabled, from the 32.768kHz internal oscillator.

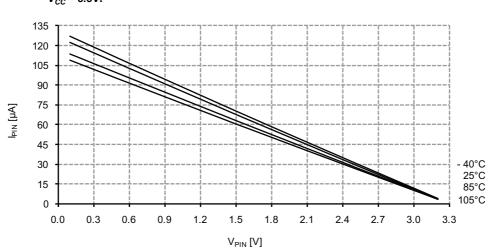

Figure 37-191. I/O pin pull-up resistor current vs. input voltage.  $V_{CC}$  = 3.3V.

## 37.3.2.2 Output Voltage vs. Sink/Source Current

Figure 37-201. I/O pin input threshold voltage vs.  $V_{CC}$ .  $V_{IH}$  I/O pin read as "1".

Figure 37-202. I/O pin input threshold voltage vs.  $V_{CC}$ .  $V_{lL}$  I/O pin read as "0".

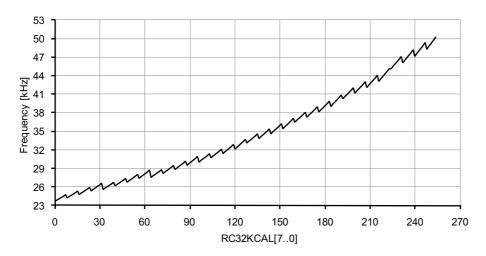

Figure 37-240. 32.768kHz internal oscillator frequency vs. calibration value.  $V_{cc} = 3.0V, T = 25^{\circ}C.$

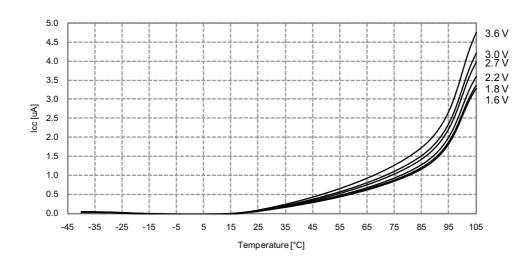

#### 37.4.1.3 Power-down mode supply current

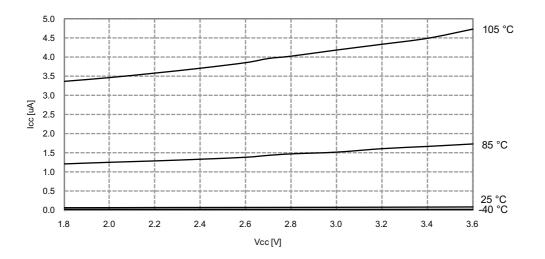

Figure 37-268. Power-down mode supply current vs. V<sub>CC</sub>. All functions disabled