Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

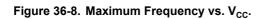

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 49-VFBGA                                                                  |

| Supplier Device Package    | 49-VFBGA (5x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega32a4u-cu |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 7.8 Data Memory and Bus Arbitration

Since the data memory is organized as four separate sets of memories, the different bus masters (CPU, DMA controller read and DMA controller write, etc.) can access different memory sections at the same time.

## 7.9 Memory Timing

Read and write access to the I/O memory takes one CPU clock cycle. A write to SRAM takes one cycle, and a read from SRAM takes two cycles. For burst read (DMA), new data are available every cycle. EEPROM page load (write) takes one cycle, and three cycles are required for read. For burst read, new data are available every second cycle. Refer to the instruction summary for more details on instructions and instruction timing.

## 7.10 Device ID and Revision

Each device has a three-byte device ID. This ID identifies Atmel as the manufacturer of the device and the device type. A separate register contains the revision number of the device.

## 7.11 I/O Memory Protection

Some features in the device are regarded as critical for safety in some applications. Due to this, it is possible to lock the I/O register related to the clock system, the event system, and the advanced waveform extensions. As long as the lock is enabled, all related I/O registers are locked and they can not be written from the application software. The lock registers themselves are protected by the configuration change protection mechanism.

## 7.12 Flash and EEPROM Page Size

The flash program memory and EEPROM data memory are organized in pages. The pages are word accessible for the flash and byte accessible for the EEPROM.

Table 7-3 on page 17 shows the Flash Program Memory organization and Program Counter (PC) size. Flash write and erase operations are performed on one page at a time, while reading the Flash is done one byte at a time. For Flash access the Z-pointer (Z[m:n]) is used for addressing. The most significant bits in the address (FPAGE) give the page number and the least significant address bits (FWORD) give the word in the page.

| Devices       | PC size | Flash size | Page Size | FWORD  | FPAGE   | Application |             | Boot |             |

|---------------|---------|------------|-----------|--------|---------|-------------|-------------|------|-------------|

|               | bits    | bytes      | words     |        |         | Size        | No of pages | Size | No of pages |

| ATxmega16A4U  | 14      | 16K + 4K   | 128       | Z[6:0] | Z[13:7] | 16K         | 64          | 4K   | 16          |

| ATxmega32A4U  | 15      | 32K + 4K   | 128       | Z[6:0] | Z[14:7] | 32K         | 128         | 4K   | 16          |

| ATxmega64A4U  | 16      | 64K + 4K   | 128       | Z[6:0] | Z[15:7] | 64K         | 256         | 4K   | 16          |

| ATxmega128A4U | 17      | 128K + 8K  | 128       | Z[6:0] | Z[16:7] | 128K        | 512         | 8K   | 32          |

#### Table 7-3. Number of words and pages in the flash.

Table 7-4 shows EEPROM memory organization for the Atmel AVR XMEGA A4U devices. EEEPROM write and erase operations can be performed one page or one byte at a time, while reading the EEPROM is done one byte at a time. For EEPROM access the NVM address register (ADDR[m:n]) is used for addressing. The most significant bits in the address (E2PAGE) give the page number and the least significant address bits (E2BYTE) give the byte in the page.

# 8. DMAC – Direct Memory Access Controller

## 8.1 Features

- Allows high speed data transfers with minimal CPU intervention

- from data memory to data memory

- from data memory to peripheral

- from peripheral to data memory

- from peripheral to peripheral

- Four DMA channels with separate

- transfer triggers

- interrupt vectors

- addressing modes

- Programmable channel priority

- From 1 byte to 16MB of data in a single transaction

- Up to 64KB block transfers with repeat

- 1, 2, 4, or 8 byte burst transfers

- Multiple addressing modes

- Static

- Incremental

- Decremental

- Optional reload of source and destination addresses at the end of each

- Burst

- Block

- Transaction

- Optional interrupt on end of transaction

- Optional connection to CRC generator for CRC on DMA data

## 8.2 Overview

The four-channel direct memory access (DMA) controller can transfer data between memories and peripherals, and thus offload these tasks from the CPU. It enables high data transfer rates with minimum CPU intervention, and frees up CPU time. The four DMA channels enable up to four independent and parallel transfers.

The DMA controller can move data between SRAM and peripherals, between SRAM locations and directly between peripheral registers. With access to all peripherals, the DMA controller can handle automatic transfer of data to/from communication modules. The DMA controller can also read from memory mapped EEPROM.

Data transfers are done in continuous bursts of 1, 2, 4, or 8 bytes. They build block transfers of configurable size from 1 byte to 64KB. A repeat counter can be used to repeat each block transfer for single transactions up to 16MB. Source and destination addressing can be static, incremental or decremental. Automatic reload of source and/or destination addresses can be done after each burst or block transfer, or when a transaction is complete. Application software, peripherals, and events can trigger DMA transfers.

The four DMA channels have individual configuration and control settings. This include source, destination, transfer triggers, and transaction sizes. They have individual interrupt settings. Interrupt requests can be generated when a transaction is complete or when the DMA controller detects an error on a DMA channel.

To allow for continuous transfers, two channels can be interlinked so that the second takes over the transfer when the first is finished, and vice versa.

## 14. Interrupts and Programmable Multilevel Interrupt Controller

## 14.1 Features

- Short and predictable interrupt response time

- Separate interrupt configuration and vector address for each interrupt

- Programmable multilevel interrupt controller

- Interrupt prioritizing according to level and vector address

- Three selectable interrupt levels for all interrupts: low, medium and high

- Selectable, round-robin priority scheme within low-level interrupts

- Non-maskable interrupts for critical functions

- Interrupt vectors optionally placed in the application section or the boot loader section

## 14.2 Overview

Interrupts signal a change of state in peripherals, and this can be used to alter program execution. Peripherals can have one or more interrupts, and all are individually enabled and configured. When an interrupt is enabled and configured, it will generate an interrupt request when the interrupt condition is present. The programmable multilevel interrupt controller (PMIC) controls the handling and prioritizing of interrupt requests. When an interrupt request is acknowledged by the PMIC, the program counter is set to point to the interrupt vector, and the interrupt handler can be executed.

All peripherals can select between three different priority levels for their interrupts: low, medium, and high. Interrupts are prioritized according to their level and their interrupt vector address. Medium-level interrupts will interrupt low-level interrupt handlers. High-level interrupts will interrupt both medium- and low-level interrupt handlers. Within each level, the interrupt priority is decided from the interrupt vector address, where the lowest interrupt vector address has the highest interrupt priority. Low-level interrupts have an optional round-robin scheduling scheme to ensure that all interrupts are serviced within a certain amount of time.

Non-maskable interrupts (NMI) are also supported, and can be used for system critical functions.

## 14.3 Interrupt vectors

The interrupt vector is the sum of the peripheral's base interrupt address and the offset address for specific interrupts in each peripheral. The base addresses for the Atmel AVR XMEGA A4U devices are shown in Table 14-1 on page 30. Offset addresses for each interrupt available in the peripheral are described for each peripheral in the XMEGA AU manual. For peripherals or modules that have only one interrupt, the interrupt vector is shown in Table 14-1 on page 30. The program address is the word address.

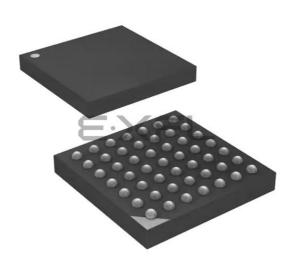

## 15.4 Input sensing

Input sensing is synchronous or asynchronous depending on the enabled clock for the ports, and the configuration is shown in Figure 15-7.

#### Figure 15-7. Input sensing system overview.

When a pin is configured with inverted I/O, the pin value is inverted before the input sensing.

## 15.5 Alternate Port Functions

Most port pins have alternate pin functions in addition to being a general purpose I/O pin. When an alternate function is enabled, it might override the normal port pin function or pin value. This happens when other peripherals that require pins are enabled or configured to use pins. If and how a peripheral will override and use pins is described in the section for that peripheral. "Pinout and Pin Functions" on page 55 shows which modules on peripherals that enable alternate functions on a pin, and which alternate functions that are available on a pin.

#### 36.3.5 I/O Pin Characteristics

The I/O pins comply with the JEDEC LVTTL and LVCMOS specification and the high- and low level input and output voltage limits reflect or exceed this specification.

## Table 36-71. I/O pin characteristics.

| Symbol                                                             | Parameter                             | Con                          | dition                 | Min.                | Тур.                 | Max.                 | Units |

|--------------------------------------------------------------------|---------------------------------------|------------------------------|------------------------|---------------------|----------------------|----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current           |                              |                        | -20                 |                      | 20                   | mA    |

|                                                                    |                                       | V <sub>CC</sub> = 2.7- 3.6V  |                        | 2.0                 |                      | V <sub>CC</sub> +0.3 |       |

| V <sub>IH</sub>                                                    | High level input voltage              | V <sub>CC</sub> = 2.0 - 2.7V |                        | 0.7*V <sub>CC</sub> |                      | V <sub>CC</sub> +0.3 | V     |

|                                                                    |                                       | V <sub>CC</sub> = 1.6 - 2.0V |                        | 0.8*V <sub>CC</sub> |                      | V <sub>CC</sub> +0.3 |       |

|                                                                    |                                       | V <sub>CC</sub> = 2.7- 3.6V  |                        | -0.3                |                      | 0.8                  |       |

| V <sub>IL</sub>                                                    | Low level input voltage               | V <sub>CC</sub> = 2.0 - 2.7V |                        | -0.3                |                      | 0.3*V <sub>CC</sub>  | V     |

|                                                                    |                                       | V <sub>CC</sub> = 1.6 - 2.0V |                        | -0.3                |                      | 0.2*V <sub>CC</sub>  | -     |

|                                                                    |                                       | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OH</sub> = -2mA | 2.4                 | 0.94*V <sub>CC</sub> |                      |       |

|                                                                    |                                       | V <sub>CC</sub> = 2.3 - 2.7V | I <sub>OH</sub> = -1mA | 2.0                 | 0.96*V <sub>CC</sub> |                      | V     |

|                                                                    | High level output voltage             |                              | I <sub>OH</sub> = -2mA | 1.7                 | 0.92*V <sub>CC</sub> |                      |       |

| V <sub>OH</sub>                                                    |                                       | V <sub>CC</sub> = 3.3V       | I <sub>OH</sub> = -8mA | 2.6                 | 2.9                  |                      |       |

|                                                                    |                                       | V <sub>CC</sub> = 3.0V       | I <sub>OH</sub> = -6mA | 2.1                 | 2.6                  |                      |       |

|                                                                    |                                       | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -2mA | 1.4                 | 1.6                  |                      |       |

|                                                                    |                                       | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OL</sub> = 2mA  |                     | 0.02*V <sub>CC</sub> | 0.4                  |       |

|                                                                    |                                       |                              | I <sub>OL</sub> = 1mA  |                     | 0.01*V <sub>CC</sub> | 0.4                  | -     |

| N                                                                  |                                       | V <sub>CC</sub> = 2.3 - 2.7V | I <sub>OL</sub> = 2mA  |                     | 0.02*V <sub>CC</sub> | 0.7                  |       |

| V <sub>OL</sub>                                                    | Low level output voltage              | V <sub>CC</sub> = 3.3V       | I <sub>OL</sub> = 15mA |                     | 0.4                  | 0.76                 | V     |

|                                                                    |                                       | V <sub>CC</sub> = 3.0V       | I <sub>OL</sub> = 10mA |                     | 0.3                  | 0.64                 | -     |

|                                                                    |                                       | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 5mA  |                     | 0.2                  | 0.46                 |       |

|                                                                    |                                       | T = 25°C                     |                        |                     | <0.01                | 0.1                  |       |

| I <sub>IN</sub>                                                    | I <sub>IN</sub> Input leakage current | XOSC and<br>TOSC pins        |                        |                     | <0.02                | 1.1                  | μA    |

| R <sub>P</sub>                                                     | Pull/buss keeper resistor             |                              |                        |                     | 24                   |                      | kΩ    |

| +                                                                  | Disc time                             | Noload                       |                        |                     | 4.0                  |                      |       |

| t <sub>r</sub>                                                     | Rise time                             | No load                      | slew rate limitation   |                     | 7.0                  |                      | ns    |

The sum of all  $I_{OH}$  for PORTA and PORTB must not exceed 100mA. Notes: 1.

The sum of all  $I_{OH}$  for PORTC must not exceed 200mA. The sum of all  $I_{OH}$  for PORTD and pins PE[0-1] on PORTE must not exceed 200mA. The sum of all  $I_{OH}$  for PE[2-3] on PORTE, PORTR and PDI must not exceed 100mA.

2. The sum of all  $I_{OL}$  for PORTA and PORTB must not exceed 100mA.

The sum of all  $\mathrm{I}_{\mathrm{OL}}$  for PORTC must not exceed 200mA.

The sum of all  $\rm I_{OL}$  for PORTD and pins PE[0-1] on PORTE must not exceed 200mA.

The sum of all  $I_{\text{OL}}$  for PE[2-3] on PORTE, PORTR and PDI must not exceed 100mA.

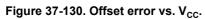

#### Table 36-74. Accuracy characteristics.

| Symbol             | Parameter                  |                                  | Condition <sup>(2)</sup>                                                            | Min.    | Тур.  | Max. | Units     |  |

|--------------------|----------------------------|----------------------------------|-------------------------------------------------------------------------------------|---------|-------|------|-----------|--|

| RES                | Resolution                 | Programmab                       | Programmable to 8 or 12 bit                                                         |         | 12    | 12   | Bits      |  |

|                    |                            | 500ksps                          | $V_{\rm CC}$ -1.0V < $V_{\rm REF}$ < $V_{\rm CC}$ -0.6V                             |         | ±1.2  | ±2   | _         |  |

| INL <sup>(1)</sup> |                            |                                  | All V <sub>REF</sub>                                                                |         | ±1.5  | ±3   |           |  |

|                    | Integral non-linearity     | 2000kapa                         | $V_{\rm CC}$ -1.0V < $V_{\rm REF}$ < $V_{\rm CC}$ -0.6V                             |         | ±1.0  | ±2   | lsb       |  |

|                    |                            | 2000ksps                         | All V <sub>REF</sub>                                                                |         | ±1.5  | ±3   |           |  |

| DNL <sup>(1)</sup> | Differential non-linearity | gu                               | aranteed monotonic                                                                  |         | <±0.8 | <±1  | lsb       |  |

|                    |                            |                                  |                                                                                     |         | -1    |      | mV        |  |

|                    | Offset error               | Temperature drift                |                                                                                     |         | <0.01 |      | mV/K      |  |

|                    |                            | Operating vo                     | Itage drift                                                                         |         | <0.6  |      | mV/V      |  |

|                    |                            | Differential                     | External reference                                                                  |         | -1    |      |           |  |

|                    |                            |                                  | AV <sub>CC</sub> /1.6                                                               |         | 10    |      | mV        |  |

|                    | Gain error                 | mode                             | AV <sub>CC</sub> /2.0                                                               |         | 8     |      |           |  |

|                    | Gainenoi                   | Temperature d<br>Operating volta |                                                                                     | Bandgap |       | ±5   |           |  |

|                    |                            |                                  | drift                                                                               |         | <0.02 |      | mV/K      |  |

|                    |                            |                                  | Itage drift                                                                         |         | <0.5  |      | mV/V      |  |

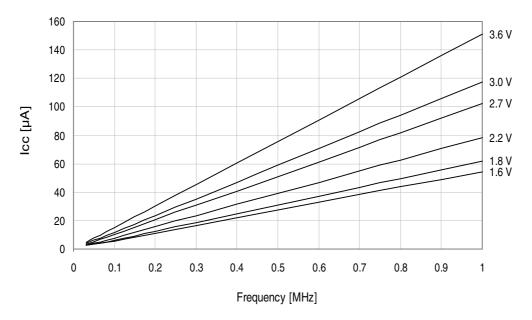

|                    | Noise                      |                                  | Differential mode, shorted input 2msps, $V_{CC}$ = 3.6V, Clk <sub>PER</sub> = 16MHz |         | 0.4   |      | mV<br>rms |  |

Notes: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

2. Unless otherwise noted all linearity, offset and gain error numbers are valid under the condition that external V<sub>REF</sub> is used.

#### Table 36-75. Gain stage characteristics.

| Symbol              | Parameter              | Condition                 |     | Min. | Тур. | Max.                         | Units |

|---------------------|------------------------|---------------------------|-----|------|------|------------------------------|-------|

| R <sub>in</sub>     | Input resistance       | Switched in normal mode   |     | 4.0  |      | kΩ                           |       |

| C <sub>sample</sub> | Input capacitance      | Switched in normal mode   |     | 4.4  |      | pF                           |       |

|                     | Signal range           | Gain stage output         |     | 0    |      | V <sub>CC</sub> - 0.6        | V     |

|                     | Propagation delay      | ADC conversion rate       |     | 1.0  |      | Clk <sub>ADC</sub><br>cycles |       |

|                     | Sample rate            | Same as ADC               | 100 |      | 1000 | kHz                          |       |

| INL <sup>(1)</sup>  | Integral non-linearity | 500ksps All gain settings |     |      | ±1.5 | ±4.0                         | lsb   |

|                     |                        | 1x gain, normal mode      |     |      | -0.8 |                              |       |

|                     | Gain error             | 8x gain, normal mode      |     |      | -2.5 |                              | %     |

|                     |                        | 64x gain, normal mode     |     |      | -3.5 |                              |       |

| Symbol                              | Parameter                                    | Condition                 | Min. | Тур. | Max. | Units |

|-------------------------------------|----------------------------------------------|---------------------------|------|------|------|-------|

| t <sub>HD;DAT</sub> Data hold time  | Data hald time                               | $f_{SCL} \leq 100 kHz$    | 0    |      | 3.45 |       |

|                                     |                                              | f <sub>SCL</sub> > 100kHz | 0    |      | 0.9  | μs    |

|                                     | Data actus tima                              | $f_{SCL} \leq 100 kHz$    | 250  |      |      |       |

| t <sub>SU;DAT</sub> Data setup time | Data setup time                              | f <sub>SCL</sub> > 100kHz | 100  |      |      | ns    |

|                                     | Cotup time for CTOD condition                | $f_{SCL} \leq 100 kHz$    | 4.0  |      |      | μs    |

| t <sub>SU;STO</sub>                 | Setup time for STOP condition                | f <sub>SCL</sub> > 100kHz | 0.6  |      |      |       |

| +                                   | Bus free time between a STOP and             | $f_{SCL} \leq 100 kHz$    | 4.7  |      |      |       |

| t <sub>BUF</sub>                    | START condition                              | f <sub>SCL</sub> > 100kHz | 1.3  |      |      | μs    |

| Notes: 1.                           | Required only for f <sub>SCL</sub> > 100kHz. |                           |      |      |      |       |

Required only for f<sub>SCL</sub> > 100kHz.

C<sub>b</sub> = Capacitance of one bus line in pF.

f<sub>PER</sub> = Peripheral clock frequency.

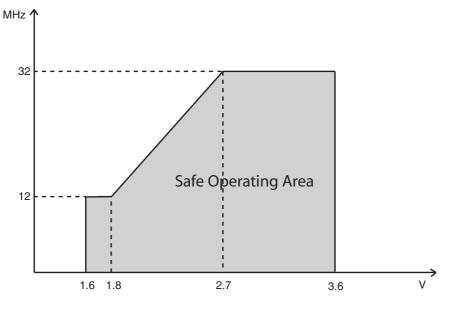

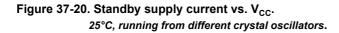

#### 37.1.1.5 Standby mode supply current

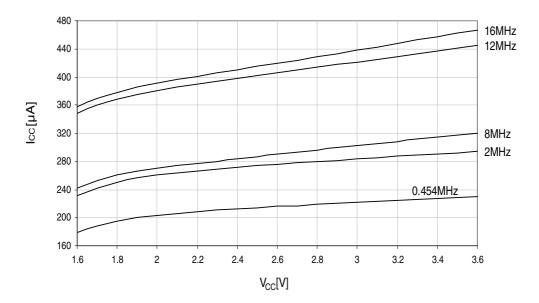

Figure 37-19. Standby supply current vs.  $V_{CC}$ . Standby,  $f_{SYS} = 1MHz$ .

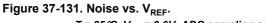

T = 25 ℃,  $V_{CC}$  = 3.6V, ADC sampling speed = 500ksps.

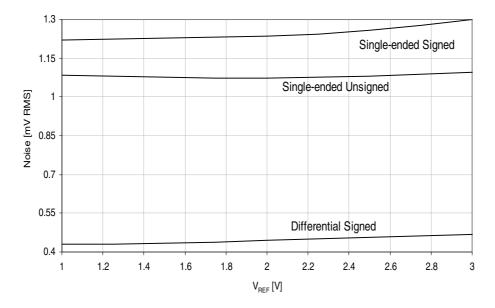

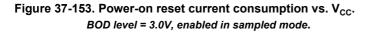

#### 37.2.9 Power-on Reset Characteristics

### 37.2.12 PDI characteristics

Figure 37-168. Maximum PDI frequency vs.  $V_{cc}$ .

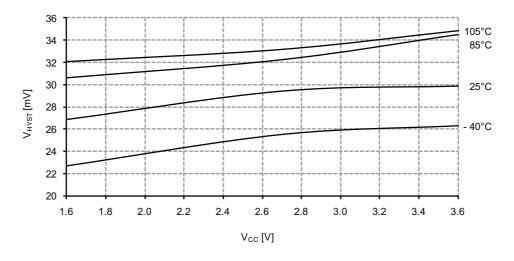

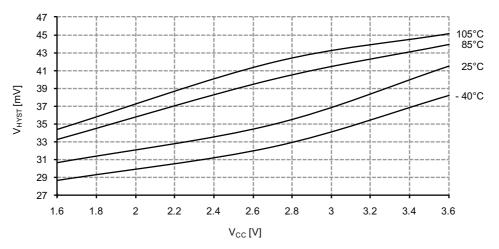

Figure 37-221. Analog comparator hysteresis vs. V<sub>CC</sub>. Low power, small hysteresis.

Figure 37-222. Analog comparator hysteresis vs. V<sub>CC</sub>. *High-speed mode, large hysteresis.*

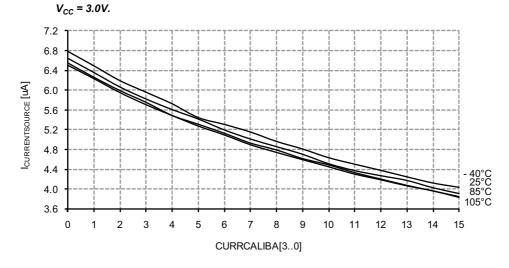

Figure 37-225. Analog comparator current source vs. calibration value.

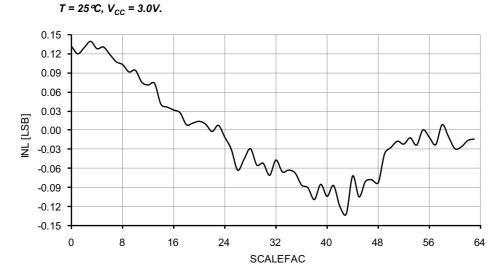

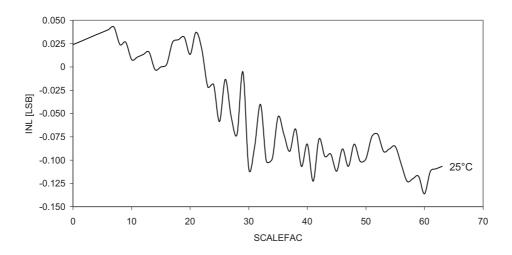

Figure 37-226. Voltage scaler INL vs. SCALEFAC.

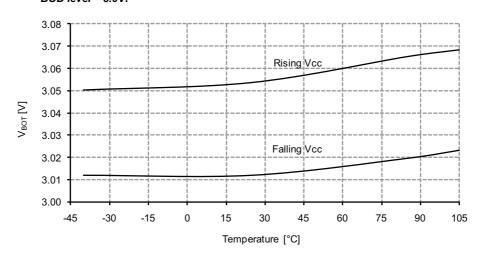

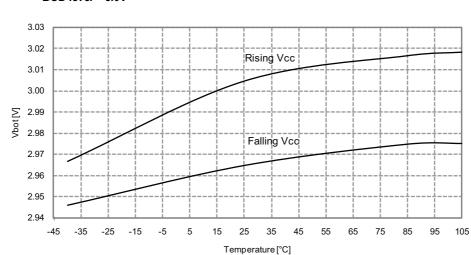

Figure 37-229. BOD thresholds vs. temperature. BOD level = 3.0V.

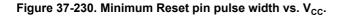

#### 37.3.8 External Reset Characteristics

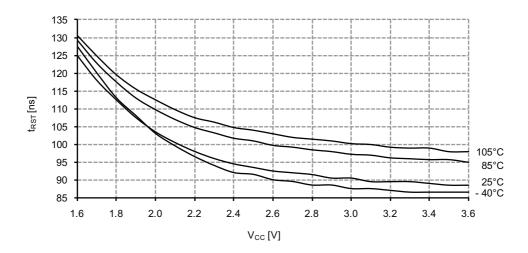

Figure 37-231. Reset pin pull-up resistor current vs. reset pin voltage.  $V_{cc} = 1.8V.$

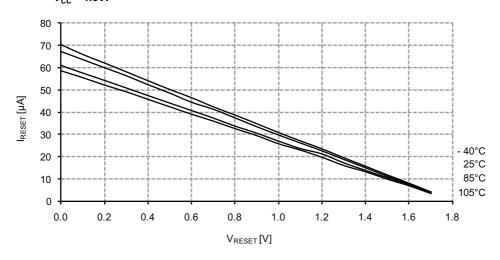

Figure 37-232. Reset pin pull-up resistor current vs. reset pin voltage.  $V_{CC} = 3.0V.$

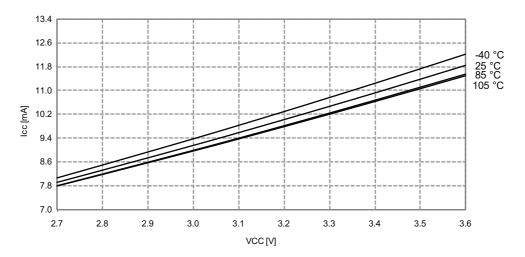

Figure 37-259. Active mode supply current vs.  $V_{CC}$ .  $f_{SYS}$  = 32MHz internal oscillator.

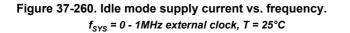

#### 37.4.1.2 Idle mode supply current

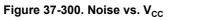

Figure 37-299. Noise vs.  $V_{REF}$ T = 25 °C,  $V_{CC}$  = 3.6V, ADC sampling speed = 500ksps

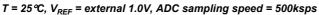

Figure 37-309. Analog comparator current source vs. calibration value.

Figure 37-310. Voltage scaler INL vs. SCALEFAC.  $T = 25 \circ C$ ,  $V_{cc} = 3.0V$ .

Figure 37-313. BOD thresholds vs. temperature. BOD level = 3.0V

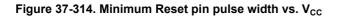

#### 37.4.8 External Reset Characteristics