Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2000                       |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 34                                                                        |

| Program Memory Size        | 32KB (16K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 12x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 44-VQFN (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega32a4u-mh |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

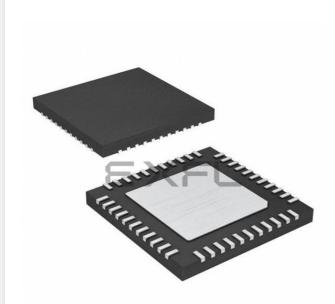

## 3.1 Block Diagram

#### Figure 3-1. XMEGA A4U Block Diagram

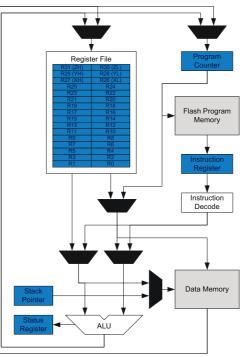

Figure 6-1. Block diagram of the AVR CPU architecture.

The arithmetic logic unit (ALU) supports arithmetic and logic operations between registers or between a constant and a register. Single-register operations can also be executed in the ALU. After an arithmetic operation, the status register is updated to reflect information about the result of the operation.

The ALU is directly connected to the fast-access register file. The 32 x 8-bit general purpose working registers all have single clock cycle access time allowing single-cycle arithmetic logic unit (ALU) operation between registers or between a register and an immediate. Six of the 32 registers can be used as three 16-bit address pointers for program and data space addressing, enabling efficient address calculations.

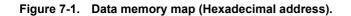

The memory spaces are linear. The data memory space and the program memory space are two different memory spaces.

The data memory space is divided into I/O registers, SRAM, and external RAM. In addition, the EEPROM can be memory mapped in the data memory.

All I/O status and control registers reside in the lowest 4KB addresses of the data memory. This is referred to as the I/O memory space. The lowest 64 addresses can be accessed directly, or as the data space locations from 0x00 to 0x3F. The rest is the extended I/O memory space, ranging from 0x0040 to 0x0FFF. I/O registers here must be accessed as data space locations using load (LD/LDS/LDD) and store (ST/STS/STD) instructions.

The SRAM holds data. Code execution from SRAM is not supported. It can easily be accessed through the five different addressing modes supported in the AVR architecture. The first SRAM address is 0x2000.

Data addresses 0x1000 to 0x1FFF are reserved for memory mapping of EEPROM.

The program memory is divided in two sections, the application program section and the boot program section. Both sections have dedicated lock bits for write and read/write protection. The SPM instruction that is used for self-programming of the application flash memory must reside in the boot program section. The application section contains an application table section with separate lock bits for write and read/write protection. The application table section table section can be used for safe storing of nonvolatile data in the program memory.

## 6.4 ALU - Arithmetic Logic Unit

The arithmetic logic unit (ALU) supports arithmetic and logic operations between registers or between a constant and a register. Single-register operations can also be executed. The ALU operates in direct connection with all 32 general

### 7.6 EEPROM

All devices have EEPROM for nonvolatile data storage. It is either addressable in a separate data space (default) or memory mapped and accessed in normal data space. The EEPROM supports both byte and page access. Memory mapped EEPROM allows highly efficient EEPROM reading and EEPROM buffer loading. When doing this, EEPROM is accessible using load and store instructions. Memory mapped EEPROM will always start at hexadecimal address 0x1000.

### 7.7 I/O Memory

The status and configuration registers for peripherals and modules, including the CPU, are addressable through I/O memory locations. All I/O locations can be accessed by the load (LD/LDS/LDD) and store (ST/STS/STD) instructions, which are used to transfer data between the 32 registers in the register file and the I/O memory. The IN and OUT instructions can address I/O memory locations in the range of 0x00 to 0x3F directly. In the address range 0x00 - 0x1F, single-cycle instructions for manipulation and checking of individual bits are available.

The I/O memory address for all peripherals and modules in XMEGA A4U is shown in the "Peripheral Module Address Map" on page 61.

#### 7.7.1 General Purpose I/O Registers

The lowest 16 I/O memory addresses are reserved as general purpose I/O registers. These registers can be used for storing global variables and flags, as they are directly bit-accessible using the SBI, CBI, SBIS, and SBIC instructions.

## 19. Hi-Res – High Resolution Extension

## 19.1 Features

- Increases waveform generator resolution up to 8x (three bits)

- Supports frequency, single-slope PWM, and dual-slope PWM generation

- Supports the AWeX when this is used for the same timer/counter

## 19.2 Overview

The high-resolution (hi-res) extension can be used to increase the resolution of the waveform generation output from a timer/counter by four or eight. It can be used for a timer/counter doing frequency, single-slope PWM, or dual-slope PWM generation. It can also be used with the AWeX if this is used for the same timer/counter.

The hi-res extension uses the peripheral 4x clock ( $Clk_{PER4}$ ). The system clock prescalers must be configured so the peripheral 4x clock frequency is four times higher than the peripheral and CPU clock frequency when the hi-res extension is enabled.

There are three hi-res extensions that each can be enabled for each timer/counters pair on PORTC, PORTD and PORTE. The notation of these are HIRESC, HIRESD and HIRESE, respectively.

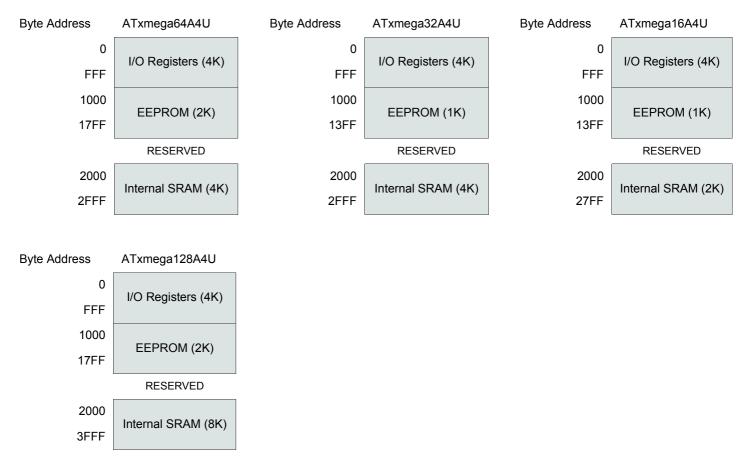

## 20. RTC – 16-bit Real-Time Counter

## 20.1 Features

- 16-bit resolution

- Selectable clock source

- 32.768kHz external crystal

- External clock

- 32.768kHz internal oscillator

- 32kHz internal ULP oscillator

- Programmable 10-bit clock prescaling

- One compare register

- One period register

- Clear counter on period overflow

- Optional interrupt/event on overflow and compare match

## 20.2 Overview

The 16-bit real-time counter (RTC) is a counter that typically runs continuously, including in low-power sleep modes, to keep track of time. It can wake up the device from sleep modes and/or interrupt the device at regular intervals.

The reference clock is typically the 1.024kHz output from a high-accuracy crystal of 32.768kHz, and this is the configuration most optimized for low power consumption. The faster 32.768kHz output can be selected if the RTC needs a resolution higher than 1ms. The RTC can also be clocked from an external clock signal, the 32.768kHz internal oscillator or the 32kHz internal ULP oscillator.

The RTC includes a 10-bit programmable prescaler that can scale down the reference clock before it reaches the counter. A wide range of resolutions and time-out periods can be configured. With a 32.768kHz clock source, the maximum resolution is 30.5µs, and time-out periods can range up to 2000 seconds. With a resolution of 1s, the maximum timeout period is more than18 hours (65536 seconds). The RTC can give a compare interrupt and/or event when the counter equals the compare register value, and an overflow interrupt and/or event when it equals the period register value.

#### Figure 20-1. Real-time counter overview.

## 25. IRCOM – IR Communication Module

## 25.1 Features

- Pulse modulation/demodulation for infrared communication

- IrDA compatible for baud rates up to 115.2Kbps

- Selectable pulse modulation scheme

- 3/16 of the baud rate period

- Fixed pulse period, 8-bit programmable

- Pulse modulation disabled

- Built-in filtering

- Can be connected to and used by any USART

### 25.2 Overview

Atmel AVR XMEGA devices contain an infrared communication module (IRCOM) that is IrDA compatible for baud rates up to 115.2Kbps. It can be connected to any USART to enable infrared pulse encoding/decoding for that USART.

#### 36.1.8 Analog Comparator Characteristics

Table 36-15. Analog Comparator characteristics.

| Symbol             | Parameter               | Condition                       | I         | Min. | Тур. | Max.      | Units |  |

|--------------------|-------------------------|---------------------------------|-----------|------|------|-----------|-------|--|

| V <sub>off</sub>   | Input offset voltage    |                                 |           |      | <±10 |           | mV    |  |

| l <sub>lk</sub>    | Input leakage current   |                                 |           |      | <1.0 |           | nA    |  |

|                    | Input voltage range     |                                 |           | -0.1 |      | $AV_{CC}$ | V     |  |

|                    | AC startup time         |                                 |           |      | 100  |           | μs    |  |

| V <sub>hys1</sub>  | Hysteresis, none        |                                 |           |      | 0    |           | mV    |  |

| V                  |                         | mode = High Spee                | ed (HS)   |      | 13   |           | mV    |  |

| V <sub>hys2</sub>  | Hysteresis, small       | mode = Low Pow                  | er (LP)   |      | 30   |           | IIIV  |  |

| N                  |                         | mode = HS                       | 3         |      | 30   |           | m)/   |  |

| V <sub>hys3</sub>  | Hysteresis, large       | mode = LP                       | )         |      | 60   |           | – mV  |  |

|                    |                         | V <sub>CC</sub> = 3.0V, T= 85°C | mode = HS |      | 30   | 90        |       |  |

|                    | Dranagation dolou       | mode = HS                       | 5         |      | 30   |           |       |  |

| t <sub>delay</sub> | Propagation delay       | V <sub>CC</sub> = 3.0V, T= 85°C | mode = LP |      | 130  | 500       | ns    |  |

|                    |                         | mode = LP                       | )         |      | 130  |           |       |  |

|                    | 64-level voltage scaler | Integral non-linearity (INL)    |           |      | 0.3  | 0.5       | lsb   |  |

## 36.1.9 Bandgap and Internal 1.0V Reference Characteristics

Table 36-16.

Bandgap and Internal 1.0V reference characteristics.

| Symbol | Parameter                              | Condition                            | Min.                         | Тур. | Max. | Units |

|--------|----------------------------------------|--------------------------------------|------------------------------|------|------|-------|

|        | Startup time                           | As reference for ADC or DAC          | 1 Clk <sub>PER</sub> + 2.5µs |      |      |       |

|        | Startup time                           | As input voltage to ADC and AC       |                              | 1.5  |      | μs    |

|        | Bandgap voltage                        |                                      |                              | 1.1  |      | V     |

| INT1V  | Internal 1.00V reference               | T= 85°C, after calibration           | 0.99                         | 1.0  | 1.01 | V     |

|        | Variation over voltage and temperature | Relative to T= 85°C, $V_{CC}$ = 3.0V |                              | ±1.5 |      | %     |

#### 36.2.14.5 Internal Phase Locked Loop (PLL) characteristics

Table 36-58. Internal PLL characteristics.

| Symbo<br>I       | Parameter                       | Condition                                                 | Min. | Тур. | Max. | Units |

|------------------|---------------------------------|-----------------------------------------------------------|------|------|------|-------|

| f <sub>IN</sub>  | Input frequency                 | Output frequency must be within $\mathbf{f}_{\text{OUT}}$ | 0.4  |      | 64   | MHz   |

| f                | Output frequency <sup>(1)</sup> | V <sub>CC</sub> = 1.6 - 1.8V                              | 20   |      | 48   | MHz   |

| f <sub>out</sub> | Output frequency <sup>(1)</sup> | V <sub>CC</sub> = 2.7 - 3.6V                              | 20   |      | 128  |       |

|                  | Start-up time                   |                                                           |      | 25   |      | μs    |

|                  | Re-lock time                    |                                                           |      | 25   |      | μs    |

Note: 1. The maximum output frequency vs. supply voltage is linear between 1.8V and 2.7V, and can never be higher than four times the maximum CPU frequency.

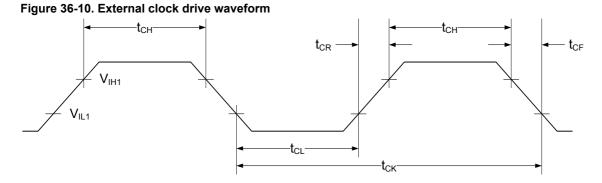

36.2.14.6 External clock characteristics

Table 36-59. External clock used as system clock without prescaling.

| Symbol            | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units |

|-------------------|---------------------------------------------------|------------------------------|------|------|------|-------|

| 1 /4              | Clock Frequency <sup>(1)</sup>                    | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 12   | MHz   |

| 1/t <sub>CK</sub> | Clock Frequency W                                 | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 32   |       |

| +                 | Clock Period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 83.3 |      |      |       |

| t <sub>ск</sub>   | CIUCK FEIIOU                                      | V <sub>CC</sub> = 2.7 - 3.6V | 31.5 |      |      | ns    |

| +                 | Clock High Time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      | 20    |

| t <sub>CH</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | ns    |

| +                 | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      |       |

| t <sub>CL</sub>   | Clock Low Time                                    | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | ns    |

| 4                 |                                                   | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |       |

| t <sub>CR</sub>   | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    | ns    |

|                   | Foll Time (for movimum fraguenov)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   |       |

| t <sub>CF</sub>   | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    | ns    |

| $\Delta t_{CK}$   | Change in period from one clock cycle to the next |                              |      |      | 10   | %     |

Note: 1. The maximum frequency vs. supply voltage is linear between 1.6V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

| Symbol | Parameter                       | Condition             |                                                 | Min. | Тур. | Max. | Units     |

|--------|---------------------------------|-----------------------|-------------------------------------------------|------|------|------|-----------|

|        | Offset error,<br>input referred | 1x gain, normal mode  |                                                 |      | -2   |      |           |

|        |                                 | 8x gain, normal mode  |                                                 |      | -5   |      | mV        |

|        |                                 | 64x gain, normal mode |                                                 |      | -4   |      |           |

|        |                                 | 1x gain, normal mode  |                                                 |      | 0.5  |      |           |

|        | Noise                           | 8x gain, normal mode  | V <sub>CC</sub> = 3.6V<br>Ext. V <sub>REF</sub> |      | 1.5  |      | mV<br>rms |

|        |                                 | 64x gain, normal mode | - KEF                                           |      | 11   |      |           |

Note: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

#### 36.3.7 DAC Characteristics

#### Table 36-76. Power supply, reference and output range.

| Symbol               | Parameter                   | Condition                               | Min.                  | Тур. | Max.                   | Units |

|----------------------|-----------------------------|-----------------------------------------|-----------------------|------|------------------------|-------|

| AV <sub>CC</sub>     | Analog supply voltage       |                                         | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3  | V     |

| AV <sub>REF</sub>    | External reference voltage  |                                         | 1.0                   |      | V <sub>CC</sub> - 0.6  | V     |

| R <sub>channel</sub> | DC output impedance         |                                         |                       |      | 50                     | Ω     |

|                      | Linear output voltage range |                                         | 0.15                  |      | AV <sub>CC</sub> -0.15 | V     |

| R <sub>AREF</sub>    | Reference input resistance  |                                         |                       | >10  |                        | MΩ    |

| CAREF                | Reference input capacitance | Static load                             |                       | 7    |                        | pF    |

|                      | Minimum resistance load     |                                         | 1.0                   |      |                        | kΩ    |

|                      | Maximum capacitance load    |                                         |                       |      | 100                    | pF    |

|                      | Maximum capacitance load    | 1000 $\Omega$ serial resistance         |                       |      | 1.0                    | nF    |

|                      | Output sink/source          | Operating within accuracy specification |                       |      | AV <sub>CC</sub> /1000 | mA    |

|                      |                             | Safe operation                          |                       |      | 10                     | IIIA  |

#### Table 36-77. Clock and timing.

| Symbol | Parameter                                                                       | Cond                      | dition         | Min. | Тур. | Max. | Units |

|--------|---------------------------------------------------------------------------------|---------------------------|----------------|------|------|------|-------|

| f      | f <sub>DAC</sub> Conversion rate C <sub>load</sub> =100pF,<br>maximum step size | C <sub>load</sub> =100pF, | Normal mode    | 0    |      | 1000 | kene  |

| 'DAC   |                                                                                 | maximum step size         | Low power mode |      |      | 500  | ksps  |

#### Table 36-78. Accuracy characteristics.

| Symbol             | Parameter                    | Conditior                               | ı                      | Min. | Тур. | Max. | Units                           |

|--------------------|------------------------------|-----------------------------------------|------------------------|------|------|------|---------------------------------|

| RES                | Input resolution             |                                         |                        |      |      | 12   | Bits                            |

|                    |                              | $\lambda = E_{\rm vt} + 0 \lambda$      | V <sub>CC</sub> = 1.6V |      | ±2.0 | ±3.0 |                                 |

|                    |                              | V <sub>REF</sub> = Ext 1.0V             | V <sub>CC</sub> = 3.6V |      | ±1.5 | ±2.5 |                                 |

| INL <sup>(1)</sup> | Integral pop linearity       |                                         | V <sub>CC</sub> = 1.6V |      | ±2.0 | ±4.0 | loh                             |

|                    | Integral non-linearity       | V <sub>REF</sub> =AV <sub>CC</sub>      | V <sub>CC</sub> = 3.6V |      | ±1.5 | ±4.0 |                                 |

|                    |                              | \/INIT4\/                               | V <sub>CC</sub> = 1.6V |      | ±5.0 |      |                                 |

|                    |                              | V <sub>REF</sub> =INT1V                 | V <sub>CC</sub> = 3.6V |      | ±5.0 |      |                                 |

|                    |                              | $\lambda = - \sum t (1 - 0) / (1 - 1) $ | V <sub>CC</sub> = 1.6V |      | ±1.5 | 3.0  |                                 |

|                    |                              | V <sub>REF</sub> =Ext 1.0V              | V <sub>CC</sub> = 3.6V |      | ±0.6 | 1.5  | Isb<br>Isb<br>Isb<br>Isb<br>Isb |

| DNL <sup>(1)</sup> |                              |                                         | V <sub>CC</sub> = 1.6V |      | ±1.0 | 3.5  |                                 |

| DNL                | Differential non-linearity   | V <sub>REF</sub> =AV <sub>CC</sub>      | V <sub>CC</sub> = 3.6V |      | ±0.6 | 1.5  |                                 |

|                    |                              |                                         | V <sub>CC</sub> = 1.6V |      | ±4.5 |      |                                 |

|                    |                              | V <sub>REF</sub> =INT1V                 | V <sub>CC</sub> = 3.6V |      | ±4.5 |      |                                 |

|                    | Gain error                   | After calibration                       | 1                      |      | <4.0 |      | lsb                             |

|                    | Gain calibration step size   |                                         |                        |      | 4.0  |      | lsb                             |

|                    | Gain calibration drift       | V <sub>REF</sub> = Ext 1.0V             |                        |      | <0.2 |      | mV/K                            |

|                    | Offset error                 | After calibration                       |                        |      | <1.0 |      | lsb                             |

|                    | Offset calibration step size |                                         |                        |      | 1.0  |      |                                 |

Note: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% output voltage range.

#### 36.4.3 Current consumption

| Symbol          | Parameter                                | Condition                                 |                         | Min. | Тур. | Max. | Units |  |

|-----------------|------------------------------------------|-------------------------------------------|-------------------------|------|------|------|-------|--|

|                 |                                          |                                           | V <sub>CC</sub> = 1.8V  |      | 55   |      |       |  |

|                 |                                          | 32kHz, Ext. Clk                           | V <sub>CC</sub> = 3.0V  |      | 135  |      | -     |  |

|                 |                                          |                                           | V <sub>CC</sub> = 1.8V  |      | 255  |      | μA    |  |

|                 | Active power consumption <sup>(1)</sup>  | 1MHz, Ext. Clk                            | V <sub>CC</sub> = 3.0V  |      | 535  |      | -     |  |

|                 |                                          |                                           | V <sub>CC</sub> = 1.8V  |      | 460  | 600  |       |  |

|                 |                                          | 2MHz, Ext. Clk                            | $\lambda = 2.0 \lambda$ |      | 1.0  | 1.4  |       |  |

|                 |                                          | 32MHz, Ext. Clk                           | V <sub>CC</sub> = 3.0V  |      | 9.5  | 12   | mA    |  |

|                 |                                          |                                           | V <sub>CC</sub> = 1.8V  |      | 2.9  |      |       |  |

|                 |                                          | 32kHz, Ext. Clk                           | V <sub>CC</sub> = 3.0V  |      | 3.9  |      | _     |  |

|                 |                                          |                                           | V <sub>CC</sub> = 1.8V  |      | 62   |      |       |  |

|                 | Idle power<br>consumption <sup>(1)</sup> | 1MHz, Ext. Clk                            | V <sub>CC</sub> = 3.0V  |      | 118  |      | μA    |  |

|                 |                                          |                                           | V <sub>CC</sub> = 1.8V  |      | 125  | 225  |       |  |

|                 |                                          | 2MHz, Ext. Clk                            | <u>)</u> ( ) () ()      |      | 240  | 350  |       |  |

|                 |                                          | 32MHz, Ext. Clk                           | V <sub>CC</sub> = 3.0V  |      | 3.8  | 5.5  | mA    |  |

| I <sub>CC</sub> |                                          | T = 25°C                                  | N/ 2.0V/                |      | 0.1  | 1.0  |       |  |

|                 |                                          | T = 85°C                                  | V <sub>CC</sub> = 3.0V  |      | 1.5  | 4.5  |       |  |

|                 |                                          | T = 105°C                                 |                         |      | 0.1  | 8.6  |       |  |

|                 | Power-down power consumption             | WDT and Sampled BOD enabled,<br>T = 25°C  |                         |      | 1.4  | 3.0  | μA    |  |

|                 |                                          | WDT and Sampled BOD enabled,<br>T = 85°C  | V <sub>CC</sub> = 3.0V  |      | 2.8  | 6.0  | -     |  |

|                 |                                          | WDT and Sampled BOD enabled,<br>T = 105°C |                         |      | 1.4  | 8.8  |       |  |

|                 |                                          | RTC from ULP clock, WDT and               | V <sub>CC</sub> = 1.8V  |      | 1.2  |      |       |  |

|                 |                                          | sampled BOD enabled, T = 25°C             | V <sub>CC</sub> = 3.0V  |      | 1.5  |      | -     |  |

|                 | Power-save power                         | RTC from 1.024kHz low power               | V <sub>CC</sub> = 1.8V  |      | 0.6  | 2.0  | -     |  |

|                 | consumption <sup>(2)</sup>               | 32.768kHz TOSC, T = 25°C                  | V <sub>CC</sub> = 3.0V  |      | 0.7  | 2.0  | μA    |  |

|                 |                                          | RTC from low power 32.768kHz              | V <sub>CC</sub> = 1.8V  |      | 0.8  | 3.0  |       |  |

|                 |                                          | TOSC, $T = 25^{\circ}C$                   | V <sub>CC</sub> = 3.0V  |      | 1.0  | 3.0  | -     |  |

|                 | Reset power consumption                  | Current through RESET pin substracted     | V <sub>CC</sub> = 3.0V  |      | 300  |      | μΑ    |  |

Table 36-100.Current consumption for Active mode and sleep modes.

2. Maximum limits are based on characterization, and not tested in production.

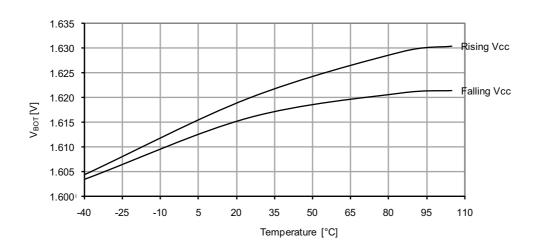

#### 36.4.10 Brownout Detection Characteristics

Table 36-113. Brownout detection characteristics.

| Symbol            | Parameter                           | Condition       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------|-----------------|------|------|------|-------|

|                   | BOD level 0 falling V <sub>CC</sub> |                 | 1.50 | 1.62 | 1.72 |       |

|                   | BOD level 1 falling V <sub>CC</sub> |                 |      | 1.8  |      | -     |

|                   | BOD level 2 falling V <sub>CC</sub> |                 |      | 2.0  |      | _     |

| V <sub>BOT</sub>  | BOD level 3 falling $V_{CC}$        |                 |      | 2.2  |      | - V   |

|                   | BOD level 4 falling V <sub>CC</sub> |                 |      | 2.4  |      |       |

|                   | BOD level 5 falling V <sub>CC</sub> |                 |      | 2.6  |      |       |

|                   | BOD level 6 falling V <sub>CC</sub> |                 |      | 2.8  |      |       |

|                   | BOD level 7 falling V <sub>CC</sub> |                 |      | 3.0  |      | _     |

| +                 | Detection time                      | Continuous mode |      | 0.4  |      |       |

| t <sub>BOD</sub>  |                                     | Sampled mode    |      | 1000 |      | μs    |

| V <sub>HYST</sub> | Hysteresis                          |                 |      | 1.2  |      | %     |

#### 36.4.11 External Reset Characteristics

#### Table 36-114. External reset characteristics.

| Symbol           | Parameter                                   | Condition                    | Min.                 | Тур. | Max.                 | Units |

|------------------|---------------------------------------------|------------------------------|----------------------|------|----------------------|-------|

| t <sub>EXT</sub> | Minimum reset pulse width                   |                              | 1000                 | 95   |                      | ns    |

|                  | Reset threshold voltage (V <sub>IH</sub> )  | V <sub>CC</sub> = 2.7 - 3.6V | $0.60 \times V_{CC}$ |      |                      | V     |

|                  | Reset tilleshold voltage (v <sub>IH</sub> ) | V <sub>CC</sub> = 1.6 - 2.7V | $0.60 \times V_{CC}$ |      |                      |       |

| V <sub>RST</sub> | Poset threshold voltage $(V_{i})$           | V <sub>CC</sub> = 2.7 - 3.6V |                      |      | $0.50 \times V_{CC}$ | V     |

|                  | Reset threshold voltage (V <sub>IL</sub> )  | V <sub>CC</sub> = 1.6 - 2.7V |                      |      | 0.40×V <sub>CC</sub> |       |

| R <sub>RST</sub> | Reset pin Pull-up Resistor                  |                              |                      | 25   |                      | kΩ    |

#### 36.4.12 Power-on Reset Characteristics

#### Table 36-115. Power-on reset characteristics.

| Symbol                           | Parameter                                     | Condition                                | Min. | Тур. | Max. | Units |

|----------------------------------|-----------------------------------------------|------------------------------------------|------|------|------|-------|

| V <sub>POT-</sub> <sup>(1)</sup> | POR threshold voltage falling $V_{CC}$        | $V_{CC}$ falls faster than 1V/ms         | 0.4  | 1.0  |      | V     |

|                                  |                                               | V <sub>CC</sub> falls at 1V/ms or slower | 0.8  | 1.0  |      |       |

| V <sub>POT+</sub>                | POR threshold voltage rising $\rm V_{\rm CC}$ |                                          |      | 1.3  | 1.59 | mV    |

Note: 1.  $V_{POT-}$  values are only valid when BOD is disabled. When BOD is enabled  $V_{POT-} = V_{POT+}$ .

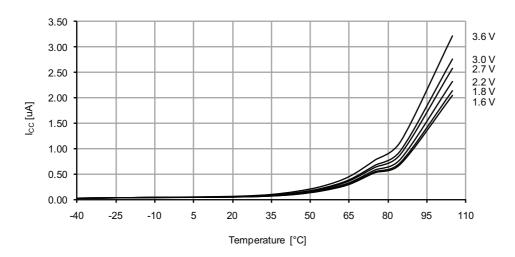

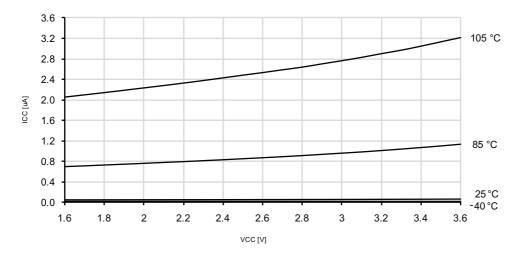

#### 37.1.1.3 Power-down mode supply current

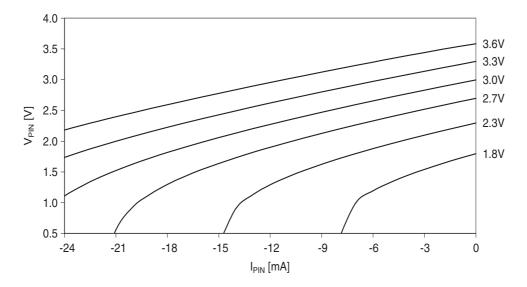

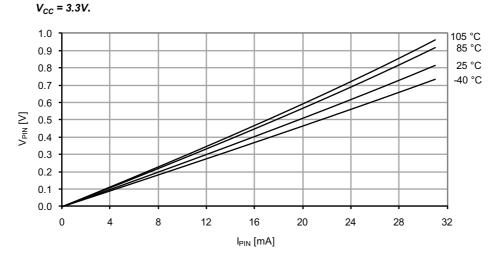

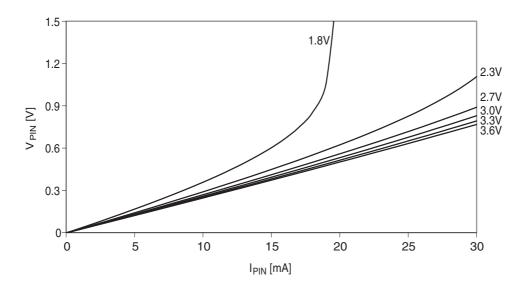

Figure 37-27. I/O pin output voltage vs. source current.

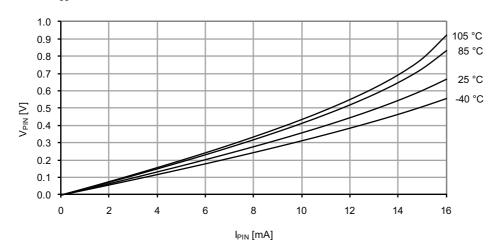

Figure 37-28. I/O pin output voltage vs. sink current.  $V_{cc} = 1.8V.$

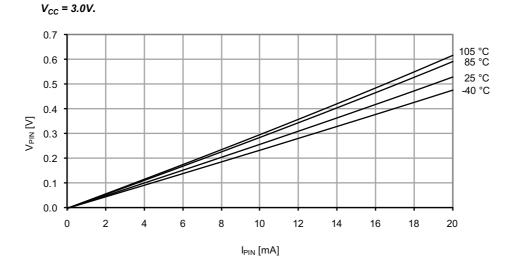

Figure 37-29. I/O pin output voltage vs. sink current.

Figure 37-30. I/O pin output voltage vs. sink current.

Figure 37-31. I/O pin output voltage vs. sink current.

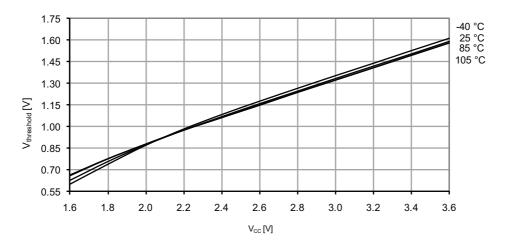

Figure 37-118. I/O pin input threshold voltage vs.  $V_{CC}$ .  $V_{IL}$  I/O pin read as "0".

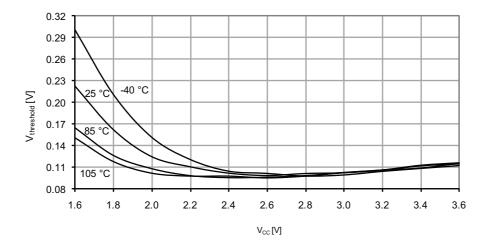

Figure 37-119. I/O pin input hysteresis vs.  $\rm V_{\rm CC}.$

#### 37.2.7 BOD Characteristics

#### 37.2.10.4 32MHz Internal Oscillator

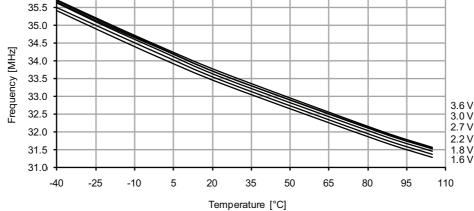

Figure 37-160. 32MHz internal oscillator frequency vs. temperature.

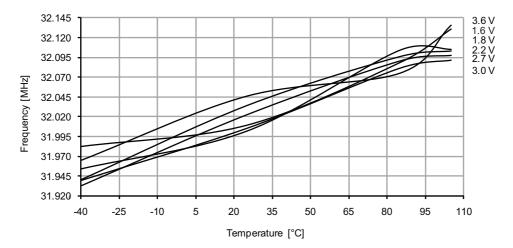

Figure 37-161. 32MHz internal oscillator frequency vs. temperature. DFLL enabled, from the 32.768kHz internal oscillator.

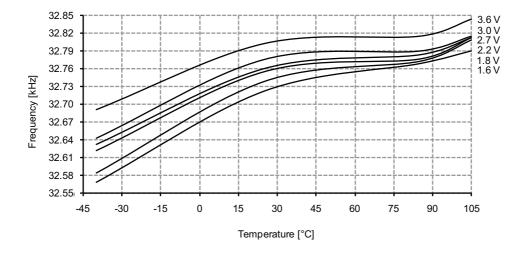

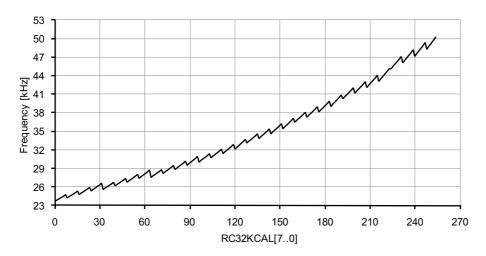

Figure 37-240. 32.768kHz internal oscillator frequency vs. calibration value.  $V_{cc} = 3.0V, T = 25^{\circ}C.$

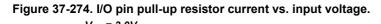

#### 37.4.2 I/O Pin Characteristics

#### 37.4.2.1 Pull-up

Vpin [V]

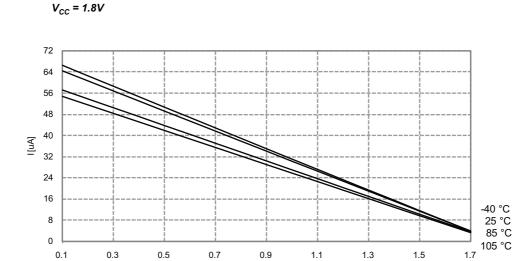

Figure 37-273. I/O pin pull-up resistor current vs. input voltage.