# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 105°C (TA)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-FBGA, FCBGA                                                                                                     |

| Supplier Device Package            | 624-FCBGA (21x21)                                                                                                   |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6d7cvt08ae                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pad Name     | Mode         | Signal             | Pad Settings          | Pad/Group Registers         |

|--------------|--------------|--------------------|-----------------------|-----------------------------|

|              |              |                    | SRE - SLOW            |                             |

| CSI_CLK0M    |              | CSI_CLK0_N         |                       |                             |

| CSI_CLK0P    |              | CSI_CLK0_P         |                       |                             |

| CSI_D0M      |              | CSI_DATA0_N        |                       |                             |

| CSI_D0P      |              | CSI_DATA0_P        |                       |                             |

| CSI_D1M      |              | CSI_DATA1_N        |                       |                             |

| CSI_D1P      |              | CSI_DATA1_P        |                       |                             |

| CSI_D2M      |              | CSI_DATA2_N        |                       |                             |

| CSI_D2P      |              | CSI_DATA2_P        |                       |                             |

| CSI_D3M      |              | CSI_DATA3_N        |                       |                             |

| CSI_D3P      |              | CSI_DATA3_P        |                       |                             |

| DI0_DISP_CLK | ALT0         | IPU1_DI0_DISP_CLK  | HYS - ENABLED         | SW_PAD_CTL_PAD_DI0_DISP_CLK |

|              | ALT1         | IPU2_DI0_DISP_CLK  | PUS - 100K_OHM_PU     |                             |

|              | ALT5         | GPIO4_IO16         | PUE - PULL            |                             |

|              |              |                    | PKE - ENABLED         |                             |

|              |              |                    | ODE - DISABLED        |                             |

|              |              |                    | SPEED - MEDIUM        |                             |

|              |              |                    | DSE - 40_OHM          |                             |

|              |              |                    | SRE - SLOW            |                             |

| DI0_PIN2     | ALT0         | IPU1_DI0_PIN02     | HYS - ENABLED         | SW_PAD_CTL_PAD_DI0_PIN02    |

| _            | ALT1         | <br>IPU2_DI0_PIN02 | <br>PUS - 100K_OHM_PU |                             |

|              | ALT2         | AUD6_TXD           | PUE - PULL            |                             |

|              | ALT5         | GPIO4_IO18         | PKE - ENABLED         |                             |

|              |              |                    | ODE - DISABLED        |                             |

|              |              |                    | SPEED - MEDIUM        |                             |

|              |              |                    |                       |                             |

|              |              |                    | DSE - 40_OHM          |                             |

|              |              |                    | SRE - SLOW            |                             |

| DI0_PIN3     | ALT0<br>ALT1 | IPU1_DI0_PIN03     | HYS - ENABLED         | SW_PAD_CTL_PAD_DI0_PIN03    |

|              |              | IPU2_DI0_PIN03     | PUS - 100K_OHM_PU     |                             |

|              | ALT2         | AUD6_TXFS          | PUE - PULL            |                             |

|              | ALT5         | GPIO4_IO19         | PKE - ENABLED         |                             |

|              |              |                    | ODE - DISABLED        |                             |

|              |              |                    | SPEED - MEDIUM        |                             |

|              |              |                    | DSE - 40_OHM          |                             |

|              |              |                    | SRE - SLOW            |                             |

| DI0_PIN4     | ALT0         | IPU1_DI0_PIN04     | HYS - ENABLED         | SW_PAD_CTL_PAD_DI0_PIN04    |

|              | ALT1         | IPU2_DI0_PIN04     | PUS - 100K_OHM_PU     |                             |

|              | ALT2         | AUD6_RXD           | PUE - PULL            |                             |

## Table 4-1. Pin Assignments (continued)

Table continues on the next page...

| RDY  | N/A <sup>1</sup> | N/A             | N/A             | N/A          | N/A           |

|------|------------------|-----------------|-----------------|--------------|---------------|

| SCLK | EIM_D16.alt1     | CSI0_DAT8.alt2  | DISP0_DAT0.alt2 | EIM_D21.alt1 | SD1_CLK.alt1  |

| SS0  | EIM_EB2.alt1     | CSI0_DAT11.alt2 | DISP0_DAT3.alt2 | EIM_D20.alt1 | SD1_DAT1.alt1 |

| SS1  | EIM_D19.alt1     | EIM_LBA.alt1    | DISP0_DAT4.alt2 | EIM_A25.alt1 | SD1_DAT2.alt1 |

| SS2  | EIM_D24.alt1     | EIM_D24.alt4    | DISP0_DAT5.alt2 | EIM_D24.alt1 | SD1_DAT3.alt1 |

| SS3  | EIM_D25.alt1     | EIM_D25.alt4    | DISP0_DAT6.alt2 | EIM_D25.alt1 | SD2_DAT3.alt1 |

## Table 8-24. ECSPI IOMUX pin configuration (continued)

1. The N/A in the ROM code indicates that the pins are not available or not used.

## 8.6 Program image

This section describes the data structures that are required to be included in the user's program image. The program image consists of:

- Image vector table—a list of pointers located at a fixed address that the ROM examines to determine where the other components of the program image are located.

- Boot data—a table that indicates the program image location, program image size in bytes, and the plugin flag.

- Device configuration data—IC configuration data.

- User code and data.

## 8.6.1 Image Vector Table and Boot Data

The Image Vector Table (IVT) is the data structure that the ROM reads from the boot device supplying the program image containing the required data components to perform a successful boot.

The IVT includes the program image entry point, a pointer to Device Configuration Data (DCD) and other pointers used by the ROM during the boot process. The ROM locates the IVT at a fixed address that is determined by the boot device connected to the Chip. The IVT offset from the base address and initial load region size for each boot device

| Field         | Description  |

|---------------|--------------|

| 4<br>spd_tx   | SPD packet   |

| 3<br>vsd_tx   | VSD packet   |

| 2<br>iscr2_tx | ISRC2 packet |

| 1<br>isr1_tx  | ISRC1 packet |

| 0<br>acp_tx   | ACP packet   |

#### HDMI\_FC\_DATMAN field descriptions (continued)

## 33.5.132 Frame Composer Data Island Auto Packet Scheduling Register 3 (HDMI\_FC\_DATAUTO3)

Configures the Frame Composer Automatic(1)/RDRB(0) data island packet insertion for AVI, GCP, AUDI and ACR packets. In Automatic mode, the packet will be inserted on Vblanking when first line with active Vsync appears.

- Address Offset: 0x10B7

- Size: 8 bits

- Value after Reset: 0x0F

- Access: Read/Write

Address: 12\_0000h base + 10B7h offset = 12\_10B7h

| Bit           | 7 | 6    | 5     | 4 | 3        | 2        | 1         | 0        |

|---------------|---|------|-------|---|----------|----------|-----------|----------|

| Read<br>Write |   | Rese | erved |   | avi_auto | gcp_auto | audi_auto | acr_auto |

| Reset         | 0 | 0    | 0     | 0 | 1        | 1        | 1         | 1        |

## HDMI\_FC\_DATAUTO3 field descriptions

| Field          | Description                         |

|----------------|-------------------------------------|

| 7-4            | This field is reserved.<br>Reserved |

| 3<br>avi_auto  | Enable AVI packet insertion         |

| 2<br>gcp_auto  | Enable GCP packet insertion         |

| 1<br>audi_auto | Enable AUDI packet insertion        |

| 0<br>acr_auto  | Enable ACR packet insertion         |

## 36.4.9 GPR (IOMUXC\_GPR8)

Address: 20E\_0000h base + 20h offset = 20E\_0020h

| Bit   | 31 | 30  | 29 | 28      | 27  | 26  | 25      | 24 | 23    | 22 | 21    | 20  | 19  | 18 | 17 | 16  | 15   | 14   | 13 | 12 | 11 | 10  | 9   | 8   | 7  | 6  | 5  | 4   | 3    | 2   | 1  | 0  |

|-------|----|-----|----|---------|-----|-----|---------|----|-------|----|-------|-----|-----|----|----|-----|------|------|----|----|----|-----|-----|-----|----|----|----|-----|------|-----|----|----|

| R     |    | ~   | ту | <u></u> |     |     | <b></b> |    | · · · | ту | C\\// |     |     |    | PC | S_1 | TX_I | DEE  | MP | H_ | PC | S_1 | Χ_  | DEE | MP | Н_ | PC | S_1 | TX_I | DEE | MP | H_ |

| w     | PC | JO_ |    | 300     | ING | _LC | , vv    | PU | ,S_   | 1. | 3001  | NG_ | _FU | LL |    | G   | EN2  | 2_6E | ЭB |    |    | GE  | N2_ | 3P5 | DB |    |    |     | GE   | N1  |    |    |

| Reset | 0  | 0   | 0  | 0       | 0   | 0   | 0       | 0  | 0     | 0  | 0     | 0   | 0   | 0  | 0  | 0   | 0    | 0    | 0  | 0  | 0  | 0   | 0   | 0   | 0  | 0  | 0  | 0   | 0    | 0   | 0  | 0  |

#### IOMUXC\_GPR8 field descriptions

| Field                                    | Description                                                                                                                                                                                                                  |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-25<br>PCS_TX_<br>SWING_LOW            | PCIe_PHY - This static value sets the launch amplitude of the transmitter when pipe0_tx_swing is set to 1'b0 (default state).<br>7'hxx - TX launch amplitude swing_low value.                                                |

| 24–18<br>PCS_TX_<br>SWING_FULL           | PCIe_PHY - This static value sets the Tx driver SWING_FULL value.<br>7'hxx - Gen2 TX SWING FULL value.                                                                                                                       |

| 17-12<br>PCS_TX_<br>DEEMPH_<br>GEN2_6DB  | PCIe_PHY - This static value sets the Tx driver de-emphasis value in the case where pipe0_tx_deemph is set to 1'b0 and the PHY is running at the Gen2 (6db) rate.<br>6'hxx - Gen2 (6db) De-emphasis value.                   |

| 11–6<br>PCS_TX_<br>DEEMPH_<br>GEN2_3P5DB | PCIe_PHY - This static value sets the Tx driver de-emphasis value in the case where pipe0_tx_deemph is set to 1'b1 (the default setting) and the PHY is running at the Gen2 (3p5db) rate.<br>6'hxx - Gen2 De-emphasis value. |

| PCS_TX_<br>DEEMPH_GEN1                   | PCIe_PHY - This static value sets the Tx driver de-emphasis value in the case where pipe0_tx_deemph is set to 1'b1 (the default setting) and the PHY is running at the Gen1 rate.<br>6'hxx - Gen1 De-emphasis value.         |

## 36.4.31 Pad Mux Register (IOMUXC\_SW\_MUX\_CTL\_PAD\_EIM\_EB2\_B)

Address: 20E\_0000h base + 8Ch offset = 20E\_008Ch

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20   | 19 | 18 | 17 | 16 |  |  |

|-------|----|----|----|----|----|----|----|----|----|----|----|------|----|----|----|----|--|--|

| R     | 0  |    |    |    |    |    |    |    |    |    |    |      |    |    |    |    |  |  |

| w     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |    |    |  |  |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0  | 0  | 0  | 0  |  |  |

|       |    |    |    |    |    |    |    |    |    |    |    |      |    |    |    |    |  |  |

| Bit   | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4    | 3  | 2  | 1  | 0  |  |  |

| R     |    |    |    |    |    | 0  |    |    |    |    |    | SION |    |    |    |    |  |  |

| w     |    |    |    |    |    |    |    |    |    |    |    |      |    |    |    |    |  |  |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0  | 1  | 0  | 1  |  |  |

#### IOMUXC\_SW\_MUX\_CTL\_PAD\_EIM\_EB2\_B field descriptions

| Field            | Description                                                                                                                                |  |  |  |  |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| 31–5<br>Reserved | This read-only field is reserved and always has the value 0.                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| 4<br>SION        | Software Input On Field.                                                                                                                   |  |  |  |  |  |  |  |  |  |  |  |

|                  | Force the selected mux mode input path no matter of MUX_MODE functionality.                                                                |  |  |  |  |  |  |  |  |  |  |  |

|                  | 1 <b>ENABLED</b> — Force input path of pad EIM_EB2.                                                                                        |  |  |  |  |  |  |  |  |  |  |  |

|                  | 0 <b>DISABLED</b> — Input Path is determined by functionality of the selected mux mode (regular).                                          |  |  |  |  |  |  |  |  |  |  |  |

| 3<br>Reserved    | This read-only field is reserved and always has the value 0.                                                                               |  |  |  |  |  |  |  |  |  |  |  |

| MUX_MODE         | MUX Mode Select Field.                                                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|                  | Select 1 of 7 iomux modes to be used for pad: EIM_EB2.                                                                                     |  |  |  |  |  |  |  |  |  |  |  |

|                  | NOTE: Pad EIM_EB2 is involved in Daisy Chain.                                                                                              |  |  |  |  |  |  |  |  |  |  |  |

|                  | 000 ALT0 — Select signal EIM_EB2_B.                                                                                                        |  |  |  |  |  |  |  |  |  |  |  |

|                  | 001 ALT1 — Select signal ECSPI1_SS0.                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

|                  | <ul> <li>Configure register IOMUXC_ECSPI1_SS0_SELECT_INPUT for mode ALT1.</li> <li>ALT3 — Select signal IPU2_CSI1_DATA19.</li> </ul>       |  |  |  |  |  |  |  |  |  |  |  |

|                  | <ul> <li>Configure register IOMUXC_IPU2_SENS1_DATA19_SELECT_INPUT for mode ALT3.</li> <li>ALT4 — Select signal HDMI_TX_DDC_SCL.</li> </ul> |  |  |  |  |  |  |  |  |  |  |  |

|                  | - Configure register IOMUXC_HDMI_II2C_CLKIN_SELECT_INPUT for mode ALT4.                                                                    |  |  |  |  |  |  |  |  |  |  |  |

|                  | 101 ALT5 — Select signal GPIO2_IO30.                                                                                                       |  |  |  |  |  |  |  |  |  |  |  |

|                  | 110 ALT6 — Select signal I2C2_SCL.                                                                                                         |  |  |  |  |  |  |  |  |  |  |  |

|                  | - Configure register IOMUXC_I2C2_SCL_IN_SELECT_INPUT for mode ALT6.<br>111 <b>ALT7</b> — Select signal SRC_BOOT_CFG30.                     |  |  |  |  |  |  |  |  |  |  |  |

#### IOMUXC Memory Map/Register Definition

## IOMUXC\_SW\_PAD\_CTL\_PAD\_DI0\_PIN02 field descriptions

| Field             | Description                                                                                            |  |  |  |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 31–17<br>Reserved | This read-only field is reserved and always has the value 0.                                           |  |  |  |  |  |  |  |  |  |

| 16                | Hysteresis Enable Field                                                                                |  |  |  |  |  |  |  |  |  |

| HYS               | Select one of next values for pad: DI0_PIN2.                                                           |  |  |  |  |  |  |  |  |  |

|                   | <ul> <li>DISABLED — CMOS input</li> <li>ENABLED — Schmitt trigger input</li> </ul>                     |  |  |  |  |  |  |  |  |  |

| 15–14             | Pull Up / Down Config. Field                                                                           |  |  |  |  |  |  |  |  |  |

| PUS               | Select one of next values for pad: DI0_PIN2.                                                           |  |  |  |  |  |  |  |  |  |

|                   | 00 <b>100K_OHM_PD</b> — 100K Ohm Pull Down                                                             |  |  |  |  |  |  |  |  |  |

|                   | 01 <b>47K_OHM_PU</b> — 47K Ohm Pull Up                                                                 |  |  |  |  |  |  |  |  |  |

|                   | 10 <b>100K_OHM_PU</b> — 100K Ohm Pull Up                                                               |  |  |  |  |  |  |  |  |  |

|                   | 11 <b>22K_OHM_PU</b> — 22K Ohm Pull Up                                                                 |  |  |  |  |  |  |  |  |  |

| 13<br>PUE         | Pull / Keep Select Field                                                                               |  |  |  |  |  |  |  |  |  |

| TOL               | Select one of next values for pad: DI0_PIN2.                                                           |  |  |  |  |  |  |  |  |  |

|                   | 0 <b>KEEP</b> — Keeper Enabled                                                                         |  |  |  |  |  |  |  |  |  |

|                   | 1 PULL — Pull Enabled                                                                                  |  |  |  |  |  |  |  |  |  |

| 12<br>PKE         | Pull / Keep Enable Field                                                                               |  |  |  |  |  |  |  |  |  |

| FRE               | Select one of next values for pad: DI0_PIN2.                                                           |  |  |  |  |  |  |  |  |  |

|                   | 0 <b>DISABLED</b> — Pull/Keeper Disabled                                                               |  |  |  |  |  |  |  |  |  |

|                   | 1 ENABLED — Pull/Keeper Enabled                                                                        |  |  |  |  |  |  |  |  |  |

| 11<br>ODE         | Open Drain Enable Field                                                                                |  |  |  |  |  |  |  |  |  |

| ODL               | Enables open drain of the pin.                                                                         |  |  |  |  |  |  |  |  |  |

|                   | 0 <b>DISABLED</b> — Output is CMOS.                                                                    |  |  |  |  |  |  |  |  |  |

|                   | 1 ENABLED — Output is Open Drain.                                                                      |  |  |  |  |  |  |  |  |  |

| 10–8<br>Reserved  | This read-only field is reserved and always has the value 0.                                           |  |  |  |  |  |  |  |  |  |

| 7–6               | Speed Field                                                                                            |  |  |  |  |  |  |  |  |  |

| SPEED             | Select one of next values for pad: DI0_PIN2.                                                           |  |  |  |  |  |  |  |  |  |

|                   | 00 LOW — 50 MHz (SRE=x)                                                                                |  |  |  |  |  |  |  |  |  |

|                   | 01 MEDIUM — 100 MHz, if SRE=1: 100MHz @ 1.8V, 150MHz @ 3.3V                                            |  |  |  |  |  |  |  |  |  |

|                   | 10 MEDIUM — 100 MHz, if SRE=1: 100MHz @ 1.8V, 150MHz @ 3.3V                                            |  |  |  |  |  |  |  |  |  |

|                   | 11 MAXIMUM — 100 MHz, if SRE=1: 150MHz @ 1.8V, 200MHz @ 3.3V                                           |  |  |  |  |  |  |  |  |  |

| 5–3<br>DSE        | Drive Strength Field<br>Select one of next values for pad: DI0_PIN2.                                   |  |  |  |  |  |  |  |  |  |

|                   |                                                                                                        |  |  |  |  |  |  |  |  |  |

|                   | 000 <b>HIZ</b> — HI-Z                                                                                  |  |  |  |  |  |  |  |  |  |

|                   | 001 <b>260_OHM</b> — 150 Ohm @ 3.3V, 260 Ohm @ 1.8V                                                    |  |  |  |  |  |  |  |  |  |

|                   | 010 <b>130_OHM</b> — 75 Ohm @ 3.3V, 130 Ohm @ 1.8V<br>011 <b>90_OHM</b> — 50 Ohm @ 3.3V, 90 Ohm @ 1.8V |  |  |  |  |  |  |  |  |  |

|                   | Table continues on the next page                                                                       |  |  |  |  |  |  |  |  |  |

Table continues on the next page ...

Chapter 37 Image Processing Unit (IPU)

| Table 37-15. | Channel Parameters Memory for interleaved | (continued) |

|--------------|-------------------------------------------|-------------|

|--------------|-------------------------------------------|-------------|

|                       | 1       | 1      | -           |                                                                                               |

|-----------------------|---------|--------|-------------|-----------------------------------------------------------------------------------------------|

|                       |         |        |             | 3'h3 = 16 Bits per pixel                                                                      |

|                       |         |        |             | 3'h4 = 12 Bits per pixel                                                                      |

|                       |         |        |             | 3'h5 = 08 Bits per pixel                                                                      |

|                       |         |        |             | 3'h6 = 04 Bits per pixel                                                                      |

| Decode Address Select | DEC_SEL | 2 bits | W0[111:110] | Upon 4BPP, selects between two look-<br>up tables                                             |

|                       |         |        |             | DEC_SEL                                                                                       |

|                       |         |        |             | 00 = addresses 0 to 15                                                                        |

|                       |         |        |             | 01 = addresses 64 to 79                                                                       |

|                       |         |        |             | 10 = addresses 128 to 143                                                                     |

|                       |         |        |             | 11 = addresses 192 to 207                                                                     |

| Access Dimension      | DIM     | 1 bit  | W0[112]     | DIM = 0 Access Dimension is 2d                                                                |

|                       |         |        |             | DIM = 1 Access Dimension is 1d                                                                |

| Scan Order            | SO      | 1 bit  | W0[113]     | SO = 0 Scan order is progressive                                                              |

|                       |         |        |             | SO = 1 Scan order is interlaced                                                               |

| Band Mode             | BNDM    | 3 bits | W0[116:114] | BNDM = 000 bands disable.                                                                     |

|                       |         |        |             | BNDM = 001 bands enable. Band<br>height = 4 lines.                                            |

|                       |         |        |             | BNDM = 010 bands enable. Band<br>height = 8 lines.                                            |

|                       |         |        |             | BNDM = 011 bands enable. Band<br>height = 16 lines.                                           |

|                       |         |        |             | BNDM = 100 bands enable. Band<br>height = 32 lines.                                           |

|                       |         |        |             | BNDM = 101 bands enable. Band<br>height = 64 lines.                                           |

|                       |         |        |             | BNDM = 110 bands enable. Band<br>height = 128 lines.                                          |

|                       |         |        |             | BNDM = 111 bands enable. Band<br>height = 256                                                 |

|                       |         |        |             | When working in band mode, the<br>channel's corresponding<br>IDMAC_BNDM_EN bit has to be set. |

| Block Mode            | BM      | 2 bits | W0[118:117] | BM = 00 block mode disable. BW = FW, BH = FH                                                  |

|                       |         |        |             | BM = 01 block mode enable. $BW = 8$ , $BH = 8$                                                |

|                       |         |        |             | BM = 10 block mode enable. BW = 16,<br>BH = 16 (this mode is reserved for<br>future use)      |

|                       |         |        |             | BM = 11 not used                                                                              |

| Rotation              | ROT     | 1 bit  | W0[119]     | ROT = 0 -> No rotation                                                                        |

|                       |         |        |             | ROT = 1 -> 90 degree rotation<br>clockwise                                                    |

Table continues on the next page ...

| IPU memory | map ( | (continued) |

|------------|-------|-------------|

|------------|-------|-------------|

| Absolute<br>address<br>(hex) | Register name                                                 | Width<br>(in bits) | Access | Reset value | Section/<br>page  |

|------------------------------|---------------------------------------------------------------|--------------------|--------|-------------|-------------------|

| 265_8154                     | DC Mapping Configuration Register 19<br>(IPU1_DC_MAP_CONF_19) | 32                 | R/W    | 0000_0000h  | 37.5.353/<br>3436 |

| 265_8158                     | DC Mapping Configuration Register 20<br>(IPU1_DC_MAP_CONF_20) | 32                 | R/W    | 0000_0000h  | 37.5.354/<br>3437 |

| 265_815C                     | DC Mapping Configuration Register 21<br>(IPU1_DC_MAP_CONF_21) | 32                 | R/W    | 0000_0000h  | 37.5.355/<br>3438 |

| 265_8160                     | DC Mapping Configuration Register 22<br>(IPU1_DC_MAP_CONF_22) | 32                 | R/W    | 0000_0000h  | 37.5.356/<br>3438 |

| 265_8164                     | DC Mapping Configuration Register 23<br>(IPU1_DC_MAP_CONF_23) | 32                 | R/W    | 0000_0000h  | 37.5.357/<br>3439 |

| 265_8168                     | DC Mapping Configuration Register 24<br>(IPU1_DC_MAP_CONF_24) | 32                 | R/W    | 0000_0000h  | 37.5.358/<br>3440 |

| 265_816C                     | DC Mapping Configuration Register 25<br>(IPU1_DC_MAP_CONF_25) | 32                 | R/W    | 0000_0000h  | 37.5.359/<br>3440 |

| 265_8170                     | DC Mapping Configuration Register 26<br>(IPU1_DC_MAP_CONF_26) | 32                 | R/W    | 0000_0000h  | 37.5.360/<br>3441 |

| 265_8174                     | DC User General Data Event 0 Register 0<br>(IPU1_DC_UGDE0_0)  | 32                 | R/W    | 0000_0000h  | 37.5.361/<br>3442 |

| 265_8178                     | DC User General Data Event 0 Register 1<br>(IPU1_DC_UGDE0_1)  | 32                 | R/W    | 0000_0000h  | 37.5.362/<br>3443 |

| 265_817C                     | DC User General Data Event 0 Register2<br>(IPU1_DC_UGDE0_2)   | 32                 | R/W    | 0000_0000h  | 37.5.363/<br>3444 |

| 265_8180                     | DC User General Data Event 0 Register 3<br>(IPU1_DC_UGDE0_3)  | 32                 | R/W    | 0000_0000h  | 37.5.364/<br>3444 |

| 265_8184                     | DC User General Data Event 1Register0<br>(IPU1_DC_UGDE1_0)    | 32                 | R/W    | 0000_0000h  | 37.5.365/<br>3445 |

| 265_8188                     | DC User General Data Event 1 Register 1<br>(IPU1_DC_UGDE1_1)  | 32                 | R/W    | 0000_0000h  | 37.5.366/<br>3446 |

| 265_818C                     | DC User General Data Event 1Register 2<br>(IPU1_DC_UGDE1_2)   | 32                 | R/W    | 0000_0000h  | 37.5.367/<br>3447 |

| 265_8190                     | DC User General Data Event 1Register 3<br>(IPU1_DC_UGDE1_3)   | 32                 | R/W    | 0000_0000h  | 37.5.368/<br>3447 |

| 265_8194                     | DC User General Data Event 2 Register 0<br>(IPU1_DC_UGDE2_0)  | 32                 | R/W    | 0000_0000h  | 37.5.369/<br>3448 |

| 265_8198                     | DC User General Data Event 2 Register 1<br>(IPU1_DC_UGDE2_1)  | 32                 | R/W    | 0000_0000h  | 37.5.370/<br>3449 |

| 265_819C                     | DC User General Data Event 2Register 2<br>(IPU1_DC_UGDE2_2)   | 32                 | R/W    | 0000_0000h  | 37.5.371/<br>3450 |

| 265_81A0                     | DC User General Data Event 2Register 3<br>(IPU1_DC_UGDE2_3)   | 32                 | R/W    | 0000_0000h  | 37.5.372/<br>3450 |

| 265_81A4                     | DC User General Data Event 3Register 0<br>(IPU1_DC_UGDE3_0)   | 32                 | R/W    | 0000_0000h  | 37.5.373/<br>3451 |

| 265_81A8                     | DC User General Data Event 3Register 1<br>(IPU1_DC_UGDE3_1)   | 32                 | R/W    | 0000_0000h  | 37.5.374/<br>3452 |

Table continues on the next page ...

| IPUx_INT_ | CTRL_ | 10 field | descriptions | (continued) |

|-----------|-------|----------|--------------|-------------|

|-----------|-------|----------|--------------|-------------|

| Field                   | Description                                                                                                                     |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

|                         | 0 Interrupt is disabled.                                                                                                        |

|                         | 1 Interrupt is enabled.                                                                                                         |

| 16                      | Tearing Error #1 enable                                                                                                         |

| DC_TEARING_<br>ERR_1_EN | This bit enables the interrupt that is a result of tearing error while the anti tearing mechanism is activated for DC channel 1 |

|                         | 0 Interrupt is disabled.                                                                                                        |

|                         | 1 Interrupt is enabled.                                                                                                         |

| 15–4<br>Reserved        | This read-only field is reserved and always has the value 0.                                                                    |

| 3                       | Frame Lost of SMFC channel 3 interrupt enable bit                                                                               |

| SMFC3_FRM_<br>LOST_EN   | This bit enables an interrupt that is a result of a Frame Lost of SMFC channel 3.                                               |

|                         | 0 Interrupt is disabled.                                                                                                        |

|                         | 1 Interrupt is enabled.                                                                                                         |

| 2                       | Frame Lost of SMFC channel 2 interrupt enable bit                                                                               |

| SMFC2_FRM_<br>LOST_EN   | This bit enables an interrupt that is a result of a Frame Lost of SMFC channel 2.                                               |

|                         | 0 Interrupt is disabled.                                                                                                        |

|                         | 1 Interrupt is enabled.                                                                                                         |

| 1                       | Frame Lost of SMFC channel 1 interrupt enable bit                                                                               |

| SMFC1_FRM_<br>LOST_EN   | This bit enables an interrupt that is a result of a Frame Lost of SMFC channel 1.                                               |

|                         | 0 Interrupt is disabled.                                                                                                        |

|                         | 1 Interrupt is enabled.                                                                                                         |

| 0                       | Frame Lost of SMFC channel 0 interrupt enable bit                                                                               |

| SMFC0_FRM_<br>LOST_EN   | This bit enables an interrupt that is a result of a Frame Lost of SMFC channel 0.                                               |

|                         | 0 Interrupt is disabled.                                                                                                        |

|                         | 1 Interrupt is enabled.                                                                                                         |

## 37.5.16 Interrupt Control Register 11 (IPUx\_INT\_CTRL\_11)

This register contains part of IPU interrupts controls. The controls of the end-of-band indication (EOBND) of DMA Channels interrupts [31:0] can be found in this register.

- Hide VDOA\_SYNC for all versions

- Show VDOA\_SYNC for IPUv3H version.

- The table below tagged with other settings (like IPU3M\_only) should be hidden in IPUv3H version.

## 37.5.341 DC Mapping Configuration Register 7 (IPUx\_DC\_MAP\_CONF\_7)

Address: Base address + 5\_8124h offset

| Bit    | 31 | 30 | 29     | 28     | 27    | 26  | 25 | 24     | 23   | 22     | 21  | 20  | 19    | 18         | 17    | 16  |

|--------|----|----|--------|--------|-------|-----|----|--------|------|--------|-----|-----|-------|------------|-------|-----|

| R      | 0  | MA | PPING  | PNTR   | BYTE2 | 15  | MA | PPING  | PNTR | _BYTE1 | 15  | MAF | PING  | PNTR       | BYTEO | 15  |

| W      |    |    |        |        | -     | _   |    | -      |      | _      | _   |     | _     |            | -     | _   |

| Reset  | 0  | 0  | 0      | 0      | 0     | 0   | 0  | 0      | 0    | 0      | 0   | 0   | 0     | 0          | 0     | 0   |

|        |    |    |        |        |       |     |    |        | •    |        |     |     |       |            |       |     |

| Bit    | 15 | 14 | 13     | 12     | 11    | 10  | 9  | 8      | 7    | 6      | 5   | 4   | 3     | 2          | 1     | 0   |

| R      | 0  | МА |        |        | BVTE2 | 1/  | MA |        |      | BVTE1  | 1/  | МА  |       |            | BVTEO | 1/  |

| w      |    |    | TING_  |        |       | 14  |    |        |      |        | _14 |     | TING_ |            |       | _14 |

| Reset  | 0  | 0  | 0      | 0      | 0     | 0   | 0  | 0      | 0    | 0      | 0   | 0   | 0     | 0          | 0     | 0   |

| R<br>W | 0  | MA | PPING_ | _PNTR_ | BYTE2 | _14 | MA | PPING_ |      | BYTE1  | _14 | MAF |       | _<br>PNTR_ |       | )_1 |

#### IPUx\_DC\_MAP\_CONF\_7 field descriptions

| Field                                  | Description                                                                                                                             |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 31<br>Reserved                         | This read-only field is reserved and always has the value 0.                                                                            |

| 30–26<br>MAPPING_<br>PNTR_BYTE2_<br>15 | Mapping pointer #15 for Byte 2<br>This field is a pointer to the set of MD_OFFSET_ <i> and MD_MASK_<i> used for mapping byte #2</i></i> |

| 25–21<br>MAPPING_<br>PNTR_BYTE1_<br>15 | Mapping pointer #15 for Byte 1<br>This field is a pointer to the set of MD_OFFSET_ <i> and MD_MASK_<i> used for mapping byte #1</i></i> |

| 20–16<br>MAPPING_<br>PNTR_BYTE0_<br>15 | Mapping pointer #15 for Byte 0<br>This field is a pointer to the set of MD_OFFSET_ <i> and MD_MASK_<i> used for mapping byte #0</i></i> |

| 15<br>Reserved                         | This read-only field is reserved and always has the value 0.                                                                            |

| 14–10<br>MAPPING_<br>PNTR_BYTE2_<br>14 | Mapping pointer #14 for Byte 2<br>This field is a pointer to the set of MD_OFFSET_ <i> and MD_MASK_<i> used for mapping byte #2</i></i> |

| 9–5<br>MAPPING_<br>PNTR_BYTE1_<br>14   | Mapping pointer #14 for Byte 1<br>This field is a pointer to the set of MD_OFFSET_ <i> and MD_MASK_<i> used for mapping byte #1</i></i> |

| MAPPING_<br>PNTR_BYTE0_<br>14          | Mapping pointer #14 for Byte 0<br>This field is a pointer to the set of MD_OFFSET_ <i> and MD_MASK_<i> used for mapping byte #0</i></i> |

## Field Description DMA\_INSERT\_ IDLE\_NUM These bits used to set the number of "IDLE" cycles when DMA\_MODE == 2'b0x.

#### MIPI\_HSI\_AHB\_MASTER\_CONF field descriptions (continued)

## 42.5.42 TX Break Length Register (MIPI\_HSI\_TX\_BREAK\_LEN)

| This register used to set tx break length         |  |

|---------------------------------------------------|--|

| Address: 220_8000h base + 22Ch offset = 220_822Ch |  |

| Bit    | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19   | 18   | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3   | 2   | 1 | 0   |

|--------|----|----|----|----|----|----|----|----|----|----|----|----|------|------|----|----|----|----|----|----|----|----|---|---|---|---|---|---|-----|-----|---|-----|

| R<br>W |    |    |    |    |    |    |    |    |    |    |    | F  | Rese | erve | d  |    |    |    |    |    |    |    |   |   |   |   |   |   | col | JNT |   |     |

|        | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 4 | 0 | 0   | 4   |   | -   |

| Reset  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0    | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 |   | 0 | 0   | 1   | 0 | I I |

#### MIPI\_HSI\_TX\_BREAK\_LEN field descriptions

| Field            | Description                                              |

|------------------|----------------------------------------------------------|

| 31–6<br>Reserved | This field is reserved.<br>Reserved, always set to zero. |

| COUNT            | The tx break length count.                               |

|                  | 6'h00 64                                                 |

|                  | 6'h01 1                                                  |

|                  | 6'h3f 63                                                 |

#### MMDC Memory Map/Register Definition

Address: Base address + 430h offset

| Bit   | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| R     |    |    |    |    |    |    |    |    |    |    |    |    |    |    | SE | BS_ | ADE | R  |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| w     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |     |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Reset | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### MMDCx\_MASBS0 field descriptions

| [ | Field    | Description                                                                                               |

|---|----------|-----------------------------------------------------------------------------------------------------------|

|   | SBS_ADDR | Step By Step Address. These bits reflect the address of the pending request in case of step by step mode. |

# 44.12.29 MMDC Core Step By Step Address Attributes Register (MMDCx\_MASBS1)

Supported Mode Of Operations:

For Channel 0: All

For Channel 1: LP2\_2ch\_x16, LP2\_2ch\_x32

Address: Base address + 434h offset Bit R SBS\_AXI\_ID W Reset Bit SBS\_ SBS\_ SBS\_ SBS\_LEN SBS\_BURST SBS\_SIZE SBS\_PROT SBS\_LOCK R BUFF TYPE VLD W Reset

#### MMDCx\_MASBS1 field descriptions

| Field               | Description                                                                                                                                                                                                                  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–16<br>SBS_AXI_ID | Step By Step AXI ID. These bits reflect the AXI ID of the pending request in case of step by step mode.                                                                                                                      |

| 15–13<br>SBS_LEN    | <ul> <li>Step By Step Length. These bits reflect the AXI LENGTH of the pending request in case of step by step mode.</li> <li>000 burst of length 1</li> <li>001 burst of length 2</li> <li>111 burst of length 8</li> </ul> |

| 12<br>SBS_BUFF      | Step By Step Buffered. This bit reflect the AXI CACHE[0] of the pending request in case of step by step mode. Relevant only for write requests                                                                               |

Table continues on the next page ...

## 48.12.29 VCn Non-Posted Buffer Depth (PCIE\_PL\_VCnNPBD)

### Offset: 0x700 + 0xAC + C\*n (n=[1:7])

Address: 1FF\_C000h base + 7B8h offset + (12d  $\times$  i), where i=0d to 6d

| Bit   | 31   | 30    | 29   | 28    | 27 | 26 | 25   | 24     | 23      | 22     | 21     | 20     | 19     | 18    | 17 | 16 |

|-------|------|-------|------|-------|----|----|------|--------|---------|--------|--------|--------|--------|-------|----|----|

| R     |      |       | Deee |       |    |    |      |        | VCn_    | Non_Po | sted_H | eader_ | Queue_ | Depth |    |    |

| w     |      |       | Rese | erved |    |    |      |        |         |        |        |        |        |       |    |    |

| Reset | 0    | 0     | 0    | 0     | 0  | 0  | 0    | 0      | 0       | 0      | 0      | 0      | 0      | 0     | 0  | 0  |

| Bit   | 15   | 14    | 13   | 12    | 11 | 10 | 9    | 8      | 7       | 6      | 5      | 4      | 3      | 2     | 1  | 0  |

| R     | Deer | erved |      |       |    |    | VCn_ | _Non_F | Posted_ | Data_Q | ueue_C | epth   |        |       |    |    |

| w     | Rese | erveu |      |       |    |    |      |        |         |        |        |        |        |       |    |    |

| Reset | 0    | 0     | 0    | 0     | 0  | 0  | 0    | 0      | 0       | 0      | 0      | 0      | 0      | 0     | 0  | 0  |

#### PCIE\_PL\_VCnNPBD field descriptions

| Field                                              | Description                                                                                                                                                                           |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–26                                              | This field is reserved.<br>Reserved                                                                                                                                                   |

| 25–16<br>VCn_Non_<br>Posted_Header_<br>Queue_Depth | VCn Non-Posted Header Queue Depth<br>Sets the number of entries in the Non-Posted header queue for VCn when using the segmented-buffer<br>configuration. Not writable through the DBI |

| 15–14<br>-                                         | This field is reserved.<br>Reserved                                                                                                                                                   |

| VCn_Non_<br>Posted_Data_<br>Queue_Depth            | VCn Non-Posted Data Queue Depth<br>Sets the number of entries in the Non-Posted data queue for VCn when using the segmented-buffer<br>configuration. Not writable through the DBI     |

## 51.7.6 PWM Counter Register (PWMx\_PWMCNR)

The read-only pulse-width modulator counter register (PWM\_PWMCNR) contains the current count value and can be read at any time without disturbing the counter.

Address: Base address + 14h offset

| Bit | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8   | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|-----|-----|---|---|---|---|---|---|---|

| R   |    |    |    |    |    |    |    | (  | )  |    |    |    |    |    |    |    |    |    |    |    |    |    |   | COL | JNT |   |   |   |   |   |   |   |

| w   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |     |     |   |   |   |   |   |   |   |

|     |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |     |     |   |   |   |   |   |   |   |

#### **PWMx\_PWMCNR** field descriptions

| Field             | Description                                                                                                              |

|-------------------|--------------------------------------------------------------------------------------------------------------------------|

| 31–16<br>Reserved | This field is reserved.<br>This read-only field is reserved and always has the value 0.                                  |

|                   | Counter Value. These bits are the counter register value and denotes the current count state the counter register is in. |

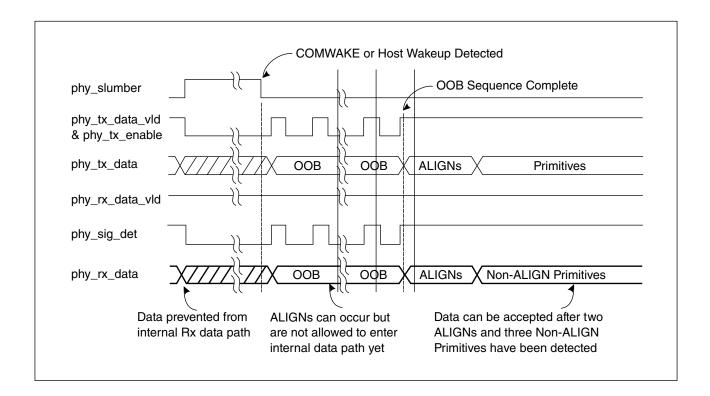

Figure 53-15. Power Mode Example: Rx and Tx In Link

## 53.3.4.6 Port Power Control Module

The Port Power Control Module (PCM) implements the following functions:

- Monitors Transport, Link and PHY ready/not ready conditions, as well as Device and Host power requests.

- Systematically controls the Link and Transport Layer transitions into and out of offline conditions (system reset, COMRESET and power modes).

- Allows clk\_asic0 and clk\_rbc0 to be stopped during Slumber and Partial power modes.

The PCM main function is to allow disabling clk\_asic0 and clk\_rbc0 in SATA power down modes.

## CAUTION

Clocks supplied to the core should never glitch at any time, including before, during, and after initialization and power modes. Clock glitch protection should be performed outside the core for any clocks that might glitch.

#### Instruction Set

- 000 GReg[0]

- 001 GReg[1]

- 010 GReg[2]

- 011 GReg[3]

- 100 GReg[4]

- 101 GReg[5]

- 110 GReg[6]

- 111 GReg[7]

## 55.5.2.51 XORI (Exclusive OR with Immediate)

#### **Operation:**

$GReg[r] \leftarrow GReg[r]$  ^ immediate

#### Assembler:

Syntax: xori r,immediate

Example: xor 7,5

XORs GReg[5] and decimal value 5 and stores the result in GReg[7]

CPU Flags: Unaffected

Cycles: 1

Description: Performs an eXclusive OR between a 0-extended 8-bit immediate value and a General Register; stores the result in the General Register. The immediate value is the low-order byte of the instruction and has a maximum value of 255 (0xFF).

Instruction Format

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| 0  | 0  | 0  | 1  | 0  | r  | r | r | i | i | i | i | i | i | i | i |

#### Instruction Fields:

#### rrr - register field:

- 000 GReg[0]

- 001 GReg[1]

- 010 GReg[2]

- 011 GReg[3]

## 64.4.3.9 Programmable CTS\_B Deassertion

The CTS\_B output can also be programmed to deassert when the RxFIFO reaches a certain level. Setting the CTS trigger level (UCR4[15:10]) at any value less than 32 deasserts the CTS\_B pin on detection of the valid start bit of the N + 1 character (where N is the trigger level setting). However, the receiver continues to receive characters until the RxFIFO is full.

## 64.4.3.10 TX\_DATA - UART Transmit

This is the transmitter serial output. When operating in RS-232/RS-485 mode, NRZ encoded data is transmitted, and the data can be inverted (controlled by INVT (UCR3[1])) before transmitted. When operating in infrared mode, a 3/16 bit-period pulse is output for each 0 bit transmitted, and no pulse is output for each 1 bit transmitted.

For RS-232/RS-485 applications, this pin must be connected to an RS-232/RS-485 transmitter. The operation of this output is the same regardless of whether the UART is in DTE or DCE mode. See Figure 64-3.

## UART memory map (continued)

| Absolute<br>address<br>(hex) | Register name                                  | Width<br>(in bits) | Access     | Reset value      | Section/<br>page  |

|------------------------------|------------------------------------------------|--------------------|------------|------------------|-------------------|

| 21F_0000                     | UART Receiver Register (UART4_URXD)            | 32                 | R          | 0000_0000h       | 64.15.1/<br>5211  |

| 21F_0040                     | UART Transmitter Register (UART4_UTXD)         | 32                 | w          | 0000_0000h       | 64.15.2/<br>5213  |

| 21F_0080                     | UART Control Register 1 (UART4_UCR1)           | 32                 | R/W        | 0000_0000h       | 64.15.3/<br>5214  |

| 21F_0084                     | UART Control Register 2 (UART4_UCR2)           | R/W                | 0000_0001h | 64.15.4/<br>5216 |                   |

| 21F_0088                     | UART Control Register 3 (UART4_UCR3)           | 32                 | R/W        | 0000_0700h       | 64.15.5/<br>5219  |

| 21F_008C                     | UART Control Register 4 (UART4_UCR4)           | 32                 | R/W        | 0000_8000h       | 64.15.6/<br>5221  |

| 21F_0090                     | UART FIFO Control Register (UART4_UFCR)        | 32                 | R/W        | 0000_0801h       | 64.15.7/<br>5223  |

| 21F_0094                     | UART Status Register 1 (UART4_USR1)            | 32                 | R/W        | 0000_2040h       | 64.15.8/<br>5225  |

| 21F_0098                     | UART Status Register 2 (UART4_USR2)            | 32                 | R/W        | 0000_4028h       | 64.15.9/<br>5228  |

| 21F_009C                     | UART Escape Character Register (UART4_UESC)    | 32                 | R/W        | 0000_002Bh       | 64.15.10/<br>5230 |

| 21F_00A0                     | UART Escape Timer Register (UART4_UTIM)        | 32                 | R/W        | 0000_0000h       | 64.15.11/<br>5231 |

| 21F_00A4                     | UART BRM Incremental Register (UART4_UBIR)     | 32                 | R/W        | 0000_0000h       | 64.15.12/<br>5231 |

| 21F_00A8                     | UART BRM Modulator Register (UART4_UBMR)       | 32                 | R/W        | 0000_0000h       | 64.15.13/<br>5232 |

| 21F_00AC                     | UART Baud Rate Count Register (UART4_UBRC)     | 32                 | R          | 0000_0004h       | 64.15.14/<br>5232 |

| 21F_00B0                     | UART One Millisecond Register (UART4_ONEMS)    | 32                 | R/W        | 0000_0000h       | 64.15.15/<br>5233 |

| 21F_00B4                     | UART Test Register (UART4_UTS)                 | 32                 | R/W        | 0000_0060h       | 64.15.16/<br>5234 |

| 21F_00B8                     | UART RS-485 Mode Control Register (UART4_UMCR) | 32                 | R/W        | 0000_0000h       | 64.15.17/<br>5235 |

| 21F_4000                     | UART Receiver Register (UART5_URXD)            | 32                 | R          | 0000_0000h       | 64.15.1/<br>5211  |

| 21F_4040                     | UART Transmitter Register (UART5_UTXD)         | 32                 | w          | 0000_0000h       | 64.15.2/<br>5213  |

| 21F_4080                     | UART Control Register 1 (UART5_UCR1)           | 32                 | R/W        | 0000_0000h       | 64.15.3/<br>5214  |

| 21F_4084                     | UART Control Register 2 (UART5_UCR2)           | 32                 | R/W        | 0000_0001h       | 64.15.4/<br>5216  |

| 21F_4088                     | UART Control Register 3 (UART5_UCR3)           | 32                 | R/W        | 0000_0700h       | 64.15.5/<br>5219  |

Table continues on the next page...

## 67.4.7 Card Insertion and Removal Detection

The uSDHC uses either the DATA3 pin or the CD\_B pin to detect card insertion or removal. When there is no card on the MMC/SD bus, the DATA3 will be pulled to a low voltage level by default.

When any card is inserted to or removed from the socket, the uSDHC detects the logic value changes on the DATA3 pin and generates an interrupt. When the DATA3 pin is not used for card detection (for example, it is implemented in GPIO), the CD\_B pin must be connected for card detection. Whether DATA3 is configured for card detection or not, the CD\_B pin is always a reference for card detection. Whether the DATA3 pin or the CD\_B pin is used to detect card insertion, the uSDHC will send an interrupt (if enabled) to inform the Host system that a card is inserted.

## 67.4.8 Power Management and Wake Up Events

When there is no operation between the uSDHC and the card through the SD bus, the user can completely disable the ipg\_clk and ipg\_perclk in the chip level clock control module to save power. When the user needs to use the uSDHC to communicate with the card, it can enable the clock and start the operation.

In some circumstances, when the clocks to the uSDHC are disabled, for instance, when the system is in low power mode, there are some events for which the user needs to enable the clock and handle the event. These events are called wakeup interrupts. The uSDHC can generate these interrupt even when there are no clocks enabled. The three interrupts which can be used as wake up events are:

- 1. Card Removal Interrupt

- 2. Card Insertion Interrupt

- 3. Interrupt from SDIO card

The uSDHC offers a power management feature. By clearing the clock enabled bits in the System Control Register, the clocks are gated in the low position to the uSDHC. For maximum power saving, the user can disable all the clocks to the uSDHC when there is no operation in progress.

These three wake up events (or wakeup interrupts) can also be used to wake up the system from low-power modes.

## NOTE

To make the interrupt a wakeup event, when all the clocks to the uSDHC are disabled or when the whole system is in low power mode, the corresponding wakeup enabled bit needs to be

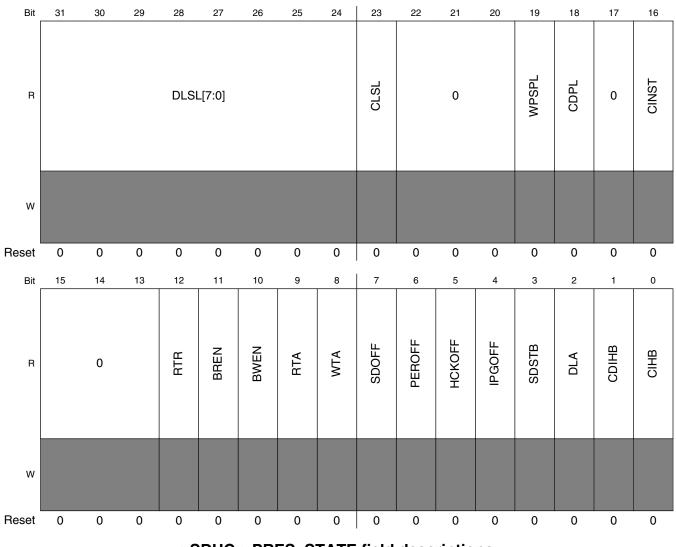

#### uSDHC Memory Map/Register Definition

Address: Base address + 24h offset

#### uSDHCx\_PRES\_STATE field descriptions

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–24<br>DLSL[7:0] | DATA[7:0] Line Signal Level<br>This status is used to check the DATA line level to recover from errors, and for debugging. This is<br>especially useful in detecting the busy signal level from DATA0. The reset value is affected by the external<br>pull-up / pull-down resistors. By default, the read value of this bit field after reset is 8'b11110111, when<br>DATA3 is pulled down and the other lines are pulled up. |

|                    | DATA7 Data 7 line signal level                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | DATA6 Data 6 line signal level                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | DATA5 Data 5 line signal level                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | DATA4 Data 4 line signal level                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | DATA3 Data 3 line signal level                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | DATA2 Data 2 line signal level                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | DATA1 Data 1 line signal level                                                                                                                                                                                                                                                                                                                                                                                                |

|                    | DATA0 Data 0 line signal level                                                                                                                                                                                                                                                                                                                                                                                                |

Table continues on the next page ...