Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Active                                                                |

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG      |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                    |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 64KB (64K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 64K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f105r8t7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 6       | Packa  | age inf | ormation                                                        | 82   |

|---------|--------|---------|-----------------------------------------------------------------|------|

|         | 6.1    | LFBGA   | A100 package information                                        | 82   |

|         | 6.2    | LQFP    | 100 package information                                         | 85   |

|         | 6.3    | LQFP    | 64 package information                                          | 88   |

|         | 6.4    | Therm   | al characteristics                                              | 91   |

|         |        | 6.4.1   | Reference document                                              | . 91 |

|         |        | 6.4.2   | Selecting the product temperature range                         | . 92 |

| 7       | Part r | numbe   | ring                                                            | 94   |

| Appendi | x A A  | pplicat | ion block diagrams                                              | 95   |

|         | A.1    | USB C   | DTG FS interface solutions                                      | 95   |

|         | A.2    | Ethern  | et interface solutions                                          | 97   |

|         | A.3    | Compl   | ete audio player solutions                                      | 99   |

|         | A.4    | USB C   | TG FS interface + Ethernet/I <sup>2</sup> S interface solutions | 100  |

| 8       | Revis  | ion his | story                                                           | 103  |

# 1 Introduction

This datasheet provides the description of the STM32F105xx and STM32F107xx connectivity line microcontrollers. For more details on the whole STMicroelectronics STM32F10xxx family, refer to *Section 2.2: Full compatibility throughout the family*.

The STM32F105xx and STM32F107xx datasheet should be read in conjunction with the STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory refer to the STM32F10xxx Flash programming manual.

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the www.arm.com website.

# 2 Description

The STM32F105xx and STM32F107xx connectivity line family incorporates the highperformance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 256 Kbytes and SRAM 64 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, four general-purpose 16-bit timers plus a PWM timer, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs, three SPIs, two I2Ss, five USARTs, an USB OTG FS and two CANs. Ethernet is available on the STM32F107xx only.

The STM32F105xx and STM32F107xx connectivity line family operates in the –40 to +105 °C temperature range, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

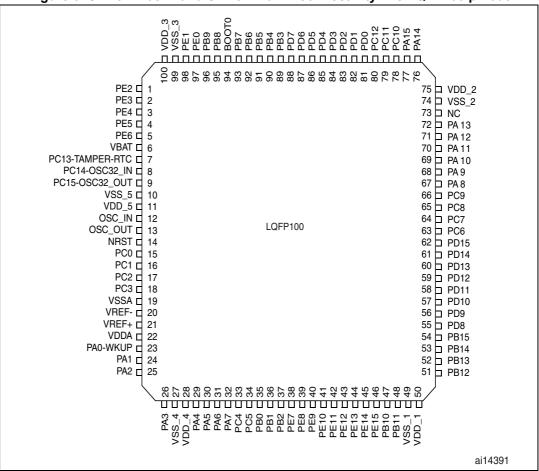

The STM32F105xx and STM32F107xx connectivity line family offers devices in three different package types: from 64 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F105xx and STM32F107xx connectivity line microcontroller family suitable for a wide range of applications such as motor drives and application control, medical and handheld equipment, industrial applications, PLCs, inverters, printers, and scanners, alarm systems, video intercom, HVAC and home audio equipment.

# 2.1 Device overview

Figure 1 shows the general block diagram of the device family.

| Peripherals <sup>(1)</sup> |                      | ST  | STM32F105Rx |       |     | STM32F107Rx |             | STM32F105Vx                |             |          | STM32F107Vx |  |

|----------------------------|----------------------|-----|-------------|-------|-----|-------------|-------------|----------------------------|-------------|----------|-------------|--|

| Flash men                  | 64                   | 128 | 256         | 128   | 256 | 64          | 128         | 256                        | 128         | 256      |             |  |

| SRAM in K                  | Kbytes               |     |             |       |     |             | 64          |                            |             | 1        |             |  |

| Package                    |                      |     |             | LQFP6 | 64  |             | LQFP<br>100 | LQFP<br>100,<br>BGA<br>100 | LQFP<br>100 | ,        |             |  |

| Ethernet                   |                      |     | No          |       | Y   | es          |             | No                         |             | Yes      |             |  |

|                            | General-<br>purpose  |     |             |       |     |             | 4           |                            |             | <u>.</u> |             |  |

| Timers                     | Advanced-<br>control | 1   |             |       |     |             |             |                            |             |          |             |  |

|                            | Basic                |     |             |       |     |             | 2           |                            |             |          |             |  |

| Tabla 2  | STM32E105vv a    | nd STM32E107vv     | fostures and | peripheral counts  |  |

|----------|------------------|--------------------|--------------|--------------------|--|

| Table 2. | 31 WJ32F 103XX a | 11U ST W32F 107 XX | leatures and | periprieral counts |  |

Any of the standard timers can be used to generate PWM outputs. Each of the timers has independent DMA request generations.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

## 2.3.16 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support 7/10-bit addressing mode and 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

## 2.3.17 Universal synchronous/asynchronous receiver transmitters (USARTs)

The STM32F105xx and STM32F107xx connectivity line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4 and UART5).

These five interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART1 interface is able to communicate at speeds of up to 4.5 Mbit/s. The other available interfaces communicate at up to 2.25 Mbit/s.

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes, that is 4 Kbytes in total

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 with the timestamp comparator connected to the TIM2 trigger input

- Triggers interrupt when system time becomes greater than target time

#### 2.3.21 Controller area network (CAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). The 256 bytes of SRAM which are allocated for each CAN (512 bytes in total) are not shared with any other peripheral.

#### 2.3.22 Universal serial bus on-the-go full-speed (USB OTG FS)

The STM32F105xx and STM32F107xx connectivity line devices embed a USB OTG fullspeed (12 Mb/s) device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- 1.25 KB of SRAM used exclusively by the endpoints (not shared with any other peripheral)

- 4 bidirectional endpoints

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

- the SOF output can be used to synchronize the external audio DAC clock in isochronous mode

- in accordance with the USB 2.0 Specification, the supported transfer speeds are:

- in Host mode: full speed and low speed

- in Device mode: full speed

## 2.3.23 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current-capable.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

I/Os on APB2 with up to 18 MHz toggling speed

Eight DAC trigger inputs are used in the STM32F105xx and STM32F107xx connectivity line family. The DAC channels are triggered through the timer update outputs that are also connected to different DMA channels.

## 2.3.27 Temperature sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V <  $V_{DDA}$  < 3.6 V. The temperature sensor is internally connected to the ADC1\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

## 2.3.28 Serial wire JTAG debug port (SWJ-DP)

The ARM SWJ-DP Interface is embedded, and is a combined JTAG and serial wire debug port that enables either a serial wire debug or a JTAG probe to be connected to the target. The JTAG TMS and TCK pins are shared respectively with SWDIO and SWCLK and a specific sequence on the TMS pin is used to switch between JTAG-DP and SW-DP.

### 2.3.29 Embedded Trace Macrocell™

The ARM<sup>®</sup> Embedded Trace Macrocell provides a greater visibility of the instruction and data flow inside the CPU core by streaming compressed data at a very high rate from the STM32F10xxx through a small number of ETM pins to an external hardware trace port analyzer (TPA) device. The TPA is connected to a host computer using USB, Ethernet, or any other high-speed channel. Real-time instruction and data flow activity can be recorded and then formatted for display on the host computer running debugger software. TPA hardware is commercially available from common development tool vendors. It operates with third party debugger software tools.

| Table | 5. | Pin | definitions |  |

|-------|----|-----|-------------|--|

|-------|----|-----|-------------|--|

|        | Pins   |         |                                    |                     |                            |                                                  | Alternate func                                                                            | tions <sup>(4)</sup> |

|--------|--------|---------|------------------------------------|---------------------|----------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------|

| BGA100 | LQFP64 | LQFP100 | Pin name                           | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                                   | Remap                |

| A3     | -      | 1       | PE2                                | I/O                 | FT                         | PE2                                              | TRACECK                                                                                   | -                    |

| B3     | -      | 2       | PE3                                | I/O                 | FT                         | PE3                                              | TRACED0                                                                                   | -                    |

| C3     | -      | 3       | PE4                                | I/O                 | FT                         | PE4                                              | TRACED1                                                                                   | -                    |

| D3     | -      | 4       | PE5                                | I/O                 | FT                         | PE5                                              | TRACED2                                                                                   | -                    |

| E3     | -      | 5       | PE6                                | I/O                 | FT                         | PE6                                              | TRACED3                                                                                   | -                    |

| B2     | 1      | 6       | V <sub>BAT</sub>                   | S                   | -                          | V <sub>BAT</sub>                                 | -                                                                                         | -                    |

| A2     | 2      | 7       | PC13-TAMPER-<br>RTC <sup>(5)</sup> | I/O                 | -                          | PC13 <sup>(6)</sup>                              | TAMPER-RTC                                                                                | -                    |

| A1     | 3      | 8       | PC14-<br>OSC32_IN <sup>(5)</sup>   | I/O                 | -                          | PC14 <sup>(6)</sup>                              | OSC32_IN                                                                                  | -                    |

| B1     | 4      | 9       | PC15-<br>OSC32_OUT <sup>(5)</sup>  | I/O                 | -                          | PC15 <sup>(6)</sup>                              | OSC32_OUT                                                                                 | -                    |

| C2     | -      | 10      | V <sub>SS_5</sub>                  | S                   | -                          | V <sub>SS_5</sub>                                | -                                                                                         | -                    |

| D2     | -      | 11      | V <sub>DD_5</sub>                  | S                   | -                          | V <sub>DD_5</sub>                                | -                                                                                         | -                    |

| C1     | 5      | 12      | OSC_IN                             | Ι                   | -                          | OSC_IN                                           | -                                                                                         | -                    |

| D1     | 6      | 13      | OSC_OUT                            | 0                   | -                          | OSC_OUT                                          | -                                                                                         | -                    |

| E1     | 7      | 14      | NRST                               | I/O                 | -                          | NRST                                             | -                                                                                         | -                    |

| F1     | 8      | 15      | PC0                                | I/O                 | -                          | PC0                                              | ADC12_IN10                                                                                | -                    |

| F2     | 9      | 16      | PC1                                | I/O                 | -                          | PC1                                              | ADC12_IN11/ ETH_MII_MDC/<br>ETH_RMII_MDC                                                  | -                    |

| E2     | 10     | 17      | PC2                                | I/O                 | -                          | PC2                                              | ADC12_IN12/ ETH_MII_TXD2                                                                  | -                    |

| F3     | 11     | 18      | PC3                                | I/O                 | -                          | PC3                                              | ADC12_IN13/<br>ETH_MII_TX_CLK                                                             | -                    |

| G1     | 12     | 19      | V <sub>SSA</sub>                   | S                   | -                          | V <sub>SSA</sub>                                 | -                                                                                         | -                    |

| H1     | -      | 20      | V <sub>REF-</sub>                  | S                   | -                          | V <sub>REF-</sub>                                | -                                                                                         | -                    |

| J1     | -      | 21      | V <sub>REF+</sub>                  | S                   | -                          | V <sub>REF+</sub>                                | -                                                                                         | -                    |

| K1     | 13     | 22      | V <sub>DDA</sub>                   | S                   | -                          | V <sub>DDA</sub>                                 | -                                                                                         | -                    |

| G2     | 14     | 23      | PA0-WKUP                           | I/O                 | -                          | PA0                                              | WKUP/USART2_CTS <sup>(7)</sup><br>ADC12_IN0/TIM2_CH1_ETR<br>TIM5_CH1/<br>ETH_MII_CRS_WKUP | -                    |

# 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for  $T_A$ .

| Symbol           | Parameter                      | Condition | Min | Мах | Unit  |

|------------------|--------------------------------|-----------|-----|-----|-------|

| t <sub>VDD</sub> | $V_{\text{DD}}$ rise time rate |           | 0   | -   | μs/V  |

| TJ               | V <sub>DD</sub> fall time rate | -         | 20  | -   | μ5/ V |

Table 10. Operating condition at power-up / power down

# 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 11* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Parameter                | Conditions                  | Min                | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Max  | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.26 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=000 (falling edge) | 2                  | 2.08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.16 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.37 | V    |

| V <sub>PVD</sub> Programmable voltage<br>detector level selection         PLS[2:0]=001 (rising edge)         2.19         2.28           PLS[2:0]=001 (falling edge)         2.09         2.18           PLS[2:0]=010 (rising edge)         2.28         2.38           PLS[2:0]=010 (rising edge)         2.18         2.28           PLS[2:0]=010 (rising edge)         2.18         2.28           PLS[2:0]=011 (rising edge)         2.38         2.48           PLS[2:0]=011 (rising edge)         2.28         2.38           PLS[2:0]=011 (rising edge)         2.28         2.38           PLS[2:0]=010 (rising edge)         2.38         2.48           PLS[2:0]=100 (rising edge)         2.47         2.58           PLS[2:0]=100 (rising edge)         2.37         2.48           PLS[2:0]=101 (rising edge)         2.57         2.68 | 2.27                     | V                           |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.48 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=010 (falling edge) | 2.18               | 2.28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.38 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.58 | V    |

| V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.28               | 2.38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.48 | V    |

| V <sub>PVD</sub> Programmable voltage     PLS[2:0]=100 (rising edge)     2.4       PLS[2:0]=100 (falling edge)     2.3       PLS[2:0]=101 (rising edge)     2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | detector level selection | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.69 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=100 (falling edge) | 2.37               | 2.48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.59 | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2.57                     | 2.68                        | 2.79               | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=101 (falling edge) | 2.47               | 2.18       2.26       V         2.08       2.16       V         2.28       2.37       V         2.18       2.27       V         2.38       2.48       V         2.38       2.69       V         2.58       2.69       V         2.78       2.9       V         2.88       3       V         2.78       2.9       V         1.00       -       mV         1.88       1.96       V         1.92       2.0       V         40       -       mV | V    |      |

| PLS[2:0]=101 (falling edge)         2.47         2.58           PLS[2:0]=110 (rising edge)         2.66         2.78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.9                      | V                           |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=110 (falling edge) | 2.56               | 2.68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.8  | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=111 (rising edge)  | 2.76               | 7     2.58     2.69     V       6     2.78     2.9     V       6     2.68     2.8     V       6     2.88     3     V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V    |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | PLS[2:0]=111 (falling edge) | 2.66               | 2.78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.9  | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PVD hysteresis           | -                           | -                  | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -    | mV   |

| M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power on/power down      | Falling edge                | 1.8 <sup>(1)</sup> | 1.88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.96 | V    |

| V <sub>POR/PDR</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | reset threshold          | Rising edge                 | 1.84               | 1.92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PDR hysteresis           | -                           | -                  | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Reset temporization      | -                           | 1                  | 2.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.5  | ms   |

#### Table 11. Embedded reset and power control block characteristics

1. The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR/PDR}}$  value.

2. Guaranteed by design, not tested in production.

|                 |                   |                                   |                   | Туј                                       | 0 <sup>(1)</sup>            |      |

|-----------------|-------------------|-----------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter         | Conditions                        | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                   |                                   | 72 MHz            | 28.2                                      | 6                           |      |

|                 |                   |                                   | 48 MHz            | 19                                        | 4.2                         |      |

|                 |                   |                                   | 36 MHz            | 14.7                                      | 3.4                         |      |

|                 |                   |                                   | 24 MHz            | 10.1                                      | 2.5                         |      |

|                 |                   |                                   | 16 MHz            | 6.7                                       | 2                           |      |

|                 |                   | External clock <sup>(3)</sup>     | 8 MHz             | 3.2                                       | 1.3                         |      |

|                 |                   |                                   | 4 MHz             | 2.3                                       | 1.2                         |      |

|                 |                   |                                   | 2 MHz             | 1.7                                       | 1.16                        | mA   |

|                 |                   |                                   | 1 MHz             | 1.5                                       | 1.1                         |      |

| I.              | Supply current in |                                   | 500 kHz           | 1.3                                       | 1.05                        |      |

| I <sub>DD</sub> | Sleep mode        |                                   | 125 kHz           | 1.2                                       | 1.05                        | ШA   |

|                 |                   |                                   | 36 MHz            | 13.7                                      | 2.6                         |      |

|                 |                   |                                   | 24 MHz            | 9.3                                       | 1.8                         |      |

|                 |                   |                                   | 16 MHz            | 6.3                                       | 1.3                         |      |

|                 |                   | Running on high speed internal RC | 8 MHz             | 2.7                                       | 0.6                         |      |

|                 |                   | (HSI), AHB prescaler              | 4 MHz             | 1.6                                       | 0.5                         |      |

|                 |                   | used to reduce the<br>frequency   | 2 MHz             | 1                                         | 0.46                        |      |

|                 |                   | 1                                 | 1 MHz             | 0.8                                       | 0.44                        |      |

|                 |                   |                                   | 500 kHz           | 0.6                                       | 0.43                        |      |

|                 |                   |                                   | 125 kHz           | 0.5                                       | 0.42                        |      |

Table 18. Typical current consumption in Sleep mode, code running from Flash or RAM

1. Typical values are measures at  $T_A = 25$  °C,  $V_{DD} = 3.3$  V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 19*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 6

## Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

|                                            |                                                        |                                  | · · · · · · · · · · · · · · · · · · · |        |                    |      |  |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|---------------------------------------|--------|--------------------|------|--|--|--|--|--|

| Symbol                                     | Parameter                                              | Conditions                       | Min                                   | Тур    | Мах                | Unit |  |  |  |  |  |

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                  |                                       | 32.768 | 1000               | kHz  |  |  |  |  |  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub>                    | -      | V <sub>DD</sub>    | V    |  |  |  |  |  |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                | V <sub>SS</sub>                       | -      | 0.3V <sub>DD</sub> | v    |  |  |  |  |  |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                                   | -      | -                  | ns   |  |  |  |  |  |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                                     | -      | 50                 | 19   |  |  |  |  |  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                | -                                     | 5      |                    | pF   |  |  |  |  |  |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                | 30                                    | -      | 70                 | %    |  |  |  |  |  |

| ١ <sub>L</sub>                             | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                                     | -      | ±1                 | μA   |  |  |  |  |  |

Table 21. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

| Symbol               | Parameter                         | Cond                   | litions                 | Min | Тур | Max | Unit |

|----------------------|-----------------------------------|------------------------|-------------------------|-----|-----|-----|------|

|                      |                                   | T <sub>A</sub> = 50 °C | -                       | 1.5 | -   |     |      |

|                      |                                   | T <sub>A</sub> = 25 °C | -                       | 2.5 | -   |     |      |

|                      |                                   | T <sub>A</sub> = 10 °C | -                       | 4   | -   |     |      |

| t <sub>SU(LSE)</sub> | t <sub>SU(LSE)</sub> Startup time |                        | T <sub>A</sub> = 0 °C   | -   | 6   | -   |      |

| (4)                  | Startup time                      | $V_{DD}$ is stabilized | T <sub>A</sub> = -10 °C | -   | 10  | -   | S    |

|                      |                                   |                        | T <sub>A</sub> = -20 °C | -   | 17  | -   |      |

|                      |                                   |                        | T <sub>A</sub> = -30 °C | -   | 32  | -   |      |

|                      |                                   |                        | T <sub>A</sub> = -40 °C | -   | 60  | -   |      |

# Table 23. LSE oscillator characteristics (f<sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> (continued)

1. Based on characterization, not tested in production.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value for example MSIV-TIN32.768kHz. Refer to crystal manufacturer for more details

- 4. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

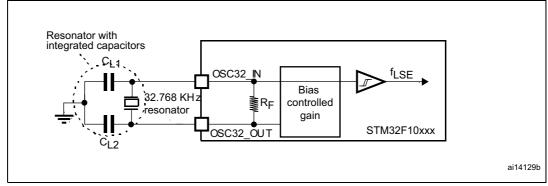

- Note: For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality external ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator (see Figure 17).  $C_{L1}$  and  $C_{L2}$ , are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

- **Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L = 6 \text{ pF}$ , and  $C_{stray} = 2 \text{ pF}$ , then  $C_{L1} = C_{L2} = 8 \text{ pF}$ .

Figure 17. Typical application with a 32.768 kHz crystal

# 5.3.7 Internal clock source characteristics

The parameters given in *Table 24* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

### High-speed internal (HSI) RC oscillator

| Parameter                           | Conditions                                                                                     |                                                                                                                                                                                                                                                       | Min                                                                                                                                                                                                                                                                                                                                                         | Тур                                                                                                                                                                                                                                            | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                | Unit                                                   |  |  |  |  |

|-------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| Frequency                           |                                                                                                | -                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                                           | 8                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MHz                                                    |  |  |  |  |