Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG      |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                    |

| Number of I/O              | 51                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 64K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                 |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f105rbt6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of figures

| Figure 1.  | STM32F105xx and STM32F107xx connectivity line block diagram                                  | . 13 |

|------------|----------------------------------------------------------------------------------------------|------|

| Figure 2.  | STM32F105xx and STM32F107xx connectivity line BGA100 ballout top view                        |      |

| Figure 3.  | STM32F105xx and STM32F107xx connectivity line LQFP100 pinout                                 |      |

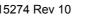

| Figure 4.  | STM32F105xx and STM32F107xx connectivity line LQFP64 pinout                                  | . 26 |

| Figure 5.  | Memory map                                                                                   | . 33 |

| Figure 6.  | Pin loading conditions                                                                       |      |

| Figure 7.  | Pin input voltage                                                                            | . 34 |

| Figure 8.  | Power supply scheme.                                                                         | . 35 |

| Figure 9.  | Current consumption measurement scheme                                                       | . 35 |

| Figure 10. | Typical current consumption on V <sub>BAT</sub> with RTC on vs. temperature at               |      |

| -          | different V <sub>BAT</sub> values                                                            | . 42 |

| Figure 11. | Typical current consumption in Stop mode with regulator in Run mode                          |      |

| -          | versus temperature at different V <sub>DD</sub> values                                       | . 42 |

| Figure 12. | Typical current consumption in Stop mode with regulator in Low-power                         |      |

| -          | mode versus temperature at different V <sub>DD</sub> values                                  | . 43 |

| Figure 13. | Typical current consumption in Standby mode versus temperature at                            |      |

| U          | different V <sub>DD</sub> values                                                             | . 43 |

| Figure 14. | High-speed external clock source AC timing diagram                                           |      |

| Figure 15. | Low-speed external clock source AC timing diagram                                            |      |

| Figure 16. | Typical application with an 8 MHz crystal                                                    |      |

| Figure 17. | Typical application with a 32.768 kHz crystal                                                |      |

| Figure 18. | Standard I/O input characteristics - CMOS port                                               |      |

| Figure 19. | Standard I/O input characteristics - TTL port                                                |      |

| Figure 20. | 5 V tolerant I/O input characteristics - CMOS port                                           |      |

| Figure 21. | 5 V tolerant I/O input characteristics - TTL port                                            |      |

| Figure 22. | I/O AC characteristics definition                                                            |      |

| Figure 23. | Recommended NRST pin protection                                                              | . 63 |

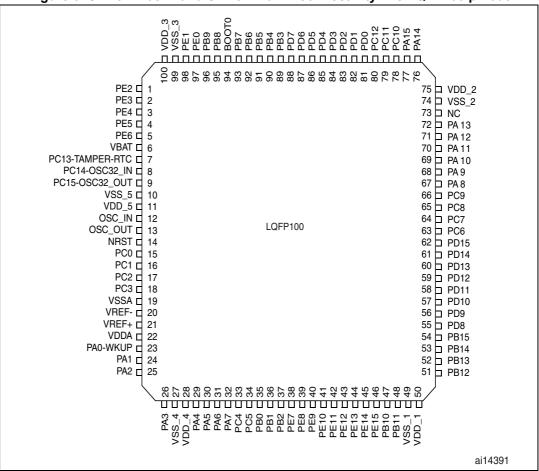

| Figure 24. | I <sup>2</sup> C bus AC waveforms and measurement circuit                                    |      |

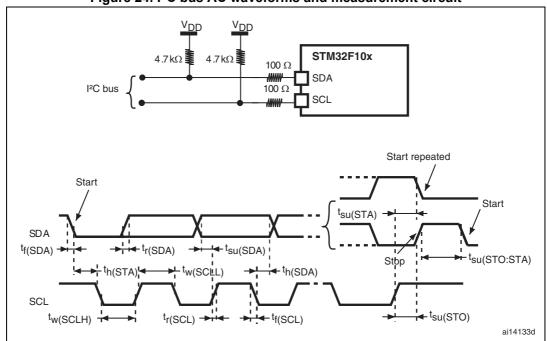

| Figure 25. | SPI timing diagram - slave mode and CPHA = 0                                                 | . 67 |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                  | . 67 |

| Figure 27. | SPI timing diagram - master mode <sup>(1)</sup>                                              |      |

| Figure 28. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>                      | . 70 |

| Figure 29. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>                     | . 70 |

| Figure 30. | USB OTG FS timings: definition of data signal rise and fall time                             |      |

| Figure 31. | Ethernet SMI timing diagram                                                                  |      |

| Figure 32. | Ethernet RMII timing diagram                                                                 |      |

| Figure 33. | Ethernet MII timing diagram                                                                  |      |

| Figure 34. | ADC accuracy characteristics                                                                 |      |

| Figure 35. | Typical connection diagram using the ADC                                                     |      |

| Figure 36. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |      |

| Figure 37. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> ).    | . 78 |

| Figure 38. | 12-bit buffered /non-buffered DAC                                                            |      |

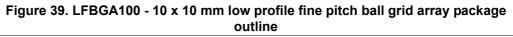

| Figure 39. | LFBGA100 - 10 x 10 mm low profile fine pitch ball grid array package                         |      |

| 0          | outline                                                                                      | . 82 |

| Figure 40. | LFBGA100 – 100-ball low profile fine pitch ball grid array, 10 x 10 mm,                      |      |

| 0          | 0.8 mm pitch, package mechanical data                                                        | . 83 |

| Figure 41. | LFBGA100 – 100-ball low profile fine pitch ball grid array, 10 x 10 mm,                      | -    |

| 0          | 0.8 mm pitch, package recommended footprint                                                  | . 83 |

|            |                                                                                              | -    |

Any of the standard timers can be used to generate PWM outputs. Each of the timers has independent DMA request generations.

#### Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

### 2.3.16 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support 7/10-bit addressing mode and 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

### 2.3.17 Universal synchronous/asynchronous receiver transmitters (USARTs)

The STM32F105xx and STM32F107xx connectivity line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4 and UART5).

These five interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART1 interface is able to communicate at speeds of up to 4.5 Mbit/s. The other available interfaces communicate at up to 2.25 Mbit/s.

DocID15274 Rev 10

USART1, USART2 and USART3 also provide hardware management of the CTS and RTS signals, Smart Card mode (ISO 7816 compliant) and SPI-like communication capability. All interfaces can be served by the DMA controller except for UART5.

#### 2.3.18 Serial peripheral interface (SPI)

Up to three SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and simplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC/SDHC<sup>(a)</sup> modes.

All SPIs can be served by the DMA controller.

#### Inter-integrated sound (I<sup>2</sup>S) 2.3.19

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI2 and SPI3) are available, that can be operated in master or slave mode. These interfaces can be configured to operate with 16/32 bit resolution, as input or output channels. Audio sampling frequencies from 8 kHz up to 96 kHz are supported. When either or both of the I<sup>2</sup>S interfaces is/are configured in master mode, the master clock can be output to the external DAC/CODEC at 256 times the sampling frequency with less than 0.5% accuracy error owing to the advanced clock controller (see Section 2.3.7: Clocks and startup).

Refer to the "Audio frequency precision" tables provided in the "Serial peripheral interface (SPI)" section of the STM32F10xxx reference manual.

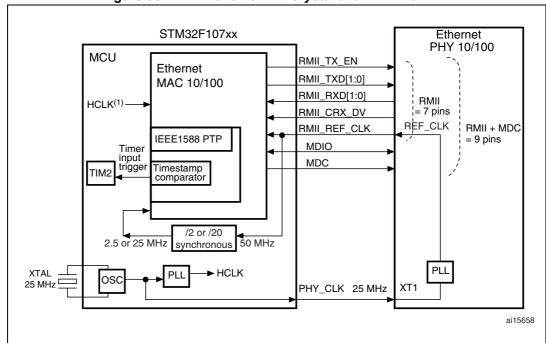

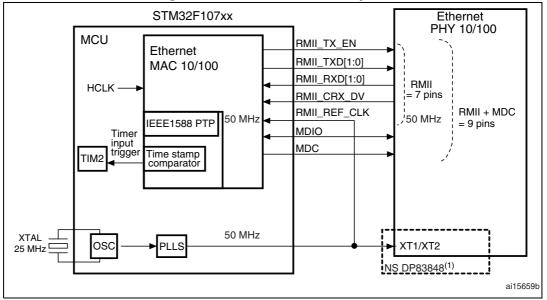

#### 2.3.20 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

Peripheral not available on STM32F105xx devices.

The STM32F107xx devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard media-independent interface (MII) or a reduced media-independent interface (RMII). The STM32F107xx requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). the PHY is connected to the STM32F107xx MII port using as many as 17 signals (MII) or 9 signals (RMII) and can be clocked using the 25 MHz (MII) or 50 MHz (RMII) output from the STM32F107xx.

The STM32F107xx includes the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors (see the STM32F105xx/STM32F107xx reference manual for details)

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

a. SDHC = Secure digital high capacity.

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes, that is 4 Kbytes in total

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 with the timestamp comparator connected to the TIM2 trigger input

- Triggers interrupt when system time becomes greater than target time

#### 2.3.21 Controller area network (CAN)

The two CANs are compliant with the 2.0A and B (active) specifications with a bitrate up to 1 Mbit/s. They can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. Each CAN has three transmit mailboxes, two receive FIFOS with 3 stages and 28 shared scalable filter banks (all of them can be used even if one CAN is used). The 256 bytes of SRAM which are allocated for each CAN (512 bytes in total) are not shared with any other peripheral.

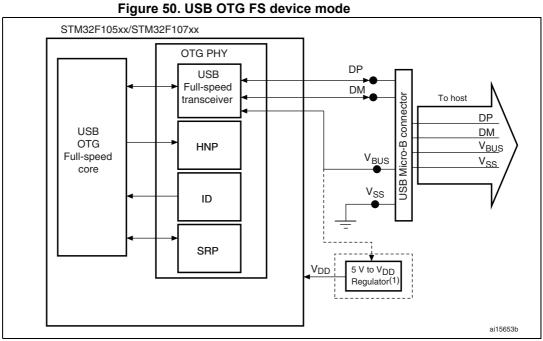

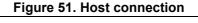

#### 2.3.22 Universal serial bus on-the-go full-speed (USB OTG FS)

The STM32F105xx and STM32F107xx connectivity line devices embed a USB OTG fullspeed (12 Mb/s) device/host/OTG peripheral with integrated transceivers. The USB OTG FS peripheral is compliant with the USB 2.0 specification and with the OTG 1.0 specification. It has software-configurable endpoint setting and supports suspend/resume. The USB OTG full-speed controller requires a dedicated 48 MHz clock that is generated by a PLL connected to the HSE oscillator. The major features are:

- 1.25 KB of SRAM used exclusively by the endpoints (not shared with any other peripheral)

- 4 bidirectional endpoints

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

- the SOF output can be used to synchronize the external audio DAC clock in isochronous mode

- in accordance with the USB 2.0 Specification, the supported transfer speeds are:

- in Host mode: full speed and low speed

- in Device mode: full speed

### 2.3.23 GPIOs (general-purpose inputs/outputs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. All GPIOs are high current-capable.

The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

I/Os on APB2 with up to 18 MHz toggling speed

DocID15274 Rev 10

# 3 Pinouts and pin description

| r |                    | 2                       | 3   | 4                 | 5                 | 6                 | 7                 | 8 <b>GA100 b</b><br>8 | 9    | 10       |

|---|--------------------|-------------------------|-----|-------------------|-------------------|-------------------|-------------------|-----------------------|------|----------|

| А | PC14-<br>OSC32_IN  | PC13-<br>TAMPER-<br>RTC | PE2 | PB9               | РВ7               | PB4               | РВЗ               | PA15                  | PA14 | PA13     |

| в | PC15-<br>bSC32_OUT | V <sub>BAT</sub>        | PE3 | PB8               | PB6               | PD5               | PD2               | PC11                  | PC10 | PA12     |

| с | OSC_IN             | V <sub>SS_5</sub>       | PE4 | PE1               | PB5               | PD6               | PD3               | PC12                  | PA9  | PA11     |

| D | OSC_OUT            | V <sub>DD_5</sub>       | PE5 | PEO               | BOOTO             | PD7               | PD4               | PD0                   | PA8  | PA10     |

| E | NRST               | PC2                     | PE6 | V <sub>SS_4</sub> | V <sub>SS_3</sub> | V <sub>SS_2</sub> | V <sub>SS_1</sub> | PD1                   | PC9  | PC7      |

| F | PC0                | PC1                     | PC3 | V <sub>DD_4</sub> | V <sub>DD_3</sub> | V <sub>DD_2</sub> | V <sub>DD_1</sub> | NC                    | PC8  | PC6      |

| G | V <sub>SSA</sub>   | PA0-WKUP                | PA4 | PC4               | PB2               | PE10              | PE14              | PB15                  | PD11 | PD15     |

| н | V <sub>REF-</sub>  | PA1                     | PA5 | PC5               | PE7               | PE11              | PE15              | PB14                  | PD10 | PD14     |

| L | V <sub>REF+</sub>  | PA2                     | PA6 | PB0               | PE8               | PE12              | PB10              | PB13                  | PD9  | PD13     |

| к | V <sub>DDA</sub>   | РАЗ                     | PA7 | PB1               | PE9               | PE13              | PB11              | PB12                  | PD8  | PD12     |

|   |                    |                         |     |                   |                   |                   |                   |                       |      | Al14601c |

Figure 2. STM32F105xx and STM32F107xx connectivity line BGA100 ballout top view

| Table 5. P | in definitions | (continued) |

|------------|----------------|-------------|

|------------|----------------|-------------|

|        | Pins   |         |                   |                     |                            |                                                  | Alternate func                                                               | tions <sup>(4)</sup>                         |

|--------|--------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------|

| BGA100 | LQFP64 | LQFP100 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                      | Remap                                        |

| J9     | -      | 56      | PD9               | I/O                 | FT                         | PD9                                              | -                                                                            | USART3_RX/<br>ETH_MII_RXD0/<br>ETH_RMII_RXD0 |

| H9     | -      | 57      | PD10              | I/O                 | FT                         | PD10                                             | -                                                                            | USART3_CK/<br>ETH_MII_RXD1/<br>ETH_RMII_RXD1 |

| G9     | -      | 58      | PD11              | I/O                 | FT                         | PD11                                             | -                                                                            | USART3_CTS/<br>ETH_MII_RXD2                  |

| K10    | -      | 59      | PD12              | I/O                 | FT                         | PD12                                             | -                                                                            | TIM4_CH1 /<br>USART3_RTS/<br>ETH_MII_RXD3    |

| J10    | -      | 60      | PD13              | I/O                 | FT                         | PD13                                             | -                                                                            | TIM4_CH2                                     |

| H10    | -      | 61      | PD14              | I/O                 | FT                         | PD14 -                                           |                                                                              | TIM4_CH3                                     |

| G10    | -      | 62      | PD15              | I/O                 | FT                         | PD15 -                                           |                                                                              | TIM4_CH4                                     |

| F10    | 37     | 63      | PC6               | I/O                 | FT                         | PC6                                              | I2S2_MCK/                                                                    | TIM3_CH1                                     |

| E10    | 38     | 64      | PC7               | I/O                 | FT                         | PC7                                              | I2S3_MCK                                                                     | TIM3_CH2                                     |

| F9     | 39     | 65      | PC8               | I/O                 | FT                         | PC8                                              | -                                                                            | TIM3_CH3                                     |

| E9     | 40     | 66      | PC9               | I/O                 | FT                         | PC9                                              | -                                                                            | TIM3_CH4                                     |

| D9     | 41     | 67      | PA8               | I/O                 | FT                         | PA8                                              | USART1_CK/OTG_FS_SOF /<br>TIM1_CH1 <sup>(8)</sup> /MCO                       | -                                            |

| C9     | 42     | 68      | PA9               | I/O                 | FT                         | PA9                                              | USART1_TX <sup>(7)</sup> / TIM1_CH2 <sup>(7)</sup> /<br>OTG_FS_VBUS          | -                                            |

| D10    | 43     | 69      | PA10              | I/O                 | FT                         | PA10                                             | USART1_RX <sup>(7)</sup> /<br>TIM1_CH3 <sup>(7)</sup> /OTG_FS_ID             | -                                            |

| C10    | 44     | 70      | PA11              | I/O                 | FT                         | PA11                                             | USART1_CTS / CAN1_RX /<br>TIM1_CH4 <sup>(7)</sup> /OTG_FS_DM                 | -                                            |

| B10    | 45     | 71      | PA12              | I/O                 | FT                         | PA12                                             | USART1_RTS / OTG_FS_DP /<br>CAN1_TX <sup>(7)</sup> / TIM1_ETR <sup>(7)</sup> | -                                            |

| A10    | 46     | 72      | PA13              | I/O                 | FT                         | JTMS-SWDIO                                       | -                                                                            | PA13                                         |

| F8     | -      | 73      |                   |                     | -                          | Not connect                                      | ed                                                                           | -                                            |

| E6     | 47     | 74      | V <sub>SS_2</sub> | S                   | -                          | V <sub>SS_2</sub>                                | -                                                                            | -                                            |

| F6     | 48     | 75      | V <sub>DD_2</sub> | S                   | -                          | V <sub>DD_2</sub>                                | -                                                                            | -                                            |

| A9     | 49     | 76      | PA14              | I/O                 | FT                         | JTCK-SWCLK                                       | -                                                                            | PA14                                         |

### 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 6: Voltage characteristics*, *Table 7: Current characteristics*, and *Table 8: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                               | Min                  | Мах                  | Unit |

|-----------------------------------|-----------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{(1)}$ | -0.3                 | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on five volt tolerant pin                               | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 | V    |

| VIN V                             | Input voltage on any other pin                                        | V <sub>SS</sub> -0.3 | 4.0                  |      |

| ΔV <sub>DDx</sub>                 | Variations between different V <sub>DD</sub> power pins               | -                    | 50                   | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                      | -                    | 50                   | IIIV |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body see Section 5.3.11:       |                      | -                    |      |

| Table 6. Volt | age characteristics |

|---------------|---------------------|

|---------------|---------------------|

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 7: Current characteristics* for the maximum allowed injected current values.

| Symbol                               | Ratings                                                                 | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|

| I <sub>VDD</sub>                     | Total current into $V_{DD}/V_{DDA}$ power lines (source) <sup>(1)</sup> | 150   |      |

| I <sub>VSS</sub>                     | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>        | 150   |      |

|                                      | Output current sunk by any I/O and control pin                          | 25    |      |

| I <sub>IO</sub>                      | Output current source by any I/Os and control pin                       | -25   | mA   |

| ı (2)                                | Injected current on five volt tolerant pins <sup>(3)</sup>              | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ± 5   |      |

| $\Sigma I_{INJ(PIN)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ± 25  |      |

#### Table 7. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See *Note: on page 76*.

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 6: Voltage characteristics* for the maximum allowed input voltage values.

A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 6: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| Тj               | Maximum junction temperature | 150         | °C   |

#### Table 8. Thermal characteristics

### 5.3 Operating conditions

### 5.3.1 General operating conditions

| Symbol                          | Parameter                                                        | Conditions                           | Min | Мах | Unit |

|---------------------------------|------------------------------------------------------------------|--------------------------------------|-----|-----|------|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                     | -                                    | 0   | 72  |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                    | -                                    | 0   | 36  | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                    | -                                    | 0   | 72  |      |

| V <sub>DD</sub>                 | Standard operating voltage                                       | -                                    | 2   | 3.6 | V    |

| V (1)                           | Analog operating voltage<br>(ADC not used)                       | Must be the same potential           | 2   | 3.6 | V    |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC used)                           | as V <sub>DD</sub> <sup>(2)</sup>    | 2.4 | 3.6 | v    |

| V <sub>BAT</sub>                | Backup operating voltage                                         | -                                    | 1.8 | 3.6 | V    |

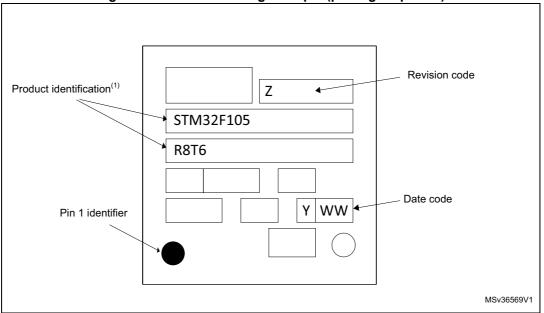

|                                 | Power dissipation at $T_A =$<br>85 °C for suffix 6 or $T_A =$    | LFBGA100                             | -   | 500 | mW   |

| $P_D$                           |                                                                  | LQFP100                              | -   | 434 |      |

|                                 | 105 °C for suffix $7^{(3)}$                                      | LQFP64                               | -   | 444 |      |

| _                               | Power dissipation at T <sub>A</sub> =                            | LQFP100                              | -   | 434 |      |

| PD                              | 85 °C for suffix 6 or $T_A =$ 105 °C for suffix 7 <sup>(4)</sup> | LQFP64                               | -   | 444 | mW   |

|                                 | Ambient temperature for 6                                        | Maximum power dissipation            | -40 | 85  | °C   |

| Та                              | suffix version                                                   | Low power dissipation <sup>(5)</sup> | -40 | 105 |      |

| IA                              | Ambient temperature for 7                                        | Maximum power dissipation            | -40 | 105 | °C   |

|                                 | suffix version                                                   | Low power dissipation <sup>(5)</sup> | -40 | 125 |      |

| TJ                              | lunction tomporature reaso                                       | 6 suffix version                     | -40 | 105 | °C   |

| IJ                              | Junction temperature range                                       | 7 suffix version                     | -40 | 125 |      |

### Table 9. General operating conditions

1. When the ADC is used, refer to *Table 52: ADC characteristics*.

2. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

3. If  $T_A$  is lower, higher  $\mathsf{P}_D$  values are allowed as long as  $\mathsf{T}_J$  does not exceed  $\mathsf{T}_J\mathsf{max}.$

4. If  $T_A$  is lower, higher  $\mathsf{P}_D$  values are allowed as long as  $\mathsf{T}_J$  does not exceed  $\mathsf{T}_J\mathsf{max}.$

5. In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_J$ max.

Figure 24. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

| £ (//U_)               | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801E                  |

| 300                    | 0x8028                  |

| 200                    | 0x803C                  |

| 100                    | 0x00B4                  |

| 50                     | 0x0168                  |

| 20                     | 0x0384                  |

### Table 42. SCL frequency $(f_{PCLK1} = 36 \text{ MHz.}, V_{DD} = 3.3 \text{ V})^{(1)(2)}$

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

### I<sup>2</sup>S - SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 43* for SPI or in *Table 44* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Refer to Section 5.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                           | Conditions                                            | Min                 | Мах                 | Unit  |  |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------|---------------------|---------------------|-------|--|

| f <sub>SCK</sub>                             |                                     | Master mode                                           | -                   | 18                  | 8 MHz |  |

| 1/t <sub>c(SCK)</sub>                        | SPI clock frequency                 | Slave mode                                            | -                   | 18                  |       |  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            | -                   | 8                   | ns    |  |

| DuCy(SCK)                                    | SPI slave input clock<br>duty cycle | Slave mode                                            | 30                  | 70                  | %     |  |

| t <sub>su(NSS)</sub>                         | NSS setup time                      | Slave mode                                            | 4 t <sub>PCLK</sub> | -                   |       |  |

| t <sub>h(NSS)</sub>                          | NSS hold time                       | Slave mode                                            | 2 t <sub>PCLK</sub> | -                   |       |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | 50                  | 60                  |       |  |

| t <sub>su(MI)</sub>                          | Data input setup time               | Master mode                                           | 4                   | -                   |       |  |

| t <sub>su(SI)</sub>                          | Data input setup time               | Slave mode                                            | 5                   | -                   |       |  |

| t <sub>h(MI)</sub>                           | Data input hold time                | Master mode                                           | 5                   | -                   | no    |  |

| t <sub>h(SI)</sub>                           | Data input noid time                | Slave mode                                            | 5                   | -                   | ns    |  |

| t <sub>a(SO)</sub>                           | Data output access time             | Slave mode, f <sub>PCLK</sub> = 20 MHz                | -                   | 3*t <sub>PCLK</sub> |       |  |

| t <sub>v(SO)</sub>                           | Data output valid time              | Slave mode (after enable edge)                        | -                   | 34                  |       |  |

| t <sub>v(MO)</sub>                           | Data output valid time              | Master mode (after enable edge)                       | -                   | 8                   |       |  |

| t <sub>h(SO)</sub>                           | Data output hold time               | Slave mode (after enable edge)                        | 32                  | -                   |       |  |

| t <sub>h(MO)</sub>                           | Data output hold time               | Master mode (after enable edge)                       | 10                  | -                   |       |  |

Table 43. SPI characteristics

Figure 27. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

## 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

## 6.1 LFBGA100 package information

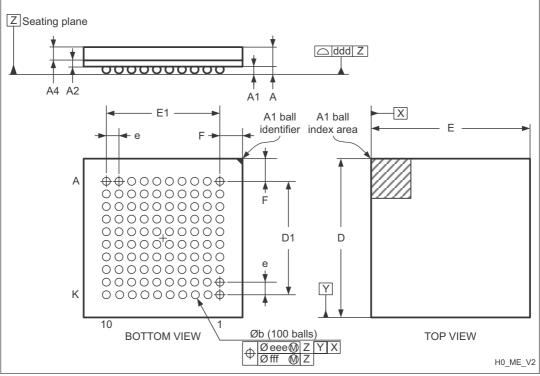

#### **Device marking for LQFP64**

The following figure shows the device marking for the LQFP64 package.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

#### Figure 48.LQFP64 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## 6.4 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 9: General operating conditions on page 37*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max \times \Theta_{JA})$$

Where:

- $T_A$  max is the maximum ambient temperature in  $^{\circ}C$ ,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{\mathsf{I}\!/\!\mathsf{O}}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol          | Parameter                                                                   | Value | Unit |  |  |  |

|-----------------|-----------------------------------------------------------------------------|-------|------|--|--|--|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch  | 46    | °C/W |  |  |  |

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch   | 45    | 0/00 |  |  |  |

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LFBGA100 - 10 × 10 mm / 0.8 mm pitch | 40    |      |  |  |  |

|                 | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm / 0.5 mm pitch  | 46    | °C/W |  |  |  |

|                 | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch   | 45    |      |  |  |  |

| Table 61. Package therm | nal characteristics |

|-------------------------|---------------------|

|-------------------------|---------------------|

### 6.4.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org.

Using the values obtained in Table 61  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 46 °C/W

- $T_{Jmax}$  = 115 °C + (46 °C/W × 134 mW) = 115 °C + 6.2 °C = 121.2 °C

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 62: Ordering information scheme*).

# Appendix A Application block diagrams

## A.1 USB OTG FS interface solutions

1. Use a regulator if you want to build a bus-powered device.

1. STMPS2141STR needed only if the application has to support bus-powered devices.

Figure 55. RMII with a 25 MHz crystal and PHY with PLL

1. HCLK must be greater than 25 MHz.

#### Figure 56. RMII with a 25 MHz crystal

1. The NS DP83848 is recommended as the input jitter requirement of this PHY. It is compliant with the output jitter specification of the MCU.

| Application                                                        | Crystal<br>value in<br>MHz<br>(XT1) | PREDIV2 | PLL2MUL       | PLLSRC | PREDIV1 | PLLMUL        | USB<br>prescaler<br>(PLLVCO<br>output) | PLL3MUL       | l2Sn<br>clock<br>input | MCO (main<br>clock<br>output)                |

|--------------------------------------------------------------------|-------------------------------------|---------|---------------|--------|---------|---------------|----------------------------------------|---------------|------------------------|----------------------------------------------|

| Ethernet only                                                      | 25                                  | /5      | PLL2ON<br>x8  | PLL2   | /5      | PLLON x9      | NA                                     | PLL3ON<br>x10 | NA                     | XT1 (MII)<br>PLL3 (RMII)                     |

| Ethernet + OTG                                                     | 25                                  | /5      | PLL2ON<br>x8  | PLL2   | /5      | PLLON x9      | /3                                     | PLL3ON<br>x10 | NA                     | XT1 (MII)<br>PLL3 (RMII)                     |

| Ethernet + OTG<br>+ basic audio                                    | 25                                  | /5      | PLL2ON<br>x8  | PLL2   | /5      | PLLON x9      | /3                                     | PLL3ON<br>x10 | PLL                    | XT1 (MII)<br>PLL3 (RMII)                     |

| Ethernet + OTG<br>+ Audio class<br>I <sup>2</sup> S <sup>(1)</sup> | 14.7456                             | /4      | PLL2ON<br>x12 | PLL2   | /4      | PLLON<br>x6.5 | /3                                     | PLL3ON<br>x20 | PLL3<br>VCO<br>Out     | NA<br>ETH PHY<br>must use its<br>own crystal |

| OTG only                                                           | 8                                   | NA      | PLL2OFF       | XT1    | /1      | PLLON x9      | /3                                     | PLL3OFF       | NA                     | NA                                           |

| OTG + basic<br>audio                                               | 8                                   | NA      | PLL2OFF       | XT1    | /1      | PLLON x9      | /3                                     | PLL3OFF       | PLL                    | NA                                           |

| OTG + Audio<br>class I <sup>2</sup> S <sup>(1)</sup>               | 14.7456                             | /4      | PLL2ON<br>x12 | PLL2   | /4      | PLLON<br>x6.5 | /3                                     | PLL3ON<br>x20 | PLL3<br>VCO<br>Out     | NA                                           |

| Audio class I <sup>2</sup> S<br>only <sup>(1)</sup>                | 14.7456                             | /4      | PLL2ON<br>x12 | PLL2   | /4      | PLLON<br>x6.5 | NA                                     | PLL3ON<br>x20 | PLL3<br>VCO<br>out     | NA                                           |

Table 63. PLL configurations

1. SYSCLK is set to be at 72 MHz except in this case where SYSCLK is at 71.88 MHz.

*Table 64* give the I<sub>DD</sub> run mode values that correspond to the conditions specified in *Table 63*.

#### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved

DocID15274 Rev 10