Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM® Cortex®-M3Core Size32-Bit Single-CoreSpeed72MHzConnectivityCANbus, I²C, IrDA, LINbus, SPI, UART/USART, USB OTGPeripheralsDMA, POR, PWM, Voltage Detect, WDTNumber of I/O51Program Memory Size256KB (256K x 8) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed72MHzConnectivityCANbus, I²C, IrDA, LINbus, SPI, UART/USART, USB OTGPeripheralsDMA, POR, PWM, Voltage Detect, WDTNumber of I/O51                                                                                     |

| Speed     72MHz       Connectivity     CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG       Peripherals     DMA, POR, PWM, Voltage Detect, WDT       Number of I/O     51                                                          |

| ConnectivityCANbus, I²C, IrDA, LINbus, SPI, UART/USART, USB OTGPeripheralsDMA, POR, PWM, Voltage Detect, WDTNumber of I/O51                                                                                                                          |

| Peripherals     DMA, POR, PWM, Voltage Detect, WDT       Number of I/O     51                                                                                                                                                                        |

| Number of I/O 51                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                      |

| Program Memory Size 256KB (256K x 8)                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                      |

| Program Memory Type FLASH                                                                                                                                                                                                                            |

| EEPROM Size -                                                                                                                                                                                                                                        |

| RAM Size 64K x 8                                                                                                                                                                                                                                     |

| Voltage - Supply (Vcc/Vdd) 2V ~ 3.6V                                                                                                                                                                                                                 |

| Data ConvertersA/D 16x12b; D/A 2x12b                                                                                                                                                                                                                 |

| Oscillator Type Internal                                                                                                                                                                                                                             |

| Operating Temperature -40°C ~ 85°C (TA)                                                                                                                                                                                                              |

| Mounting Type Surface Mount                                                                                                                                                                                                                          |

| Package / Case 64-LQFP                                                                                                                                                                                                                               |

| Supplier Device Package64-LQFP (10x10)                                                                                                                                                                                                               |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f105rct6w                                                                                                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 2.3.29               | Embedded Trace Macrocell™23                            |

|---|--------|----------------------|--------------------------------------------------------|

| 3 | Pinou  | its and <sub>l</sub> | pin description                                        |

| 4 | Memo   | ory map              | ping                                                   |

| 5 | Electr | rical cha            | aracteristics                                          |

|   | 5.1    | Parame               | ter conditions                                         |

|   |        | 5.1.1                | Minimum and maximum values                             |

|   |        | 5.1.2                | Typical values                                         |

|   |        | 5.1.3                | Typical curves                                         |

|   |        | 5.1.4                | Loading capacitor                                      |

|   |        | 5.1.5                | Pin input voltage                                      |

|   |        | 5.1.6                | Power supply scheme                                    |

|   |        | 5.1.7                | Current consumption measurement                        |

|   | 5.2    | Absolute             | e maximum ratings                                      |

|   | 5.3    | Operatir             | ng conditions                                          |

|   |        | 5.3.1                | General operating conditions                           |

|   |        | 5.3.2                | Operating conditions at power-up / power-down          |

|   |        | 5.3.3                | Embedded reset and power control block characteristics |

|   |        | 5.3.4                | Embedded reference voltage                             |

|   |        | 5.3.5                | Supply current characteristics                         |

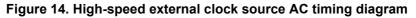

|   |        | 5.3.6                | External clock source characteristics                  |

|   |        | 5.3.7                | Internal clock source characteristics                  |

|   |        | 5.3.8                | PLL, PLL2 and PLL3 characteristics                     |

|   |        | 5.3.9                | Memory characteristics                                 |

|   |        | 5.3.10               | EMC characteristics                                    |

|   |        | 5.3.11               | Absolute maximum ratings (electrical sensitivity)      |

|   |        | 5.3.12               | I/O current injection characteristics                  |

|   |        | 5.3.13               | I/O port characteristics                               |

|   |        | 5.3.14               | NRST pin characteristics                               |

|   |        | 5.3.15               | TIM timer characteristics                              |

|   |        | 5.3.16               | Communications interfaces                              |

|   |        | 5.3.17               | 12-bit ADC characteristics                             |

|   |        | 5.3.18               | DAC electrical specifications                          |

|   |        | 5.3.19               | Temperature sensor characteristics                     |

| 6       | Packa  | age inf | ormation                                                        | 82   |

|---------|--------|---------|-----------------------------------------------------------------|------|

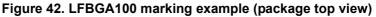

|         | 6.1    | LFBGA   | A100 package information                                        | 82   |

|         | 6.2    | LQFP    | 100 package information                                         | 85   |

|         | 6.3    | LQFP    | 64 package information                                          | 88   |

|         | 6.4    | Therm   | al characteristics                                              | 91   |

|         |        | 6.4.1   | Reference document                                              | . 91 |

|         |        | 6.4.2   | Selecting the product temperature range                         | . 92 |

| 7       | Part r | numbe   | ring                                                            | 94   |

| Appendi | x A A  | pplicat | ion block diagrams                                              | 95   |

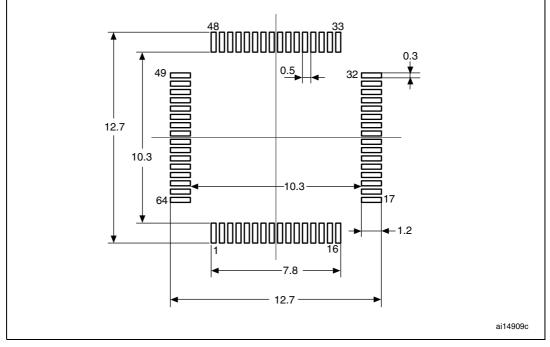

|         | A.1    | USB C   | DTG FS interface solutions                                      | 95   |

|         | A.2    | Ethern  | et interface solutions                                          | 97   |

|         | A.3    | Compl   | ete audio player solutions                                      | 99   |

|         | A.4    | USB C   | TG FS interface + Ethernet/I <sup>2</sup> S interface solutions | 100  |

| 8       | Revis  | ion his | story                                                           | 103  |

## 1 Introduction

This datasheet provides the description of the STM32F105xx and STM32F107xx connectivity line microcontrollers. For more details on the whole STMicroelectronics STM32F10xxx family, refer to *Section 2.2: Full compatibility throughout the family*.

The STM32F105xx and STM32F107xx datasheet should be read in conjunction with the STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory refer to the STM32F10xxx Flash programming manual.

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the www.arm.com website.

| Periph        | herals <sup>(1)</sup>                | STM32F105Rx                                                                                  | STM32F107Rx    | STM32F105Vx | STM32F107Vx |  |  |  |

|---------------|--------------------------------------|----------------------------------------------------------------------------------------------|----------------|-------------|-------------|--|--|--|

|               | SPI(I <sup>2</sup> S) <sup>(2)</sup> | 3(2)                                                                                         | 3(2) 3(2) 3(2) |             |             |  |  |  |

| Communicat    | l <sup>2</sup> C                     | 2                                                                                            | 1              | 2           | 1           |  |  |  |

| ion           | USART                                |                                                                                              | 5              |             |             |  |  |  |

| interfaces    | USB OTG FS                           |                                                                                              |                | Yes         |             |  |  |  |

|               | CAN                                  |                                                                                              |                |             |             |  |  |  |

| GPIOs         |                                      | 51                                                                                           |                | 80          |             |  |  |  |

| 12-bit ADC    |                                      | 2                                                                                            |                |             |             |  |  |  |

| Number of ch  | annels                               | 16                                                                                           |                |             |             |  |  |  |

| 12-bit DAC    |                                      | 2                                                                                            |                |             |             |  |  |  |

| Number of ch  | annels                               | 2                                                                                            |                |             |             |  |  |  |

| CPU frequence | су                                   | 72 MHz                                                                                       |                |             |             |  |  |  |

| Operating vol | tage                                 | 2.0 to 3.6 V                                                                                 |                |             |             |  |  |  |

| Operating ten | nperatures                           | Ambient temperatures: -40 to +85 °C /-40 to +105 °C<br>Junction temperature: -40 to + 125 °C |                |             |             |  |  |  |

#### Table 2. STM32F105xx and STM32F107xx features and peripheral counts (continued)

1. Refer to *Table 5: Pin definitions* for peripheral availability when the I/O pins are shared by the peripherals required by the application.

2. The SPI2 and SPI3 interfaces give the flexibility to work in either the SPI mode or the  $I^2S$  audio mode.

Any of the standard timers can be used to generate PWM outputs. Each of the timers has independent DMA request generations.

#### **Basic timers TIM6 and TIM7**

These timers are mainly used for DAC trigger generation. They can also be used as a generic 16-bit time base.

#### Independent watchdog

The independent watchdog is based on a 12-bit downcounter and 8-bit prescaler. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### Window watchdog

The window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- A 24-bit down counter

- Autoreload capability

- Maskable system interrupt generation when the counter reaches 0.

- Programmable clock source

## 2.3.16 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support 7/10-bit addressing mode and 7-bit dual addressing mode (as slave). A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SMBus 2.0/PMBus.

## 2.3.17 Universal synchronous/asynchronous receiver transmitters (USARTs)

The STM32F105xx and STM32F107xx connectivity line embeds three universal synchronous/asynchronous receiver transmitters (USART1, USART2 and USART3) and two universal asynchronous receiver transmitters (UART4 and UART5).

These five interfaces provide asynchronous communication, IrDA SIR ENDEC support, multiprocessor communication mode, single-wire half-duplex communication mode and have LIN Master/Slave capability.

The USART1 interface is able to communicate at speeds of up to 4.5 Mbit/s. The other available interfaces communicate at up to 2.25 Mbit/s.

DocID15274 Rev 10

| Table 5. I | Pin definitions | (continued) |

|------------|-----------------|-------------|

|------------|-----------------|-------------|

|        | Pins   |         |                   |                     |                            |                                                  | Alternate func                                                           | tions <sup>(4)</sup>                   |

|--------|--------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------|

| BGA100 | LQFP64 | LQFP100 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                  | Remap                                  |

| A8     | 50     | 77      | PA15              | I/O                 | FT                         | JTDI                                             | SPI3_NSS / I2S3_WS                                                       | TIM2_CH1_ETR / PA15<br>SPI1_NSS        |

| В9     | 51     | 78      | PC10              | I/O                 | FT                         | PC10                                             | UART4_TX                                                                 | USART3_TX/<br>SPI3_SCK/I2S3_CK         |

| B8     | 52     | 79      | PC11              | I/O                 | FT                         | PC11                                             | UART4_RX                                                                 | USART3_RX/<br>SPI3_MISO                |

| C8     | 53     | 80      | PC12              | I/O                 | FT                         | PC12                                             | UART5_TX                                                                 | USART3_CK/<br>SPI3_MOSI/I2S3_SD        |

| D8     | -      | 81      | PD0               | I/O                 | FT                         | PD0                                              | -                                                                        | OSC_IN <sup>(9)</sup> /CAN1_RX         |

| E8     | -      | 82      | PD1               | I/O                 | FT                         | PD1                                              | -                                                                        | OSC_OUT <sup>(9)</sup> /CAN1_TX        |

| B7     | 54     | 83      | PD2               | I/O                 | FT                         | PD2                                              | TIM3_ETR / UART5_RX                                                      |                                        |

| C7     | -      | 84      | PD3               | I/O                 | FT                         | PD3                                              | -                                                                        | USART2_CTS                             |

| D7     | -      | 85      | PD4               | I/O                 | FT                         | PD4                                              | -                                                                        | USART2_RTS                             |

| B6     | -      | 86      | PD5               | I/O                 | FT                         | PD5                                              | -                                                                        | USART2_TX                              |

| C6     | -      | 87      | PD6               | I/O                 | FT                         | PD6                                              | -                                                                        | USART2_RX                              |

| D6     | -      | 88      | PD7               | I/O                 | FT                         | PD7                                              | -                                                                        | USART2_CK                              |

| A7     | 55     | 89      | PB3               | I/O                 | FT                         | JTDO                                             | SPI3_SCK / I2S3_CK                                                       | PB3 / TRACESWO/<br>TIM2_CH2 / SPI1_SCK |

| A6     | 56     | 90      | PB4               | I/O                 | FT                         | NJTRST                                           | SPI3_MISO                                                                | PB4 / TIM3_CH1/<br>SPI1_MISO           |

| C5     | 57     | 91      | PB5               | I/O                 | -                          | PB5                                              | I2C1_SMBA / SPI3_MOSI /<br>ETH_MII_PPS_OUT / I2S3_SD<br>ETH_RMII_PPS_OUT | TIM3_CH2/SPI1_MOSI/<br>CAN2_RX         |

| B5     | 58     | 92      | PB6               | I/O                 | FT                         | PB6                                              | I2C1_SCL <sup>(7)</sup> /TIM4_CH1 <sup>(7)</sup>                         | USART1_TX/CAN2_TX                      |

| A5     | 59     | 93      | PB7               | I/O                 | FT                         | PB7                                              | I2C1_SDA <sup>(7)</sup> /TIM4_CH2 <sup>(7)</sup>                         | USART1_RX                              |

| D5     | 60     | 94      | BOOT0             | Ι                   | -                          | BOOT0                                            | -                                                                        | -                                      |

| B4     | 61     | 95      | PB8               | I/O                 | FT                         | PB8                                              | TIM4_CH3 <sup>(7)</sup> / ETH_MII_TXD3                                   | I2C1_SCL/CAN1_RX                       |

| A4     | 62     | 96      | PB9               | I/O                 | FT                         | PB9                                              | TIM4_CH4 <sup>(7)</sup>                                                  | I2C1_SDA / CAN1_TX                     |

| D4     | -      | 97      | PE0               | I/O                 | FT                         | PE0                                              | TIM4_ETR                                                                 | -                                      |

| C4     | -      | 98      | PE1               | I/O                 | FT                         | PE1                                              | -                                                                        | -                                      |

| E5     | 63     | 99      | V <sub>SS_3</sub> | S                   | -                          | V <sub>SS_3</sub>                                | -                                                                        | -                                      |

| F5     | 64     | 100     | V <sub>DD_3</sub> | S                   | -                          | V <sub>DD_3</sub>                                | -                                                                        | -                                      |

# 5 Electrical characteristics

## 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.3$  V (for the 2 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\Sigma$ ).

## 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

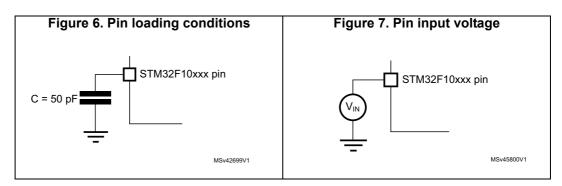

## 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 6*.

## 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 7*.

| Symbol          | Parameter                     | Conditions                          | £                 | Ма                     | Unit                    |      |  |

|-----------------|-------------------------------|-------------------------------------|-------------------|------------------------|-------------------------|------|--|

| Symbol          | Parameter                     | Conditions                          | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |  |

|                 |                               |                                     | 72 MHz            | 68                     | 68.4                    |      |  |

|                 |                               |                                     | 48 MHz            | 49                     | 49.2                    |      |  |

|                 |                               | External clock <sup>(2)</sup> , all | 36 MHz            | 38.7                   | 38.9                    |      |  |

|                 |                               | peripherals enabled                 | 24 MHz            | 27.3                   | 27.9                    | - mA |  |

|                 | Supply current in<br>Run mode |                                     | 16 MHz            | 20.2                   | 20.5                    |      |  |

|                 |                               |                                     | 8 MHz             | 10.2                   | 10.8                    |      |  |

| I <sub>DD</sub> |                               |                                     | 72 MHz            | 32.7                   | 32.9                    |      |  |

|                 |                               |                                     | 48 MHz            | 25                     | 25.2                    |      |  |

|                 |                               | External clock <sup>(2)</sup> , all | 36 MHz            | 20.3                   | 20.6                    |      |  |

|                 |                               | peripherals disabled                | 24 MHz            | 14.8                   | 15.1                    |      |  |

|                 |                               |                                     | 16 MHz            | 11.2                   | 11.7                    |      |  |

|                 |                               |                                     | 8 MHz             | 6.6                    | 7.2                     |      |  |

# Table 13. Maximum current consumption in Run mode, code with data processingrunning from Flash

1. Based on characterization, not tested in production.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

| Table 14. Maximum current consumption in Run mode, code with data processing |

|------------------------------------------------------------------------------|

| running from RAM                                                             |

| Symbol          | Parameter                        | Conditions                                               | f                 | Ma                     | Unit                    |      |

|-----------------|----------------------------------|----------------------------------------------------------|-------------------|------------------------|-------------------------|------|

|                 | Falametei                        | Conditions                                               | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                                  |                                                          | 72 MHz            | 65.5                   | 66                      |      |

|                 |                                  |                                                          | 48 MHz            | 45.4                   | 46                      |      |

|                 |                                  | External clock <sup>(2)</sup> , all                      | 36 MHz            | 35.5                   | 36.1                    |      |

|                 | Supply<br>current in<br>Run mode | peripherals enabled                                      | 24 MHz            | 25.2                   | 25.6                    | - mA |

|                 |                                  |                                                          | 16 MHz            | 18                     | 18.5                    |      |

|                 |                                  |                                                          | 8 MHz             | 10.5                   | 11                      |      |

| I <sub>DD</sub> |                                  | External clock <sup>(2)</sup> , all peripherals disabled | 72 MHz            | 31.4                   | 31.9                    |      |

|                 |                                  |                                                          | 48 MHz            | 27.8                   | 28.2                    |      |

|                 |                                  |                                                          | 36 MHz            | 17.6                   | 18.3                    | -    |

|                 |                                  |                                                          | 24 MHz            | 13.1                   | 13.8                    |      |

|                 |                                  |                                                          | 16 MHz            | 10.2                   | 10.9                    |      |

|                 |                                  |                                                          | 8 MHz             | 6.1                    | 7.8                     |      |

1. Based on characterization, tested in production at  $V_{\text{DD}}$  max,  $f_{\text{HCLK}}$  max..

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

|                 |                                    |                                   |                   | Туј                                       |                             |      |

|-----------------|------------------------------------|-----------------------------------|-------------------|-------------------------------------------|-----------------------------|------|

| Symbol          | Parameter                          | Conditions                        | f <sub>HCLK</sub> | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |

|                 |                                    |                                   | 72 MHz            | 28.2                                      | 6                           |      |

|                 |                                    |                                   | 48 MHz            | 19                                        | 4.2                         |      |

|                 |                                    |                                   | 36 MHz            | 14.7                                      | 3.4                         |      |

|                 |                                    |                                   | 24 MHz            | 10.1                                      | 2.5                         |      |

|                 |                                    |                                   | 16 MHz            | 6.7                                       | 2                           |      |

|                 |                                    | External clock <sup>(3)</sup>     | 8 MHz             | 3.2                                       | 1.3                         |      |

|                 | Supply<br>current in<br>Sleep mode |                                   | 4 MHz             | 2.3                                       | 1.2                         | mA   |

|                 |                                    |                                   | 2 MHz             | 1.7                                       | 1.16                        |      |

|                 |                                    |                                   | 1 MHz             | 1.5                                       | 1.1                         |      |

| I.              |                                    |                                   | 500 kHz           | 1.3                                       | 1.05                        |      |

| I <sub>DD</sub> |                                    |                                   | 125 kHz           | 1.2                                       | 1.05                        |      |

|                 |                                    |                                   | 36 MHz            | 13.7                                      | 2.6                         |      |

|                 |                                    |                                   | 24 MHz            | 9.3                                       | 1.8                         |      |

|                 |                                    |                                   | 16 MHz            | 6.3                                       | 1.3                         |      |

|                 |                                    | Running on high speed internal RC | 8 MHz             | 2.7                                       | 0.6                         |      |

|                 |                                    | (HSI), AHB prescaler              | 4 MHz             | 1.6                                       | 0.5                         |      |

|                 |                                    | used to reduce the<br>frequency   | 2 MHz             | 1                                         | 0.46                        |      |

|                 |                                    | 1 7                               | 1 MHz             | 0.8                                       | 0.44                        |      |

|                 |                                    |                                   | 500 kHz           | 0.6                                       | 0.43                        |      |

|                 |                                    |                                   | 125 kHz           | 0.5                                       | 0.42                        |      |

Table 18. Typical current consumption in Sleep mode, code running from Flash or RAM

1. Typical values are measures at  $T_A = 25$  °C,  $V_{DD} = 3.3$  V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 19*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with one peripheral clocked on (with only the clock applied)

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 6

DocID15274 Rev 10

## Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

| Symbol                                     | Parameter                                              | Conditions                       | Min                | Тур    | Мах                | Unit |  |  |  |  |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|--|--|--|--|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                  |                    | 32.768 | 1000               | kHz  |  |  |  |  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |  |  |  |  |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |  |  |  |  |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                | -      | -                  | ns   |  |  |  |  |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 19   |  |  |  |  |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                | -                  | 5      |                    | pF   |  |  |  |  |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                | 30                 | -      | 70                 | %    |  |  |  |  |

| ١ <sub>L</sub>                             | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |  |  |  |  |

Table 21. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

## I<sup>2</sup>S - SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 43* for SPI or in *Table 44* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Refer to Section 5.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                           | Conditions                                            | Min                 | Мах                 | Unit |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------|---------------------|---------------------|------|

| f <sub>SCK</sub>                             |                                     | Master mode                                           | -                   | 18                  | MHz  |

| 1/t <sub>c(SCK)</sub>                        | SPI clock frequency                 | Slave mode                                            | -                   | 18                  |      |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            | -                   | 8                   | ns   |

| DuCy(SCK)                                    | SPI slave input clock<br>duty cycle | Slave mode                                            | 30                  | 70                  | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                      | Slave mode                                            | 4 t <sub>PCLK</sub> | -                   |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                       | Slave mode                                            | 2 t <sub>PCLK</sub> | -                   |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | 50                  | 60                  |      |

| t <sub>su(MI)</sub>                          | Data input setup time               | Master mode                                           | 4                   | -                   |      |

| t <sub>su(SI)</sub>                          | Data input setup time               | Slave mode                                            | 5                   | -                   |      |

| t <sub>h(MI)</sub>                           | Data input hold time                | Master mode                                           | 5                   | -                   | no   |

| t <sub>h(SI)</sub>                           | Data input noid time                | Slave mode                                            | 5                   | -                   | ns   |

| t <sub>a(SO)</sub>                           | Data output access time             | Slave mode, f <sub>PCLK</sub> = 20 MHz                | -                   | 3*t <sub>PCLK</sub> |      |

| t <sub>v(SO)</sub>                           | Data output valid time              | Slave mode (after enable edge)                        | -                   | 34                  |      |

| t <sub>v(MO)</sub>                           | Data output valid time              | Master mode (after enable edge)                       | -                   | 8                   |      |

| t <sub>h(SO)</sub>                           | Data output hold time               | Slave mode (after enable edge)                        | 32                  | -                   |      |

| t <sub>h(MO)</sub>                           | Data output hold time               | Master mode (after enable edge)                       | 10                  | -                   |      |

Table 43. SPI characteristics

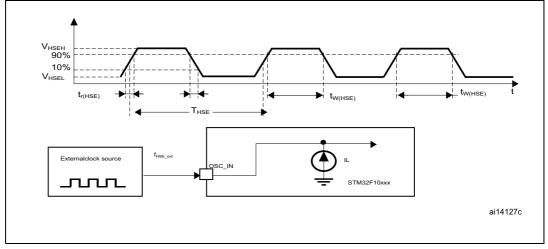

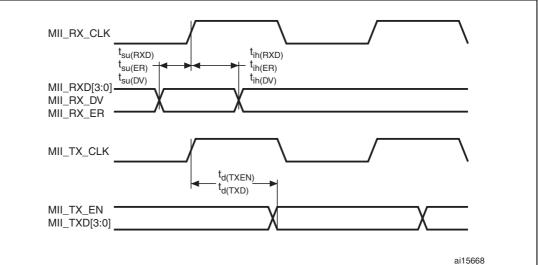

*Table 50* gives the list of Ethernet MAC signals for the RMII and *Figure 32* shows the corresponding timing diagram.

| Symbol               | Rating                           | Min | Тур | Max | Unit |

|----------------------|----------------------------------|-----|-----|-----|------|

| t <sub>su(RXD)</sub> | Receive data setup time          | 4   | -   | -   | ns   |

| t <sub>ih(RXD)</sub> | Receive data hold time           | 2   | -   | -   | ns   |

| t <sub>su(DV)</sub>  | Carrier sense set-up time        | 4   | -   | -   | ns   |

| t <sub>ih(DV)</sub>  | Carrier sense hold time          | 2   | -   | -   | ns   |

| t <sub>d(TXEN)</sub> | Transmit enable valid delay time | 8   | 10  | 16  | ns   |

| t <sub>d(TXD)</sub>  | Transmit data valid delay time   | 7   | 10  | 16  | ns   |

*Table 51* gives the list of Ethernet MAC signals for MII and *Figure 32* shows the corresponding timing diagram.

## Figure 33. Ethernet MII timing diagram

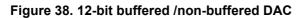

# 5.3.18 DAC electrical specifications

| Symbol                           | Parameter                                                                                                    | Min Typ Max U |     |                          | Unit | Comments                                                                                                               |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|---------------|-----|--------------------------|------|------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                           | Farameter                                                                                                    | IVIIII        | Тур | IVIAX                    | Unit | comments                                                                                                               |  |

| $V_{DDA}$                        | Analog supply voltage                                                                                        | 2.4           | -   | 3.6                      | V    | -                                                                                                                      |  |

| V <sub>REF+</sub>                | Reference supply voltage                                                                                     | 2.4           | -   | 3.6                      | V    | $V_{REF}$ must always be below $V_{DDA}$                                                                               |  |

| $V_{SSA}$                        | Ground                                                                                                       | 0             | -   | 0                        | V    | -                                                                                                                      |  |

| $R_{LOAD}^{(1)}$                 | Resistive load with buffer ON                                                                                | 5             | -   | -                        | kΩ   | -                                                                                                                      |  |

| R <sub>0</sub> <sup>(1)</sup>    | Impedance output with buffer<br>OFF                                                                          | -             | -   | 15                       | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 $M\Omega$ |  |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | -             | -   | 50                       | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                        |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2           | -   | -                        | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input code                            |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON                                                                        | -             | -   | V <sub>DDA</sub> – 0.2   | V    | (0x0E0) to (0xF1C) at V <sub>REF+</sub> =<br>3.6 V and (0x155) to (0xEAB) at<br>V <sub>REF+</sub> = 2.4 V              |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer OFF                                                                        | -             | 0.5 | -                        | mV   | It gives the maximum output excursion of the DAC.                                                                      |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage<br>with buffer OFF                                                                    | -             | -   | V <sub>REF+</sub> – 1LSB | V    |                                                                                                                        |  |

| I <sub>DDVREF+</sub>             | DAC DC current<br>consumption in quiescent<br>mode (Standby mode)                                            | -             | -   | 220                      | μA   | With no load, worst code (0xF1C)<br>at $V_{REF+}$ = 3.6 V in terms of DC<br>consumption on the inputs                  |  |

|                                  | DAC DC current                                                                                               | -             | -   | 380                      | μA   | With no load, middle code (0x800) on the inputs                                                                        |  |

| I <sub>DDA</sub>                 | onsumption in quiescent<br>node (Standby mode)                                                               | -             | -   | 480                      | μA   | With no load, worst code (0xF1C)<br>at $V_{REF+}$ = 3.6 V in terms of DC<br>consumption on the inputs                  |  |

| DNL <sup>(2)</sup>               | Differential non linearity<br>Difference between two                                                         | -             | -   | ±0.5                     | LSB  | Given for the DAC in 10-bit configuration.                                                                             |  |

| =                                | consecutive code-1LSB)                                                                                       | -             | -   | ±2                       | LSB  | Given for the DAC in 12-bit configuration.                                                                             |  |

|                                  | Integral non linearity<br>(difference between                                                                | -             | -   | ±1                       | LSB  | Given for the DAC in 10-bit configuration.                                                                             |  |

| INL <sup>(2)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -             | -   | ±4                       | LSB  | Given for the DAC in 12-bit configuration.                                                                             |  |

#### Table 56. DAC characteristics

#### **Electrical characteristics**

|                                      | Table 56. DAC characteristics (continued)                                                                                                                          |     |     |      |      |                                                                                                              |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--------------------------------------------------------------------------------------------------------------|--|--|

| Symbol                               | Parameter                                                                                                                                                          | Min | Тур | Мах  | Unit | Comments                                                                                                     |  |  |

| Offset <sup>(2)</sup>                | Offset error                                                                                                                                                       | -   | -   | ±10  | mV   | Given for the DAC in 12-bit configuration                                                                    |  |  |

|                                      | (difference between<br>measured value at Code<br>(0x800) and the ideal value =<br>V <sub>REF+</sub> /2)                                                            | -   | -   | ±3   | LSB  | Given for the DAC in 10-bit at<br>V <sub>REF+</sub> = 3.6 V                                                  |  |  |

|                                      |                                                                                                                                                                    | -   | -   | ±12  | LSB  | Given for the DAC in 12-bit at<br>V <sub>REF+</sub> = 3.6 V                                                  |  |  |

| Gain<br>error <sup>(2)</sup>         | Gain error                                                                                                                                                         | -   | -   | ±0.5 | %    | Given for the DAC in 12bit configuration                                                                     |  |  |

| t <sub>SETTLING</sub> <sup>(2)</sup> | Settling time (full scale: for a<br>10-bit input code transition<br>between the lowest and the<br>highest input codes when<br>DAC_OUT reaches final<br>value ±1LSB | -   | 3   | 4    | μs   | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                            |  |  |

| Update<br>rate <sup>(2)</sup>        | Max frequency for a correct<br>DAC_OUT change when<br>small variation in the input<br>code (from code i to i+1LSB)                                                 | -   | -   | 1    | MS/s | $C_{LOAD} \le 50 \text{ pF},$<br>$R_{LOAD} \ge 5 \text{ k}\Omega$                                            |  |  |

| t <sub>WAKEUP</sub> <sup>(2)</sup>   | Wakeup time from off state<br>(Setting the ENx bit in the<br>DAC Control register)                                                                                 | -   | 6.5 | 10   | μs   | $C_{LOAD} \le 50$ pF, $R_{LOAD} \ge 5$ k $\Omega$<br>input code between lowest and<br>highest possible ones. |  |  |

| PSRR+ <sup>(1)</sup>                 | Power supply rejection ratio<br>(to V <sub>DDA</sub> ) (static DC<br>measurement                                                                                   | -   | -67 | -40  | dB   | No R <sub>LOAD</sub> , C <sub>LOAD</sub> = 50 pF                                                             |  |  |

| Table 56. DAC characteristics | (continued) |

|-------------------------------|-------------|

|-------------------------------|-------------|

1. Guaranteed by design, not tested in production.

2. Guaranteed by characterization, not tested in production.

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

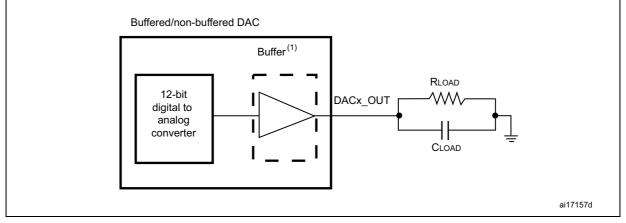

### **Device marking for LFBGA100**

The following figure shows the device marking for the LQFP100 package.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|

|        | Min   | Тур         | Max   | Min                   | Тур    | Max    |  |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |  |

| θ      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |  |

| ссс    | -     | -           | 0.080 | -                     | -      | 0.0031 |  |

#### Table 60.LQFP64 – 10 x 10 mm 64 pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

#### Figure 47.LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are in millimeters.

1. STMPS2141STR needed only if the application has to support bus-powered devices.

|             | Table 65. Document revision history (continued) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Date        | Revision                                        | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 19-Jun-2009 | 3                                               | Section 2.3.8: Boot modes and Section 2.3.20: Ethernet MAC<br>interface with dedicated DMA and IEEE 1588 support updated.<br>Section 2.3.24: Remap capability added.<br>Figure 1: STM32F105xx and STM32F107xx connectivity line block<br>diagram and Figure 5: Memory map updated.<br>In Table 5: Pin definitions:<br>- I2S3_WS, I2S3_CK and I2S3_SD default alternate functions<br>added<br>- small changes in signal names<br>- Note 6 modified<br>- ETH_MII_PPS_OUT and ETH_RMII_PPS_OUT replaced by<br>ETH_PPS_OUT<br>- ETH_MII_DDC and ETH_RMII_MDIO replaced by ETH_MDIO<br>- ETH_MII_MDIO and ETH_RMII_MDIO replaced by ETH_MDIO<br>- ETH_MII_MDC and ETH_RMII_MDIC replaced by ETH_MDC<br>Figures: Typical current consumption in Run mode versus frequency<br>(at 3.6 V) - code with data processing running from RAM, peripherals<br>enabled and Typical current consumption in Run mode, code with<br>data processing running from Flash, Table 14: Maximum current<br>consumption in Run mode, code with data processing running from<br>RAM and Table 15: Maximum current consumption in Run mode, code with<br>data processing running from Flash, Table 14: Maximum current<br>consumption in Run mode, code with data processing running from<br>RAM and Table 15: Maximum current consumption in Stop mode,<br>code running from Flash or RAM are to be determined.<br>Figure 12 and Figure 13 show typical curves. PLL1 renamed to PLL.<br>I <sub>DD</sub> supply current in Stop mode modified in Table 16: Typical and<br>maximum current consumptions in Stop and Standby modes.<br>Figure 11: Typical current consumption in Stop mode with regulator<br>in Run mode versus temperature at different VDD values, Figure 13:<br>Typical current consumption in Run mode, code with data<br>processing running from Flash, Table 18: Typical current<br>consumption in Step mode, code running from Flash or RAM and<br>Table 19: Peripheral current consumption in Run mode, code with data<br>processing running from Flash, Table 20: High-speed external user clock<br>characteristics.<br>Min PLL input clock (fPLL_IN), fPLL_OUT min and fPLL_VCO min<br>modified in Table 20: High-speed extern |  |  |  |  |  |

| Date | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date | Revision | Changes           Document status promoted from Preliminary data to full datasheet.           Number of DACs corrected in Table 3: STM32F105xx and           STM32F107xx family versus STM32F103xx family.           Note 5 added in Table 5: Pin definitions.           V <sub>RERINT</sub> and T <sub>Coeff</sub> added to Table 12: Embedded internal reference voltage.           Values added to Table 13: Maximum current consumption in Run mode, code with data processing running from Flash, Table 14: Maximum current consumption in Sleep mode, code running from Flash or RAM.           Typical I <sub>DD_VBAT</sub> value added in Table 16: Typical and maximum current consumptions in Slop and Standby modes.           Figure 10: Typical current consumption on VBAT with RTC on vs.           temperature at different VBAT values added.           Values modified in Table 17: Typical current consumption in Run mode, code with data processing running from Flash and Table 18: Typical current consumption in Sleep mode, code running from Flash or RAM.           fHSE_ext min modified in Table 20: High-speed external user clock characteristics.           CL1 and CL2 replaced by C in Table 22: HSE 3-25 MHz oscillator characteristics (fLSE = 32.768 kHz), notes modified and moved below the tables. Note 1 modified below Figure 16: Typical application with an 8 MHz crystal.           Conditions removed from Table 26: Low-power mode wakeup timings.           Standards modified in Section 5.3.10: EMC characteristics.           RPU and RPD modified in Table 36: I/O static characteristics.           Conditions added for V <sub>NF(NRST)</sub> |

Table 65. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11-May-2010 | 5        | Added BGA package.<br><i>Table 5: Pin definitions</i> :<br>ETH_RMII_RXD0 and ETH_RMII_RXD1 added in remap column for<br>PD9 and PD10, respectively.<br>Note added to ETH_MII_RX_DV, ETH_MII_RXD0, ETH_MII_RXD1,<br>ETH_MII_RXD2 and ETH_MII_RXD3<br>Updated <i>Table 36: I/O static characteristics on page 57</i><br>Added <i>Figure 18: Standard I/O input characteristics - CMOS port</i><br>to <i>Figure 21: 5 V tolerant I/O input characteristics - TTL port</i><br>Updated <i>Table 43: SPI characteristics on page 66</i> .<br>Updated <i>Table 43: SPI characteristics on page 69</i> .<br>Updated <i>Table 48: Ethernet DC electrical characteristics on page 72</i> .<br>Updated <i>Table 48: Ethernet DC electrical characteristics on page 72</i> .<br>Updated <i>Table 49: Dynamic characteristics: Ethernet MAC signals</i><br><i>for SMI on page 72</i> .<br>Updated <i>Table 50: Dynamic characteristics: Ethernet MAC signals</i><br><i>for RMII on page 73</i><br>Updated <i>Figure 59: USB O44TG FS + Ethernet solution on</i><br><i>page 100</i> .<br>Updated <i>Figure 60: USB OTG FS + I2S (Audio) solution on</i><br><i>page 100</i> . |

| 01-Aug-2011 | 6        | Changed SRAM size to 64 KB on all parts.<br>Updated PD0 and PD1 description in <i>Table 5: Pin definitions on</i><br>page 27<br>Updated footnotes below <i>Table 6: Voltage characteristics on page 36</i><br>and <i>Table 7: Current characteristics on page 36</i><br>Updated tw min in <i>Table 20: High-speed external user clock</i><br><i>characteristics on page 47</i><br>Updated startup time in <i>Table 23: LSE oscillator characteristics (fLSE</i><br>= 32.768 kHz) on page 50<br>Added Section 5.3.12: I/O current injection characteristics on<br>page 56<br>Updated <i>Table 36: I/O static characteristics on page 57</i><br>Add Interna code V to <i>Table 62: Ordering information scheme on</i><br>page 94                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 06-Mar-2014 | 7        | Added a "Packing" entry to <i>Table 62: Ordering information scheme</i><br>including "Blank = tray" and "TR = Tape and reel".<br>Referenced 4 Figures: <i>Figure 41, Figure 49, Figure 59</i> and<br><i>Figure 60.</i><br>Updated the "Package" line with "BGA100" in <i>Table 2:</i><br><i>STM32F105xx and STM32F107xx features and peripheral counts.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 65. Document revision history (continued)