## STMicroelectronics - <u>STM32F105VCT6TR Datasheet</u>

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2014110                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG        |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                      |

| Number of I/O              | 80                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 64K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 100-LQFP                                                                |

| Supplier Device Package    | 100-LQFP (14x14)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f105vct6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 6       | Packa  | age inf | ormation                                                        | 82   |

|---------|--------|---------|-----------------------------------------------------------------|------|

|         | 6.1    | LFBGA   | A100 package information                                        | 82   |

|         | 6.2    | LQFP    | 100 package information                                         | 85   |

|         | 6.3    | LQFP    | 64 package information                                          | 88   |

|         | 6.4    | Therm   | al characteristics                                              | 91   |

|         |        | 6.4.1   | Reference document                                              | . 91 |

|         |        | 6.4.2   | Selecting the product temperature range                         | . 92 |

| 7       | Part r | numbe   | ring                                                            | 94   |

| Appendi | x A A  | pplicat | ion block diagrams                                              | 95   |

|         | A.1    | USB C   | DTG FS interface solutions                                      | 95   |

|         | A.2    | Ethern  | et interface solutions                                          | 97   |

|         | A.3    | Compl   | ete audio player solutions                                      | 99   |

|         | A.4    | USB C   | TG FS interface + Ethernet/I <sup>2</sup> S interface solutions | 100  |

| 8       | Revis  | ion his | story                                                           | 103  |

# 1 Introduction

This datasheet provides the description of the STM32F105xx and STM32F107xx connectivity line microcontrollers. For more details on the whole STMicroelectronics STM32F10xxx family, refer to *Section 2.2: Full compatibility throughout the family*.

The STM32F105xx and STM32F107xx datasheet should be read in conjunction with the STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory refer to the STM32F10xxx Flash programming manual.

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the www.arm.com website.

| Periph                 | herals <sup>(1)</sup>                | STM32F105Rx                                                                                  | STM32F107Rx | STM32F105Vx | STM32F107Vx |  |  |

|------------------------|--------------------------------------|----------------------------------------------------------------------------------------------|-------------|-------------|-------------|--|--|

|                        | SPI(I <sup>2</sup> S) <sup>(2)</sup> | 3(2)                                                                                         | 3(2)        | 3(2)        | 3(2)        |  |  |

| Communicat             | l <sup>2</sup> C                     | 2                                                                                            | 1           | 2           | 1           |  |  |

| ion                    | USART                                |                                                                                              |             | 5           | -1          |  |  |

| interfaces             | USB OTG FS                           |                                                                                              |             | Yes         |             |  |  |

|                        | CAN                                  | 2                                                                                            |             |             |             |  |  |

| GPIOs                  |                                      | 51                                                                                           |             | 80          |             |  |  |

| 12-bit ADC             |                                      | 2                                                                                            |             |             |             |  |  |

| Number of ch           | annels                               | 16                                                                                           |             |             |             |  |  |

| 12-bit DAC             |                                      |                                                                                              |             | 2           |             |  |  |

| Number of ch           | annels                               | 2                                                                                            |             |             |             |  |  |

| CPU frequence          | су                                   |                                                                                              | 7           | 2 MHz       |             |  |  |

| Operating vol          | tage                                 | 2.0 to 3.6 V                                                                                 |             |             |             |  |  |

| Operating temperatures |                                      | Ambient temperatures: -40 to +85 °C /-40 to +105 °C<br>Junction temperature: -40 to + 125 °C |             |             |             |  |  |

#### Table 2. STM32F105xx and STM32F107xx features and peripheral counts (continued)

1. Refer to *Table 5: Pin definitions* for peripheral availability when the I/O pins are shared by the peripherals required by the application.

2. The SPI2 and SPI3 interfaces give the flexibility to work in either the SPI mode or the  $I^2S$  audio mode.

## 2.3.6 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 20 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

## 2.3.7 Clocks and startup

System clock selection is performed on startup, however, the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 3-25 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example with failure of an indirectly used external oscillator).

A single 25 MHz crystal can clock the entire system including the ethernet and USB OTG FS peripherals. Several prescalers and PLLs allow the configuration of the AHB frequency, the high speed APB (APB2) and the low speed APB (APB1) domains. The maximum frequency of the AHB and the high speed APB domains is 72 MHz. The maximum allowed frequency of the low speed APB domain is 36 MHz. Refer to *Figure 59: USB O44TG FS* + *Ethernet solution on page 100*.

The advanced clock controller clocks the core and all peripherals using a single crystal or oscillator. In order to achieve audio class performance, an audio crystal can be used. In this case, the  $I^2S$  master clock can generate all standard sampling frequencies from 8 kHz to 96 kHz with less than 0.5% accuracy error. Refer to *Figure 60: USB OTG FS + I2S (Audio)* solution on page 100.

To configure the PLLs, refer to *Table 63 on page 101*, which provides PLL configurations according to the application type.

## 2.3.8 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from User Flash

- Boot from System Memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1, USART2 (remapped), CAN2 (remapped) or USB OTG FS in device mode (DFU: device firmware upgrade). For remapped signals refer to *Table 5: Pin definitions*.

The USART peripheral operates with the internal 8 MHz oscillator (HSI), however the CAN and USB OTG FS can only function if an external 8 MHz, 14.7456 MHz or 25 MHz clock (HSE) is present.

For full details about the boot loader, refer to AN2606.

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| Тj               | Maximum junction temperature | 150         | °C   |

### Table 8. Thermal characteristics

## 5.3 Operating conditions

## 5.3.1 General operating conditions

| Symbol                          | Parameter                                                        | Conditions                           | Min | Мах | Unit |  |

|---------------------------------|------------------------------------------------------------------|--------------------------------------|-----|-----|------|--|

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                     | -                                    | 0   | 72  |      |  |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                    | -                                    | 0   | 36  | MHz  |  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                    | -                                    | 0   | 72  |      |  |

| V <sub>DD</sub>                 | Standard operating voltage                                       | -                                    | 2   | 3.6 | V    |  |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC not used)                       | Must be the same potential           | 2   | 3.6 | V    |  |

| V DDA <sup>®</sup>              | Analog operating voltage<br>(ADC used)                           | as V <sub>DD</sub> <sup>(2)</sup>    | 2.4 | 3.6 | v    |  |

| V <sub>BAT</sub>                | Backup operating voltage                                         | -                                    | 1.8 | 3.6 | V    |  |

|                                 | Power dissipation at $T_A =$                                     | LFBGA100                             | -   | 500 |      |  |

| $P_D$                           | 85 °C for suffix 6 or $T_{\Delta}$ =                             | LQFP100                              | -   | 434 | mW   |  |

|                                 | 105 °C for suffix $7^{(3)}$                                      | LQFP64                               | -   | 444 |      |  |

| _                               | Power dissipation at T <sub>A</sub> =                            | LQFP100                              | -   | 434 |      |  |

| PD                              | 85 °C for suffix 6 or $T_A =$ 105 °C for suffix 7 <sup>(4)</sup> | LQFP64                               | -   | 444 | mW   |  |

|                                 | Ambient temperature for 6                                        | Maximum power dissipation            | -40 | 85  | °C   |  |

| Та                              | suffix version                                                   | Low power dissipation <sup>(5)</sup> | -40 | 105 |      |  |

| IA                              | Ambient temperature for 7                                        | Maximum power dissipation            | -40 | 105 | °C   |  |

|                                 | suffix version                                                   | Low power dissipation <sup>(5)</sup> | -40 | 125 |      |  |

| TJ                              | lunction tomporature reaso                                       | 6 suffix version                     | -40 | 105 | °C   |  |

| IJ                              | Junction temperature range                                       | 7 suffix version                     | -40 | 125 | °C   |  |

## Table 9. General operating conditions

1. When the ADC is used, refer to *Table 52: ADC characteristics*.

2. It is recommended to power  $V_{DD}$  and  $V_{DDA}$  from the same source. A maximum difference of 300 mV between  $V_{DD}$  and  $V_{DDA}$  can be tolerated during power-up and operation.

3. If  $T_A$  is lower, higher  $\mathsf{P}_D$  values are allowed as long as  $\mathsf{T}_J$  does not exceed  $\mathsf{T}_J\mathsf{max}.$

4. If  $T_A$  is lower, higher  $\mathsf{P}_D$  values are allowed as long as  $\mathsf{T}_J$  does not exceed  $\mathsf{T}_J\mathsf{max}.$

5. In low power dissipation state,  $T_A$  can be extended to this range as long as  $T_J$  does not exceed  $T_J$ max.

## 5.3.4 Embedded reference voltage

The parameters given in *Table 12* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                                | Parameter                                                           | Conditions                        | Min  | Тур  | Max                 | Unit   |

|---------------------------------------|---------------------------------------------------------------------|-----------------------------------|------|------|---------------------|--------|

| V                                     | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +105 °C | 1.16 | 1.20 | 1.26                | V      |

| V <sub>REFINT</sub>                   | Internal reference voltage                                          | –40 °C < T <sub>A</sub> < +85 °C  | 1.16 | 1.20 | 1.24                | V      |

| T <sub>S_vrefint</sub> <sup>(1)</sup> | ADC sampling time when<br>reading the internal reference<br>voltage | -                                 | -    | 5.1  | 17.1 <sup>(2)</sup> | μs     |

| V <sub>RERINT</sub> <sup>(2)</sup>    | Internal reference voltage<br>spread over the temperature<br>range  | V <sub>DD</sub> = 3 V ±10 mV      | -    | -    | 10                  | mV     |

| T <sub>Coeff</sub> <sup>(2)</sup>     | Temperature coefficient                                             | -                                 | _    | -    | 100                 | ppm/°C |

Table 12. Embedded internal reference voltage

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design, not tested in production.

## 5.3.5 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code.

The current consumption is measured as described in *Figure 9: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code.

#### Maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load)

- All peripherals are disabled except when explicitly mentioned

- The Flash memory access time is adjusted to the f<sub>HCLK</sub> frequency (0 wait state from 0 to 24 MHz, 1 wait state from 24 to 48 MHz and 2 wait states above)

- Prefetch in ON (reminder: this bit must be set before clock setting and bus prescaling)

- When the peripherals are enabled f<sub>PCLK1</sub> = f<sub>HCLK</sub>/2, f<sub>PCLK2</sub> = f<sub>HCLK</sub>

The parameters given in *Table 13*, *Table 14* and *Table 15* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Cumhal          | Deverator         | Conditions                          | £                 | Ма                     | x <sup>(1)</sup>        | 11   |

|-----------------|-------------------|-------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol          | Parameter         | Conditions                          | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                   |                                     | 72 MHz            | 48.4                   | 49                      |      |

|                 |                   |                                     | 48 MHz            | 33.9                   | 34.4                    |      |

|                 |                   | External clock <sup>(2)</sup> , all | 36 MHz            | 26.7                   | 27.2                    |      |

|                 |                   | peripherals enabled                 | 24 MHz            | 19.3                   | 19.8                    |      |

|                 |                   |                                     | 16 MHz            | 14.2                   | 14.8                    |      |

|                 | Supply current in |                                     | 8 MHz             | 8.7                    | 9.1                     |      |

| I <sub>DD</sub> | Sleep mode        |                                     | 72 MHz            | 10.1                   | 10.6                    | mA   |

|                 |                   |                                     | 48 MHz            | 8.3                    | 8.75                    |      |

|                 |                   | External clock <sup>(2)</sup> , all | 36 MHz            | 7.5                    | 8                       |      |

|                 |                   | peripherals disabled                | 24 MHz            | 6.6                    | 7.1                     |      |

|                 |                   |                                     | 16 MHz            | 6                      | 6.5                     |      |

|                 |                   |                                     | 8 MHz             | 2.5                    | 3                       |      |

## Table 15. Maximum current consumption in Sleep mode, code running from Flash or RAM

1. Based on characterization, tested in production at  $V_{\text{DD}}$  max and  $f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

|                      |                                    |                                                                                                                                                 |                                              | Тур <sup>(1)</sup>                           |                                              |                           | ax                         |      |

|----------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|---------------------------|----------------------------|------|

| Symbol               | Parameter                          | Conditions                                                                                                                                      | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.0 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.4 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 3.3 V | T <sub>A</sub> =<br>85 °C | T <sub>A</sub> =<br>105 °C | Unit |

|                      |                                    | Regulator in Run mode, low-speed<br>and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog)        | -                                            | 32                                           | 33                                           | 600                       | 1300                       |      |

| I <sub>DD</sub>      | in Stop mode                       | Regulator in Low Power mode, low-<br>speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog) | -                                            | 25                                           | 26                                           | 590                       | 1280                       |      |

| -00                  |                                    | Low-speed internal RC oscillator and independent watchdog ON                                                                                    | -                                            | 3                                            | 3.8                                          | -                         | -                          | μA   |

|                      | in Standby                         | Low-speed internal RC oscillator<br>ON, independent watchdog OFF                                                                                | -                                            | 2.8                                          | 3.6                                          | -                         | -                          |      |

|                      | mode                               | Low-speed internal RC oscillator and<br>independent watchdog OFF, low-<br>speed oscillator and RTC OFF                                          | -                                            | 1.9                                          | 2.1                                          | 5 <sup>(2)</sup>          | 6.5 <sup>(2)</sup>         |      |

| I <sub>DD_VBAT</sub> | Backup<br>domain supply<br>current | Low-speed oscillator and RTC ON                                                                                                                 | 1.1                                          | 1.2                                          | 1.4                                          | 2.1 <sup>(2)</sup>        | 2.3 <sup>(2)</sup>         |      |

## Table 16. Typical and maximum current consumptions in Stop and Standby modes

1. Typical values are measured at  $T_A = 25$  °C.

2. Based on characterization, not tested in production.

|                 |                      |                                 |                                 |                                           | p <sup>(1)</sup>            |      |    |

|-----------------|----------------------|---------------------------------|---------------------------------|-------------------------------------------|-----------------------------|------|----|

| Symbol          | Parameter            | Conditions                      | f <sub>HCLK</sub>               | All peripherals<br>enabled <sup>(2)</sup> | All peripherals<br>disabled | Unit |    |

|                 |                      |                                 | 72 MHz                          | 47.3                                      | 28.3                        |      |    |

|                 |                      |                                 | 48 MHz                          | 32                                        | 19.6                        |      |    |

|                 |                      |                                 | 36 MHz                          | 24.6                                      | 15.4                        |      |    |

|                 |                      |                                 | 24 MHz                          | 16.8                                      | 10.6                        |      |    |

|                 |                      |                                 | 16 MHz                          | 11.8                                      | 7.4                         |      |    |

|                 |                      | External clock <sup>(3)</sup>   | 8 MHz                           | 5.9                                       | 3.7                         | mA   |    |

|                 |                      |                                 |                                 | 4 MHz                                     | 3.7                         | 2.9  |    |

|                 |                      |                                 |                                 | 2 MHz                                     | 2.5                         | 2    |    |

|                 |                      |                                 | 1 MHz                           | 1.8                                       | 1.53                        |      |    |

| I <sub>DD</sub> | Supply<br>current in |                                 |                                 | 500 kHz                                   | 1.5                         | 1.3  |    |

| טטי             | Run mode             |                                 | 125 kHz                         | 1.3                                       | 1.2                         |      |    |

|                 |                      |                                 | 36 MHz                          | 23.9                                      | 14.8                        |      |    |

|                 |                      |                                 | 24 MHz                          | 16.1                                      | 9.7                         |      |    |

|                 |                      | Running on high                 | 16 MHz                          | 11.1                                      | 6.7                         |      |    |

|                 |                      | speed internal RC               | 8 MHz                           | 5.6                                       | 3.8                         |      |    |

|                 |                      | (HSI), AHB<br>prescaler used to | (HSI), AHB<br>prescaler used to | 4 MHz                                     | 3.1                         | 2.1  | mA |

|                 |                      | reduce the                      | 2 MHz                           | 1.8                                       | 1.3                         |      |    |

|                 |                      | frequency                       | 1 MHz                           | 1.16                                      | 0.9                         |      |    |

|                 |                      |                                 | 500 kHz                         | 0.8                                       | 0.67                        |      |    |

|                 |                      |                                 | 125 kHz                         | 0.6                                       | 0.5                         |      |    |

Table 17. Typical current consumption in Run mode, code with data processing<br/>running from Flash

1. Typical values are measures at T\_A = 25 °C, V\_{DD} = 3.3 V.

2. Add an additional power consumption of 0.8 mA per ADC for the analog part. In applications, this consumption occurs only while the ADC is on (ADON bit is set in the ADC\_CR2 register).

3. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

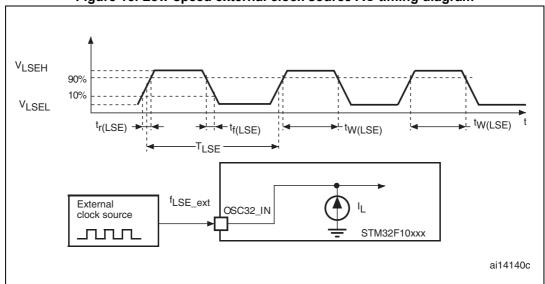

Figure 15. Low-speed external clock source AC timing diagram

#### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 3 to 25 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 22*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                             | Parameter                                                                                     | Conditions                                               | Min | Тур | Max | Unit |

|------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub>                | Oscillator frequency                                                                          | -                                                        | 3   |     | 25  | MHz  |

| R <sub>F</sub>                     | Feedback resistor                                                                             | -                                                        | -   | 200 | -   | kΩ   |

| С                                  | Recommended load capacitance versus equivalent serial resistance of the crystal $(R_S)^{(3)}$ | R <sub>S</sub> = 30 Ω                                    | -   | 30  | -   | pF   |

| i <sub>2</sub>                     | HSE driving current                                                                           | $V_{DD}$ = 3.3 V, $V_{IN}$ = $V_{SS}$<br>with 30 pF load | -   | -   | 1   | mA   |

| 9 <sub>m</sub>                     | Oscillator transconductance                                                                   | Startup                                                  | 25  | -   | -   | mA/V |

| t <sub>SU(HSE</sub> <sup>(4)</sup> | Startup time                                                                                  | $V_{DD}$ is stabilized                                   | -   | 2   | -   | ms   |

Table 22. HSE 3-25 MHz oscillator characteristics<sup>(1) (2)</sup>

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Based on characterization, not tested in production.

3. The relatively low value of the RF resistor offers a good protection against issues resulting from use in a humid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.

t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

| Symbol           | Para                             | ameter                         | Conditions                                                         | Min | Тур | Max | Unit |

|------------------|----------------------------------|--------------------------------|--------------------------------------------------------------------|-----|-----|-----|------|

| l <sub>lkg</sub> | Input leakag                     | e current <sup>(4)</sup>       | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -   | -   | ±1  | μA   |

| 0                |                                  |                                | V <sub>IN</sub> = 5 V, I/O FT                                      | -   | -   | 3   |      |

| R <sub>PU</sub>  | Weak pull-<br>up<br>equivalent   | All pins<br>except for<br>PA10 | $V_{IN} = V_{SS}$                                                  | 30  | 40  | 50  | kΩ   |

|                  | resistor <sup>(5)</sup>          | PA10                           |                                                                    | 8   | 11  | 15  |      |

| R <sub>PD</sub>  | Weak pull-<br>down<br>equivalent | All pins<br>except for<br>PA10 | $V_{IN} = V_{DD}$                                                  | 30  | 40  | 50  | kΩ   |

|                  | resistor <sup>(5)</sup>          | PA10                           |                                                                    | 8   | 11  | 15  | 1    |

| C <sub>IO</sub>  | I/O pin capa                     | citance                        | -                                                                  | -   | 5   | -   | pF   |

#### Table 36. I/O static characteristics (continued)

1. FT = Five-volt tolerant. In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

3. With a minimum of 100 mV.

4. Leakage could be higher than max. if negative current is injected on adjacent pins.

5. Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

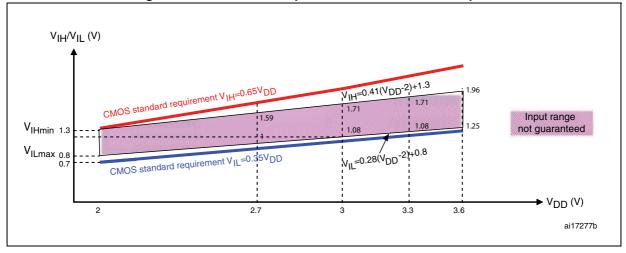

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 18* and *Figure 19* for standard I/Os, and in *Figure 20* and *Figure 21* for 5 V tolerant I/Os.

#### Figure 18. Standard I/O input characteristics - CMOS port

DocID15274 Rev 10

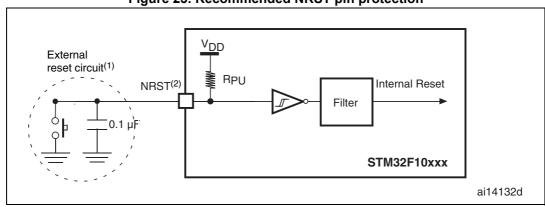

Figure 23. Recommended NRST pin protection

2. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 39. Otherwise the reset will not be taken into account by the device.

## 5.3.15 TIM timer characteristics

The parameters given in *Table 40* are guaranteed by design.

Refer to Section 5.3.12: I/O current injection characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

|                        |                                    | 1                             |        |                         |                      |

|------------------------|------------------------------------|-------------------------------|--------|-------------------------|----------------------|

| Symbol                 | Parameter                          | Conditions                    | Min    | Max                     | Unit                 |

| t ann                  | Timer resolution time              | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  |                                    | f <sub>TIMxCLK</sub> = 72 MHz | 13.9   | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock               | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4            | f <sub>TIMxCLK</sub> = 72 MHz | 0      | 36                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                   | -                             | -      | 16                      | bit                  |

| +                      | 16-bit counter clock period        | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER   | when internal clock is<br>selected | f <sub>TIMxCLK</sub> = 72 MHz | 0.0139 | 910                     | μs                   |

| t                      | Maximum possible count             | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT |                                    | f <sub>TIMxCLK</sub> = 72 MHz | -      | 59.6                    | s                    |

Table 40. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3, TIM4 and TIM5 timers.

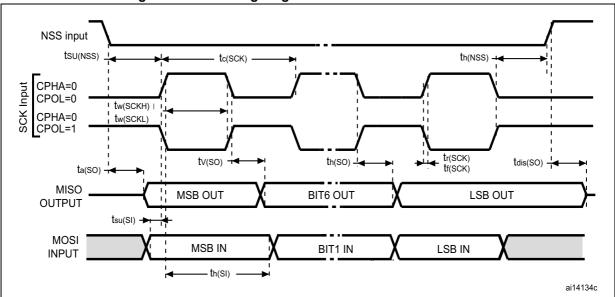

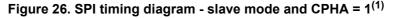

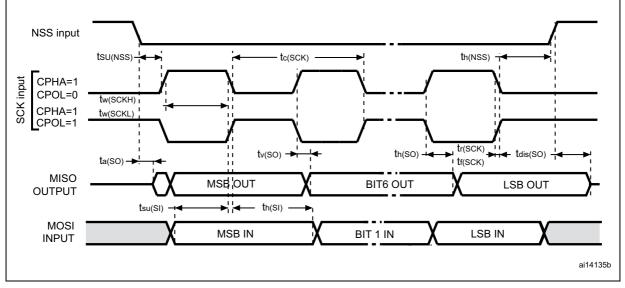

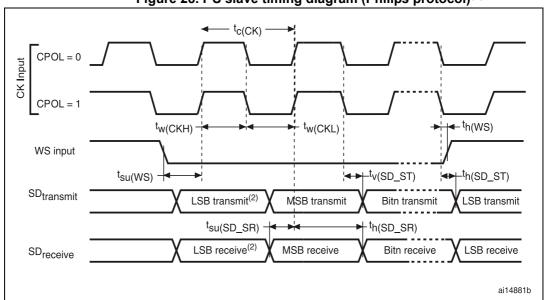

## I<sup>2</sup>S - SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 43* for SPI or in *Table 44* for  $I^2S$  are derived from tests performed under the ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

Refer to Section 5.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO for SPI and WS, CK, SD for I<sup>2</sup>S).

| Symbol                                       | Parameter                           | Conditions                                            | Min                 | Мах                 | Unit |

|----------------------------------------------|-------------------------------------|-------------------------------------------------------|---------------------|---------------------|------|

| f <sub>SCK</sub>                             | SPI clock frequency                 | Master mode                                           | -                   | 18                  | MHz  |

| 1/t <sub>c(SCK)</sub>                        | SPI Clock frequency                 | Slave mode                                            | -                   | 18                  |      |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time        | Capacitive load: C = 30 pF                            | -                   | 8                   | ns   |

| DuCy(SCK)                                    | SPI slave input clock<br>duty cycle | Slave mode                                            | 30                  | 70                  | %    |

| t <sub>su(NSS)</sub>                         | NSS setup time                      | Slave mode                                            | 4 t <sub>PCLK</sub> | -                   |      |

| t <sub>h(NSS)</sub>                          | NSS hold time                       | Slave mode                                            | 2 t <sub>PCLK</sub> | -                   |      |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time               | Master mode, f <sub>PCLK</sub> = 36 MHz,<br>presc = 4 | 50                  | 60                  |      |

| t <sub>su(MI)</sub>                          | Data input setup time               | Master mode                                           | 4                   | -                   |      |

| t <sub>su(SI)</sub>                          | Data input setup time               | Slave mode                                            | 5                   | -                   |      |

| t <sub>h(MI)</sub>                           | Data input hold time                | Master mode                                           | 5                   | -                   | ns   |

| t <sub>h(SI)</sub>                           | Data input noid time                | Slave mode                                            | 5                   | -                   | 115  |

| t <sub>a(SO)</sub>                           | Data output access time             | Slave mode, f <sub>PCLK</sub> = 20 MHz                | -                   | 3*t <sub>PCLK</sub> |      |

| t <sub>v(SO)</sub>                           | Data output valid time              | Slave mode (after enable edge)                        | -                   | 34                  |      |

| t <sub>v(MO)</sub>                           | Data output valid time              | Master mode (after enable edge)                       | -                   | 8                   |      |

| t <sub>h(SO)</sub>                           | Data output hold time               | Slave mode (after enable edge)                        | 32                  | -                   |      |

| t <sub>h(MO)</sub>                           |                                     | Master mode (after enable edge)                       | 10                  | -                   |      |

Table 43. SPI characteristics

Figure 25. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

Figure 28. I<sup>2</sup>S slave timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Measurement points are done at CMOS levels: 0.3 ×  $V_{DD}$  and 0.7 ×  $V_{DD}.$

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

### Figure 29. I<sup>2</sup>S master timing diagram (Philips protocol)<sup>(1)</sup>

- 1. Based on characterization, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

|                                          | Driver characteristics          |                                |     |     |    |  |  |  |

|------------------------------------------|---------------------------------|--------------------------------|-----|-----|----|--|--|--|

| Symbol Parameter Conditions Min Max Unit |                                 |                                |     |     |    |  |  |  |

| t <sub>r</sub>                           | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |

| t <sub>f</sub>                           | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |

| t <sub>rfm</sub>                         | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %  |  |  |  |

| V <sub>CRS</sub>                         | Output signal crossover voltage | -                              | 1.3 | 2.0 | V  |  |  |  |

## Table 47 USB OTG ES electrical characteristics<sup>(1)</sup>

1. Guaranteed by design, not tested in production.

Measured from 10% to 90% of the data signal. For more detailed informations, refer to USB Specification - Chapter 7 (version 2.0). 2.

#### **Ethernet characteristics**

Table 48 showns the Ethernet operating voltage.

#### Table 48. Ethernet DC electrical characteristics

| Symbol      |                                                        | Parameter | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |

|-------------|--------------------------------------------------------|-----------|---------------------|---------------------|------|

| Input level | Input level V <sub>DD</sub> Ethernet operating voltage |           | 3.0                 | 3.6                 | V    |

1. All the voltages are measured from the local ground potential.

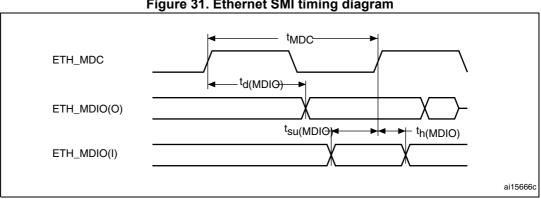

Table 49 gives the list of Ethernet MAC signals for the SMI (station management interface) and Figure 31 shows the corresponding timing diagram.

## Figure 31. Ethernet SMI timing diagram

#### Table 49. Dynamic characteristics: Ethernet MAC signals for SMI

| Symbol                | Rating                                  | Min  | Тур   | Max  | Unit |

|-----------------------|-----------------------------------------|------|-------|------|------|

| t <sub>MDC</sub>      | MDC cycle time (1.71 MHz, AHB = 72 MHz) | 583  | 583.5 | 584  | ns   |

| t <sub>d(MDIO)</sub>  | MDIO write data valid time              | 13.5 | 14.5  | 15.5 | ns   |

| t <sub>su(MDIO)</sub> | Read data setup time                    | 35   | -     | -    | ns   |

| t <sub>h(MDIO)</sub>  | Read data hold time                     | 0    | -     | -    | ns   |

| Table 51. Dynamic characteristics. Ethernet MAO signals for Min |                                  |     |     |     |      |  |  |

|-----------------------------------------------------------------|----------------------------------|-----|-----|-----|------|--|--|

| Symbol                                                          | Rating                           | Min | Тур | Мах | Unit |  |  |

| t <sub>su(RXD)</sub>                                            | Receive data setup time          | 10  | -   | -   | ns   |  |  |

| t <sub>ih(RXD)</sub>                                            | Receive data hold time           | 10  | -   | -   | ns   |  |  |

| t <sub>su(DV)</sub>                                             | Data valid setup time            | 10  | -   | -   | ns   |  |  |

| t <sub>ih(DV)</sub>                                             | Data valid hold time             | 10  | -   | -   | ns   |  |  |

| t <sub>su(ER)</sub>                                             | Error setup time                 | 10  | -   | -   | ns   |  |  |

| t <sub>ih(ER)</sub>                                             | Error hold time                  | 10  | -   | -   | ns   |  |  |

| t <sub>d(TXEN)</sub>                                            | Transmit enable valid delay time | 14  | 16  | 18  | ns   |  |  |

| t <sub>d(TXD)</sub>                                             | Transmit data valid delay time   | 13  | 16  | 20  | ns   |  |  |

Table 51. Dynamic characteristics: Ethernet MAC signals for MII

## CAN (controller area network) interface

Refer to Section 5.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (CANTX and CANRX).

## 5.3.17 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 52* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 9*.

Note: It is recommended to perform a calibration after each power-up.

|                                  | Table 52. ADC characteristics             |                                                       |                                                             |                    |                    |                    |  |  |

|----------------------------------|-------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|--|--|

| Symbol                           | Parameter                                 | Conditions                                            | Min                                                         | Тур                | Мах                | Unit               |  |  |

| $V_{DDA}$                        | Power supply                              | -                                                     | 2.4                                                         | -                  | 3.6                | V                  |  |  |

| $V_{REF^+}$                      | Positive reference voltage                | -                                                     | 2.4                                                         | -                  | V <sub>DDA</sub>   | V                  |  |  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin | -                                                     | -                                                           | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μA                 |  |  |

| f <sub>ADC</sub>                 | ADC clock frequency                       | -                                                     | 0.6                                                         | -                  | 14                 | MHz                |  |  |

| $f_S^{(2)}$                      | Sampling rate                             | -                                                     | 0.05                                                        | -                  | 1                  | MHz                |  |  |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 823                | kHz                |  |  |

|                                  |                                           | -                                                     | -                                                           | -                  | 17                 | 1/f <sub>ADC</sub> |  |  |

| V <sub>AIN</sub>                 | Conversion voltage range <sup>(3)</sup>   | -                                                     | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -                  | V <sub>REF+</sub>  | V                  |  |  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                  | See <i>Equation 1</i> and <i>Table 53</i> for details | -                                                           | -                  | 50                 | kΩ                 |  |  |

| $R_{ADC}^{(2)}$                  | Sampling switch resistance                | -                                                     | -                                                           | -                  | 1                  | kΩ                 |  |  |

| $C_{ADC}^{(2)}$                  | Internal sample and hold capacitor        | -                                                     | -                                                           | -                  | 8                  | pF                 |  |  |

| t <sub>CAL</sub> <sup>(2)</sup>  | Calibration time                          | f <sub>ADC</sub> = 14 MHz                             | 5                                                           | .9                 |                    | μs                 |  |  |

| 'CAL`´                           |                                           | -                                                     | 83                                                          |                    |                    | 1/f <sub>ADC</sub> |  |  |

| Symbol                           | Parameter                                          | Conditions                | Min                                                                        | Тур | Max              | Unit               |

|----------------------------------|----------------------------------------------------|---------------------------|----------------------------------------------------------------------------|-----|------------------|--------------------|

| t <sub>lat</sub> (2)             | Injection trigger conversion latency               | f <sub>ADC</sub> = 14 MHz | -                                                                          | -   | 0.214            | μs                 |

| 'lat` '                          |                                                    | -                         | -                                                                          | -   | 3 <sup>(4)</sup> | 1/f <sub>ADC</sub> |

| t <sub>latr</sub> (2)            | Regular trigger conversion latency                 | f <sub>ADC</sub> = 14 MHz | -                                                                          | -   | 0.143            | μs                 |

| 'latr'                           |                                                    | -                         | -                                                                          | -   | 2 <sup>(4)</sup> | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Sampling time                                      | f <sub>ADC</sub> = 14 MHz | 0.107                                                                      | -   | 17.1             | μs                 |

| LS.                              |                                                    | -                         | 1.5                                                                        | -   | 239.5            | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                      | -                         | 0                                                                          | 0   | 1                | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time (including                   | f <sub>ADC</sub> = 14 MHz | 1                                                                          | -   | 18               | μs                 |

|                                  | Total conversion time (including<br>sampling time) | -                         | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |     |                  | 1/f <sub>ADC</sub> |

## Table 52. ADC characteristics (continued)

1. Based on characterization, not tested in production.

2. Guaranteed by design, not tested in production.

3.  $V_{REF+}$  is internally connected to  $V_{DDA}$  and  $V_{REF-}$  is internally connected to  $V_{SSA}$ .

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in Table 52.

## Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{r_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (μs) | R <sub>AIN</sub> max (kΩ) |

|-------------------------|---------------------|---------------------------|

| 1.5                     | 0.11                | 0.4                       |

| 7.5                     | 0.54                | 5.9                       |

| 13.5                    | 0.96                | 11.4                      |

| 28.5                    | 2.04                | 25.2                      |

| 41.5                    | 2.96                | 37.2                      |

| 55.5                    | 3.96                | 50                        |

| 71.5                    | 5.11                | NA                        |

| 239.5                   | 17.1                | NA                        |

## Table 53. $R_{AIN}$ max for $f_{ADC} = 14 \text{ MHz}^{(1)}$

1. Based on characterization, not tested in production.

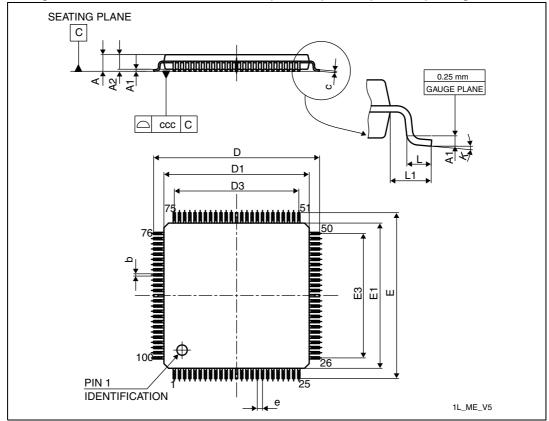

# 6.2 LQFP100 package information

Figure 43. LQFP100 – 14 x 14 mm 100 pin low-profile quad flat package outline

1. Drawing is not to scale. Dimension are in millimeter.

| Table | 59. LQPF100 - 100-pin, 14 x 14 mm l<br>mechanical dat |                 |

|-------|-------------------------------------------------------|-----------------|

|       |                                                       | · · · · · · (1) |

| Symbol |        | millimeters |        |        | inches <sup>(1)</sup> |        |

|--------|--------|-------------|--------|--------|-----------------------|--------|

| Symbol | Min    | Тур         | Мах    | Min    | Тур                   | Max    |

| А      | -      | -           | 1.600  | -      | -                     | 0.0630 |

| A1     | 0.050  | -           | 0.150  | 0.0020 | -                     | 0.0059 |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531 | 0.0551                | 0.0571 |

| b      | 0.170  | 0.220       | 0.270  | 0.0067 | 0.0087                | 0.0106 |

| С      | 0.090  | -           | 0.200  | 0.0035 | -                     | 0.0079 |

| D      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

| D3     | -      | 12.000      | -      | -      | 0.4724                | -      |

| Е      | 15.800 | 16.000      | 16.200 | 0.6220 | 0.6299                | 0.6378 |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433 | 0.5512                | 0.5591 |

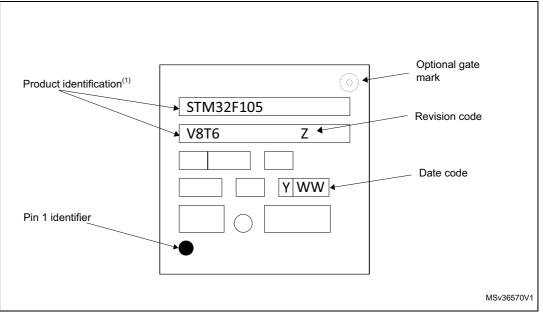

#### **Device marking for LQFP100**

The following figure shows the device marking for the LQFP100 package.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

## Figure 45.LQFP100 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

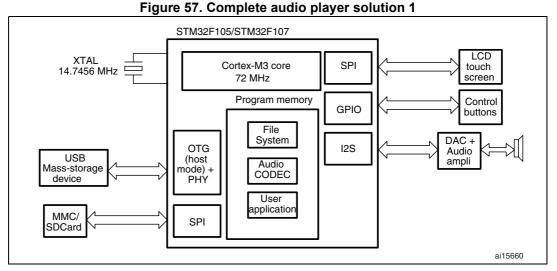

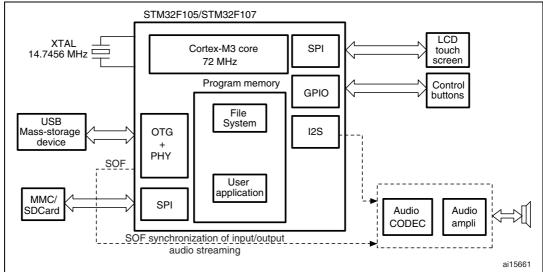

## A.3 Complete audio player solutions

Two solutions are offered, illustrated in Figure 57 and Figure 58.

*Figure* 57 shows storage media to audio DAC/amplifier streaming using a software Codec. This solution implements an audio crystal to provide audio class I<sup>2</sup>S accuracy on the master clock (0.5% error maximum, see the Serial peripheral interface section in the reference manual for details).

*Figure 58* shows storage media to audio Codec/amplifier streaming with SOF synchronization of input/output audio streaming using a hardware Codec.

#### Figure 58. Complete audio player solution 2