Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 72MHz                                                                      |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                         |

| Number of I/O              | 51                                                                         |

| Program Memory Size        | 256KB (256K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | -                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f107rct6tr    |

## **Contents**

| 1 | Intro | duction  |                                                                   | . 9  |

|---|-------|----------|-------------------------------------------------------------------|------|

| 2 | Desc  | cription |                                                                   | 10   |

|   | 2.1   | Device   | overview                                                          | . 10 |

|   | 2.2   | Full cor | mpatibility throughout the family                                 | 12   |

|   | 2.3   |          |                                                                   |      |

|   |       | 2.3.1    | ARM Cortex-M3 core with embedded Flash and SRAM                   |      |

|   |       | 2.3.2    | Embedded Flash memory                                             | . 14 |

|   |       | 2.3.3    | CRC (cyclic redundancy check) calculation unit                    |      |

|   |       | 2.3.4    | Embedded SRAM                                                     | . 14 |

|   |       | 2.3.5    | Nested vectored interrupt controller (NVIC)                       | . 14 |

|   |       | 2.3.6    | External interrupt/event controller (EXTI)                        | . 15 |

|   |       | 2.3.7    | Clocks and startup                                                | . 15 |

|   |       | 2.3.8    | Boot modes                                                        | . 15 |

|   |       | 2.3.9    | Power supply schemes                                              | . 16 |

|   |       | 2.3.10   | Power supply supervisor                                           | . 16 |

|   |       | 2.3.11   | Voltage regulator                                                 | . 16 |

|   |       | 2.3.12   | Low-power modes                                                   | . 16 |

|   |       | 2.3.13   | DMA                                                               | . 17 |

|   |       | 2.3.14   | RTC (real-time clock) and backup registers                        | . 17 |

|   |       | 2.3.15   | Timers and watchdogs                                              | . 18 |

|   |       | 2.3.16   | I <sup>2</sup> C bus                                              | . 19 |

|   |       | 2.3.17   | Universal synchronous/asynchronous receiver transmitters (USARTs) | . 19 |

|   |       | 2.3.18   | Serial peripheral interface (SPI)                                 | . 20 |

|   |       | 2.3.19   | Inter-integrated sound (I <sup>2</sup> S)                         | . 20 |

|   |       | 2.3.20   | Ethernet MAC interface with dedicated DMA and IEEE 1588 support   | . 20 |

|   |       | 2.3.21   | Controller area network (CAN)                                     | . 21 |

|   |       | 2.3.22   | Universal serial bus on-the-go full-speed (USB OTG FS)            | . 21 |

|   |       | 2.3.23   | GPIOs (general-purpose inputs/outputs)                            | . 21 |

|   |       | 2.3.24   | Remap capability                                                  | . 22 |

|   |       | 2.3.25   | ADCs (analog-to-digital converters)                               | . 22 |

|   |       | 2.3.26   | DAC (digital-to-analog converter)                                 | . 22 |

|   |       | 2.3.27   | Temperature sensor                                                |      |

|   |       | 2.3.28   | Serial wire JTAG debug port (SWJ-DP)                              | . 23 |

### Contents

| 6        | Packa                   | ige info           | rmation                                                        | 82   |

|----------|-------------------------|--------------------|----------------------------------------------------------------|------|

|          | 6.1                     | LFBGA <sup>2</sup> | 00 package information                                         | 82   |

|          | 6.2                     | LQFP10             | 0 package information                                          | 85   |

|          | 6.3                     | LQFP64             | package information                                            | 88   |

|          | 6.4                     | Thermal            | characteristics                                                | 91   |

|          |                         | 6.4.1              | Reference document                                             | . 91 |

|          |                         | 6.4.2              | Selecting the product temperature range                        | 92   |

| 7        | Part n                  | umberi             | ng                                                             | 94   |

| Appendix | <b>A</b> A <sub>I</sub> | pplication         | on block diagrams                                              | 95   |

|          | A.1                     | USB OT             | G FS interface solutions                                       | 95   |

|          | A.2                     | Etherne            | interface solutions                                            | 97   |

|          | A.3                     | Complet            | e audio player solutions                                       | 99   |

|          | A.4                     | USB OT             | G FS interface + Ethernet/I <sup>2</sup> S interface solutions | 100  |

| 8        | Revis                   | ion hist           | ory                                                            | 03   |

# List of figures

| Figure 1.  | STM32F105xx and STM32F107xx connectivity line block diagram                     | 13 |

|------------|---------------------------------------------------------------------------------|----|

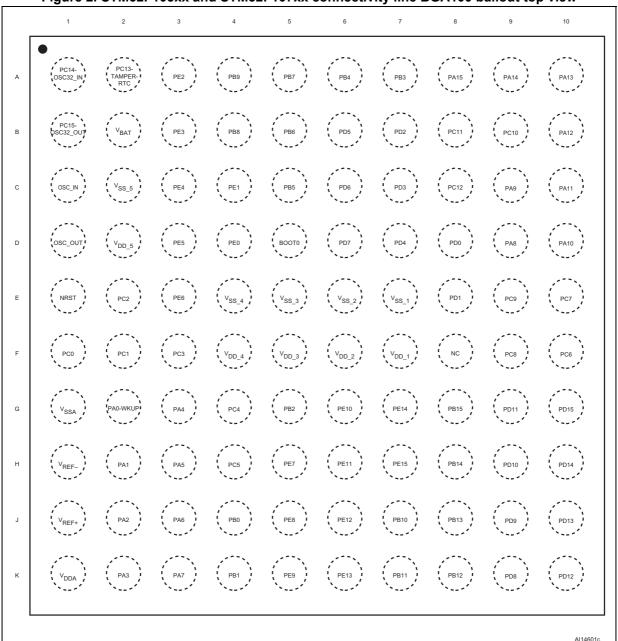

| Figure 2.  | STM32F105xx and STM32F107xx connectivity line BGA100 ballout top view           | 24 |

| Figure 3.  | STM32F105xx and STM32F107xx connectivity line LQFP100 pinout                    | 25 |

| Figure 4.  | STM32F105xx and STM32F107xx connectivity line LQFP64 pinout                     |    |

| Figure 5.  | Memory map                                                                      | 33 |

| Figure 6.  | Pin loading conditions                                                          |    |

| Figure 7.  | Pin input voltage                                                               | 34 |

| Figure 8.  | Power supply scheme                                                             | 35 |

| Figure 9.  | Current consumption measurement scheme                                          | 35 |

| Figure 10. | Typical current consumption on V <sub>BAT</sub> with RTC on vs. temperature at  |    |

|            | different V <sub>BAT</sub> values                                               | 42 |

| Figure 11. | Typical current consumption in Stop mode with regulator in Run mode             |    |

|            | versus temperature at different V <sub>DD</sub> values                          | 42 |

| Figure 12. | Typical current consumption in Stop mode with regulator in Low-power            |    |

|            | mode versus temperature at different V <sub>DD</sub> values                     | 43 |

| Figure 13. | Typical current consumption in Standby mode versus temperature at               |    |

|            | different V <sub>DD</sub> values                                                |    |

| Figure 14. | High-speed external clock source AC timing diagram                              |    |

| Figure 15. | Low-speed external clock source AC timing diagram                               |    |

| Figure 16. | Typical application with an 8 MHz crystal                                       |    |

| Figure 17. | Typical application with a 32.768 kHz crystal                                   |    |

| Figure 18. | Standard I/O input characteristics - CMOS port                                  |    |

| Figure 19. | Standard I/O input characteristics - TTL port                                   |    |

| Figure 20. | 5 V tolerant I/O input characteristics - CMOS port                              |    |

| Figure 21. | 5 V tolerant I/O input characteristics - TTL port                               |    |

| Figure 22. | I/O AC characteristics definition                                               |    |

| Figure 23. | Recommended NRST pin protection                                                 |    |

| Figure 24. | I <sup>2</sup> C bus AC waveforms and measurement circuit                       |    |

| Figure 25. | SPI timing diagram - slave mode and CPHA = 0                                    |    |

| Figure 26. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                     | 67 |

| Figure 27. | SPI timing diagram - master mode <sup>(1)</sup>                                 | 68 |

| Figure 28. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>         | 70 |

| Figure 29. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>        |    |

| Figure 30. | USB OTG FS timings: definition of data signal rise and fall time                |    |

| Figure 31. | Ethernet SMI timing diagram                                                     |    |

| Figure 32. | Ethernet RMII timing diagram                                                    |    |

| Figure 33. | Ethernet MII timing diagram                                                     |    |

| Figure 34. | ADC accuracy characteristics                                                    |    |

| Figure 35. | Typical connection diagram using the ADC                                        |    |

| Figure 36. | Power supply and reference decoupling ( $V_{REF+}$ not connected to $V_{DDA}$ ) |    |

| Figure 37. | Power supply and reference decoupling ( $V_{REF+}$ connected to $V_{DDA}$ )     |    |

| Figure 38. | 12-bit buffered /non-buffered DAC                                               | 80 |

| Figure 39. | LFBGA100 - 10 x 10 mm low profile fine pitch ball grid array package            |    |

|            | outline                                                                         | 82 |

| Figure 40. | LFBGA100 – 100-ball low profile fine pitch ball grid array, 10 x 10 mm,         |    |

|            | 0.8 mm pitch, package mechanical data                                           | 83 |

| Figure 41. | LFBGA100 – 100-ball low profile fine pitch ball grid array, 10 x 10 mm,         |    |

|            | 0.8 mm pitch, package recommended footprint                                     | 83 |

## 2.3 Overview

TRACECLK TRACED[0:3] as AF TPIU  $V_{DD} = 2 \text{ to } 3.6 \text{ V}$ Trace/Tric SW/JTAG Voltage reg. 3.3 V to 1.8 V  $V_{SS}$ NJTRST JTDI JTCK/SWCLK JTMS/SWDIO Flash 256 KB Cortex-M3 CPU @V<sub>DD</sub> JTDC NRST V<sub>DDA</sub> V<sub>SSA</sub> 64 KB POR / PDR RC HS Bus Matri x NVIC PVD PLL3 GP DMA1 MII\_TXD[3:0]/RMII\_TXD[1:0]

MII\_TX\_CLK/RMII\_TX\_CLK

MII\_TX\_EN/RMII\_TX\_EN @V<sub>DDA</sub> PLL2 OSC\_IN OSC\_OUT 7 channels XTAL osc 3-25 MHz MII\_RXD[3:0]/RMII\_RXD[1:0]

MII\_RX\_ER/RMII\_RX\_ER

MII\_RX\_CLK/RMII\_REF\_CLK

MII\_RX\_DV/RMII\_CRS\_DV GP DMA2 PCLK1

PCLK2

HCLK Reset & clock Standby V<sub>BAT</sub>=1.8 V to 3.6 V interface MII CRS MII\_COL/RMII\_COL MDC Ethernet MAC 10/100 ®V<sub>BAT</sub> DMA Ethernet OSC32\_IN OSC32\_OUT MDIO PPS\_OUT XTAL 32kHz Bac kup register RTC AWU TAMPER-RTC/ SOF DPRAM 2 KB DPRAM 2 KB ALARM/SECOND OUT VBUS ID DM DP Backup interface 4 Channels, ETR as AF USB OTG FS TIM2 4 Channels, ETR as AF SRAM 1.25 KB 4 Channels, ETR as AF í EXT.IT 80 AF 4 Channel s, ETR as AF TIM5 PA[15:0] < GPIO port A RX,TX, CTS, RTS, USART2 CK as AF PB[15:0] < > RX,TX, CTS, RTS, USART3 CK as AF PC[15:0] < GPIO port C UART4 PD[15:0] < GPIO port D RX,TX as AF UART5 PE[15:0] < GPIO port E MOSI/SD. MISO. MCK MOSI/SD, MISO, NICK, SCK/CK, NSS/WS as AF MOSI/SD, MISO, MCK, SCK/CK, NSS/WS as AF SPI2 / I2S2 4 Channels 4 compl. Channels 4 compl. Channels BKIN, ETR input as AF TIM1 SPI3 / I2S3 SCL,SDA, SMBA as AF I2C1 SCL,SDA,SMBA as AF MOSI MISO 12C2 SCK,NSS as AF RX,TX, CTS, RTS, bx CAN1 CAN1\_TX as AF USART1 WWDG CK as AF CAN1\_RX as AF Ĵ, SRAM 512B Temp sensor 1C CAN2\_TX a AF bxCAN2 16 ADC12\_INs 12bit ADC1 CAN2\_RX as AF 12bit DAC1 ADC1 & ADC2 12bit ADC2 DAC\_OUT1 as AF 12bit DAC 2 DAC\_OUT2 as AF TIM7  $V_{REF-}$ @ VDDA @VDDA ai15411

Figure 1. STM32F105xx and STM32F107xx connectivity line block diagram

T<sub>A</sub> = -40 °C to +85 °C (suffix 6, see *Table 62*) or -40 °C to +105 °C (suffix 7, see *Table 62*), junction temperature up to 105 °C or 125 °C, respectively.

<sup>2.</sup> AF = alternate function on I/O port pin.

### 2.3.9 Power supply schemes

- $V_{DD}$  = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 2.0 to 3.6 V: external analog power supplies for ADC, Reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 2.4 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

- $V_{BAT}$  = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when  $V_{DD}$  is not present.

## 2.3.10 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$ , without the need for an external reset circuit.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

### 2.3.11 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in the nominal regulation mode (Run)

- LPR is used in the Stop modes.

- Power down is used in Standby mode: the regulator output is in high impedance: the kernel circuitry is powered down, inducing zero consumption (but the contents of the registers and SRAM are lost)

This regulator is always enabled after reset. It is disabled in Standby mode.

#### 2.3.12 Low-power modes

The STM32F105xx and STM32F107xx connectivity line supports three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### • Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

#### Stop mode

Stop mode achieves the lowest power consumption while retaining the content of SRAM and registers. All clocks in the 1.8 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled. The voltage regulator can also be put either in normal or in low-power mode.

The device can be woken up from Stop mode by any of the EXTI line. The EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm or the USB OTG FS wakeup.

## 3 Pinouts and pin description

Figure 2. STM32F105xx and STM32F107xx connectivity line BGA100 ballout top view

- 1. I = input, O = output, S = supply, HiZ = high impedance.

- 2. FT = 5 V tolerant. All I/Os are V<sub>DD</sub> capable.

- 3. Function availability depends on the chosen device.

- 4. If several peripherals share the same I/O pin, to avoid conflict between these alternate functions only one peripheral should be enabled at a time through the peripheral clock enable bit (in the corresponding RCC peripheral clock enable register).

- 5. PC13, PC14 and PC15 are supplied through the power switch, and so their use in output mode is limited: they can be used only in output 2 MHz mode with a maximum load of 30 pF and only one pin can be put in output mode at a time.

- 6. Main function after the first backup domain power-up. Later on, it depends on the contents of the Backup registers even after reset (because these registers are not reset by the main reset). For details on how to manage these IOs, refer to the Battery backup domain and BKP register description sections in the STM32F10xxx reference manual, available from the STMicroelectronics website: www.st.com.

- This alternate function can be remapped by software to some other port pins (if available on the used package). For more

details, refer to the Alternate function I/O and debug configuration section in the STM32F10xxx reference manual, available

from the STMicroelectronics website: www.st.com.

- 8. SPI2/I2S2 and I2C2 are not available when the Ethernet is being used.

- 9. For the LQFP64 package, the pins number 5 and 6 are configured as OSC\_IN/OSC\_OUT after reset, however the functionality of PD0 and PD1 can be remapped by software on these pins. For the LQFP100 and BGA100 packages, PD0 and PD1 are available by default, so there is no need for remapping. For more details, refer to Alternate function I/O and debug configuration section in the STM32F10xxx reference manual.

Table 13. Maximum current consumption in Run mode, code with data processing running from Flash

| Symbol          | Parameter                  | Conditions                          |                   | Ma                     | Unit                    |       |

|-----------------|----------------------------|-------------------------------------|-------------------|------------------------|-------------------------|-------|

| Syllibol        | Parameter                  | Conditions                          | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Ollit |

|                 |                            |                                     | 72 MHz            | 68                     | 68.4                    |       |

|                 |                            |                                     | 48 MHz            | 49                     | 49.2                    |       |

|                 |                            | External clock <sup>(2)</sup> , all | 36 MHz            | 38.7                   | 38.9                    |       |

|                 | Supply current in Run mode | peripherals enabled                 | 24 MHz            | 27.3                   | 27.9                    |       |

|                 |                            |                                     | 16 MHz            | 20.2                   | 20.5                    |       |

|                 |                            |                                     | 8 MHz             | 10.2                   | 10.8                    | mΛ    |

| I <sub>DD</sub> |                            |                                     | 72 MHz            | 32.7                   | 32.9                    | mA    |

|                 |                            |                                     | 48 MHz            | 25                     | 25.2                    |       |

|                 |                            | External clock <sup>(2)</sup> , all | 36 MHz            | 20.3                   | 20.6                    |       |

|                 |                            | peripherals disabled                | 24 MHz            | 14.8                   | 15.1                    |       |

|                 |                            |                                     | 16 MHz            | 11.2                   | 11.7                    |       |

|                 |                            |                                     | 8 MHz             | 6.6                    | 7.2                     |       |

<sup>1.</sup> Based on characterization, not tested in production.

Table 14. Maximum current consumption in Run mode, code with data processing running from RAM

| Symbol          | Daramatar                  | Parameter Conditions f <sub>HCLK</sub> | £                   | Ma                     | Unit                    |      |  |

|-----------------|----------------------------|----------------------------------------|---------------------|------------------------|-------------------------|------|--|

|                 | Parameter                  |                                        | HCLK                | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Onit |  |

|                 |                            |                                        | 72 MHz              | 65.5                   | 66                      |      |  |

|                 |                            |                                        | 48 MHz              | 45.4                   | 46                      |      |  |

|                 |                            | External clock <sup>(2)</sup> , all    | 36 MHz              | 35.5                   | 36.1                    |      |  |

|                 |                            | peripherals enabled                    | peripherals enabled | 24 MHz                 | 25.2                    | 25.6 |  |

|                 | Supply current in Run mode |                                        |                     | 16 MHz                 | 18                      | 18.5 |  |

|                 |                            |                                        | 8 MHz               | 10.5                   | 11                      | mA   |  |

| I <sub>DD</sub> |                            |                                        | 72 MHz              | 31.4                   | 31.9                    | IIIA |  |

|                 |                            |                                        | 48 MHz              | 27.8                   | 28.2                    |      |  |

|                 |                            | External clock <sup>(2)</sup> , all    | 36 MHz              | 17.6                   | 18.3                    |      |  |

|                 |                            | peripherals disabled                   | 24 MHz              | 13.1                   | 13.8                    |      |  |

|                 |                            |                                        | 16 MHz              | 10.2                   | 10.9                    |      |  |

|                 |                            |                                        | 8 MHz               | 6.1                    | 7.8                     |      |  |

<sup>1.</sup> Based on characterization, tested in production at  $V_{\mbox{\scriptsize DD}}$  max,  $f_{\mbox{\scriptsize HCLK}}$  max..

<sup>2.</sup> External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

<sup>2.</sup> External clock is 8 MHz and PLL is on when  $f_{\mbox{\scriptsize HCLK}}$  > 8 MHz.

**Peripheral** Typical consumption at 25 °C Unit APB2-Bridge 3.47 **GPIOA** 6.39 **GPIOB** 6.39 **GPIOC** 6.11 **GPIOD** 6.39 APB2 (up to 72 MHz) µA/MHz **GPIOE** 6.11 SPI1 3.61 **USART1** 12.08 TIM1 23.47 ADC1<sup>(4)</sup> 18.21

Table 19. Peripheral current consumption (continued)

- 1. The BusMatrix is automatically active when at least one master is ON.(CPU, ETH-MAC, DMA1 or DMA2).

- 2. When I2S is enabled we have a consumption add equal to 0, 02 mA.

- 3. When DAC\_OUT1 or DAC\_OUT2 is enabled we have a consumption add equal to 0, 3 mA.

- Specific conditions for measuring ADC current consumption: f<sub>HCLK</sub> = 56 MHz, f<sub>APB1</sub> = f<sub>HCLK</sub>/2, f<sub>APB2</sub> = f<sub>HCLK</sub>, f<sub>ADCCLK</sub> = f<sub>APB2</sub>/4. When ADON bit in the ADC\_CR2 register is set to 1, a current consumption of analog part equal to 0.6 mA must be added.

#### 5.3.6 External clock source characteristics

#### High-speed external user clock generated from an external source

The characteristics given in *Table 20* result from tests performed using an high-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

Table 20. High-speed external user clock characteristics

| Symbol                    | Parameter                                           | Conditions                       | Min                | Тур | Max                | Unit |

|---------------------------|-----------------------------------------------------|----------------------------------|--------------------|-----|--------------------|------|

| f <sub>HSE_ext</sub>      | External user clock source frequency <sup>(1)</sup> |                                  | 1                  | 8   | 50                 | MHz  |

| V <sub>HSEH</sub>         | OSC_IN input pin high level voltage                 |                                  | 0.7V <sub>DD</sub> | -   | $V_{DD}$           | V    |

| V <sub>HSEL</sub>         | OSC_IN input pin low level voltage                  | -                                | $V_{SS}$           | ı   | 0.3V <sub>DD</sub> | ٧    |

| $t_{w(HSE)}$ $t_{w(HSE)}$ | OSC_IN high or low time <sup>(1)</sup>              |                                  | 5                  | ı   | ı                  | ns   |

| $t_{r(HSE)} \ t_{f(HSE)}$ | OSC_IN rise or fall time <sup>(1)</sup>             |                                  | 1                  | -   | 20                 | 113  |

| C <sub>in(HSE)</sub>      | OSC_IN input capacitance <sup>(1)</sup>             | -                                | -                  | 5   | -                  | pF   |

| DuCy <sub>(HSE)</sub>     | Duty cycle                                          | -                                | 45                 |     | 55                 | %    |

| ΙL                        | OSC_IN Input leakage current                        | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -   | ±1                 | μΑ   |

<sup>1.</sup> Guaranteed by design, not tested in production.

#### 5.3.7 Internal clock source characteristics

The parameters given in *Table 24* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

#### High-speed internal (HSI) RC oscillator

Table 24. HSI oscillator characteristics (1)

| Symbol                              | Parameter                        | Conditions                            |                                              | Min  | Тур | Max              | Unit |

|-------------------------------------|----------------------------------|---------------------------------------|----------------------------------------------|------|-----|------------------|------|

| f <sub>HSI</sub>                    | Frequency                        |                                       | -                                            | -    | 8   |                  | MHz  |

| DuCy <sub>(HSI)</sub>               | Duty cycle                       |                                       | -                                            | 45   | -   | 55               | %    |

|                                     |                                  | User-trimmed register <sup>(2)</sup>  | with the RCC_CR                              | -    | -   | 1 <sup>(3)</sup> | %    |

|                                     | Accuracy of the HSI oscillator   |                                       | $T_A = -40 \text{ to } 105 ^{\circ}\text{C}$ | -2   | -   | 2.5              | %    |

| ACC <sub>HSI</sub>                  |                                  | Factory-<br>calibrated <sup>(4)</sup> | T <sub>A</sub> = -10 to 85 °C                | -1.5 | -   | 2.2              | %    |

|                                     |                                  |                                       | T <sub>A</sub> = 0 to 70 °C                  | -1.3 | -   | 2                | %    |

|                                     |                                  | T <sub>A</sub> = 25 °C                |                                              | -1.1 | -   | 1.8              | %    |

| t <sub>su(HSI)</sub> <sup>(4)</sup> | HSI oscillator startup time      | -                                     |                                              | 1    | -   | 2                | μs   |

| I <sub>DD(HSI)</sub> <sup>(4)</sup> | HSI oscillator power consumption |                                       | -                                            | -    | 80  | 100              | μΑ   |

- 1.  $V_{DD}$  = 3.3 V,  $T_A$  = -40 to 105 °C unless otherwise specified.

- 2. Refer to application note AN2868 "STM32F10xxx internal RC oscillator (HSI) calibration" available from the ST website <a href="https://www.st.com">www.st.com</a>.

- 3. Guaranteed by design, not tested in production.

- 4. Based on characterization, not tested in production.

#### Low-speed internal (LSI) RC oscillator

Table 25. LSI oscillator characteristics (1)

| Symbol                              | Parameter                        | Min | Тур  | Max | Unit |

|-------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub> <sup>(2)</sup>     | Frequency                        | 30  | 40   | 60  | kHz  |

| t <sub>su(LSI)</sub> (3)            | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DD(LSI)</sub> <sup>(3)</sup> | LSI oscillator power consumption | -   | 0.65 | 1.2 | μΑ   |

- 1.  $V_{DD} = 3 \text{ V}$ ,  $T_A = -40 \text{ to } 105 \,^{\circ}\text{C}$  unless otherwise specified.

- 2. Based on characterization, not tested in production.

- 3. Guaranteed by design, not tested in production.

#### Wakeup time from low-power mode

The wakeup times given in *Table 26* is measured on a wakeup phase with a 8-MHz HSI RC oscillator. The clock source used to wake up the device depends from the current operating mode:

- Stop or Standby mode: the clock source is the RC oscillator

- Sleep mode: the clock source is the clock that was set before entering Sleep mode.

A device reset allows normal operations to be resumed.

The test results are given in *Table 31*. They are based on the EMS levels and classes defined in application note AN1709.

**Table 31. EMS characteristics**

| Symbol            | Parameter                                                                                                                                       | Conditions                                                                                              | Level/<br>Class |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                                  | $V_{\rm DD}$ = 3.3 V, LQFP100, $T_{\rm A}$ = +25 °C, $f_{\rm HCLK}$ = 72 MHz, conforms to IEC 61000-4-2 | 2B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on V <sub>DD</sub> and V <sub>SS</sub> pins to induce a functional disturbance | $V_{\rm DD}$ = 3.3 V, LQFP100, $T_{\rm A}$ = +25 °C, $f_{\rm HCLK}$ = 72 MHz, conforms to IEC 61000-4-4 | 4A              |

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### **Prequalification trials**

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behavior is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

#### **Electromagnetic Interference (EMI)**

The electromagnetic field emitted by the device are monitored while a simple application is executed (toggling 2 LEDs through the I/O ports). This emission test is compliant with IEC61967-2 standard which specifies the test board and the pin loading.

| Symbol           | Parameter                                                                   |                                | Conditions                                                         | Min | Тур | Мах | Unit |

|------------------|-----------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>Ikg</sub> | Input leakage current (4)                                                   |                                | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub><br>Standard I/Os | -   | -   | ±1  | μA   |

| ing ing          |                                                                             |                                | V <sub>IN</sub> = 5 V, I/O FT                                      | -   | -   | 3   |      |

| R <sub>PU</sub>  | Weak pull-<br>up<br>equivalent                                              | All pins<br>except for<br>PA10 | $V_{IN} = V_{SS}$                                                  | 30  | 40  | 50  | kΩ   |

|                  | resistor <sup>(5)</sup>                                                     | PA10                           |                                                                    | 8   | 11  | 15  |      |

| R <sub>PD</sub>  | R <sub>PD</sub> Weak pull-<br>down<br>equivalent<br>resistor <sup>(5)</sup> | down except for                | 30                                                                 | 40  | 50  | kΩ  |      |

|                  |                                                                             | PA10                           |                                                                    | 8   | 11  | 15  |      |

| C <sub>IO</sub>  | I/O pin capa                                                                | citance                        | -                                                                  | -   | 5   | -   | pF   |

Table 36. I/O static characteristics (continued)

- FT = Five-volt tolerant. In order to sustain a voltage higher than V<sub>DD</sub>+0.3 the internal pull-up/pull-down resistors must be disabled.

- 2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization, not tested in production.

- 3. With a minimum of 100 mV.

- 4. Leakage could be higher than max. if negative current is injected on adjacent pins.

- Pull-up and pull-down resistors are designed with a true resistance in series with a switchable PMOS/NMOS. This MOS/NMOS contribution to the series resistance is minimum (~10% order).

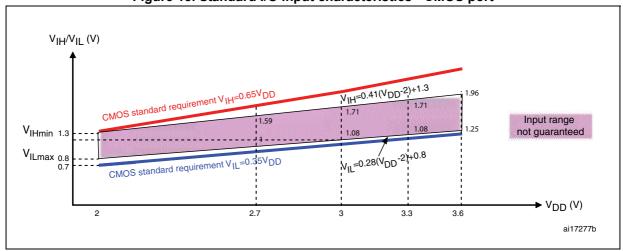

All I/Os are CMOS and TTL compliant (no software configuration required). Their characteristics cover more than the strict CMOS-technology or TTL parameters. The coverage of these requirements is shown in *Figure 18* and *Figure 19* for standard I/Os, and in *Figure 20* and *Figure 21* for 5 V tolerant I/Os.

Figure 18. Standard I/O input characteristics - CMOS port

577

#### 5.3.16 Communications interfaces

### I<sup>2</sup>C interface characteristics

Unless otherwise specified, the parameters given in *Table 41* are derived from tests performed under the ambient temperature,  $f_{PCLK1}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

The STM32F105xx and STM32F107xx  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DD}$  is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 41*. Refer also to *Section 5.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Comple al                                  | Downwater                               | Standard r       | mode I <sup>2</sup> C <sup>(1)</sup> | Fast mode              | l lmi4             |      |

|--------------------------------------------|-----------------------------------------|------------------|--------------------------------------|------------------------|--------------------|------|

| Symbol                                     | Parameter                               | Min              | Max                                  | Min                    | Max                | Unit |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7              | -                                    | 1.3                    | -                  | ше   |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0              | -                                    | 0.6                    | -                  | μs   |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250              | -                                    | 100                    | -                  |      |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>(3)</sup> | -                                    | 0 <sup>(4)</sup>       | 900 <sup>(3)</sup> |      |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   | -                | 1000                                 | 20 + 0.1C <sub>b</sub> | 300                | ns   |

| $t_{f(SDA)} \ t_{f(SCL)}$                  | SDA and SCL fall time                   | -                | 300                                  | 1                      | 300                |      |

| t <sub>h(STA)</sub>                        | Start condition hold time               | 4.0              | -                                    | 0.6                    | -                  |      |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time     | 4.7              | -                                    | 0.6                    | -                  | μs   |

| t <sub>su(STO)</sub>                       | Stop condition setup time               | 4.0              | -                                    | 0.6                    | -                  | μs   |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free) | 4.7              | -                                    | 1.3                    | -                  | μs   |

| C <sub>b</sub>                             | Capacitive load for each bus line       | -                | 400                                  | -                      | 400                | pF   |

Table 41. I<sup>2</sup>C characteristics

<sup>1.</sup> Guaranteed by design, not tested in production.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve the fast mode I<sup>2</sup>C frequencies and it must be a mulitple of 10 MHz in order to reach I<sup>2</sup>C fast mode maximum clock 400 kHz.

The maximum hold time of the Start condition has only to be met if the interface does not stretch the low period of SCL signal.

The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

| Driver characteristics                |                                 |                                |     |     |    |  |  |  |  |  |

|---------------------------------------|---------------------------------|--------------------------------|-----|-----|----|--|--|--|--|--|

| Symbol Parameter Conditions Min Max U |                                 |                                |     |     |    |  |  |  |  |  |

| t <sub>r</sub>                        | Rise time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |  |  |

| t <sub>f</sub>                        | Fall time <sup>(2)</sup>        | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |  |  |

| t <sub>rfm</sub>                      | Rise/ fall time matching        | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %  |  |  |  |  |  |

| V <sub>CRS</sub>                      | Output signal crossover voltage | -                              | 1.3 | 2.0 | V  |  |  |  |  |  |

Table 47. USB OTG FS electrical characteristics<sup>(1)</sup>

#### **Ethernet characteristics**

Table 48 showns the Ethernet operating voltage.

Table 48. Ethernet DC electrical characteristics

| Symb        | ol       | Parameter                  | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |

|-------------|----------|----------------------------|---------------------|---------------------|------|--|

| Input level | $V_{DD}$ | Ethernet operating voltage | 3.0                 | 3.6                 | V    |  |

<sup>1.</sup> All the voltages are measured from the local ground potential.

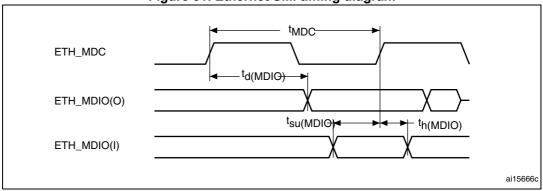

*Table 49* gives the list of Ethernet MAC signals for the SMI (station management interface) and *Figure 31* shows the corresponding timing diagram.

Figure 31. Ethernet SMI timing diagram

Table 49. Dynamic characteristics: Ethernet MAC signals for SMI

| Symbol                | Rating                                  | Min  | Тур   | Max  | Unit |

|-----------------------|-----------------------------------------|------|-------|------|------|

| t <sub>MDC</sub>      | MDC cycle time (1.71 MHz, AHB = 72 MHz) | 583  | 583.5 | 584  | ns   |

| t <sub>d(MDIO)</sub>  | MDIO write data valid time              | 13.5 | 14.5  | 15.5 | ns   |

| t <sub>su(MDIO)</sub> | Read data setup time                    | 35   | -     | -    | ns   |

| t <sub>h(MDIO)</sub>  | Read data hold time                     | 0    | -     | -    | ns   |

<sup>1.</sup> Guaranteed by design, not tested in production.

Measured from 10% to 90% of the data signal. For more detailed informations, refer to USB Specification -Chapter 7 (version 2.0).

## 5.3.18 DAC electrical specifications

Table 56. DAC characteristics

| Symbol                           | Parameter                                                                                                    | Min | Тур | Max                      | Unit     | Comments                                                                                                                |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|----------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                 | Analog supply voltage                                                                                        | 2.4 | -   | 3.6                      | V        | -                                                                                                                       |

| V <sub>REF+</sub>                | Reference supply voltage                                                                                     | 2.4 | -   | 3.6                      | V        | V <sub>REF+</sub> must always be below V <sub>DDA</sub>                                                                 |

| V <sub>SSA</sub>                 | Ground                                                                                                       | 0   | -   | 0                        | ٧        | -                                                                                                                       |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer ON                                                                                | 5   | -   | -                        | kΩ       | -                                                                                                                       |

| R <sub>O</sub> <sup>(1)</sup>    | Impedance output with buffer OFF                                                                             | -   | -   | 15                       | kΩ       | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | -   | -   | 50                       | pF       | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | 1                        | V        | It gives the maximum output excursion of the DAC.  It corresponds to 12-bit input code                                  |

| DAC_OUT max <sup>(1)</sup>       | Higher DAC_OUT voltage with buffer ON                                                                        | -   | ı   | V <sub>DDA</sub> – 0.2   | <b>V</b> | (0x0E0) to (0xF1C) at $V_{REF+}$ = 3.6 V and (0x155) to (0xEAB) at $V_{REF+}$ = 2.4 V                                   |

| DAC_OUT min <sup>(1)</sup>       | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                        | mV       | It gives the maximum output                                                                                             |

| DAC_OUT max <sup>(1)</sup>       | Higher DAC_OUT voltage with buffer OFF                                                                       | -   | -   | V <sub>REF+</sub> – 1LSB | V        | excursion of the DAC.                                                                                                   |

| I <sub>DDVREF+</sub>             | DAC DC current<br>consumption in quiescent<br>mode (Standby mode)                                            | -   | ı   | 220                      | μΑ       | With no load, worst code (0xF1C) at V <sub>REF+</sub> = 3.6 V in terms of DC consumption on the inputs                  |

|                                  | DAC DC current                                                                                               | -   | -   | 380                      | μA       | With no load, middle code (0x800) on the inputs                                                                         |

| I <sub>DDA</sub>                 | consumption in quiescent mode (Standby mode)                                                                 | -   | ı   | 480                      | μΑ       | With no load, worst code (0xF1C) at V <sub>REF+</sub> = 3.6 V in terms of DC consumption on the inputs                  |

| DNL <sup>(2)</sup>               | Differential non linearity Difference between two                                                            | -   | -   | ±0.5                     | LSB      | Given for the DAC in 10-bit configuration.                                                                              |

|                                  | consecutive code-1LSB)                                                                                       | -   | -   | ±2                       | LSB      | Given for the DAC in 12-bit configuration.                                                                              |

|                                  | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                       | LSB      | Given for the DAC in 10-bit configuration.                                                                              |

| INL <sup>(2)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                       | LSB      | Given for the DAC in 12-bit configuration.                                                                              |

## 5.3.19 Temperature sensor characteristics

Table 57. TS characteristics

| Symbol                         | Parameter                                      | Min  | Тур  | Max       | Unit  |

|--------------------------------|------------------------------------------------|------|------|-----------|-------|

| T <sub>L</sub> <sup>(1)</sup>  | V <sub>SENSE</sub> linearity with temperature  | -    | ±1   | <u>+2</u> | °C    |

| Avg_Slope <sup>(1)</sup>       | Average slope                                  | 4.0  | 4.3  | 4.6       | mV/°C |

| V <sub>25</sub> <sup>(1)</sup> | Voltage at 25 °C                               | 1.34 | 1.43 | 1.52      | V     |

| t <sub>START</sub> (2)         | Startup time                                   | 4    | -    | 10        | μs    |

| T <sub>S_temp</sub> (3)(2)     | ADC sampling time when reading the temperature | -    | -    | 17.1      | μs    |

<sup>1.</sup> Based on characterization, not tested in production.

<sup>2.</sup> Guaranteed by design, not tested in production.

<sup>3.</sup> Shortest sampling time can be determined in the application by multiple iterations.

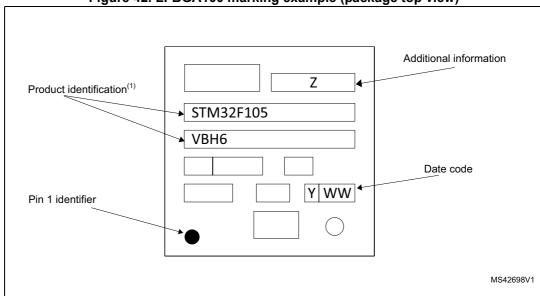

#### **Device marking for LFBGA100**

The following figure shows the device marking for the LQFP100 package.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 42. LFBGA100 marking example (package top view)

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

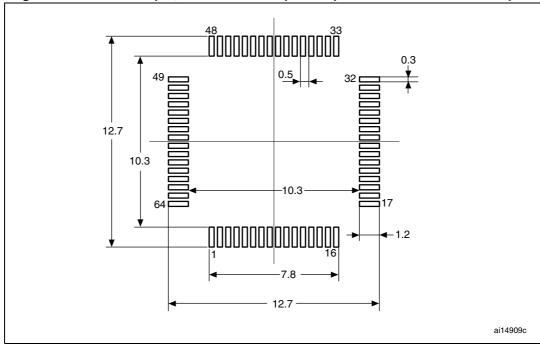

Table 60.LQFP64 - 10 x 10 mm 64 pin low-profile quad flat package mechanical data

| Symbol |       | millimeters |       | inches <sup>(1)</sup> |        |        |  |  |

|--------|-------|-------------|-------|-----------------------|--------|--------|--|--|

| Symbol | Min   | Тур         | Max   | Min                   | Тур    | Max    |  |  |

| е      | -     | 0.500       | -     | -                     | 0.0197 | -      |  |  |

| θ      | 0°    | 3.5°        | 7°    | 0°                    | 3.5°   | 7°     |  |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177                | 0.0236 | 0.0295 |  |  |

| L1     | -     | 1.000       | -     | -                     | 0.0394 | -      |  |  |

| ccc    | -     | -           | 0.080 | -                     | -      | 0.0031 |  |  |

<sup>1.</sup> Values in inches are converted from mm and rounded to 4 decimal digits.

Figure 47.LQFP64 - 64-pin, 10 x 10 mm low-profile quad flat recommended footprint

1. Dimensions are in millimeters.

## A.4 USB OTG FS interface + Ethernet/I<sup>2</sup>S interface solutions

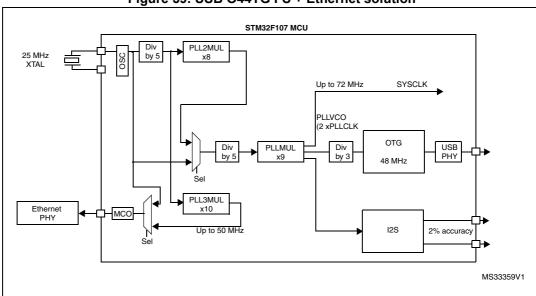

With the clock tree implemented on the STM32F107xx, only one crystal is required to work with both the USB (host/device/OTG) and the Ethernet (MII/RMII) interfaces. *Figure 59* illustrate the solution.

Figure 59. USB O44TG FS + Ethernet solution

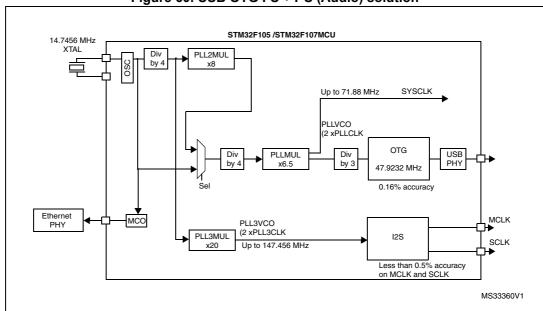

With the clock tree implem1ented on the STM32F107xx, only one crystal is required to work with both the USB (host/device/OTG) and the I<sup>2</sup>S (Audio) interfaces. *Figure 60* illustrate the solution.

Figure 60. USB OTG FS + I<sup>2</sup>S (Audio) solution

Table 63. PLL configurations

| Application                                                        | Crystal<br>value in<br>MHz<br>(XT1) | PREDIV2 | PLL2MUL       | PLLSRC | PREDIV1 | PLLMUL        | USB<br>prescaler<br>(PLLVCO<br>output) | PLL3MUL       | I2Sn<br>clock<br>input | MCO (main<br>clock<br>output)                |

|--------------------------------------------------------------------|-------------------------------------|---------|---------------|--------|---------|---------------|----------------------------------------|---------------|------------------------|----------------------------------------------|

| Ethernet only                                                      | 25                                  | /5      | PLL2ON<br>x8  | PLL2   | /5      | PLLON x9      | NA                                     | PLL3ON<br>x10 | NA                     | XT1 (MII)<br>PLL3 (RMII)                     |

| Ethernet + OTG                                                     | 25                                  | /5      | PLL2ON<br>x8  | PLL2   | /5      | PLLON x9      | /3                                     | PLL3ON<br>x10 | NA                     | XT1 (MII)<br>PLL3 (RMII)                     |

| Ethernet + OTG<br>+ basic audio                                    | 25                                  | /5      | PLL2ON<br>x8  | PLL2   | /5      | PLLON x9      | /3                                     | PLL3ON<br>x10 | PLL                    | XT1 (MII)<br>PLL3 (RMII)                     |

| Ethernet + OTG<br>+ Audio class<br>I <sup>2</sup> S <sup>(1)</sup> | 14.7456                             | /4      | PLL2ON<br>x12 | PLL2   | /4      | PLLON<br>x6.5 | /3                                     | PLL3ON<br>x20 | PLL3<br>VCO<br>Out     | NA<br>ETH PHY<br>must use its<br>own crystal |

| OTG only                                                           | 8                                   | NA      | PLL2OFF       | XT1    | /1      | PLLON x9      | /3                                     | PLL3OFF       | NA                     | NA                                           |

| OTG + basic<br>audio                                               | 8                                   | NA      | PLL2OFF       | XT1    | /1      | PLLON x9      | /3                                     | PLL3OFF       | PLL                    | NA                                           |

| OTG + Audio<br>class I <sup>2</sup> S <sup>(1)</sup>               | 14.7456                             | /4      | PLL2ON<br>x12 | PLL2   | /4      | PLLON<br>x6.5 | /3                                     | PLL3ON<br>x20 | PLL3<br>VCO<br>Out     | NA                                           |

| Audio class I <sup>2</sup> S only <sup>(1)</sup>                   | 14.7456                             | /4      | PLL2ON<br>x12 | PLL2   | /4      | PLLON<br>x6.5 | NA                                     | PLL3ON<br>x20 | PLL3<br>VCO<br>out     | NA                                           |

<sup>1.</sup> SYSCLK is set to be at 72 MHz except in this case where SYSCLK is at 71.88 MHz.

Table 64 give the  $I_{DD}$  run mode values that correspond to the conditions specified in Table 63.