# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 72MHz                                                                      |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB OTG |

| Peripherals                | DMA, POR, PWM, Voltage Detect, WDT                                         |

| Number of I/O              | 80                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 64K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | -                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f107vbt6      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Introduction

This datasheet provides the description of the STM32F105xx and STM32F107xx connectivity line microcontrollers. For more details on the whole STMicroelectronics STM32F10xxx family, refer to *Section 2.2: Full compatibility throughout the family*.

The STM32F105xx and STM32F107xx datasheet should be read in conjunction with the STM32F10xxx reference manual.

For information on programming, erasing and protection of the internal Flash memory refer to the STM32F10xxx Flash programming manual.

The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the www.arm.com website.

# 2 Description

The STM32F105xx and STM32F107xx connectivity line family incorporates the highperformance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 256 Kbytes and SRAM 64 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, four general-purpose 16-bit timers plus a PWM timer, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs, three SPIs, two I2Ss, five USARTs, an USB OTG FS and two CANs. Ethernet is available on the STM32F107xx only.

The STM32F105xx and STM32F107xx connectivity line family operates in the –40 to +105 °C temperature range, from a 2.0 to 3.6 V power supply. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F105xx and STM32F107xx connectivity line family offers devices in three different package types: from 64 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F105xx and STM32F107xx connectivity line microcontroller family suitable for a wide range of applications such as motor drives and application control, medical and handheld equipment, industrial applications, PLCs, inverters, printers, and scanners, alarm systems, video intercom, HVAC and home audio equipment.

## 2.1 Device overview

Figure 1 shows the general block diagram of the device family.

| Peripherals <sup>(1)</sup> |                      | STM32F105Rx |     | STM32 | F107Rx | STM32F105Vx |             | STM32F107Vx                |             |     |     |  |

|----------------------------|----------------------|-------------|-----|-------|--------|-------------|-------------|----------------------------|-------------|-----|-----|--|

| Flash memory in Kbytes     |                      | 64          | 128 | 256   | 128    | 256         | 64          | 128                        | 256         | 128 | 256 |  |

| SRAM in k                  | Kbytes               |             |     |       |        |             | 64          |                            |             |     |     |  |

| Package                    |                      |             |     | LQFP6 | 64     |             | LQFP<br>100 | LQFP<br>100,<br>BGA<br>100 | LQFP<br>100 | ,   |     |  |

| Ethernet                   |                      | No          |     |       | Y      | es          | No          |                            | Yes         |     |     |  |

| General-<br>purpose        |                      | 4           |     |       |        |             |             |                            |             |     |     |  |

| Timers                     | Advanced-<br>control | 1           |     |       |        |             |             |                            |             |     |     |  |

|                            | Basic                |             |     |       |        |             | 2           |                            |             |     |     |  |

| Tabla 2  | STM32E105vv a    | nd STM32E107vv     | fostures and | peripheral counts  |  |

|----------|------------------|--------------------|--------------|--------------------|--|

| Table 2. | 31 WJ32F 103XX d | 11U ST W32F 107 XX | leatures and | periprieral counts |  |

| Table 5. Pin definitions (continued |

|-------------------------------------|

|-------------------------------------|

|        | Pins   |         |                   |                     |                            |                                                  | Alternate func                                                                                                                                                                     | tions <sup>(4)</sup>                            |

|--------|--------|---------|-------------------|---------------------|----------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| BGA100 | LQFP64 | LQFP100 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                                                                                                                            | Remap                                           |

| K5     | -      | 40      | PE9               | I/O                 | FT                         | PE9                                              | -                                                                                                                                                                                  | TIM1_CH1                                        |

| -      | -      | -       | V <sub>SS_7</sub> | S                   | -                          | -                                                | -                                                                                                                                                                                  | -                                               |

| -      | -      | -       | V <sub>DD_7</sub> | S                   | -                          | -                                                | -                                                                                                                                                                                  | -                                               |

| G6     | -      | 41      | PE10              | I/O                 | FT                         | PE10                                             | -                                                                                                                                                                                  | TIM1_CH2N                                       |

| H6     | -      | 42      | PE11              | I/O                 | FT                         | PE11                                             | -                                                                                                                                                                                  | TIM1_CH2                                        |

| J6     | -      | 43      | PE12              | I/O                 | FT                         | PE12                                             | -                                                                                                                                                                                  | TIM1_CH3N                                       |

| K6     | -      | 44      | PE13              | I/O                 | FT                         | PE13                                             | -                                                                                                                                                                                  | TIM1_CH3                                        |

| G7     | -      | 45      | PE14              | I/O                 | FT                         | PE14                                             | -                                                                                                                                                                                  | TIM1_CH4                                        |

| H7     | -      | 46      | PE15              | I/O                 | FT                         | PE15                                             | -                                                                                                                                                                                  | TIM1_BKIN                                       |

| J7     | 29     | 47      | PB10              | I/O                 | FT                         | PB10                                             | I2C2_SCL <sup>(8)</sup> /USART3_TX <sup>(7)</sup> /<br>ETH_MII_RX_ER                                                                                                               | TIM2_CH3                                        |

| К7     | 30     | 48      | PB11              | I/O                 | FT                         | PB11                                             | I2C2_SDA <sup>(8)</sup> /USART3_RX <sup>(7)</sup> /<br>ETH_MII_TX_EN/<br>ETH_RMII_TX_EN                                                                                            | TIM2_CH4                                        |

| E7     | 31     | 49      | V <sub>SS_1</sub> | S                   | -                          | V <sub>SS_1</sub>                                | -                                                                                                                                                                                  | -                                               |

| F7     | 32     | 50      | V <sub>DD_1</sub> | S                   | -                          | V <sub>DD_1</sub>                                | -                                                                                                                                                                                  | -                                               |

| К8     | 33     | 51      | PB12              | I/O                 | FT                         | PB12                                             | SPI2_NSS <sup>(8)</sup> /I2S2_WS <sup>(8)</sup> /<br>I2C2_SMBA <sup>(8)</sup> /<br>USART3_CK <sup>(7)</sup> /TIM1_BKIN <sup>(7)</sup> /<br>CAN2_RX/ ETH_MII_TXD0/<br>ETH_RMII_TXD0 | -                                               |

| J8     | 34     | 52      | PB13              | I/O                 | FT                         | PB13                                             | SPI2_SCK <sup>(8)</sup> / I2S2_CK <sup>(8)</sup> /<br>USART3_CTS <sup>(7)</sup> /<br>TIM1_CH1N/CAN2_TX/<br>ETH_MII_TXD1/<br>ETH_RMII_TXD1                                          | -                                               |

| H8     | 35     | 53      | PB14              | I/O                 | FT                         | PB14                                             | SPI2_MISO <sup>(8)</sup> / TIM1_CH2N /<br>USART3_RTS <sup>(7)</sup>                                                                                                                | -                                               |

| G8     | 36     | 54      | PB15              | I/O                 | FT                         | PB15                                             | SPI2_MOSI <sup>(8)</sup> / I2S2_SD <sup>(8)</sup> /<br>TIM1_CH3N <sup>(7)</sup>                                                                                                    | -                                               |

| К9     | -      | 55      | PD8               | I/O                 | FT                         | PD8                                              | -                                                                                                                                                                                  | USART3_TX/<br>ETH_MII_RX_DV/<br>ETH_RMII_CRS_DV |

## 5.1.6 Power supply scheme

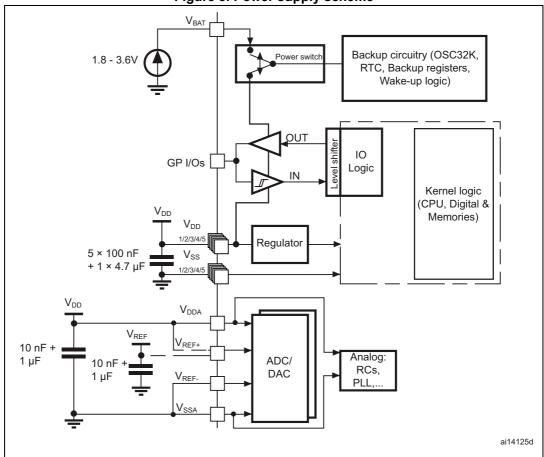

Figure 8. Power supply scheme

## 5.1.7 Current consumption measurement

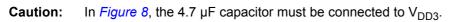

#### Figure 9. Current consumption measurement scheme

# 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 6: Voltage characteristics*, *Table 7: Current characteristics*, and *Table 8: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                                               | Min                  | Мах                  | Unit |

|-----------------------------------|-----------------------------------------------------------------------|----------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}$ and $V_{DD})^{(1)}$ | -0.3                 | 4.0                  |      |

| V <sub>IN</sub> <sup>(2)</sup>    | Input voltage on five volt tolerant pin                               | V <sub>SS</sub> –0.3 | V <sub>DD</sub> +4.0 | V    |

| VIN'                              | Input voltage on any other pin                                        | V <sub>SS</sub> -0.3 | 4.0                  |      |

| ΔV <sub>DDx</sub>                 | Variations between different V <sub>DD</sub> power pins               | -                    | 50                   | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins                      | -                    | 50                   | IIIV |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                    | see Section 5.3.11:  |                      | -    |

| Table 6. Volt | age characteristics |

|---------------|---------------------|

|---------------|---------------------|

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. V<sub>IN</sub> maximum must always be respected. Refer to *Table 7: Current characteristics* for the maximum allowed injected current values.

| Symbol                               | Ratings                                                                 | Max.  | Unit |

|--------------------------------------|-------------------------------------------------------------------------|-------|------|

| I <sub>VDD</sub>                     | Total current into $V_{DD}/V_{DDA}$ power lines (source) <sup>(1)</sup> |       |      |

| I <sub>VSS</sub>                     | Total current out of $V_{SS}$ ground lines (sink) <sup>(1)</sup>        | 150   |      |

|                                      | Output current sunk by any I/O and control pin                          | 25    |      |

| Ι <sub>ΙΟ</sub>                      | Output current source by any I/Os and control pin                       | -25   | mA   |

| ı (2)                                | Injected current on five volt tolerant pins <sup>(3)</sup>              | -5/+0 |      |

| I <sub>INJ(PIN)</sub> <sup>(2)</sup> | Injected current on any other pin <sup>(4)</sup>                        | ± 5   |      |

| $\Sigma I_{INJ(PIN)}$                | Total injected current (sum of all I/O and control pins) <sup>(5)</sup> | ± 25  |      |

#### Table 7. Current characteristics

1. All main power ( $V_{DD}$ ,  $V_{DDA}$ ) and ground ( $V_{SS}$ ,  $V_{SSA}$ ) pins must always be connected to the external power supply, in the permitted range.

2. Negative injection disturbs the analog performance of the device. See *Note: on page 76*.

Positive injection is not possible on these I/Os. A negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 6: Voltage characteristics* for the maximum allowed input voltage values.

A positive injection is induced by V<sub>IN</sub>>V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 6: Voltage characteristics* for the maximum allowed input voltage values.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

## 5.3.2 Operating conditions at power-up / power-down

Subject to general operating conditions for  $T_A$ .

| Symbol           | Parameter                      | Condition | Min | Мах | Unit  |

|------------------|--------------------------------|-----------|-----|-----|-------|

| t <sub>VDD</sub> | $V_{\text{DD}}$ rise time rate |           | 0   | -   | μs/V  |

| TJ               | V <sub>DD</sub> fall time rate | -         | 20  | -   | μ5/ V |

Table 10. Operating condition at power-up / power down

## 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 11* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                               | Parameter                | Conditions                  | Min                | Тур  | Max  | Unit |

|--------------------------------------|--------------------------|-----------------------------|--------------------|------|------|------|

|                                      |                          | PLS[2:0]=000 (rising edge)  | 2.1                | 2.18 | 2.26 | V    |

|                                      |                          | PLS[2:0]=000 (falling edge) | 2                  | 2.08 | 2.16 | V    |

|                                      |                          | PLS[2:0]=001 (rising edge)  | 2.19               | 2.28 | 2.37 | V    |

|                                      |                          | PLS[2:0]=001 (falling edge) | 2.09               | 2.18 | 2.27 | V    |

|                                      |                          | PLS[2:0]=010 (rising edge)  | 2.28               | 2.38 | 2.48 | V    |

|                                      |                          | PLS[2:0]=010 (falling edge) | 2.18               | 2.28 | 2.38 | V    |

|                                      |                          | PLS[2:0]=011 (rising edge)  | 2.38               | 2.48 | 2.58 | V    |

| V                                    | Programmable voltage     | PLS[2:0]=011 (falling edge) | 2.28               | 2.38 | 2.48 | V    |

| V <sub>PVD</sub>                     | detector level selection | PLS[2:0]=100 (rising edge)  | 2.47               | 2.58 | 2.69 | V    |

|                                      |                          | PLS[2:0]=100 (falling edge) | 2.37               | 2.48 | 2.59 | V    |

|                                      |                          | PLS[2:0]=101 (rising edge)  | 2.57               | 2.68 | 2.79 | V    |

|                                      |                          | PLS[2:0]=101 (falling edge) | 2.47               | 2.58 | 2.69 | V    |

|                                      |                          | PLS[2:0]=110 (rising edge)  | 2.66               | 2.78 | 2.9  | V    |

|                                      |                          | PLS[2:0]=110 (falling edge) | 2.56               | 2.68 | 2.8  | V    |

|                                      |                          | PLS[2:0]=111 (rising edge)  | 2.76               | 2.88 | 3    | V    |

|                                      |                          | PLS[2:0]=111 (falling edge) | 2.66               | 2.78 | 2.9  | V    |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis           | -                           | -                  | 100  | -    | mV   |

| M                                    | Power on/power down      | Falling edge                | 1.8 <sup>(1)</sup> | 1.88 | 1.96 | V    |

| V <sub>POR/PDR</sub>                 | reset threshold          | Rising edge                 | 1.84               | 1.92 | 2.0  | V    |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis           | -                           | -                  | 40   | -    | mV   |

| T <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization      | -                           | 1                  | 2.5  | 4.5  | ms   |

#### Table 11. Embedded reset and power control block characteristics

1. The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR/PDR}}$  value.

2. Guaranteed by design, not tested in production.

DocID15274 Rev 10

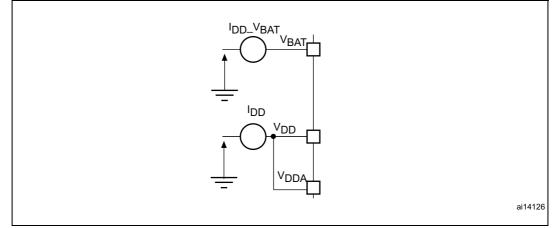

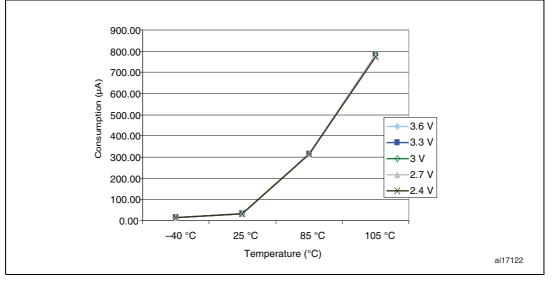

Figure 10. Typical current consumption on  $\rm V_{BAT}$  with RTC on vs. temperature at different  $\rm V_{BAT}$  values

Figure 11. Typical current consumption in Stop mode with regulator in Run mode versus temperature at different  $V_{DD}$  values

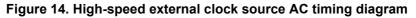

#### Low-speed external user clock generated from an external source

The characteristics given in *Table 21* result from tests performed using an low-speed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 9*.

| Symbol                                     | Parameter                                              | Conditions                       | Min                | Тур    | Мах                | Unit |

|--------------------------------------------|--------------------------------------------------------|----------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                       | User External clock source<br>frequency <sup>(1)</sup> |                                  |                    | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                          | OSC32_IN input pin high level voltage                  |                                  | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | V    |

| V <sub>LSEL</sub>                          | OSC32_IN input pin low level voltage                   | -                                | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | v    |

| t <sub>w(LSE)</sub><br>t <sub>w(LSE)</sub> | OSC32_IN high or low time <sup>(1)</sup>               |                                  | 450                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub> | OSC32_IN rise or fall time <sup>(1)</sup>              |                                  | -                  | -      | 50                 | 19   |

| C <sub>in(LSE)</sub>                       | OSC32_IN input capacitance <sup>(1)</sup>              | -                                | -                  | 5      |                    | pF   |

| DuCy <sub>(LSE)</sub>                      | Duty cycle                                             | -                                | 30                 | -      | 70                 | %    |

| ١ <sub>L</sub>                             | OSC32_IN Input leakage current                         | $V_{SS} \leq V_{IN} \leq V_{DD}$ | -                  | -      | ±1                 | μA   |

Table 21. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

All timings are derived from tests performed under ambient temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 9.

| Table 26. Low-power | mode wakeup | timings |

|---------------------|-------------|---------|

|---------------------|-------------|---------|

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 | μs   |

| + (1)                               | Wakeup from Stop mode (regulator in run mode)       | 3.6 |      |

| t <sub>WUSTOP</sub> <sup>(1)</sup>  | Wakeup from Stop mode (regulator in low power mode) | 5.4 | μs   |

| twustdby <sup>(1)</sup>             | Wakeup from Standby mode                            | 50  | μs   |

1. The wakeup times are measured from the wakeup event to the point in which the user application code reads the first instruction.

#### 5.3.8 PLL, PLL2 and PLL3 characteristics

The parameters given in Table 27 and Table 28 are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in Table 9.

| Symbol               | Parameter                      | Min <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|----------------------|--------------------------------|--------------------|--------------------|------|

| f                    | PLL input clock <sup>(2)</sup> | 3                  | 12                 | MHz  |

| f <sub>PLL_IN</sub>  | Pulse width at high level      | 30                 | -                  | ns   |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 18                 | 72                 | MHz  |

| f <sub>VCO_OUT</sub> | PLL VCO output                 | 36                 | 144                | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                  | 350                | μs   |

| Jitter               | Cycle-to-cycle jitter          | _                  | 300                | ps   |

#### Table 27. PLL characteristics

1. Based on characterization, not tested in production.

Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by f\_PLL\_OUT. 2.

| Table 28. PLL2 and PLL3 charac | teristics |

|--------------------------------|-----------|

|                                |           |

| Symbol               | Parameter                      | Min <sup>(1)</sup> | Max <sup>(1)</sup> | Unit |

|----------------------|--------------------------------|--------------------|--------------------|------|

| f                    | PLL input clock <sup>(2)</sup> | 3                  | 5                  | MHz  |

| f <sub>PLL_IN</sub>  | Pulse width at high level      | 30                 | -                  | ns   |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 40                 | 74                 | MHz  |

| f <sub>VCO_OUT</sub> | PLL VCO output                 | 80                 | 148                | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                  | 350                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                  | 400                | ps   |

1. Based on characterization, not tested in production.

Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\text{PLL\_OUT}}$ . 2

## 5.3.9 Memory characteristics

#### Flash memory

The characteristics are given at  $T_A = -40$  to 105 °C unless otherwise specified.

| Symbol             | Parameter               | Conditions                                                                             | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|----------------------------------------------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C                                                        | 40                 | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | $T_A = -40$ to +105 °C                                                                 | 20                 | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C                                                                 | 20                 | -    | 40                 | ms   |

|                    |                         | Read mode<br>f <sub>HCLK</sub> = 72 MHz with 2 wait<br>states, V <sub>DD</sub> = 3.3 V | -                  | -    | 20                 | mA   |

| I <sub>DD</sub>    | Supply current          | Write / Erase modes<br>f <sub>HCLK</sub> = 72 MHz, V <sub>DD</sub> = 3.3 V             | -                  | -    | 5                  | mA   |

|                    |                         | Power-down mode / Halt,<br>$V_{DD}$ = 3.0 to 3.6 V                                     | -                  | -    | 50                 | μA   |

| V <sub>prog</sub>  | Programming voltage     | -                                                                                      | 2                  | -    | 3.6                | V    |

| Table 29 | . Flash | memory | characteristics |

|----------|---------|--------|-----------------|

|----------|---------|--------|-----------------|

1. Guaranteed by design, not tested in production.

| Symbol           | Parameter      | Conditions                                                                              | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|-----|--------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | -   | -                  | Kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 | -   | -                  |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | -   | -                  | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 | -   | -                  |         |

#### Table 30. Flash memory endurance and data retention

1. Based on characterization, not tested in production.

2. Cycling performed over the whole temperature range.

## 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

DocID15274 Rev 10

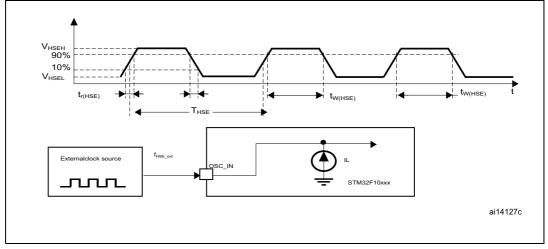

Figure 23. Recommended NRST pin protection

2. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 39. Otherwise the reset will not be taken into account by the device.

### 5.3.15 TIM timer characteristics

The parameters given in *Table 40* are guaranteed by design.

Refer to Section 5.3.12: I/O current injection characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

| Symbol                 | Parameter                                          | Conditions                    | Min    | Max                     | Unit                 |  |

|------------------------|----------------------------------------------------|-------------------------------|--------|-------------------------|----------------------|--|

| t ann                  | Timer resolution time                              | -                             | 1      | -                       | t <sub>TIMxCLK</sub> |  |

| t <sub>res(TIM)</sub>  |                                                    | f <sub>TIMxCLK</sub> = 72 MHz | 13.9   | -                       | ns                   |  |

| f <sub>EXT</sub>       | Timer external clock                               | -                             | 0      | f <sub>TIMxCLK</sub> /2 | MHz                  |  |

| 'EXT                   | frequency on CH1 to CH4                            | f <sub>TIMxCLK</sub> = 72 MHz | 0      | 36                      | MHz                  |  |

| Res <sub>TIM</sub>     | Timer resolution                                   | -                             | -      | 16                      | bit                  |  |

| +                      | 16-bit counter clock period when internal clock is | -                             | 1      | 65536                   | t <sub>TIMxCLK</sub> |  |

| <sup>t</sup> COUNTER   | selected                                           | f <sub>TIMxCLK</sub> = 72 MHz | 0.0139 | 910                     | μs                   |  |

| t                      | Maximum possible count                             | -                             | -      | 65536 × 65536           | t <sub>TIMxCLK</sub> |  |

| <sup>t</sup> MAX_COUNT |                                                    | f <sub>TIMxCLK</sub> = 72 MHz | -      | 59.6                    | s                    |  |

Table 40. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3, TIM4 and TIM5 timers.

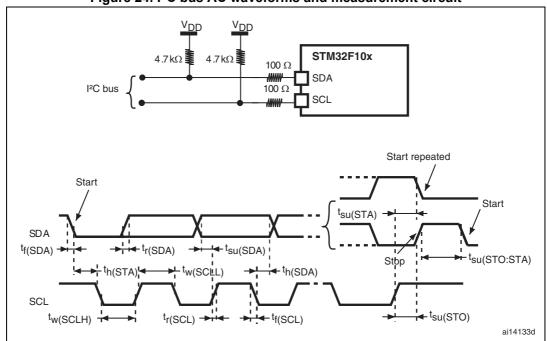

Figure 24. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

| £ (//U=)               | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801E                  |

| 300                    | 0x8028                  |

| 200                    | 0x803C                  |

| 100                    | 0x00B4                  |

| 50                     | 0x0168                  |

| 20                     | 0x0384                  |

# Table 42. SCL frequency ( $f_{PCLK1}$ = 36 MHz., $V_{DD}$ = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

| Symbol                                   | Parameter                                 | Conditions                                              |                                            | Min | Мах  | Unit |

|------------------------------------------|-------------------------------------------|---------------------------------------------------------|--------------------------------------------|-----|------|------|

| f <sub>CK</sub>                          | I <sup>2</sup> S clock frequency          | Master data: 16 bits, a<br>freq = 48 K                  | Master data: 16 bits, audio<br>freq = 48 K |     | 1.54 | MHz  |

| 1/t <sub>c(CK)</sub>                     |                                           | Slave                                                   |                                            | 0   | 6.5  |      |

| t <sub>r(CK)</sub><br>t <sub>f(CK)</sub> | I <sup>2</sup> S clock rise and fall time | capacitive load C <sub>L</sub> = 5                      | 50 pF                                      | -   | 8    |      |

| t <sub>w(CKH)</sub> <sup>(1)</sup>       | I <sup>2</sup> S clock high time          | Master f <sub>PCLK</sub> = 16 MHz,<br>audio freq = 48 K |                                            | 317 | 320  |      |

| t <sub>w(CKL)</sub> <sup>(1)</sup>       | I <sup>2</sup> S clock low time           |                                                         |                                            | 333 | 336  |      |

| t <sub>v(WS)</sub> <sup>(1)</sup>        | WS valid time                             | Master mode                                             |                                            | 3   | -    |      |

| t <sub>h(WS)</sub> <sup>(1)</sup>        | WS hold time                              | Master mode                                             | I2S2                                       | 0   | -    | ns   |

| <sup>ι</sup> h(WS) `´                    |                                           | Master mode I2S3<br>Slave mode I2S2                     | 0                                          | -   |      |      |

| + (1)                                    | W/S actus time                            |                                                         | I2S2                                       | 4   | -    |      |

| t <sub>su(WS)</sub> <sup>(1)</sup>       | WS setup time                             |                                                         | I2S3                                       | 9   | -    |      |

| t <sub>h(WS)</sub> <sup>(1)</sup>        | WS hold time                              | Slave mode                                              |                                            | 0   | -    |      |

| DuCy(SCK)                                | I2S slave input clock duty cycle          | Slave mode                                              |                                            | 30  | 70   | %    |

| + (1)                                    | Data input setup time                     | (1) Mostor receiver                                     | I2S2                                       | 8   | -    |      |

| t <sub>su(SD_MR)</sub> <sup>(1)</sup>    |                                           | Master receiver                                         | I2S3                                       | 10  | -    |      |

| t (1)                                    |                                           |                                                         | I2S2                                       | 3   | -    |      |

| t <sub>su(SD_SR)</sub> <sup>(1)</sup>    |                                           | Slave receiver                                          | I2S3                                       | 8   | -    |      |

| t <sub>h(SD_MR)</sub> <sup>(1)</sup>     |                                           | Master receiver                                         | I2S2                                       | 2   | -    |      |

| 'h(SD_MR)                                | - Data input hold time                    | Inaster receiver                                        | I2S3                                       | 4   | -    |      |

| + (1)                                    |                                           | Slave receiver                                          | I2S2                                       | 2   | -    |      |

| t <sub>h(SD_SR)</sub> <sup>(1)</sup>     |                                           | Slave receiver                                          | I2S3                                       | 4   | -    |      |

| t (1)(3)                                 | Data output valid time                    | Slave transmitter                                       | I2S2                                       | 23  | -    | ns   |

| t <sub>v(SD_ST)</sub> (1)(3)             | Data output valid time                    | (after enable edge)                                     | I2S3                                       | 33  | -    |      |

| t                                        | Data output hold time                     | Slave transmitter                                       | I2S2                                       | 29  | -    |      |

| $t_{h(SD\_ST)}$ <sup>(1)</sup>           |                                           | (after enable edge)                                     | I2S3                                       | 27  | -    |      |

| t (1)                                    | Data output valid time                    | Master transmitter                                      | I2S2                                       | -   | 5    |      |

| $t_{v(SD_MT)}$ <sup>(1)</sup>            |                                           | (after enable edge)                                     | I2S3                                       | -   | 2    |      |

| t (1)                                    | Data output hold time                     | Master transmitter                                      | I2S2                                       | 11  | -    |      |

| t <sub>h(SD_MT)</sub> <sup>(1)</sup>     | Data output hold time                     | (after enable edge)                                     | I2S3                                       | 4   | -    |      |

Table 44. I<sup>2</sup>S characteristics

1. Based on design simulation and/or characterization results, not tested in production.

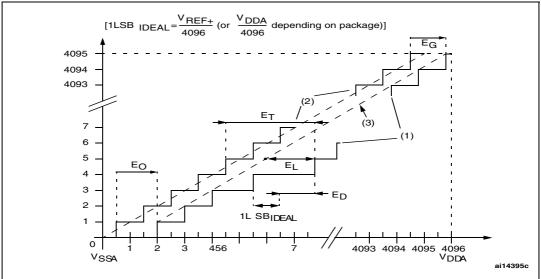

| Symbol | Parameter                    | Test conditions                                           | Тур  | Max <sup>(2)</sup> | Unit |

|--------|------------------------------|-----------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | f <sub>PCLK2</sub> = 56 MHz,                              | ±1.3 | ±2                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> = 14 MHz, R <sub>AIN</sub> < 10 kΩ,      | ±1   | ±1.5               |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 3 V to 3.6 V<br>T <sub>A</sub> = 25 °C | ±0.5 | ±1.5               | LSB  |

| ED     | Differential linearity error | Measurements made after                                   | ±0.7 | ±1                 |      |

| EL     | Integral linearity error     | ADC calibration                                           | ±0.8 | ±1.5               |      |

Table 54. ADC accuracy - limited test conditions<sup>(1)</sup>

1. ADC DC accuracy values are measured after internal calibration.

2. Based on characterization, not tested in production.

| Symbol | Parameter                    | Test conditions                                                                                                                                                                         | Тур  | Max <sup>(3)</sup> | Unit |

|--------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|------|

| ET     | Total unadjusted error       | $f_{PCLK2} = 56 \text{ MHz},$<br>$f_{ADC} = 14 \text{ MHz}, R_{AIN} < 10 \text{ k}\Omega,$<br>$V_{DDA} = 2.4 \text{ V to } 3.6 \text{ V}$<br>Measurements made after<br>ADC calibration | ±2   | ±5                 | LSB  |

| EO     | Offset error                 |                                                                                                                                                                                         | ±1.5 | ±2.5               |      |

| EG     | Gain error                   |                                                                                                                                                                                         | ±1.5 | ±3                 |      |

| ED     | Differential linearity error |                                                                                                                                                                                         | ±1   | ±2                 |      |

| EL     | Integral linearity error     |                                                                                                                                                                                         | ±1.5 | ±3                 |      |

#### Table 55. ADC accuracy<sup>(1) (2)</sup>

1. ADC DC accuracy values are measured after internal calibration.

2. Better performance could be achieved in restricted V<sub>DD</sub>, frequency and temperature ranges.

3. Based on characterization, not tested in production.

*Note:* ADC accuracy vs. negative injection current: Injecting a negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.12 does not affect the ADC accuracy.

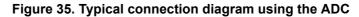

Figure 34. ADC accuracy characteristics

- Refer to Table 52 for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}\,\text{and}\,\mathsf{C}_{ADC}.$ 1.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

# 6 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

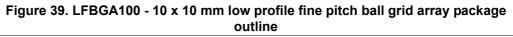

# 6.1 LFBGA100 package information

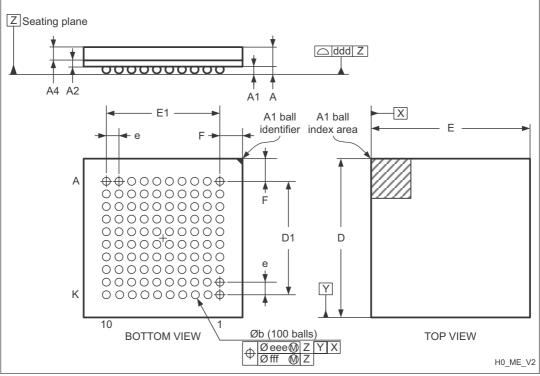

Using the values obtained in Table 61  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 46 °C/W

- $T_{Jmax}$  = 115 °C + (46 °C/W × 134 mW) = 115 °C + 6.2 °C = 121.2 °C

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 62: Ordering information scheme*).

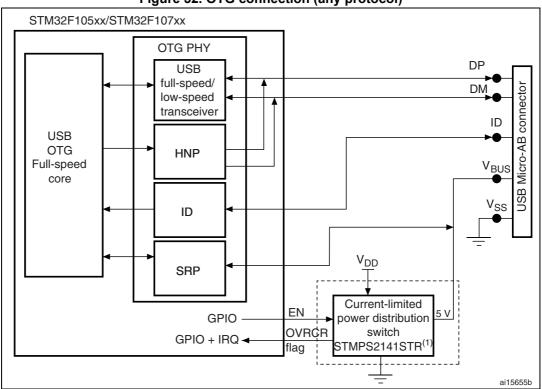

1. STMPS2141STR needed only if the application has to support bus-powered devices.

| Date | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date | Revision | Changes           Document status promoted from Preliminary data to full datasheet.           Number of DACs corrected in Table 3: STM32F105xx and           STM32F107xx family versus STM32F103xx family.           Note 5 added in Table 5: Pin definitions.           V <sub>RERINT</sub> and T <sub>Coeff</sub> added to Table 12: Embedded internal reference voltage.           Values added to Table 13: Maximum current consumption in Run mode, code with data processing running from Flash, Table 14: Maximum current consumption in Sleep mode, code running from Flash or RAM.           Typical I <sub>DD_VBAT</sub> value added in Table 16: Typical and maximum current consumptions in Slop and Standby modes.           Figure 10: Typical current consumption on VBAT with RTC on vs.           temperature at different VBAT values added.           Values modified in Table 17: Typical current consumption in Run mode, code with data processing running from Flash and Table 18: Typical current consumption in Sleep mode, code running from Flash or RAM.           fHSE_ext min modified in Table 20: High-speed external user clock characteristics.           CL1 and CL2 replaced by C in Table 22: HSE 3-25 MHz oscillator characteristics (fLSE = 32.768 kHz), notes modified and moved below the tables. Note 1 modified below Figure 16: Typical application with an 8 MHz crystal.           Conditions removed from Table 26: Low-power mode wakeup timings.           Standards modified in Section 5.3.10: EMC characteristics.           RPU and RPD modified in Table 36: I/O static characteristics.           Conditions added for V <sub>NF(NRST)</sub> |

Table 65. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11-May-2010 | 5        | Added BGA package.<br><i>Table 5: Pin definitions</i> :<br>ETH_RMII_RXD0 and ETH_RMII_RXD1 added in remap column for<br>PD9 and PD10, respectively.<br>Note added to ETH_MII_RX_DV, ETH_MII_RXD0, ETH_MII_RXD1,<br>ETH_MII_RXD2 and ETH_MII_RXD3<br>Updated <i>Table 36: I/O static characteristics on page 57</i><br>Added <i>Figure 18: Standard I/O input characteristics - CMOS port</i><br>to <i>Figure 21: 5 V tolerant I/O input characteristics - TTL port</i><br>Updated <i>Table 43: SPI characteristics on page 66</i> .<br>Updated <i>Table 43: SPI characteristics on page 69</i> .<br>Updated <i>Table 48: Ethernet DC electrical characteristics on page 72</i> .<br>Updated <i>Table 48: Ethernet DC electrical characteristics on page 72</i> .<br>Updated <i>Table 49: Dynamic characteristics: Ethernet MAC signals</i><br><i>for SMI on page 72</i> .<br>Updated <i>Table 50: Dynamic characteristics: Ethernet MAC signals</i><br><i>for RMII on page 73</i><br>Updated <i>Figure 59: USB O44TG FS + Ethernet solution on</i><br><i>page 100</i> .<br>Updated <i>Figure 60: USB OTG FS + I2S (Audio) solution on</i><br><i>page 100</i> . |

| 01-Aug-2011 | 6        | Changed SRAM size to 64 KB on all parts.<br>Updated PD0 and PD1 description in <i>Table 5: Pin definitions on</i><br>page 27<br>Updated footnotes below <i>Table 6: Voltage characteristics on page 36</i><br>and <i>Table 7: Current characteristics on page 36</i><br>Updated tw min in <i>Table 20: High-speed external user clock</i><br><i>characteristics on page 47</i><br>Updated startup time in <i>Table 23: LSE oscillator characteristics (fLSE</i><br>= 32.768 kHz) on page 50<br>Added Section 5.3.12: I/O current injection characteristics on<br>page 56<br>Updated <i>Table 36: I/O static characteristics on page 57</i><br>Add Interna code V to <i>Table 62: Ordering information scheme on</i><br>page 94                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 06-Mar-2014 | 7        | Added a "Packing" entry to <i>Table 62: Ordering information scheme</i><br>including "Blank = tray" and "TR = Tape and reel".<br>Referenced 4 Figures: <i>Figure 41, Figure 49, Figure 59</i> and<br><i>Figure 60.</i><br>Updated the "Package" line with "BGA100" in <i>Table 2:</i><br><i>STM32F105xx and STM32F107xx features and peripheral counts.</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 65. Document revision history (continued)