#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100Mbps (1)                                                                                                      |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (3)                                                                                                   |

| Voltage - I/O                      | 1.2V, 1.8V, 3.0V                                                                                                    |

| Operating Temperature              | -40°C ~ 105°C (TA)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 432-TFBGA                                                                                                           |

| Supplier Device Package            | 432-MAPBGA (13x13)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6l2evn10ab                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block<br>Mnemonic                              | Block Name                                      | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------------|-------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPDC                                           | Electrophoretic<br>Display<br>Controller        | Peripherals                      | The SPDC is a feature-rich, low power, and high-performance direct-drive, active matrix EPD controller. It is specifically designed to drive SiPix <sup>™</sup> EPD panels, supporting a wide variety of TFT backplanes.                                                                                                                                                                                                                                                                                                                                                                                                 |

| SPDIF                                          | Sony Phillips<br>Digital Interface              | Multimedia<br>Peripherals        | A standard audio file transfer format, developed jointly by the Sony and Phillips corporations. Has Transmitter and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SSI-1<br>SSI-2<br>SSI-3                        | I2S/SSI/AC97<br>Interface                       | Connectivity<br>Peripherals      | The SSI is a full-duplex synchronous interface, which is used on the AP to provide connectivity with off-chip audio peripherals. The SSI supports a wide variety of protocols (SSI normal, SSI network, I2S, and AC-97), bit depths (up to 24 bits per word), and clock / frame sync options. The SSI has two pairs of 8x24 FIFOs and hardware support for an external DMA controller in order to minimize its impact on system performance. The second pair of FIFOs provides hardware interleaving of a second audio stream that reduces CPU overhead in use cases where two time slots are being used simultaneously. |

| TEMPMON                                        | Temperature<br>Monitor                          | System<br>Control<br>Peripherals | The temperature monitor/sensor IP, for detecting high temperature conditions.<br>The Temperature sensor IP for detecting die temperature. The temperature<br>read out does not reflect case or ambient temperature, but the proximity of the<br>temperature sensor location on the die. Temperature distribution may not be<br>uniformly distributed, therefore the read out value may not be the reflection of<br>the temperature value of the entire die.                                                                                                                                                              |

| TZASC                                          | Trust-Zone<br>Address Space<br>Controller       | Security                         | The TZASC (TZC-380 by ARM) provides security address region control functions required for intended application. It is used on the path to the DRAM controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| UART-1<br>UART-2<br>UART-3<br>UART-4<br>UART-5 | UART Interface                                  | Connectivity<br>Peripherals      | <ul> <li>Each of the UARTv2 modules support the following serial data transmit/receive protocols and configurations:</li> <li>7- or 8-bit data words, 1 or 2 stop bits, programmable parity (even, odd or none)</li> <li>Programmable baud rates up to 4 MHz. This is a higher max baud rate relative to the 1.875 MHz, which is stated by the TIA/EIA-232-F standard and the i.MX31 UART modules.</li> <li>32-byte FIFO on Tx and 32 half-word FIFO on Rx supporting auto-baud</li> <li>IrDA 1.0 support (up to SIR speed of 115200 bps)</li> <li>Option to operate as 8-pins full UART, DCE, or DTE</li> </ul>         |

| USBOH2A                                        | 2x USB 2.0 High<br>Speed OTG and<br>1x HS Hosts | Connectivity<br>Peripherals      | USBO2H contains:<br>• One Two high-speed OTG module with integrated HS USB PHY<br>• One identical high-speed Host modules connected to HSIC USB ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

### **Modules List**

| Block<br>Mnemonic                        | Block Name                                                                                | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| uSDHC-1<br>uSDHC-2<br>uSDHC-2<br>uSDHC-4 | SD/MMC and<br>SDXC<br>Enhanced<br>Multi-Media Card<br>/ Secure Digital<br>Host Controller | Connectivity<br>Peripherals | <ul> <li>i.MX 6SoloLite specific SoC characteristics:</li> <li>All four MMC/SD/SDIO controller IPs are identical and are based on the uSDHC IP. They are:</li> <li>Fully compliant with MMC command/response sets and Physical Layer as defined in the Multimedia Card System Specification, v4.2/4.3/4.4 including high-capacity (size &gt; 2 GB) cards HC MMC. HW reset as specified for eMMC cards is supported at ports #3 and #4 only.</li> <li>Fully compliant with SD command/response sets and Physical Layer as defined in the SD Memory Card Specifications, v3.0 including high-capacity SDHC cards up to 32 GB.</li> <li>Fully compliant with SDIO command/response sets and interrupt/read-wait mode as defined in the SDIO card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specification, Part E1, v1.10</li> <li>Fully compliant with SD Card Specifications for SD and SDIO cards up to UHS-I SDR104 mode (104 MB/s max)</li> <li>1-bit or 4-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)</li> <li>However, the SoC level integration and I/O muxing logic restrict the functionality to the following:</li> <li>Instances #1 and #2 are primarily intended to serve as external slots or interfaces to on-board SDIO devices. These ports are equipped with "Card detection" and "Write Protection" pads and do not support HW reset</li> <li>All ports can work with 1.8 V and 3.3 V cards. There are two completely independent I/O power domains for Ports #1 and #2 in four bit configuration (SD interface). Port #3 is placed in his own independent power domain and port #4 shares power domain with some other interfaces.</li> </ul> |

| WDOG-1                                   | Watchdog                                                                                  | Timer<br>Peripherals        | The Watchdog Timer supports two comparison points during each counting period. Each of the comparison points is configurable to evoke an interrupt to the ARM core, and a second point evokes an external event on the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WDOG-2<br>(TZ)                           | Watchdog<br>(TrustZone)                                                                   | Timer<br>Peripherals        | The TrustZone Watchdog (TZ WDOG) timer module protects against<br>TrustZone starvation by providing a method of escaping normal mode and<br>forcing a switch to the TZ mode. TZ starvation is a situation where the normal<br>OS prevents switching to the TZ mode. Such situation is undesirable as it can<br>compromise the system's security. Once the TZ WDOG module is activated,<br>it must be serviced by TZ software on a periodic basis. If servicing does not<br>take place, the timer times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode. If it is still not served,<br>the TZ WDOG asserts a security violation signal to the CSU. The TZ WDOG<br>module cannot be programmed or deactivated by a normal mode Software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| XTALOSC                                  | Crystal Oscillator<br>I/F                                                                 | Clocking                    | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Rating                                           | Board                   | Symbol              | No Lid | Unit |

|--------------------------------------------------|-------------------------|---------------------|--------|------|

| Junction to Ambient <sup>1</sup> (at 200 ft/min) | Single layer board (1s) | R <sub>0JMA</sub>   | 40     | °C/W |

|                                                  | Four layer board (2s2p) | R <sub>0JMA</sub>   | 24     | °C/W |

| Junction to Board <sup>2</sup>                   | —                       | $R_{\theta JB}$     | 14     | °C/W |

| Junction to Case <sup>3</sup> (Top)              | —                       | R <sub>0JCtop</sub> | 9      | °C/W |

| Junction to Package Top <sup>4</sup>             | Natural Convection      | $\Psi_{JT}$         | 2      | °C/W |

### Table 8. Package Thermal Resistance Data (continued)

<sup>1</sup> Junction-to-Ambient Thermal Resistance was determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>2</sup> Junction-to-Board Thermal Resistance was determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

<sup>3</sup> Junction-to-Case at the top of the package was determined by using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

<sup>4</sup> Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

Table 9 provides the operating ranges of the i.MX 6SoloLite processor.

| Parameter<br>Description      | Symbol                               | Min                  | Тур | Max <sup>1</sup> | Unit | Comment                                                                                                                             |

|-------------------------------|--------------------------------------|----------------------|-----|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| Run mode: LDO<br>enabled      | VDD_ARM_IN                           | 1.375 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 1.250V minimum for operation up to 996MHz.                                                                        |

|                               |                                      | 1.275 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 1.150V minimum for operation up to 792MHz                                                                         |

|                               |                                      | 1.075 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 0.95V minimum for operation up to 396MHz                                                                          |

|                               |                                      | 1.075 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 0.950V minimum for operation up to 192MHz                                                                         |

|                               |                                      | 1.050 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 0.9250V minimum for operation up to 24MHz                                                                         |

|                               | VDD_SOC_IN <sup>3</sup><br>VDD_PU_IN | 1.275 <sup>2,4</sup> |     | 1.5              | V    | VDD_SOC and VDD_PU LDO outputs<br>(VDD_SOC_CAP and VDD_PU_CAP)<br>require 1.15 V minimum.                                           |

| Run mode: LDO                 | VDD_ARM_IN                           | 1.250                |     | 1.3              | V    | LDO bypassed for operation up to 996 MHz.                                                                                           |

| bypassed                      |                                      | 1.150                |     | 1.3              | V    | LDO bypassed for operation up to 792 MHz.                                                                                           |

|                               |                                      | 0.950                |     | 1.3              | V    | LDO bypassed for operation up to 396 MHz.                                                                                           |

|                               |                                      | 0.950                |     | 1.3              | V    | LDO bypassed for operation up to 192MHz                                                                                             |

|                               |                                      | 0.925                |     | 1.3              | V    | LDO bypassed for operation up to 24MHz                                                                                              |

|                               | VDD_SOC_IN <sup>3</sup><br>VDD_PU_IN | 1.15 <sup>4</sup>    |     | 1.3              | V    |                                                                                                                                     |

| Standby/DSM Mode              | VDD_ARM_IN                           | 0.9                  |     | 1.3              | V    | See Table 12, "Stop Mode Current and                                                                                                |

|                               | VDD_SOC_IN<br>VDD_PU_IN              | 0.9                  |     | 1.3              | V    | Power Consumption," on page 24.                                                                                                     |

| VDDHIGH internal<br>Regulator | VDD_HIGH_IN <sup>5</sup>             | 2.8                  |     | 3.3              | V    | Must match the range of voltges that the rechargeable backup battery supports.                                                      |

| Backup battery supply range   | VDD_SNVS_IN <sup>5</sup>             | 2.8                  |     | 3.3              | V    | Should be supplied from the same supply as VDDHIGH_IN if the system does not require keeping real time and other data on OFF state. |

| USB supply voltages           | USB_OTG1_VBUS<br>USB_OTG2_VBUS       | 4.4                  |     | 5.25             | V    |                                                                                                                                     |

| DDR I/O supply                | NVCC_DRAM                            | 1.14                 | 1.2 | 1.3              | V    | LPDDR2                                                                                                                              |

|                               |                                      | 1.425                | 1.5 | 1.575            | V    | DDR3                                                                                                                                |

|                               | NVCC_DRAM_2P5                        | 2.5                  | 2.5 | 2.75             | V    |                                                                                                                                     |

### Table 9. Operating Ranges

- <sup>3</sup> Recommended nominal frequency 32.768 kHz.

- <sup>4</sup> External oscillator or a fundamental frequency crystal with internal oscillator amplifier.

The typical values shown in Table 10 are required for use with Freescale BSPs to ensure precise time keeping and USB operation. For RTC\_XTAL operation, two clock sources are available:

- On-chip 40 kHz ring oscillator: This clock source has the following characteristics:

- Approximately 25 µA more Idd than crystal oscillator

- Approximately  $\pm 50\%$  tolerance

- No external component required

- Starts up quicker than 32 kHz crystal oscillator

- External crystal oscillator with on-chip support circuit

- At power up, ring oscillator is utilized. After crystal oscillator is stable, the clock circuit switches over to the crystal oscillator automatically.

- Higher accuracy than ring oscillator

- If no external crystal is present, then the ring oscillator is utilized

The decision of choosing a clock source should be taken based on real-time clock use and precision timeout.

## 4.1.5 Maximal Supply Currents

The Power Virus numbers shown in Table 11 represent a use case designed specifically to show the maximum current consumption possible. All cores are running at the defined maximum frequency and are limited to L1 cache accesses only to ensure no pipeline stalls. Although a valid condition, it would have a very limited practical use case, if at all, and be limited to an extremely low duty cycle unless the intention was to specifically show the worst case power consumption.

The MMPF0100xxxx, Freescale's power management IC targeted for the i.MX 6x family, supports the Power Virus mode operating at 1% duty cycle. Higher duty cycles are allowed, but a robust thermal design is required for the increased system power dissipation.

See the i.MX 6SoloLite Power Consumption Measurement Application Note for more details on typical power consumption under various use case definitions.

| Power Line  | Conditions                                     | Max Current      | Unit |

|-------------|------------------------------------------------|------------------|------|

| VDD_ARM_IN  | 1 GHz ARM clock based on Power Virus operation | 1100             | mA   |

| VDD_SOC_IN  | 1 GHz ARM clock                                | 650              | mA   |

| VDD_PU_IN   | 1 GHz ARM clock                                | 150              | mA   |

| VDD_HIGH_IN | —                                              | 30 <sup>1</sup>  | mA   |

| VDD_SNVS_IN | —                                              | 250 <sup>2</sup> | μA   |

| Parameter                                                     | Symbol           | Test Condition                 | Min | Тур | Мах | Unit |

|---------------------------------------------------------------|------------------|--------------------------------|-----|-----|-----|------|

| Single output slew rate, measured between Vol(ac) and Voh(ac) | tsr              | Driver impedance = $34 \Omega$ | 2.5 | _   | 5   | V/ns |

| Skew between pad rise/fall asymmetry + skew caused by SSN     | t <sub>SKD</sub> | clk = 400 MHz                  | —   | _   | 0.1 | ns   |

Table 28. DDR I/O DDR3 Mode AC Parameters<sup>1</sup> (continued)

<sup>1</sup> Note that the JEDEC JESD79\_3C specification supersedes any specification in this document.

<sup>2</sup> Vid(ac) specifies the input differential voltage |Vtr-Vcp| required for switching, where Vtr is the "true" input signal and Vcp is the "complementary" input signal. The Minimum value is equal to Vih(ac) – Vil(ac).

<sup>3</sup> The typical value of Vix(ac) is expected to be about 0.5 \* OVDD. and Vix(ac) is expected to track variation of OVDD. Vix(ac) indicates the voltage at which differential input signal must cross.

## 4.8 Output Buffer Impedance Parameters

This section defines the I/O impedance parameters of the i.MX 6SoloLite processor for the following I/O types:

- Dual Voltage General Purpose I/O cell set (DVGPIO)

- Single Voltage General Purpose I/O cell set (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2, and DDR3 modes

### NOTE

GPIO and DDR I/O output driver impedance is measured with "long" transmission line of impedance Ztl attached to I/O pad and incident wave launched into transmission line. Rpu/Rpd and Ztl form a voltage divider that defines specific voltage of incident wave relative to OVDD. Output driver impedance is calculated from this voltage divider (see Figure 7).

## 4.9.4 DDR SDRAM Specific Parameters (DDR3 and LPDDR2)

### 4.9.4.1 DDR3 Parameters

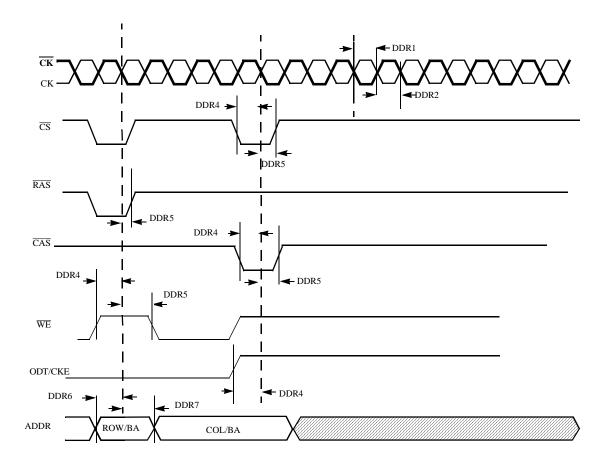

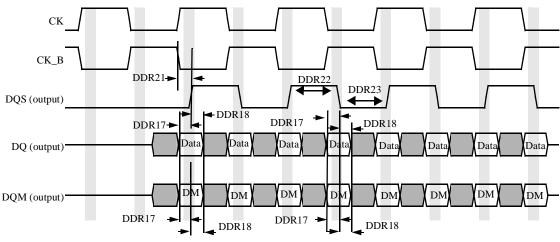

Figure 22 shows the DDR3 basic timing diagram. The timing parameters for this diagram appear in Table 39.

Figure 22. DDR3 Command and Address Timing Diagram

| ID   | Parameter                             | Symbol | CK = 40        | Unit |     |

|------|---------------------------------------|--------|----------------|------|-----|

|      | Falameter                             | Symbol | Symbol Min Max |      |     |

| DDR1 | CK clock high-level width             | tсн    | 0.47           | 0.53 | tск |

| DDR2 | CK clock low-level width              | tCL    | 0.47           | 0.53 | tск |

| DDR4 | CS, RAS, CAS, CKE, WE, ODT setup time | tis    | 800            | —    | ps  |

| DDR5 | CS, RAS, CAS, CKE, WE, ODT hold time  | tıн    | 580            | —    | ps  |

### Table 39. DDR3 Timing Parameter Table

| ID   | Parameter                 | Symbol | CK = 40 | Unit |         |

|------|---------------------------|--------|---------|------|---------|

|      |                           |        | Min     | Мах  | - Cilit |

| DDR6 | Address output setup time | tis    | 800     | _    | ps      |

| DDR7 | Address output hold time  | tıн    | 580     | _    | ps      |

Table 39. DDR3 Timing Parameter Table (continued)

<sup>1</sup> All measurements are in reference to Vref level.

$^2\,$  Measurements were done using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

Figure 23 shows the DDR3 write timing diagram. The timing parameters for this diagram appear in Table 40.

Figure 23. DDR3 Write Cycle

### Table 40. DDR3 Write Cycle

| ID    | Parameter                                                 | Symbol | CK = 400MHz |       | Unit |

|-------|-----------------------------------------------------------|--------|-------------|-------|------|

|       |                                                           |        | Min         | Max   | Unit |

| DDR17 | DQ and DQM setup time to DQS (differential strobe)        | tDS    | 420         | —     | ps   |

| DDR18 | DQ and DQM hold time to DQS (differential strobe)         | tDH    | 345         | _     | ps   |

| DDR21 | DQS latching rising transitions to associated clock edges | tDQSS  | -0.25       | +0.25 | tCK  |

| DDR22 | DQS high level width                                      | tDQSH  | 0.45        | 0.55  | tCK  |

| DDR23 | DQS low level width                                       | tDQSL  | 0.45        | 0.55  | tCK  |

<sup>1</sup> To receive the reported setup and hold values, write calibration should be performed in order to locate the DQS in the middle of DQ window.

<sup>2</sup> All measurements are in reference to Vref level.

$^3\,$  Measurements were taken using balanced load and 25  $\Omega$  resistor from outputs to VDD\_REF.

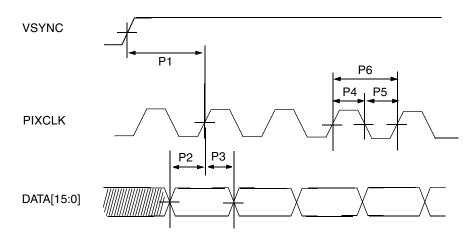

| ID | Parameter                 | Symbol | Min. | Max.   | Units |

|----|---------------------------|--------|------|--------|-------|

| P1 | CSI VSYNC to HSYNC time   | tV2H   | 67.5 | —      | ns    |

| P2 | CSI HSYNC setup time      | tHsu   | 2    | _      | ns    |

| P3 | CSI DATA setup time       | tDsu   | 2.5  | _      | ns    |

| P4 | CSI DATA hold time        | tDh    | 1.2  | —      | ns    |

| P5 | CSI pixel clock high time | tCLKh  | 10   | —      | ns    |

| P6 | CSI pixel clock low time  | tCLKI  | 10   | —      | ns    |

| P7 | CSI pixel clock frequency | fCLK   | —    | 66±10% | MHz   |

Table 45. CSI Gated Clock Mode Timing Parameters

## 4.10.2.0.2 Ungated Clock Mode Timing

Figure 30 shows the ungated clock mode timings of CSI, and Table 46 describes the timing parameters (P1–P6) that are shown in the figure. In ungated mode the VSYNC and PIXCLK signals are used, and the HSYNC signal is ignored.

Figure 30. CSI Ungated Clock Mode—Sensor Data at Falling Edge, Latch Data at Rising Edge

| ID | Parameter                     | Symbol | Min. | Max.   | Units |

|----|-------------------------------|--------|------|--------|-------|

| P1 | CSI VSYNC to pixel clock time | tVSYNC | 67.5 | —      | ns    |

| P2 | CSI DATA setup time           | tDsu   | 2.5  | —      | ns    |

| P3 | CSI DATA hold time            | tDh    | 1.2  | —      | ns    |

| P4 | CSI pixel clock high time     | tCLKh  | 10   | _      | ns    |

| P5 | CSI pixel clock low time      | tCLKI  | 10   | —      | ns    |

| P6 | CSI pixel clock frequency     | fCLK   | _    | 66±10% | MHz   |

| ID                                                                          | Parameter               | Symbols          | Min                  | Мах | Unit |  |  |

|-----------------------------------------------------------------------------|-------------------------|------------------|----------------------|-----|------|--|--|

| uSDHC Input/Card Outputs CMD, DAT in SDR104 (Reference to CLK) <sup>2</sup> |                         |                  |                      |     |      |  |  |

| SD8                                                                         | Card Output Data Window | t <sub>ODW</sub> | 0.5*t <sub>CLK</sub> | _   | ns   |  |  |

<sup>1</sup> If using KEY\_COL1, KEY\_ROW1, KEY\_COL2 and KEY\_ROW2 for USDHC3\_DAT4 - USDHC3\_DAT7, please note that the timing is differnt. t<sub>od</sub> min is -1.1 and t<sub>od</sub> max is 1.5

<sup>2</sup>Data window in SDR100 mode is variable.

## 4.10.5 FEC AC Timing Parameters

This section describes the electrical information of the Fast Ethernet Controller (FEC) module. The FEC is designed to support both 10 and 100 Mbps Ethernet/IEEE 802.3 networks. An external transceiver interface and transceiver function are required to complete the interface to the media. The FEC supports the 10/100 Mbps MII (18 pins in total) and the 10 Mbps (only 7-wire interface, which uses 7 of the MII pins), for connection to an external Ethernet transceiver. For the pin list of MII and 7-wire, see the i.MX 6SoloLite Reference Manual.

This section describes the AC timing specifications of the FEC. The MII signals are compatible with transceivers operating at a voltage of 3.3 V.

## 4.10.5.1 MII Receive Signal Timing

The MII receive signal timing involves the FEC\_RX\_DATA3,2,1,0, FEC\_RX\_DV, FEC\_RX\_ER, and FEC\_RX\_CLK signals. The receiver functions correctly up to a FEC\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement but the processor clock frequency must exceed twice the FEC\_RX\_CLK frequency. Table 52 lists the MII receive channel signal timing parameters and Figure 36 shows MII receive signal timings.

| No. | Characteristics <sup>1 2</sup>                               | Min | Max | Unit              |

|-----|--------------------------------------------------------------|-----|-----|-------------------|

| M1  | FEC_RX_DATA3,2,1,0, FEC_RX_DV, FEC_RX_ER to FEC_RX_CLK setup | 5   | _   | ns                |

| M2  | FEC_RX_CLK to FEC_RX_DATA3,2,1,0, FEC_RX_DV, FEC_RX_ER hold  | 5   | _   | ns                |

| МЗ  | FEC_RX_CLK pulse width high                                  | 35% | 65% | FEC_RX_CLK period |

| M4  | FEC_RX_CLK pulse width low                                   | 35% | 65% | FEC_RX_CLK period |

<sup>1</sup> FEC\_RX\_DV, FEC\_RX\_CLK, and FEC\_RXD0 have same timing in 10 Mbps 7-wire interface mode.

<sup>2</sup> Test conditions: 25pF on each output signal.

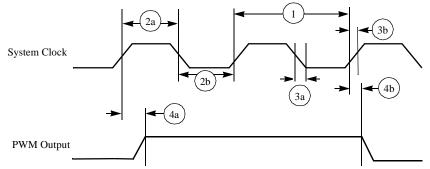

Figure 42 depicts the timing of the PWM, and Table 58 lists the PWM timing parameters.

Figure 42. PWM Timing

Table 58. PWM Output Timing Parameters

| Reference Number | Parameter                         | Min   | Мах     | Unit |

|------------------|-----------------------------------|-------|---------|------|

| 1                | System CLK frequency <sup>1</sup> | 0     | ipg_clk | MHz  |

| 2a               | Clock high time                   | 12.29 | _       | ns   |

| 2b               | Clock low time                    | 9.91  | _       | ns   |

<sup>1</sup> CL of PWMO = 30 pF

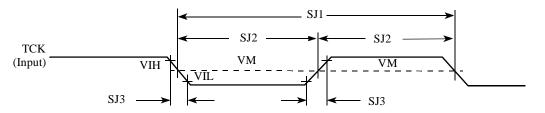

## 4.10.8 SCAN JTAG Controller (SJC) Timing Parameters

Figure 43 depicts the SJC test clock input timing. Figure 44 depicts the SJC boundary scan timing. Figure 45 depicts the SJC test access port. Signal parameters are listed in Table 59.

Figure 43. Test Clock Input Timing Diagram

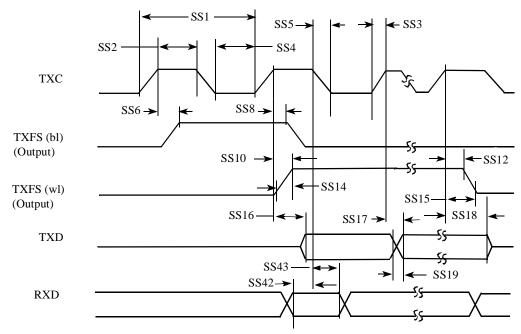

## 4.10.10.1 SSI Transmitter Timing with Internal Clock

Figure 49 depicts the SSI transmitter internal clock timing and Table 62 lists the timing parameters for the SSI transmitter internal clock.

Note: SRXD input in synchronous mode only

### Figure 49. SSI Transmitter Internal Clock Timing Diagram

| ID   | Parameter                                      | Min  | Мах  | Unit |  |  |  |

|------|------------------------------------------------|------|------|------|--|--|--|

|      | Internal Clock Operation                       |      |      |      |  |  |  |

| SS1  | (Tx/Rx) CK clock period                        | 81.4 | _    | ns   |  |  |  |

| SS2  | (Tx/Rx) CK clock high period                   | 36.0 | _    | ns   |  |  |  |

| SS4  | (Tx/Rx) CK clock low period                    | 36.0 | _    | ns   |  |  |  |

| SS6  | (Tx) CK high to FS (bl) high                   | —    | 15.0 | ns   |  |  |  |

| SS8  | (Tx) CK high to FS (bl) low                    | —    | 15.0 | ns   |  |  |  |

| SS10 | (Tx) CK high to FS (wl) high                   | —    | 15.0 | ns   |  |  |  |

| SS12 | (Tx) CK high to FS (wl) low                    | —    | 15.0 | ns   |  |  |  |

| SS14 | (Tx/Rx) Internal FS rise time                  | —    | 6.0  | ns   |  |  |  |

| SS15 | (Tx/Rx) Internal FS fall time                  | —    | 6.0  | ns   |  |  |  |

| SS16 | (Tx) CK high to STXD valid from high impedance | —    | 15.0 | ns   |  |  |  |

| SS17 | (Tx) CK high to STXD high/low                  | —    | 15.0 | ns   |  |  |  |

| SS18 | (Tx) CK high to STXD high impedance            | —    | 15.0 | ns   |  |  |  |

### Table 62. SSI Transmitter Timing with Internal Clock

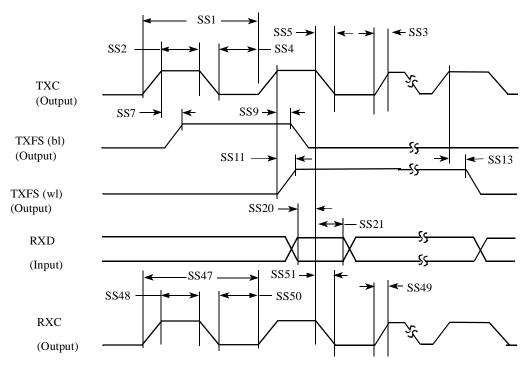

## 4.10.10.2 SSI Receiver Timing with Internal Clock

Figure 50 depicts the SSI receiver internal clock timing and Table 63 lists the timing parameters for the receiver timing with the internal clock.

Figure 50. SSI Receiver Internal Clock Timing Diagram

| ID                           | Parameter                          | Min  | Мах  | Unit |  |  |  |

|------------------------------|------------------------------------|------|------|------|--|--|--|

|                              | Internal Clock Operation           |      |      |      |  |  |  |

| SS1                          | (Tx/Rx) CK clock period            | 81.4 |      | ns   |  |  |  |

| SS2                          | (Tx/Rx) CK clock high period       | 36.0 | _    | ns   |  |  |  |

| SS3                          | (Tx/Rx) CK clock rise time         | _    | 6.0  | ns   |  |  |  |

| SS4                          | (Tx/Rx) CK clock low period        | 36.0 | _    | ns   |  |  |  |

| SS5                          | (Tx/Rx) CK clock fall time         | _    | 6.0  | ns   |  |  |  |

| SS7                          | (Rx) CK high to FS (bl) high       | _    | 15.0 | ns   |  |  |  |

| SS9                          | (Rx) CK high to FS (bl) low        | _    | 15.0 | ns   |  |  |  |

| SS11                         | (Rx) CK high to FS (wl) high       | _    | 15.0 | ns   |  |  |  |

| SS13                         | (Rx) CK high to FS (wl) low        | _    | 15.0 | ns   |  |  |  |

| SS20                         | SRXD setup time before (Rx) CK low | 10.0 |      | ns   |  |  |  |

| SS21                         | SRXD hold time after (Rx) CK low   | 0.0  |      | ns   |  |  |  |

| Oversampling Clock Operation |                                    |      |      |      |  |  |  |

Table 63. SSI Receiver Timing with Internal Clock

| ID   | Parameter                            | Min  | Мах  | Unit |  |  |  |

|------|--------------------------------------|------|------|------|--|--|--|

| SS39 | (Tx) CK high to STXD high impedance  | —    | 15.0 | ns   |  |  |  |

|      | Synchronous External Clock Operation |      |      |      |  |  |  |

| SS44 | SRXD setup before (Tx) CK falling    | 10.0 | —    | ns   |  |  |  |

| SS45 | SRXD hold after (Tx) CK falling      | 2.0  | —    | ns   |  |  |  |

| SS46 | SRXD rise/fall time                  | —    | 6.0  | ns   |  |  |  |

Table 64. SSI Transmitter Timing with External Clock (continued)

### NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms WL and BL refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

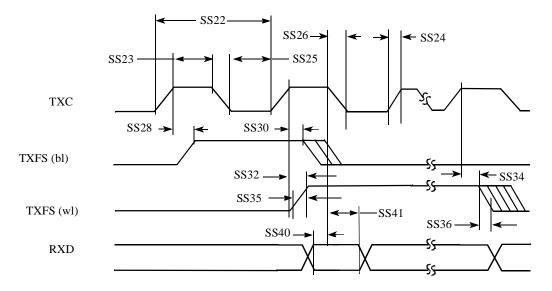

## 4.10.10.4 SSI Receiver Timing with External Clock

Figure 52 depicts the SSI receiver external clock timing and Table 65 lists the timing parameters for the receiver timing with the external clock.

### Figure 52. SSI Receiver External Clock Timing Diagram

| ID   | Parameter                          | Min  | Мах  | Unit |

|------|------------------------------------|------|------|------|

|      | External Clock Operat              | ion  |      |      |

| SS22 | (Tx/Rx) CK clock period            | 81.4 | —    | ns   |

| SS23 | (Tx/Rx) CK clock high period       | 36   | —    | ns   |

| SS24 | (Tx/Rx) CK clock rise time         | _    | 6.0  | ns   |

| SS25 | (Tx/Rx) CK clock low period        | 36   | —    | ns   |

| SS26 | (Tx/Rx) CK clock fall time         | _    | 6.0  | ns   |

| SS28 | (Rx) CK high to FS (bl) high       | -10  | 15.0 | ns   |

| SS30 | (Rx) CK high to FS (bl) low        | 10   | —    | ns   |

| SS32 | (Rx) CK high to FS (wl) high       | -10  | 15.0 | ns   |

| SS34 | (Rx) CK high to FS (wl) low        | 10   | —    | ns   |

| SS35 | (Tx/Rx) External FS rise time      | _    | 6.0  | ns   |

| SS36 | (Tx/Rx) External FS fall time      | _    | 6.0  | ns   |

| SS40 | SRXD setup time before (Rx) CK low | 10   | —    | ns   |

| SS41 | SRXD hold time after (Rx) CK low   | 2    | —    | ns   |

### Table 65. SSI Receiver Timing with External Clock

### Package Information and Contact Assignments

|            |      |             |           |                                    | Out of Reset Co  | ondition <sup>1</sup> |           |

|------------|------|-------------|-----------|------------------------------------|------------------|-----------------------|-----------|

| Ball Name  | Ball | Power Group | Ball Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function | Input/Output          | Value     |

| AUD_TXC    | H20  | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[3]    | Input                 | Keeper    |

| AUD_TXD    | J22  | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[5]    | Input                 | Keeper    |

| AUD_TXFS   | H21  | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[4]    | Input                 | Keeper    |

| BOOT_MODE0 | AC15 | VDD_SNVS_IN | GPIO      | ALT0                               | src_BOOT_MODE[0] | Input                 | Keeper    |

| BOOT_MODE1 | AB15 | VDD_SNVS_IN | GPIO      | ALT0                               | src_BOOT_MODE[1] | Input                 | Keeper    |

| CLK1_N     | AD23 | VDDHIGH_CAP |           |                                    | CLK1_N           | _                     |           |

| CLK1_P     | AC23 | VDDHIGH_CAP |           |                                    | CLK1_P           | _                     |           |

| DRAM_A0    | U4   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[0]   | Output                | 0         |

| DRAM_A1    | U5   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[1]   | Output                | 0         |

| DRAM_A10   | J2   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[10]  | Output                | 0         |

| DRAM_A11   | T2   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[11]  | Output                | 0         |

| DRAM_A12   | U2   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[12]  | Output                | 0         |

| DRAM_A13   | H5   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[13]  | Output                | 0         |

| DRAM_A14   | R2   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[14]  | Output                | 0         |

| DRAM_A15   | K2   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[15]  | Output                | 0         |

| DRAM_A2    | Т3   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[2]   | Output                | 0         |

| DRAM_A3    | T4   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[3]   | Output                | 0         |

| DRAM_A4    | N4   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[4]   | Output                | 0         |

| DRAM_A5    | М3   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[5]   | Output                | 0         |

| DRAM_A6    | M4   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[6]   | Output                | 0         |

| DRAM_A7    | H4   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[7]   | Output                | 0         |

| DRAM_A8    | J3   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[8]   | Output                | 0         |

| DRAM_A9    | J4   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_A[9]   | Output                | 0         |

| DRAM_CAS_B | P1   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_CAS    | Output                | 0         |

| DRAM_CS0_B | N2   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_CS[0]  | Output                | 0         |

| DRAM_CS1_B | L2   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_CS[1]  | Output                | 0         |

| DRAM_D0    | AC2  | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_D[0]   | Input                 | PU (100K) |

| DRAM_D1    | AC1  | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_D[1]   | Input                 | PU (100K) |

| DRAM_D10   | E3   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_D[10]  | Input                 | PU (100K) |

| DRAM_D11   | D3   | NVCC_DRAM   | DDR       | ALT0                               | mmdc_DRAM_D[11]  | Input                 | PU (100K) |

Table 80. 13 x 13 mm Functional Contact Assignments (continued)

### Package Information and Contact Assignments

|                    |      |             |           |                                    | Out of Reset Co  | ondition <sup>1</sup> |           |

|--------------------|------|-------------|-----------|------------------------------------|------------------|-----------------------|-----------|

| Ball Name          | Ball | Power Group | Ball Type | Default<br>Mode<br>(Reset<br>Mode) | Default Function | Input/Output          | Value     |

| EPDC_PWRSTAT       | E10  | NVCC_GPIO   | GPIO      | ALT5                               | gpio2_GPIO[13]   | Input                 | Keeper    |

| EPDC_PWRWAKE<br>UP | D10  | NVCC_GPIO   | GPIO      | ALT5                               | gpio2_GPIO[14]   | Input                 | Keeper    |

| EPDC_SDCE0         | C11  | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[27]   | Input                 | Keeper    |

| EPDC_SDCE1         | A10  | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[28]   | Input                 | Keeper    |

| EPDC_SDCE2         | B9   | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[29]   | Input                 | Keeper    |

| EPDC_SDCE3         | A9   | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[30]   | Input                 | Keeper    |

| EPDC_SDCLK         | B10  | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[23]   | Input                 | Keeper    |

| EPDC_SDLE          | B8   | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[24]   | Input                 | Keeper    |

| EPDC_SDOE          | E7   | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[25]   | Input                 | Keeper    |

| EPDC_SDSHR         | F7   | NVCC_GPIO   | GPIO      | ALT5                               | gpio1_GPIO[26]   | Input                 | Keeper    |

| EPDC_VCOM0         | C7   | NVCC_GPIO   | GPIO      | ALT5                               | gpio2_GPIO[3]    | Input                 | Keeper    |

| EPDC_VCOM1         | D7   | NVCC_GPIO   | GPIO      | ALT5                               | gpio2_GPIO[4]    | Input                 | Keeper    |

| FEC_CRS_DV         | AC9  | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[25]   | Input                 | Keeper    |

| FEC_MDC            | AA7  | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[23]   | Input                 | Keeper    |

| FEC_MDIO           | AB7  | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[20]   | Input                 | Keeper    |

| FEC_REF_CLK        | W10  | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[26]   | Input                 | Keeper    |

| FEC_RX_ER          | AD9  | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[19]   | Input                 | Keeper    |

| FEC_RXD0           | AA10 | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[17]   | Input                 | Keeper    |

| FEC_RXD1           | AC10 | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[18]   | Input                 | Keeper    |

| FEC_TX_CLK         | AC8  | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[21]   | Input                 | Keeper    |

| FEC_TX_EN          | AD10 | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[22]   | Input                 | Keeper    |

| FEC_TXD0           | Y10  | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[24]   | Input                 | Keeper    |

| FEC_TXD1           | W11  | NVCC_GPIO   | GPIO      | ALT5                               | gpio4_GPIO[16]   | Input                 | Keeper    |

| HSIC_DAT           | AA6  | NVCC_GPIO   | DDR       |                                    | usb_H_DATA       | Input                 | PD (100K) |

| HSIC_STROBE        | AB6  | NVCC_GPIO   | DDR       |                                    | usb_H_STROBE     | Input                 | PD (100K) |

| I2C1_SCL           | AC13 | NVCC_GPIO   | GPIO      | ALT5                               | gpio3_GPIO[12]   | Input                 | Keeper    |

| I2C1_SDA           | AD13 | NVCC_GPIO   | GPIO      | ALT5                               | gpio3_GPIO[13]   | Input                 | Keeper    |

| I2C2_SCL           | E18  | NVCC_GPIO   | GPIO      | ALT5                               | gpio3_GPIO[14]   | Input                 | Keeper    |

| I2C2_SDA           | D18  | NVCC_GPIO   | GPIO      | ALT5                               | gpio3_GPIO[15]   | Input                 | Keeper    |

Table 80. 13 x 13 mm Functional Contact Assignments (continued)

### Package Information and Contact Assignments

| 8           | 6           | 10             | 1             | 12            | 13          | 14           |

|-------------|-------------|----------------|---------------|---------------|-------------|--------------|

| DRAM_D31    | EPDC_SDCE3  | EPDC_SDCE1     | EPDC_GDSP     | EPDC_GDCLK    | EPDC_D15    | EPDC_D14     |

| EPDC_SDLE   | EPDC_SDCE2  | EPDC_SDCLK     | EPDC_PRWCOM   | EPDC_GDRL     | EPDC_GDOE   | EPDC_D13     |

| NC          | NC          | GND            | EPDC_SDCE0    | NC            | NC          | GND          |

| NC          | NC          | EPDC_PWRWAKEUP | EPDC_PWRCTRL0 | NC            | NC          | EPDC_D12     |

| NC          | NC          | EPDC_PWRSTAT   | EPDC_PWRCTRL1 | NC            | NC          | NVCC18_IO    |

| NC          | NC          | EPDC_PWRINT    | EPDC_PWRCTRL2 | NC            | NC          | EPDC_D11     |

| GND         | GND         | GND            | GND           | EPDC_PWRCTRL3 | GND         | GND          |

| NC          | NC          | NVCC33_IO      | NVCC33_IO     | NC            | NC          | NVCC33_IO    |

| VDD_SOC_CAP | VDD_SOC_CAP | VDD_SOC_IN     | VDD_SOC_IN    | VDD_ARM_IN    | VDD_ARM_IN  | VDD_ARM_IN   |

| VDD_SOC_CAP | VDD_SOC_CAP | VDD_SOC_IN     | VDD_SOC_IN    | VDD_ARM_IN    | VDD_ARM_IN  | VDD_ARM_IN   |

| NC          | GND         | GND            | GND           | GND           | GND         | GND          |

| GND         | GND         | GND            | GND           | GND           | GND         | GND          |

| GND         | GND         | GND            | GND           | GND           | GND         | GND          |

| NC          | GND         | GND            | GND           | GND           | GND         | GND          |

| VDD_PU_CAP  | VDD_PU_CAP  |                |               | VDD_HIGH_IN   | VDD_HIGH_IN | VDD_HIGH_CAP |

| VDD_PU_CAP  | VDD_PU_CAP  | VDD_PU_IN      |               | VDD_HIGH_IN   | VDD_HIGH_IN | VDD_HIGH_CAP |

| NC          | NC          | NVCC_3V3       | NHVCC_3V3     | NC            | NC          | VDD_USB_CAP  |

| GND         | GND         | GND            | GND           | GND           | GND         | GND          |

| NC          | NC          | FEC_REF_CLK    | FEC_TXD1      | NC            | NC          | JTAG_TDI     |

| NC          | NC          | FEC_TXD0       | NVCC18_IO     | NC            | NC          | JTAG_MOD     |

| NC          | NC          | FEC_RXD0       | SD3_CMD       | NC            | NC          | JTAG_TCK     |

| NC          | NC          | GND            | SD3_CLk       | NC            | NC          | GND          |

| FEC_TX_CLK  | FEC_CRS_DV  | FEC_RXD1       | SD3_DAT0      | SD3_DAT2      | I2C1_SCL    | REF_CLK_24M  |

| DRAM_D16    | FEC_RX_ER   | FEC_TX_EN      | SD3_DAT1      | SD3_DAT3      | I2C1_SDA    | REF_CLK_32K  |

### Table 81. 13 x 13 mm, 0.5 mm Pitch Ball Map (continued)

**Revision History**

# 7 Revision History

Table 83 provides a revision history for this data sheet.

| Table 83. i. | .MX 6SoloLite | Data Sheet Do | ocument Revision | History |

|--------------|---------------|---------------|------------------|---------|

|--------------|---------------|---------------|------------------|---------|

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                    |

|----------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 1         | 11/2012 | Updated Table 77, "Interfaces Allocation During Boot," on page 97.                                                                                                                                                                                                       |

| Rev 0.1        | 11/2012 | <ul> <li>Updated Table 8, "Package Thermal Resistance Data," on page 18.</li> <li>Corrected title of Table 79, "13 x 13 mm Supplies Contact Assignment," on page 100.</li> <li>Corrected title of Table 81, "13 x 13 mm, 0.5 mm Pitch Ball Map," on page 110.</li> </ul> |

| Rev. 0         | 10/2012 | Initial public release.                                                                                                                                                                                                                                                  |