#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100Mbps (1)                                                                                                      |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (3)                                                                                                   |

| Voltage - I/O                      | 1.2V, 1.8V, 3.0V                                                                                                    |

| Operating Temperature              | -40°C ~ 105°C (TA)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 432-TFBGA                                                                                                           |

| Supplier Device Package            | 432-MAPBGA (13x13)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6l3evn10ab                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3 Modules List

The i.MX 6SoloLite processor contains a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

| Block<br>Mnemonic                         | Block Name                                                                         | Subsystem                               | Brief Description                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 128x8 Fuse<br>Box                         | Electrical Fuse<br>Array                                                           | Security                                | Electrical Fuse Array. Enables to setup Boot Modes, Security Levels, Security Keys, and many other system parameters.<br>The i.MX 6SoloLite processor consists of 2-128x8-bit fuse box accessible through OCOTP_CTRL interface.                                                                                                                                                                   |

| ARM                                       | ARM Platform                                                                       | ARM                                     | The ARM Cortex-A9 platform consists of a Cortex-A9 core version r2p10 and associated sub-blocks, including Level 2 Cache Controller, SCU (Snoop Control Unit), GIC (General Interrupt Controller), private timers, Watchdog, and CoreSight debug modules.                                                                                                                                         |

| AUDMUX                                    | Digital Audio Mux                                                                  | Multimedia<br>Peripherals               | The AUDMUX is a programmable interconnect for voice, audio, and<br>synchronous data routing between host serial interfaces (for example, SSI1,<br>SSI2, and SSI3) and peripheral serial interfaces (audio and voice codecs).<br>The AUDMUX has seven ports with identical functionality and programming<br>models. A desired connectivity is achieved by configuring two or more<br>AUDMUX ports. |

| CCM<br>GPC<br>SRC                         | Clock Control<br>Module, Global<br>Power Controller,<br>System Reset<br>Controller | Clocks,<br>Resets, and<br>Power Control | These modules are responsible for clock and reset distribution in the system, and also for the system power management.                                                                                                                                                                                                                                                                           |

| CSU                                       | Central Security<br>Unit                                                           | Security                                | The Central Security Unit (CSU) is responsible for setting comprehensive security policy within the i.MX 6SoloLite platform. The Security Control Registers (SCR) of the CSU are set during boot time by the HAB and are locked to prevent further writing.                                                                                                                                       |

| CTI-1<br>CTI-2<br>CTI-3<br>CTI-4<br>CTI-5 | Cross Trigger<br>Interfaces                                                        | Debug / Trace                           | Cross Trigger Interfaces allows cross-triggering based on inputs from masters attached to CTIs. The CTI module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                                        |

| СТМ                                       | Cross Trigger<br>Matrix                                                            | Debug / Trace                           | Cross Trigger Matrix IP is used to route triggering events between CTIs. The CTM module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                                                               |

| DAP                                       | Debug Access<br>Port                                                               | System<br>Control<br>Peripherals        | <ul> <li>The DAP provides real-time access for the debugger without halting the core to:</li> <li>System memory and peripheral registers</li> <li>All debug configuration registers</li> <li>The DAP also provides debugger access to JTAG scan chains. The DAP module is internal to the Cortex-A9 Core Platform.</li> </ul>                                                                     |

| DCP                                       | Data<br>co-processor                                                               | Security                                | This module provides support for general encryption and hashing functions typically used for security functions. Because its basic job is moving data from memory to memory, it also incorporates a memory-copy (memcopy) function for both debugging and as a more efficient method of copying data between memory blocks than the DMA-based approach.                                           |

Table 2. i.MX 6SoloLite Modules List

| Block<br>Mnemonic                | Block Name                                   | Subsystem                        | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|----------------------------------|----------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IOMUXC                           | IOMUX Control                                | System<br>Control<br>Peripherals | This module enables flexible IO multiplexing. Each IO pad has default and several alternate functions. The alternate functions are software configurable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| КРР                              | Key Pad Port                                 | Connectivity<br>Peripherals      | <ul> <li>KPP Supports 8 x 8 external key pad matrix. KPP features are:</li> <li>Open drain design</li> <li>Glitch suppression circuit design</li> <li>Multiple keys detection</li> <li>Standby key press detection</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| LCDIF                            | LCD Interface                                | Multimedia<br>Peripherals        | The LCDIF provides display data for external LCD panels from simple<br>text-only displays to WVGA, 16/18/24 bpp color TFT panels. The LCDIF<br>supports all of these different interfaces by providing fully programmable<br>functionality and sharing register space, FIFOs, and ALU resources at the<br>same time. The LCDIF supports RGB (DOTCLK) modes as well as system<br>mode including both VSYNC and WSYNC modes.                                                                                                                                                                                                                                                                                                                     |  |

| MMDC                             | Multi-Mode DDR<br>Controller                 | Connectivity<br>Peripherals      | DDR Controller has the following features:<br>• Support 16/32-bit DDR3-800 or LPDDR2-800<br>• Supports up to 2 GByte DDR memory space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| OCOTP_C<br>TRL                   | OTP Controller                               | Security                         | The On-Chip OTP controller (OCOTP_CTRL) provides an interface for reading, programming, and/or overriding identification and control information stored in on-chip fuse elements. The module supports electrically-programmable poly fuses (eFUSEs). The OCOTP_CTRL also provides a set of volatile software-accessible signals that can be used for software control of hardware elements, not requiring non-volatility. The OCOTP_CTRL provides the primary user-visible mechanism for interfacing with on-chip fuse elements. Among the uses for the fuses are unique chip identifiers, mask revision numbers, cryptographic keys, JTAG secure mode, boot characteristics, and various control signals, requiring permanent non-volatility. |  |

| OCRAM                            | On-Chip Memory<br>controller                 | Data Path                        | The On-Chip Memory controller (OCRAM) module is designed as an interface<br>between system's AXI bus and internal (on-chip) SRAM memory module.<br>In i.MX 6SoloLite processor, the OCRAM is used for controlling the 128 KB<br>multimedia RAM through a 64-bit AXI bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| OCRAM_L<br>2                     | On-Chip Memory<br>Controller for L2<br>Cache | Data Path                        | The On-Chip Memory controller for L2 cache (OCRAM_L2) module is designed as an interface between system's AXI bus and internal (on-chip) L2 cache memory module during boot mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| OSC 32<br>kHz                    | OSC 32 kHz                                   | Clocking                         | Generates 32.768 kHz clock from external crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| PMU                              | Power-Managem<br>ent functions               | Data Path                        | Integrated power management unit. Used to provide power to various SoC domains.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| PWM-1<br>PWM-2<br>PWM-3<br>PWM-4 | Pulse Width<br>Modulation                    | Connectivity<br>Peripherals      | The pulse-width modulator (PWM) has a 16-bit counter and is optimized to generate sound from stored sample audio images and it can also generate tones. It uses 16-bit resolution and a 4x16 data FIFO to generate sound.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

#### **Electrical Characteristics**

Table 9 provides the operating ranges of the i.MX 6SoloLite processor.

| Parameter Symbol Description  |                                      | Min                  | Тур | Max <sup>1</sup> | Unit | Comment                                                                                                                             |  |

|-------------------------------|--------------------------------------|----------------------|-----|------------------|------|-------------------------------------------------------------------------------------------------------------------------------------|--|

| Run mode: LDO<br>enabled      | VDD_ARM_IN                           | 1.375 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 1.250V minimum for operation up to 996MHz.                                                                        |  |

|                               |                                      | 1.275 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 1.150V minimum for operation up to 792MHz                                                                         |  |

|                               |                                      | 1.075 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 0.95V minimum for operation up to 396MHz                                                                          |  |

|                               |                                      | 1.075 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 0.950V minimum for operation up to 192MHz                                                                         |  |

|                               |                                      | 1.050 <sup>2</sup>   |     | 1.5              | V    | LDO output set at 0.9250V minimum for operation up to 24MHz                                                                         |  |

|                               | VDD_SOC_IN <sup>3</sup><br>VDD_PU_IN | 1.275 <sup>2,4</sup> |     | 1.5              | V    | VDD_SOC and VDD_PU LDO outputs<br>(VDD_SOC_CAP and VDD_PU_CAP)<br>require 1.15 V minimum.                                           |  |

| Run mode: LDO                 | VDD_ARM_IN                           | 1.250                |     | 1.3              | V    | LDO bypassed for operation up to 996 MHz.                                                                                           |  |

| bypassed                      |                                      | 1.150                |     | 1.3              | V    | LDO bypassed for operation up to 792 MHz.                                                                                           |  |

|                               |                                      | 0.950                |     | 1.3              | V    | LDO bypassed for operation up to 396 MHz.                                                                                           |  |

|                               |                                      | 0.950                |     | 1.3              | V    | LDO bypassed for operation up to 192MHz                                                                                             |  |

|                               |                                      | 0.925                |     | 1.3              | V    | LDO bypassed for operation up to 24MHz                                                                                              |  |

|                               | VDD_SOC_IN <sup>3</sup><br>VDD_PU_IN | 1.15 <sup>4</sup>    |     | 1.3              | V    |                                                                                                                                     |  |

| Standby/DSM Mode              | VDD_ARM_IN                           | 0.9                  |     | 1.3              | V    | See Table 12, "Stop Mode Current and                                                                                                |  |

|                               | VDD_SOC_IN<br>VDD_PU_IN              | 0.9                  |     | 1.3              | V    | Power Consumption," on page 24.                                                                                                     |  |

| VDDHIGH internal<br>Regulator | VDD_HIGH_IN <sup>5</sup>             | 2.8                  |     | 3.3              | V    | Must match the range of voltges that the rechargeable backup battery supports.                                                      |  |

| Backup battery supply range   | -                                    |                      |     | 3.3              | V    | Should be supplied from the same supply as VDDHIGH_IN if the system does not require keeping real time and other data on OFF state. |  |

| USB supply voltages           | USB_OTG1_VBUS<br>USB_OTG2_VBUS       | 4.4                  |     | 5.25             | V    |                                                                                                                                     |  |

| DDR I/O supply                | NVCC_DRAM                            | 1.14                 | 1.2 | 1.3              | V    | LPDDR2                                                                                                                              |  |

|                               |                                      | 1.425                | 1.5 | 1.575            | V    | DDR3                                                                                                                                |  |

|                               | NVCC_DRAM_2P5                        | 2.5                  | 2.5 | 2.75             | V    |                                                                                                                                     |  |

## Table 9. Operating Ranges

| Parameter       | Value                            |

|-----------------|----------------------------------|

| Reference clock | 24 MHz                           |

| Lock time       | <11250 reference cycles (450 µs) |

# 4.4.2 528 MHz PLL

#### Table 16. 528 MHz PLL's Electrical Parameters

| Parameter          | Value                                |

|--------------------|--------------------------------------|

| Clock output range | 528 MHz PLL output                   |

| Reference clock    | 24 MHz                               |

| Lock time          | <11250 reference cycles (15 $\mu$ s) |

# 4.4.3 Ethernet PLL

#### Table 17. Ethernet PLL's Electrical Parameters

| Parameter          | Value                                 |

|--------------------|---------------------------------------|

| Clock output range | 500 MHz                               |

| Reference clock    | 24 MHz                                |

| Lock time          | <11250 reference cycles (450 $\mu$ s) |

## 4.4.4 480 MHz PLL

## Table 18. 480 MHz PLL's Electrical Parameters

| Parameter          | Value                         |

|--------------------|-------------------------------|

| Clock output range | 480 MHz PLL output            |

| Reference clock    | 24 MHz                        |

| Lock time          | <383 reference cycles (15 µs) |

# 4.4.5 ARM PLL

#### Table 19. ARM PLL's Electrical Parameters

| Parameter          | Value           |

|--------------------|-----------------|

| Clock output range | 650 MHz~1.3 GHz |

| Parameter              | Min | Тур        | Max             | Comments                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------|-----|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fosc                   |     | 32.768 kHz |                 | This frequency is nominal and determined mainly by the crystal selected. 32.0 K would work as well.                                                                                                                                                                                                                                                                        |

| Current<br>consumption |     | 4 μΑ       |                 | The typical value shown is only for the oscillator, driven by an external crystal. If the internal ring oscillator is used instead of an external crystal, then approximately $25 \ \mu$ A should be added to this value.                                                                                                                                                  |

| Bias resistor          |     | 14 MΩ      |                 | This the integrated bias resistor that sets the amplifier<br>into a high gain state. Any leakage through the ESD<br>network, external board leakage, or even a scope<br>probe that is significant relative to this value will<br>debias the amp. The debiasing will result in low gain,<br>and will impact the circuit's ability to start up and<br>maintain oscillations. |

| ł                      |     | Targ       | et Crystal Prop | erties                                                                                                                                                                                                                                                                                                                                                                     |

| Cload                  |     | 10 pF      |                 | Usually crystals can be purchased tuned for different<br>Cloads. This Cload value is typically 1/2 of the<br>capacitances realized on the PCB on either side of<br>the quartz. A higher Cload will decrease oscillation<br>margin, but increases current oscillating through the<br>crystal.                                                                               |

| ESR                    |     | 50 kΩ      |                 | Equivalent series resistance of the crystal. Choosing<br>a crystal with a higher value will decrease the<br>oscillating margin.                                                                                                                                                                                                                                            |

#### Table 20. OSC32K Main Characteristics

# 4.6 I/O DC Parameters

This section includes the DC parameters of the following I/O types:

- Dual Voltage General Ppurpose I/O cell set (DVGPIO)

- Single Voltage General Purpose I/O cell set (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3 modes

## NOTE

The term 'OVDD' in this section refers to the associated supply rail of an input or output.

# 4.7.1 General Purpose I/O AC Parameters

The I/O AC parameters for GPIO in slow and fast modes are presented in the Table 25 and Table 26, respectively. Note that the fast or slow I/O behavior is determined by the appropriate control bits in the IOMUXC control registers.

| Parameter                                                             | Symbol | Test Condition                                             | Min | Тур | Мах                    | Unit |

|-----------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, ipp_dse=111)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.72/2.79<br>1.51/1.54 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, ipp_dse=101)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.20/3.36<br>1.96/2.07 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, ipp_dse=100) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.64/3.88<br>2.27/2.53 |      |

| Output Pad Transition Times, rise/fall<br>(Low Drive. ipp_dse=011)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 4.32/4.50<br>3.16/3.17 |      |

| Input Transition Times <sup>1</sup>                                   | trm    | _                                                          | _   | —   | 25                     | ns   |

Table 25. General Purpose I/O AC Parameters 1.8 V Mode

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

## Table 26. General Purpose I/O AC Parameters 3.3 V Mode

| Parameter                                                             | Symbol | Test Condition                                             | Min | Тур | Max                    | Unit |

|-----------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, ipp_dse=101)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 1.70/1.79<br>1.06/1.15 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, ipp_dse=011)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.35/2.43<br>1.74/1.77 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, ipp_dse=010) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.13/3.29<br>2.46/2.60 |      |

| Output Pad Transition Times, rise/fall<br>(Low Drive. ipp_dse=001)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 5.14/5.57<br>4.77/5.15 |      |

| Input Transition Times <sup>1</sup>                                   | trm    | _                                                          | —   | —   | 25                     | ns   |

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

# 4.9.3.1 EIM Signal Cross Reference

Table 35 is a guide intended to help the user identify the signals in the EIM chapter of the i.MX 6SoloLite reference manual that are identical to those mentioned in this data sheet.

| Reference Manual EIM Chapter<br>Nomenclature | Data Sheet Nomenclature, Reference Manual External Signals and Pin<br>Multiplexing Chapter, and IOMUXC Controller Chapter Nomenclature |  |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| BCLK                                         | EIM_BCLK                                                                                                                               |  |  |  |  |

| CSx                                          | EIM_CSx                                                                                                                                |  |  |  |  |

| WE_B                                         | EIM_RW                                                                                                                                 |  |  |  |  |

| OE_B                                         | EIM_OE                                                                                                                                 |  |  |  |  |

| BEy_B                                        | EIM_EBx                                                                                                                                |  |  |  |  |

| ADV                                          | EIM_LBA                                                                                                                                |  |  |  |  |

| ADDR                                         | EIM_A[25:16], EIM_DA[15:0]                                                                                                             |  |  |  |  |

| ADDR/M_DATA                                  | EIM_DAx (Addr/Data muxed mode)                                                                                                         |  |  |  |  |

| DATA                                         | EIM_NFC_D (Data bus shared with NAND Flash)<br>EIM_Dx (dedicated data bus)                                                             |  |  |  |  |

| WAIT_B                                       | EIM_WAIT                                                                                                                               |  |  |  |  |

| Table 35. | EIM Signal | Cross | Reference |

|-----------|------------|-------|-----------|

|-----------|------------|-------|-----------|

## 4.9.3.2 EIM Interface Pads Allocation

EIM supports 32-bit, 16-bit, and 8-bit devices operating in address/data separate or multiplexed modes. Table 36 provides EIM interface pads allocation in different modes.

|                      | Non Mul   | tiplexed Add<br>Mode | Multiplexed<br>Address/Data mode |           |                 |

|----------------------|-----------|----------------------|----------------------------------|-----------|-----------------|

| Setup                | 8         | Bit                  | 16 Bit                           | 16 Bit    | 32 Bit          |

|                      | MUM = 0,  | MUM = 0,             | MUM = 0,                         | MUM = 1,  | MUM = 1,        |

|                      | DSZ = 100 | DSZ = 101            | DSZ = 001                        | DSZ = 010 | DSZ = 011       |

| A[15:0]              | EIM_DA_A  | EIM_DA_A             | EIM_DA_A                         | EIM_DA_A  | EIM_DA_A        |

|                      | [15:0]    | [15:0]               | [15:0]                           | [15:0]    | [15:0]          |

| A[25:16]             | EIM_A     | EIM_A                | EIM_A                            | EIM_A     | EIM_D           |

|                      | [25:16]   | [25:16]              | [25:16]                          | [25:16]   | [9:0]           |

| D[7:0],              | EIM_D     | _                    | EIM_D                            | EIM_DA_A  | EIM_DA_A        |

| EIM_EB0              | [7:0]     |                      | [7:0]                            | [7:0]     | [7:0]           |

| D[15:8],             | —         | EIM_D                | EIM_D                            | EIM_DA_A  | EIM_DA_A        |

| EIM_EB1              |           | [15:8]               | [15:8]                           | [15:8]    | [15:8]          |

| D[23:16],<br>EIM_EB2 | —         | —                    | —                                | —         | EIM_D<br>[7:0]  |

| D[31:24],<br>EIM_EB3 | —         | —                    | —                                | —         | EIM_D<br>[15:8] |

#### Table 36. EIM Internal Module Multiplexing<sup>1</sup>

<sup>1</sup> For more information on configuration ports mentioned in this table, see the i.MX 6SololLite reference manual.

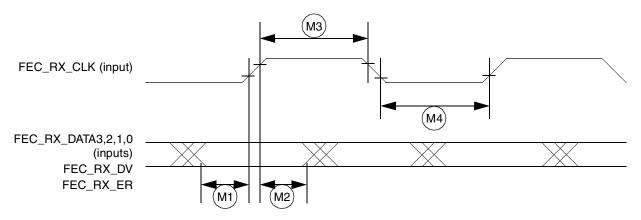

Figure 36. MII Receive Signal Timing Diagram

## 4.10.5.2 MII Transmit Signal Timing

The MII transmit signal timing affects the FEC\_TX\_DATA3,2,1,0, FEC\_TX\_EN, FEC\_TX\_ER, and FEC\_TX\_CLK signals. The transmitter functions correctly up to a FEC\_TX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. In addition, the processor clock frequency must exceed twice the FEC\_TX\_CLK frequency.

Table 53 lists MII transmit channel timing parameters. Figure 37 shows MII transmit signal timing diagram for the values listed in Table 53.

| Num | Characteristic <sup>1 2</sup>                                  | Min | Max | Unit              |

|-----|----------------------------------------------------------------|-----|-----|-------------------|

| M5  | FEC_TX_CLK to FEC_TX_DATA3,2,1,0, FEC_TX_EN, FEC_TX_ER invalid | 5   | —   | ns                |

| M6  | FEC_TX_CLK to FEC_TX_DATA3,2,1,0, FEC_TX_EN, FEC_TX_ER valid   | —   | 20  | ns                |

| M7  | FEC_TX_CLK pulse width high                                    | 35% | 65% | FEC_TX_CLK period |

| M8  | FEC_TX_CLK pulse width low                                     | 35% | 65% | FEC_TX_CLK period |

Table 53. MII Transmit Signal Timing

<sup>1</sup> FEC\_TX\_EN, FEC\_TX\_CLK, and FEC\_TXD0 have the same timing in 10 Mbps 7-wire interface mode.

<sup>2</sup> Test conditions: 25pF on each output signal.

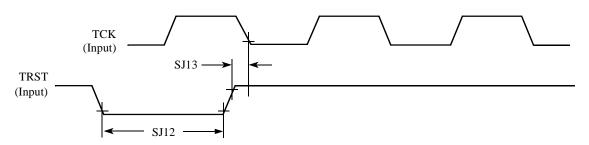

### Figure 46. TRST Timing Diagram

| ID   | Parameter <sup>1,2</sup>                                       | All Freq | All Frequencies |      |  |

|------|----------------------------------------------------------------|----------|-----------------|------|--|

|      |                                                                | Min      | Мах             | Unit |  |

| SJ0  | TCK frequency of operation 1/(3•T <sub>DC</sub> ) <sup>1</sup> | 0.001    | 22              | MHz  |  |

| SJ1  | TCK cycle time in crystal mode                                 | 45       | _               | ns   |  |

| SJ2  | TCK clock pulse width measured at $V_M^2$                      | 22.5     | _               | ns   |  |

| SJ3  | TCK rise and fall times                                        | _        | 3               | ns   |  |

| SJ4  | Boundary scan input data set-up time                           | 5        | _               | ns   |  |

| SJ5  | Boundary scan input data hold time                             | 24       | _               | ns   |  |

| SJ6  | TCK low to output data valid                                   | _        | 40              | ns   |  |

| SJ7  | TCK low to output high impedance                               | _        | 40              | ns   |  |

| SJ8  | TMS, TDI data set-up time                                      | 5        | _               | ns   |  |

| SJ9  | TMS, TDI data hold time                                        | 25       | _               | ns   |  |

| SJ10 | TCK low to TDO data valid                                      | _        | 44              | ns   |  |

| SJ11 | TCK low to TDO high impedance                                  | —        | 44              | ns   |  |

| SJ12 | TRST assert time                                               | 100      | —               | ns   |  |

| SJ13 | TRST set-up time to TCK low                                    | 40       | —               | ns   |  |

<sup>1</sup>  $T_{DC}$  = target frequency of SJC

<sup>2</sup>  $V_{\rm M}$  = mid-point voltage

# 4.10.9 SPDIF Timing Parameters

The Sony/Philips Digital Interconnect Format (SPDIF) data is sent using the bi-phase marking code. When encoding, the SPDIF data signal is modulated by a clock that is twice the bit rate of the data signal.

Table 60 and Figure 47 and Figure 48 show SPDIF timing parameters for the Sony/Philips Digital Interconnect Format (SPDIF), including the timing of the modulating Rx clock (SRCK) for SPDIF in Rx mode and the timing of the modulating Tx clock (STCLK) for SPDIF in Tx mode.

| ID   | Parameter                                      | Min | Мах | Unit |  |  |

|------|------------------------------------------------|-----|-----|------|--|--|

|      | Synchronous Internal Clock Operation           |     |     |      |  |  |

| SS42 | 42 SRXD setup before (Tx) CK falling 10.0 — ns |     |     |      |  |  |

| SS43 | SRXD hold after (Tx) CK falling                | 0.0 | _   | ns   |  |  |

#### Table 62. SSI Transmitter Timing with Internal Clock (continued)

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

| ID   | Parameter                      | Min   | Мах | Unit |

|------|--------------------------------|-------|-----|------|

| SS47 | Oversampling clock period      | 15.04 | —   | ns   |

| SS48 | Oversampling clock high period | 6.0   | —   | ns   |

| SS49 | Oversampling clock rise time   | —     | 3.0 | ns   |

| SS50 | Oversampling clock low period  | 6.0   | —   | ns   |

| SS51 | Oversampling clock fall time   | _     | 3.0 | ns   |

Table 63. SSI Receiver Timing with Internal Clock (continued)

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

**Electrical Characteristics**

| ID   | Parameter                            | Min  | Мах  | Unit |

|------|--------------------------------------|------|------|------|

| SS39 | (Tx) CK high to STXD high impedance  | —    | 15.0 | ns   |

|      | Synchronous External Clock Operation |      |      |      |

| SS44 | SRXD setup before (Tx) CK falling    | 10.0 | —    | ns   |

| SS45 | SS45 SRXD hold after (Tx) CK falling |      | —    | ns   |

| SS46 | SS46 SRXD rise/fall time             |      | 6.0  | ns   |

Table 64. SSI Transmitter Timing with External Clock (continued)

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal STCK/SRCK and/or the frame sync STFS/SRFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- "Tx" and "Rx" refer to the Transmit and Receive sections of the SSI.

- The terms WL and BL refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the FS timing is same as that of Tx Data (for example, during AC97 mode of operation).

#### **Electrical Characteristics**

| Name    | Parameter                       | Min   | Max   | Unit | Comment                        |  |  |

|---------|---------------------------------|-------|-------|------|--------------------------------|--|--|

| Tstrobe | strobe period                   | 4.166 | 4.167 | ns   |                                |  |  |

| Thold   | data hold time                  | 300   |       | ps   | Measured at 50% point          |  |  |

| Tsetup  | data setup time                 | 365   |       | ps   | Measured at 50% point          |  |  |

| Tslew   | strobe/data rising/falling time | 0.7   | 2     | V/ns | Averaged from 30% – 70% points |  |  |

## Table 72. USB HSIC Receive Parameters<sup>1</sup>

<sup>1</sup> The timings in the table are guaranteed when:

—AC I/O voltage is between 0.9x to 1x of the I/O supply

-DDR\_SEL configuration bits of the I/O are set to (10)b

## 4.10.13 USB PHY Parameters

This section describes the USB-OTG PHY and the USB Host port PHY parameters.

The USB PHY meets the electrical compliance requirements defined in the Universal Serial Bus Revision 2.0 OTG, USB Host.

# 5 Boot Mode Configuration

This section provides information on boot mode configuration pins allocation and boot devices interfaces allocation.

# 5.1 Boot Mode Configuration Pins

Table 76 provides boot options, functionality, fuse values, and associated pins. Several input pins are also sampled at reset and can be used to override fuse values, depending on the value of BT\_FUSE\_SEL fuse. The boot option pins are in effect when BT\_FUSE\_SEL fuse is '0' (cleared, which is the case for an unblown fuse). For detailed boot mode options configured by the boot mode pins, see the i.MX 6SoloLite Fuse Map document and the System Boot chapter of the i.MX 6SoloLite reference manual.

| Pin        | Direction at Reset | eFuse Name          | Details             |

|------------|--------------------|---------------------|---------------------|

| BOOT_MODE1 | Input              | Boot Mode Selection | Boot Mode selection |

| BOOT_MODE0 | Input              | Boot Mode Selection | Boot Mode Selection |

| Table 76. Fuses and Associated Pins Used for Boot | Table 76 | . Fuses and | d Associated | Pins | Used for Boo | t |

|---------------------------------------------------|----------|-------------|--------------|------|--------------|---|

|---------------------------------------------------|----------|-------------|--------------|------|--------------|---|

| Parameter                   | O-multical |          | Common Dimensions |         |  |  |

|-----------------------------|------------|----------|-------------------|---------|--|--|

| Parameter                   | Symbol     | Minimum  | Normal            | Maximum |  |  |

| Total Thickness             | А          | 0.88     | -                 | 1.1     |  |  |

| Stand Off                   | A1         | 0.16     | -                 | 0.26    |  |  |

| Substrate Thickness         | A2         |          | 0.26 REF          |         |  |  |

| Mold Thickness              | A3         |          | 0.54 REF          |         |  |  |

| Body Size                   | D          |          | 13 BSC            |         |  |  |

|                             | E          | 13 BSC   |                   |         |  |  |

| Ball Diameter               |            | 0.3      |                   |         |  |  |

| Ball Opening                |            | 0.275    |                   |         |  |  |

| Ball Width                  | b          | 0.27 -   |                   | 0.37    |  |  |

| Ball Pitch                  | е          |          | 0.5 BSC           |         |  |  |

| Ball Count                  | n          | 432      |                   |         |  |  |

| Edge Ball Center to Center  | D1         |          | 11.5 BSC          |         |  |  |

|                             | E1         |          | 11.5 BSC          |         |  |  |

| Body Center to Contact Ball | SD         |          | 0.25 BSC          |         |  |  |

|                             | SE         | 0.25 BSC |                   |         |  |  |

| Package Edge Tolerance      | aaa        | 0.1      |                   |         |  |  |

| Mold Flatness               | bbb        | 0.1      |                   |         |  |  |

| Coplanarity                 | ddd        | 0.08     |                   |         |  |  |

| Ball Offset (Package)       | eee        | 0.15     |                   |         |  |  |

| Ball Offset (Ball)          | fff        |          | 0.05              |         |  |  |

#### Table 78. 13 x 13, 0.5 mm BGA Package Details

# 6.1.2 13 x 13 mm Ground, Power, Sense, Not Connected and Reference Contact Assignments

Table 79 shows the device connection list for ground, power, sense, and reference contact signals.

| Supply Rail Name | Ball(s) Position(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Remark                                                                                                                             |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| DDR_VREF         | N5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

| GND              | A1, A4, A7, A24, C6, C10, C14, C19, D1, D2, E5, G1, G8, G9,<br>G10, G11, G13, G14, G15, G17, G18, H3, H7, H18, H22, J5,<br>K1, L7, L9, L10, L11, L12, L13, L14, L15, L16, M5, M7, M8, M9,<br>M10, M11, M12, M13, M14, M15, M16, M17, N3, N7, N8, N9,<br>N10, N11, N12, N13, N14, N15, N16, N17, N22, P9, P10, P11,<br>P12, P13, P14, P15, P16, R1, T5, U3, U7, U18, U22, V1, V8,<br>V9, V10, V11, V12, V13, V14, V15, V16, V18, Y5, AA1, AA2,<br>AB10, AB14, AB18, AC18, AD1, AD4, AD7, AD24 |                                                                                                                                    |

| GND_Kelvin       | V17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Must be connected                                                                                                                  |

| GPANAIO          | AD22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Analog pad                                                                                                                         |

| NVCC_1P2V        | W7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

| NVCC18_IO        | E14, E15, M20, Y11                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

| NVCC33_IO        | H10, H11, H14, H15, L18, M18, T19, U10, U11                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                    |

| NVCC_DRAM        | E6, Y6, G7, H6, J6, N6, P7, T6, U6, V7                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Supply of the DDR Interface                                                                                                        |

| NVCC_DRAM_2P5    | M6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

| NVCC_PLL         | Y19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                    |

| NVCC_SD1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |

| NVCC_SD2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |

| NVCC_SD3         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                    |

| VDD_ARM_CAP      | J15, J16, J17, J18, K15, K16, K17, K18                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Secondary Supply for the ARM0 and<br>ARM1 Cores (internal regulator<br>output—requires capacitor if internal<br>regulator is used) |

| VDD_ARM_IN       | J12, J13, J14, K12, K13, K14                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Primary Supply, for the ARM0 and ARM1 Core' Regulator                                                                              |

| VDD_HIGH_CAP     | R14, R15, T14, T15                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Secondary Supply for the 2.5 V<br>domain (internal regulator<br>output—requires capacitor if internal<br>regulator is used)        |

| VDD_HIGH_IN      | R12, R13, T12, T13                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Primary Supply for the 2.5 V Regulator                                                                                             |

| VDD_PU_CAP       | R7, R8, R9, T7, T8, T9                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Secondary Supply for the VPU and<br>GPU's (internal regulator<br>output—requires capacitor if internal<br>regulator is used)       |

| VDD_PU_IN        | R10, R11, T10, T11                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                    |

## Table 79. 13 x 13 mm Supplies Contact Assignment

| Supply Rail Name | Ball(s) Position(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Remark                                                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD_SNVS_CAP     | AD20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Secondary Supply for the SNVS<br>(internal regulator output—requires<br>capacitor if internal regulator is used)                                   |

| VDD_SNVS_IN      | AC20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Primary Supply, for the SNVS<br>Regulator                                                                                                          |

| VDD_SOC_CAP      | J7, J8, J9, K7, K8, K9, N18, P18, R18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Secondary Supply for the SoC and PU<br>(internal regulator output—requires<br>capacitor if internal regulator is used)                             |

| VDD_SOC_IN       | J10, J11, K10, K11, R16, R17, T16, T17, T18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Primary Supply, for the SoC and PU<br>Regulators                                                                                                   |

| VDD_USB_CAP      | U14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Secondary Supply for the 3V Domain<br>(USBPHY, MLPBPHY, eFuse), internal<br>regulator output, requires capacitor if<br>internal regulator is used. |

| USB_OTG1_VBUS    | AA18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                    |

| USB_OTG2_VBUS    | AD18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                    |

| ZQPAD            | AE17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                    |

| NC               | C4, C5, C8, C9, C12, C13, C16, C17, C20, C21, D4, D5, D8, D9, D12, D13, D16, D17, D20, D21, E8, E9, E12, E13, E16, E17, F3, F4, F5, F6, F8, F9, F12, F13, F16, F17, F19, F20, F21, F22, G3, G4, G5, G6, G19, G20, G21, G22, H8, H9, H12, H13, H16, H17, K3, K4, K5, K6, K19, K20, K21, K22, L3, L4, L5, L6, L8, L17, L19, L20, L21, L22, P3, P4, P5, P6, P8, P17, P19, P20, P21, P22, R3, R4, R5, R6, R19, R20, R21, R22, U8, U9, U12, U13, U16, U17, V3, V4, V5, V6, V19, V20, V21, V22, W3, W4, W5, W6, W8, W9, W12, W13, W16, W17, W19, W20, W21, W22, Y8, Y9, Y12, Y13, Y16, Y17, AA4, AA5, AA8, AA9, AA12, AA13, AA16, AA17, AA20, AA21, AB4, AB5, AB8, AB9, AB12, AB13, AB16, AB17 AB20, AB21 | No Connections.                                                                                                                                    |

#### Table 79. 13 x 13 mm Supplies Contact Assignment (continued)

Table 80 displays an alpha-sorted list of the signal assignments including power rails. The table also includes out of reset pad state.

Table 80. 13 x 13 mm Functional Contact Assignments

|           |      |             |           | Out of Reset Condition <sup>1</sup> |                  |              |        |

|-----------|------|-------------|-----------|-------------------------------------|------------------|--------------|--------|

| Ball Name | Ball | Power Group | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/Output | Value  |

| AUD_MCLK  | H19  | NVCC_GPIO   | GPIO      | ALT5                                | gpio1_GPIO[6]    | Input        | Keeper |

| AUD_RXC   | J21  | NVCC_GPIO   | GPIO      | ALT5                                | gpio1_GPIO[1]    | Input        | Keeper |

| AUD_RXD   | J20  | NVCC_GPIO   | GPIO      | ALT5                                | gpio1_GPIO[2]    | Input        | Keeper |

| AUD_RXFS  | J19  | NVCC_GPIO   | GPIO      | ALT5                                | gpio1_GPIO[0]    | Input        | Keeper |

|            |      |             |           | Out of Reset Condition <sup>1</sup> |                  |              |           |

|------------|------|-------------|-----------|-------------------------------------|------------------|--------------|-----------|

| Ball Name  | Ball | Power Group | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/Output | Value     |

| AUD_TXC    | H20  | NVCC_GPIO   | GPIO      | ALT5                                | gpio1_GPIO[3]    | Input        | Keeper    |

| AUD_TXD    | J22  | NVCC_GPIO   | GPIO      | ALT5                                | gpio1_GPIO[5]    | Input        | Keeper    |

| AUD_TXFS   | H21  | NVCC_GPIO   | GPIO      | ALT5                                | gpio1_GPIO[4]    | Input        | Keeper    |

| BOOT_MODE0 | AC15 | VDD_SNVS_IN | GPIO      | ALT0                                | src_BOOT_MODE[0] | Input        | Keeper    |

| BOOT_MODE1 | AB15 | VDD_SNVS_IN | GPIO      | ALT0                                | src_BOOT_MODE[1] | Input        | Keeper    |

| CLK1_N     | AD23 | VDDHIGH_CAP |           |                                     | CLK1_N           | _            |           |

| CLK1_P     | AC23 | VDDHIGH_CAP |           |                                     | CLK1_P           | _            |           |

| DRAM_A0    | U4   | NVCC_DRAM   | DDR       | ALT0                                | mmdc_DRAM_A[0]   | Output       | 0         |