Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 72MHz                                                                   |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB            |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT            |

| Number of I/O              | 26                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 20K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                               |

| Data Converters            | A/D 10x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 36-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 36-VFQFPN (6x6)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103tbu6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## List of figures

| Figure 1.  | STM32F103xx performance line block diagram                                                                  | 11 |

|------------|-------------------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Clock tree                                                                                                  |    |

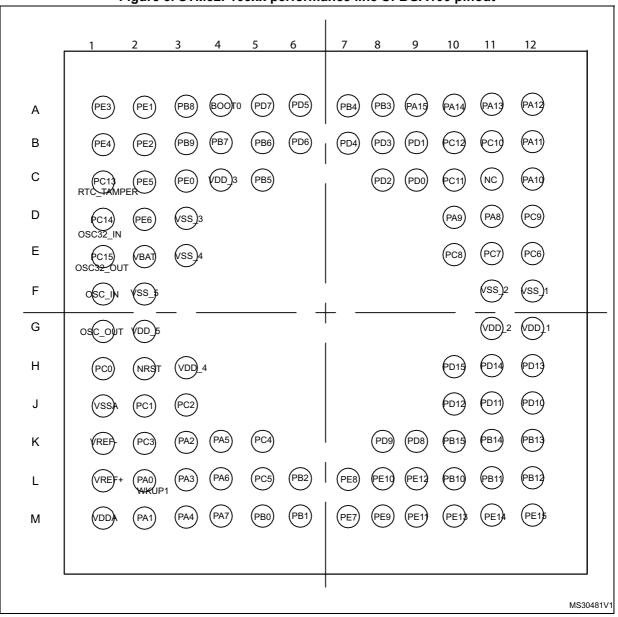

| Figure 3.  | STM32F103xx performance line LFBGA100 ballout                                                               | 21 |

| Figure 4.  | STM32F103xx performance line LQFP100 pinout                                                                 | 22 |

| Figure 5.  | STM32F103xx performance line UFBGA100 pinout                                                                | 23 |

| Figure 6.  | STM32F103xx performance line LQFP64 pinout                                                                  |    |

| Figure 7.  | STM32F103xx performance line TFBGA64 ballout                                                                |    |

| Figure 8.  | STM32F103xx performance line LQFP48 pinout                                                                  | 26 |

| Figure 9.  | STM32F103xx performance line UFQFPN48 pinout                                                                |    |

| Figure 10. | STM32F103xx performance line VFQFPN36 pinout                                                                |    |

| Figure 11. | Memory map                                                                                                  |    |

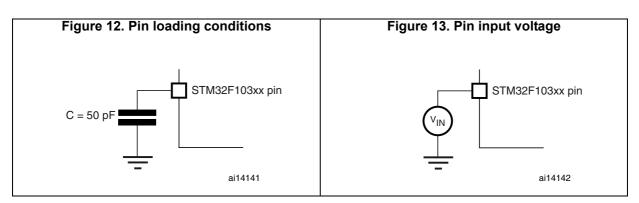

| Figure 12. | Pin loading conditions.                                                                                     |    |

| Figure 13. | Pin input voltage                                                                                           |    |

| Figure 14. | Power supply scheme                                                                                         |    |

| Figure 15. | Current consumption measurement scheme                                                                      |    |

| Figure 16. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                                       |    |

| -          |                                                                                                             | 43 |

| Figure 17. | Typical current consumption in Run mode versus frequency (at 3.6 V) -                                       |    |

| -          | code with data processing running from RAM, peripherals disabled                                            | 43 |

| Figure 18. | Typical current consumption on V <sub>BAT</sub> with RTC on versus temperature at different                 |    |

| -          | V <sub>BAT</sub> values                                                                                     | 45 |

| Figure 19. | Typical current consumption in Stop mode with regulator in Run mode versus                                  |    |

| U          | temperature at $V_{DD}$ = 3.3 V and 3.6 V                                                                   | 46 |

| Figure 20. | Typical current consumption in Stop mode with regulator in Low-power mode versus                            |    |

| U          | temperature at $V_{DD}$ = 3.3 V and 3.6 V                                                                   | 46 |

| Figure 21. | Typical current consumption in Standby mode versus temperature at                                           |    |

| -          | V <sub>DD</sub> = 3.3 V and 3.6 V                                                                           | 47 |

| Figure 22. | High-speed external clock source AC timing diagram                                                          | 52 |

| Figure 23. | Low-speed external clock source AC timing diagram                                                           |    |

| Figure 24. | Typical application with an 8 MHz crystal                                                                   | 54 |

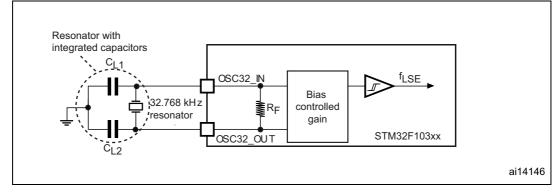

| Figure 25. | Typical application with a 32.768 kHz crystal                                                               | 55 |

| Figure 26. | Standard I/O input characteristics - CMOS port                                                              |    |

| Figure 27. | Standard I/O input characteristics - TTL port                                                               | 63 |

| Figure 28. | 5 V tolerant I/O input characteristics - CMOS port                                                          | 64 |

| Figure 29. | 5 V tolerant I/O input characteristics - TTL port                                                           |    |

| Figure 30. | I/O AC characteristics definition                                                                           | 67 |

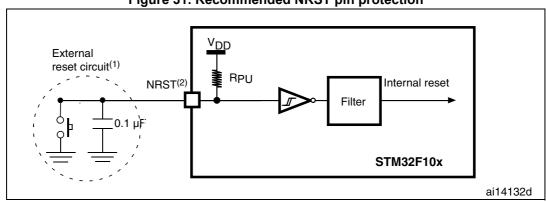

| Figure 31. | Recommended NRST pin protection                                                                             | 68 |

| Figure 32. | I <sup>2</sup> C bus AC waveforms and measurement circuit                                                   |    |

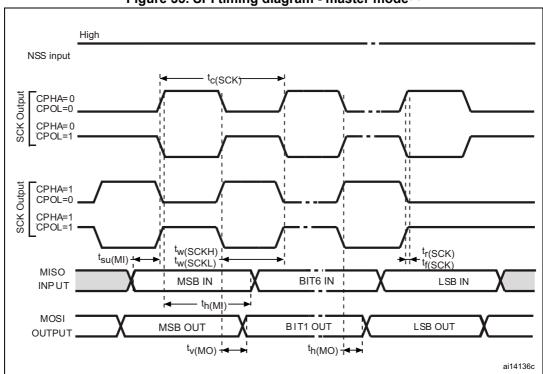

| Figure 33. | SPI timing diagram - slave mode and CPHA = 0                                                                | 72 |

| Figure 34. | SPI timing diagram - slave mode and CPHA = 0<br>SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup> | 72 |

| Figure 35. | SPI timing diagram - master mode <sup>(1)</sup>                                                             | 73 |

| Figure 36. | USB timings: definition of data signal rise and fall time                                                   | 74 |

| Figure 37. | ADC accuracy characteristics                                                                                | 77 |

| Figure 38. | Typical connection diagram using the ADC                                                                    | 78 |

| Figure 39. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> )                | 78 |

| Figure 40. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )                    | 79 |

| Figure 41. | VFQFPN36 - 36-pin, 6x6 mm, 0.5 mm pitch very thin profile fine pitch quad                                   |    |

|            | flat package outline                                                                                        | 80 |

### 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32F103x8 and STM32F103xB medium-density performance line microcontrollers. For more details on the whole STMicroelectronics STM32F103xx family, please refer to *Section 2.2: Full compatibility throughout the family*.

The medium-density STM32F103xx datasheet should be read in conjunction with the low-, medium- and high-density STM32F10xxx reference manual. The reference and Flash programming manuals are both available from the STMicroelectronics website *www.st.com*.

For information on the Cortex<sup>®</sup>-M3 core please refer to the Cortex<sup>®</sup>-M3 Technical Reference Manual, available from the www.arm.com website.

### 2 Description

The STM32F103xx medium-density performance line family incorporates the highperformance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a 72 MHz frequency, highspeed embedded memories (Flash memory up to 128 Kbytes and SRAM up to 20 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses. All devices offer two 12-bit ADCs, three general purpose 16-bit timers plus one PWM timer, as well as standard and advanced communication interfaces: up to two I<sup>2</sup>Cs and SPIs, three USARTs, an USB and a CAN.

The devices operate from a 2.0 to 3.6 V power supply. They are available in both the –40 to +85 °C temperature range and the –40 to +105 °C extended temperature range. A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F103xx medium-density performance line family includes devices in six different package types: from 36 pins to 100 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the STM32F103xx medium-density performance line microcontroller family suitable for a wide range of applications such as motor drives, application control, medical and handheld equipment, PC and gaming peripherals, GPS platforms, industrial applications, PLCs, inverters, printers, scanners, alarm systems, video intercoms, and HVACs.

### 3 Pinouts and pin description

| r | 1                  | 2<br>2                  | арана и калана и кала<br>З | 4                 | 5                 | 6                 | 7                 | 8<br>8 | 9    | 10       |

|---|--------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|--------|------|----------|

| A | PC14-<br>OSC32_IN  | PC13-<br>TAMPER-<br>RTC | PE2                                                                                                                  | PB9               | РВ7               | PB4               | РВЗ               | PA15   | PA14 | PA13     |

| в | PC15-<br>bSC32_out | V <sub>BAT</sub>        | PE3                                                                                                                  | PB8               | PB6               | PD5               | PD2               | PC11   | PC10 | PA12     |

| с | OSC_IN             | V <sub>SS_5</sub>       | PE4                                                                                                                  | PE1               | PB5               | PD6               | PD3               | PC12   | PA9  | PA11     |

| D | OSC_OUT            | V <sub>DD_5</sub>       | PES                                                                                                                  | PEO               | воото             | PD7               | PD4               | PDO    | PA8  | PA10     |

| E | NRST               | PC2                     | PE6                                                                                                                  | V <sub>SS_4</sub> | V <sub>SS_3</sub> | V SS_2            | V <sub>SS_1</sub> | PD1    | PC9  | PC7      |

| F | PC0                | PC1                     | PC3                                                                                                                  | V <sub>DD_4</sub> | V <sub>DD_3</sub> | V <sub>DD_2</sub> | V <sub>DD_1</sub> | NC     | PC8  | PC6      |

| G | V <sub>SSA</sub>   | PA0-WKUP                | PA4                                                                                                                  | PC4               | PB2               | PE10              | PE14              | PB15   | PD11 | PD15     |

| н | V <sub>REF-</sub>  | PA1                     | PA5                                                                                                                  | PC5               | PE7               | PE11              | PE15              | PB14   | PD10 | PD14     |

| L | V <sub>REF+</sub>  | PA2                     | PA6                                                                                                                  | PB0               | PE8               | PE12              | PB10              | PB13   | PD9  | PD13     |

| к | V <sub>DDA</sub>   | PA3                     | PA7                                                                                                                  | PB1               | PE9               | PE13              | PB11              | PB12   | PD8  | PD12     |

|   |                    |                         |                                                                                                                      |                   |                   |                   |                   |        |      | Al14601c |

Figure 3. STM32F103xx performance line LFBGA100 ballout

Figure 5. STM32F103xx performance line UFBGA100 pinout

|          |         |                 | Pins    |        |         |          |                   |                     |                            |                                                  | Alternate fu                                                               | nctions <sup>(4)</sup>   |

|----------|---------|-----------------|---------|--------|---------|----------|-------------------|---------------------|----------------------------|--------------------------------------------------|----------------------------------------------------------------------------|--------------------------|

| LFBGA100 | UFBG100 | LQFP48/UFQFPN48 | TFBGA64 | LQFP64 | LQFP100 | VFQFPN36 | Pin name          | Type <sup>(1)</sup> | I / O Level <sup>(2)</sup> | Main<br>function <sup>(3)</sup><br>(after reset) | Default                                                                    | Remap                    |

| H9       | J12     | -               | -       | -      | 57      | -        | PD10              | I/O                 | FT                         | PD10                                             | -                                                                          | USART3_CK                |

| G9       | J11     | -               | -       | -      | 58      | -        | PD11              | I/O                 | FT                         | PD11                                             | -                                                                          | USART3_CTS               |

| K10      | J10     | -               | -       | -      | 59      | -        | PD12              | I/O                 | FT                         | PD12                                             | -                                                                          | TIM4_CH1 /<br>USART3_RTS |

| J10      | H12     | -               | -       | -      | 60      | -        | PD13              | I/O                 | FT                         | PD13                                             | -                                                                          | TIM4_CH2                 |

| H10      | H11     | -               | -       | -      | 61      | -        | PD14              | I/O                 | FT                         | PD14                                             | -                                                                          | TIM4_CH3                 |

| G10      | H10     | -               | -       | -      | 62      | -        | PD15              | I/O                 | FT                         | PD15                                             | -                                                                          | TIM4_CH4                 |

| F10      | E12     | -               | F6      | 37     | 63      | -        | PC6               | I/O                 | FT                         | PC6                                              | -                                                                          | TIM3_CH1                 |

| E10      | E11     |                 | E7      | 38     | 64      | -        | PC7               | I/O                 | FT                         | PC7                                              | -                                                                          | TIM3_CH2                 |

| F9       | E10     |                 | E8      | 39     | 65      | -        | PC8               | I/O                 | FT                         | PC8                                              | -                                                                          | TIM3_CH3                 |

| E9       | D12     | -               | D8      | 40     | 66      | -        | PC9               | I/O                 | FT                         | PC9                                              | -                                                                          | TIM3_CH4                 |

| D9       | D11     | 29              | D7      | 41     | 67      | 20       | PA8               | I/O                 | FT                         | PA8                                              | USART1_CK/<br>TIM1_CH1 <sup>(9)</sup> /<br>MCO                             | -                        |

| C9       | D10     | 30              | C7      | 42     | 68      | 21       | PA9               | I/O                 | FT                         | PA9                                              | USART1_TX <sup>(9)</sup> /<br>TIM1_CH2 <sup>(9)</sup>                      | -                        |

| D10      | C12     | 31              | C6      | 43     | 69      | 22       | PA10              | I/O                 | FT                         | PA10                                             | USART1_RX <sup>(9)</sup> /<br>TIM1_CH3 <sup>(9)</sup>                      | -                        |

| C10      | B12     | 32              | C8      | 44     | 70      | 23       | PA11              | I/O                 | FT                         | PA11                                             | USART1_CTS/<br>CANRX <sup>(9)</sup> /<br>USBDM/<br>TIM1_CH4 <sup>(9)</sup> | -                        |

| B10      | A12     | 33              | B8      | 45     | 71      | 24       | PA12              | I/O                 | FT                         | PA12                                             | USART1_RTS/<br>CANTX <sup>(9)</sup><br>/USBDP<br>TIM1_ETR <sup>(9)</sup>   | -                        |

| A10      | A11     | 34              | A8      | 46     | 72      | 25       | PA13              | I/O                 | FT                         | JTMS/SWDIO                                       | -                                                                          | PA13                     |

| F8       | C11     | -               | -       | -      | 73      | -        |                   | ١                   | lot c                      | connected                                        |                                                                            | -                        |

| E6       | F11     | 35              | D5      | 47     | 74      | 26       | V <sub>SS_2</sub> | S                   | -                          | V <sub>SS_2</sub>                                | -                                                                          | -                        |

| F6       | G11     | 36              | E5      | 48     | 75      | 27       | V <sub>DD_2</sub> | S                   | -                          | V <sub>DD_2</sub>                                | -                                                                          | -                        |

### 5 Electrical characteristics

#### 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean±3ơ).

#### 5.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 2 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

#### 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 5.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in *Figure 12*.

#### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 13*.

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| Т <sub>Ј</sub>   | Maximum junction temperature | 150         | °C   |

### 5.3 Operating conditions

### 5.3.1 General operating conditions

| Symbol                          | Parameter                                                           | -                                 | Conditions                                             | Min  | Мах                      | Unit |

|---------------------------------|---------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------|------|--------------------------|------|

| Symbol                          |                                                                     | ,                                 | Conditions                                             |      | WIGA                     | Onit |

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                        |                                   | -                                                      | 0    | 72                       |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                       | -                                 |                                                        | 0    | 36                       | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                       |                                   | -                                                      | 0    | 72                       |      |

| $V_{DD}$                        | Standard operating voltage                                          |                                   | -                                                      | 2    | 3.6                      |      |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC not used)                          | Must be                           | the same potential                                     | 2    | 3.6                      | v    |

| V DDA                           | Analog operating voltage<br>(ADC used)                              | as V <sub>DD</sub> <sup>(2)</sup> |                                                        | 2.4  | 3.6                      | v    |

| $V_{BAT}$                       | Backup operating voltage                                            | -                                 |                                                        | 1.8  | 3.6                      |      |

|                                 |                                                                     | Standard IO                       |                                                        | -0.3 | V <sub>DD</sub> +<br>0.3 |      |

| V <sub>IN</sub>                 | I/O input voltage                                                   | FT IO <sup>(3)</sup>              | $2 \text{ V} < \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3 | -0.3 5.5                 |      |

|                                 |                                                                     |                                   | V <sub>DD</sub> = 2 V                                  | -0.3 | 5.2                      |      |

|                                 |                                                                     | BOOT0                             |                                                        | 0    | 5.5                      |      |

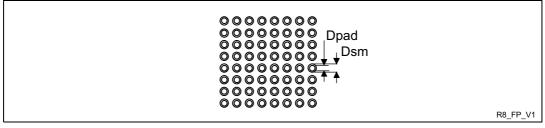

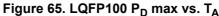

|                                 |                                                                     | LFBGA100                          |                                                        | -    | 454                      |      |

|                                 |                                                                     | LQFP100                           |                                                        | -    | 434                      |      |

|                                 |                                                                     | UFBGA100                          |                                                        | -    | 339                      |      |

| р                               | Power dissipation at $T_A =$                                        | TFBGA6                            | 4                                                      | -    | 308                      | m\\/ |

| P <sub>D</sub>                  | 85 °C for suffix 6 or $T_A =$<br>105 °C for suffix 7 <sup>(4)</sup> | LQFP64                            |                                                        | -    | 444                      | mW   |

|                                 |                                                                     | LQFP48                            |                                                        | -    | 363                      |      |

|                                 |                                                                     | UFQFPN                            | 148                                                    | -    | 624                      |      |

|                                 |                                                                     | VFQFPN                            | 36                                                     | -    | 1000                     |      |

#### Table 9. General operating conditions

| Symbol          | Parameter                       | Conditions                          | £                 | Max                    | Unit                    |      |

|-----------------|---------------------------------|-------------------------------------|-------------------|------------------------|-------------------------|------|

| Symbol          | Parameter                       | Conditions                          | f <sub>HCLK</sub> | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                                 |                                     | 72 MHz            | 30                     | 32                      |      |

|                 |                                 |                                     | 48 MHz            | 20                     | 20.5                    |      |

|                 |                                 | External clock <sup>(2)</sup> , all | 36 MHz            | 15.5                   | 16                      |      |

|                 | Supply current in<br>Sleep mode | peripherals enabled                 | 24 MHz            | 11.5                   | 12                      | mA   |

|                 |                                 |                                     | 16 MHz            | 8.5                    | 9                       |      |

|                 |                                 |                                     | 8 MHz             | 5.5                    | 6                       |      |

| I <sub>DD</sub> |                                 |                                     | 72 MHz            | 7.5                    | 8                       |      |

|                 |                                 |                                     | 48 MHz            | 6                      | 6.5                     |      |

|                 |                                 | External clock <sup>(2)</sup> , all | 36 MHz            | 5                      | 5.5                     |      |

|                 |                                 | peripherals disabled                | 24 MHz            | 4.5                    | 5                       |      |

|                 |                                 |                                     | 16 MHz            | 4                      | 4.5                     |      |

|                 |                                 |                                     | 8 MHz             | 3                      | 4                       |      |

## Table 15. Maximum current consumption in Sleep mode, code running from Flash or RAM

1. Based on characterization, tested in production at  $V_{\text{DD}\ \text{max}},\,f_{\text{HCLK}}$  max with peripherals enabled.

2. External clock is 8 MHz and PLL is on when  $f_{HCLK}$  > 8 MHz.

| Symbol                              | Parameter      | Conditions                       | -                       | Min | Тур | Max | Unit |

|-------------------------------------|----------------|----------------------------------|-------------------------|-----|-----|-----|------|

|                                     |                |                                  | T <sub>A</sub> = 50 °C  | -   | 1.5 | -   |      |

|                                     |                |                                  | T <sub>A</sub> = 25 °C  | -   | 2.5 | -   |      |

|                                     | ) Startup time | V <sub>DD</sub> is<br>stabilized | T <sub>A</sub> = 10 °C  | -   | 4   | -   |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> |                |                                  | T <sub>A</sub> = 0 °C   | -   | 6   | -   |      |

| <sup>I</sup> SU(LSE)`´              |                |                                  | T <sub>A</sub> = -10 °C | -   | 10  | -   | S    |

|                                     |                |                                  | T <sub>A</sub> = -20 °C | -   | 17  | -   |      |

|                                     |                |                                  | T <sub>A</sub> = -30 °C | -   | 32  | -   |      |

|                                     |                |                                  | T <sub>A</sub> = -40 °C | -   | 60  | -   |      |

Table 23. LSE oscillator characteristics ( $f_{LSE} = 32.768 \text{ kHz}$ )<sup>(1) (2)</sup> (continued)

1. Guaranteed based on test during characterization.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

Note: For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ .

is the series combination of  $C_{L1}$  and  $C_{L2}$ . Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L = 6 \text{ pF}$ , and  $C_{stray} = 2 \text{ pF}$ , then  $C_{L1} = C_{L2} = 8 \text{ pF}$ .

Figure 25. Typical application with a 32.768 kHz crystal

#### 5.3.7 Internal clock source characteristics

The parameters given in *Table 24* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

DocID13587 Rev 17

#### 5.3.12 I/O current injection characteristics

As a general rule, current injection to the I/O pins, due to external voltage below  $V_{SS}$  or above  $V_{DD}$  (for standard, 3 V-capable I/O pins) should be avoided during normal product operation. However, in order to give an indication of the robustness of the microcontroller in cases when abnormal injection accidentally happens, susceptibility tests are performed on a sample basis during device characterization.

#### Functional susceptibilty to I/O current injection

While a simple application is executed on the device, the device is stressed by injecting current into the I/O pins programmed in floating input mode. While current is injected into the I/O pin, one at a time, the device is checked for functional failures.

The failure is indicated by an out of range parameter: ADC error above a certain limit (>5 LSB TUE), out of spec current injection on adjacent pins or other functional failure (for example reset, oscillator frequency deviation).

The test results are given in Table 34

|                  |                                                            | Functional s       |                    |      |

|------------------|------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                | Negative injection | Positive injection | Unit |

|                  | Injected current on OSC_IN32,<br>OSC_OUT32, PA4, PA5, PC13 | -0                 | +0                 |      |

| I <sub>INJ</sub> | Injected current on all FT pins                            | -5                 | +0                 | mA   |

|                  | Injected current on any other pin                          | -5                 | +5                 |      |

#### Table 34. I/O current injection susceptibility

#### **Output driving current**

The GPIOs (general-purpose inputs/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with a relaxed V<sub>OL</sub>/V<sub>OH</sub>) except PC13, PC14 and PC15 which can sink or source up to +/-3mA. When using the GPIOs PC13 to PC15 in output mode, the speed should not exceed 2 MHz with a maximum load of 30 pF.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 5.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating I<sub>VDD</sub> (see *Table 7*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating I<sub>VSS</sub> (see *Table 7*).

#### Output voltage levels

Unless otherwise specified, the parameters given in *Table 36* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                                                     | Conditions                                                 | Min                  | Max | Unit |

|-----------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------------|----------------------|-----|------|

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | CMOS port <sup>(2)</sup> ,<br>I <sub>IO</sub> = +8 mA      | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $1_{O} - 40 \text{ mA}$<br>2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4 | -   |      |

| V <sub>OL</sub> <sup>(1)</sup>    | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | TTL port <sup>(2)</sup><br>I <sub>IO</sub> =+ 8mA          | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)</sup>    | Output high level voltage for an I/O pin when 8 pins are sourced at same time | $2.7 V < V_{DD} < 3.6 V$                                   | 2.4                  | -   | V    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | l <sub>IO</sub> = +20 mA                                   | -                    | 1.3 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2.7 V < V <sub>DD</sub> < 3.6 V                            | V <sub>DD</sub> -1.3 | -   |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin when 8 pins are sunk at same time     | I <sub>IO</sub> = +6 mA                                    | -                    | 0.4 |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin when 8 pins are sourced at same time | 2 V < V <sub>DD</sub> < 2.7 V                              | V <sub>DD</sub> -0.4 | -   |      |

#### Table 36. Output voltage characteristics

The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in Table 7 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 7 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed based on test during characterization.

Figure 31. Recommended NRST pin protection

2. The reset network protects the device against parasitic resets.

The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in *Table 38*. Otherwise the reset will not be taken into account by the device.

#### 5.3.15 TIM timer characteristics

The parameters given in Table 39 are guaranteed by design.

Refer to Section 5.3.12: I/O current injection characteristics for details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output).

|                        |                                 |                               | uotorio |                         |                      |

|------------------------|---------------------------------|-------------------------------|---------|-------------------------|----------------------|

| Symbol                 | Parameter                       | Conditions                    | Min     | Мах                     | Unit                 |

| t ann                  | Timer resolution time           | -                             | 1       | -                       | t <sub>TIMxCLK</sub> |

| t <sub>res(TIM)</sub>  |                                 | f <sub>TIMxCLK</sub> = 72 MHz | 13.9    | -                       | ns                   |

| f <sub>EXT</sub>       | Timer external clock            | -                             | 0       | f <sub>TIMxCLK</sub> /2 | MHz                  |

| 'EXT                   | frequency on CH1 to CH4         | f <sub>TIMxCLK</sub> = 72 MHz | 0       | 36                      | MHz                  |

| Res <sub>TIM</sub>     | Timer resolution                | -                             | -       | 16                      | bit                  |

| +                      | 16-bit counter clock period     | -                             | 1       | 65536                   | t <sub>TIMxCLK</sub> |

| <sup>t</sup> COUNTER   | when internal clock is selected | f <sub>TIMxCLK</sub> = 72 MHz | 0.0139  | 910                     | μs                   |

| tury count             | Maximum possible count          | -                             | -       | 65536 × 65536           | t <sub>TIMxCLK</sub> |

| <sup>t</sup> MAX_COUNT |                                 | f <sub>TIMxCLK</sub> = 72 MHz | -       | 59.6                    | s                    |

Table 39. TIMx<sup>(1)</sup> characteristics

1. TIMx is used as a general term to refer to the TIM1, TIM2, TIM3 and TIM4 timers.

Figure 35. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}$ .

#### **USB** characteristics

The USB interface is USB-IF certified (Full Speed).

#### Table 43. USB startup time

| Symbol                              | Parameter                    | Мах | Unit |

|-------------------------------------|------------------------------|-----|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1   | μs   |

1. Guaranteed by design.

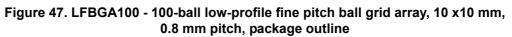

# 6.3 LFBGA100 10 x 10 mm, low-profile fine pitch ball grid array package information

1. Drawing is not to scale.

| Table 53. LFBGA100 – 100-ball low-profile fine pitch ball grid array, 10 x 10 mm, |

|-----------------------------------------------------------------------------------|

| 0.8 mm pitch, package mechanical data                                             |

| Cumb al |       | millimeters | -      |        | inches <sup>(1)</sup> |        |

|---------|-------|-------------|--------|--------|-----------------------|--------|

| Symbol  | Min   | Тур         | Мах    | Min    | Тур                   | Мах    |

| А       | -     | -           | 1.700  | -      | -                     | 0.0669 |

| A1      | 0.270 | -           | -      | 0.0106 | -                     | -      |

| A2      | -     | 0.300       | -      | -      | 0.0118                | -      |

| A4      | -     | -           | 0.800  | -      | -                     | 0.0315 |

| b       | 0.450 | 0.500       | 0.550  | 0.0177 | 0.0197                | 0.0217 |

| D       | 9.850 | 10.000      | 10.150 | 0.3878 | 0.3937                | 0.3996 |

| D1      | -     | 7.200       | -      | -      | 0.2835                | -      |

| E       | 9.850 | 10.000      | 10.150 | 0.3878 | 0.3937                | 0.3996 |

| E1      | -     | 7.200       | -      | -      | 0.2835                | -      |

| е       | -     | 0.800       | -      | -      | 0.0315                | -      |

| F       | -     | 1.400       | -      | -      | 0.0551                | -      |

| ddd     | -     | -           | 0.120  | -      | -                     | 0.0047 |

| Table 53. LFBGA100 – 100-ball low-profile fine pitch ball grid array, 10 x 10 mm, |  |

|-----------------------------------------------------------------------------------|--|

| 0.8 mm pitch, package mechanical data (continued)                                 |  |

| Symbol |     | millimeters |       |     | inches <sup>(1)</sup> |        |

|--------|-----|-------------|-------|-----|-----------------------|--------|

| Symbol | Min | Тур         | Мах   | Min | Тур                   | Max    |

| eee    | -   | -           | 0.150 | -   | -                     | 0.0059 |

| fff    | -   | -           | 0.080 | -   | -                     | 0.0031 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

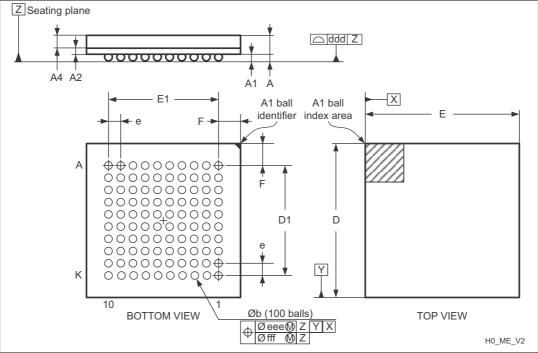

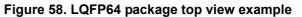

## Figure 48. LFBGA100 – 100-ball low-profile fine pitch ball grid array, 10 x 10 mm, 0.8 mm pitch, package recommended footprint

#### Table 54. LFBGA100 recommended PCB design rules (0.8 mm pitch BGA)

| Dimension         | Recommended values                                                    |

|-------------------|-----------------------------------------------------------------------|

| Pitch             | 0.8                                                                   |

| Dpad              | 0.500 mm                                                              |

| Dsm               | 0.570 mm typ. (depends on the soldermask reg-<br>istration tolerance) |

| Stencil opening   | 0.500 mm                                                              |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                         |

| Pad trace width   | 0.120 mm                                                              |

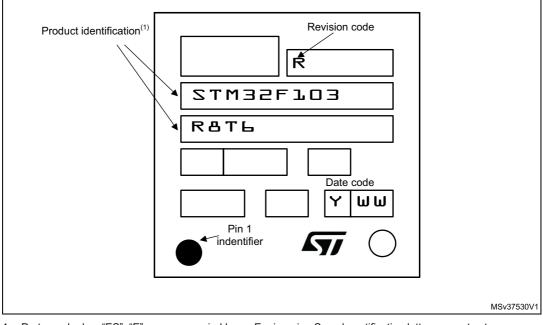

#### Marking of engineering samples

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

## Table 59. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array package mechanical data (continued)

| Cumhal | Symbol |     |       |     | inches <sup>(1)</sup> |        |

|--------|--------|-----|-------|-----|-----------------------|--------|

| Symbol | Min    | Тур | Мах   | Min | Тур                   | Мах    |

| ddd    | -      | -   | 0.080 | -   | -                     | 0.0031 |

| eee    | -      | -   | 0.150 | -   | -                     | 0.0059 |

| fff    | -      | -   | 0.050 | -   | -                     | 0.0020 |

1. Values in inches are converted from mm and rounded to 4 decimal digits.

## Figure 60. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid array package recommended footprint

#### Table 60. TFBGA64 recommended PCB design rules (0.5 mm pitch BGA)

| Dimension         | Recommended values                                               |

|-------------------|------------------------------------------------------------------|

| Pitch             | 0.5                                                              |

| Dpad              | 0.280 mm                                                         |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |

| Stencil opening   | 0.280 mm                                                         |

| Stencil thickness | Between 0.100 mm and 1.125 mm                                    |

| Pad trace width   | 0.100 mm                                                         |

Using the values obtained in *Table* 62  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 46 °C/W

- $T_{Jmax}$  = 115 °C + (46 °C/W × 134 mW) = 115 °C + 6.2 °C = 121.2 °C

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 63: Ordering information scheme*).

| Dato        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Date        | REVISION | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22-Nov-2007 | 4        | Document status promoted from preliminary data to datasheet.<br>The STM32F103xx is USB certified. Small text changes.<br><i>Power supply schemes on page 15</i> modified. Number of<br>communication peripherals corrected for STM32F103Tx and number of<br>GPIOs corrected for LQFP package in <i>Table 2: STM32F103xx</i><br><i>Main</i> function and default alternate function modified for PC14 and<br>PC15 in, <i>Note</i> 6 added and Remap column added in <i>Table</i> 5: <i>Medium-<br/>density STM32F103xx</i> pin definitions.<br>V <sub>DD</sub> -V <sub>SS</sub> ratings and <i>Note</i> 1 modified in <i>Table</i> 6: <i>Voltage</i><br><i>characteristics, Note</i> 1 modified in <i>Table</i> 7: <i>Current characteristics.</i><br><i>Note</i> 1 and <i>Note</i> 2 added in <i>Table</i> 11: <i>Embedded reset and power</i><br><i>control block characteristics.</i><br>I <sub>DD</sub> value at 72 MHz with peripherals enabled modified in <i>Table</i> 14:<br><i>Maximum current consumption in Run mode, code with data</i><br><i>processing running from RAM.</i><br>I <sub>DD</sub> value at 72 MHz with peripherals enabled modified in <i>Table</i> 15:<br><i>Maximum current consumption in Sleep mode, code running from</i><br><i>Flash or RAM on page</i> 44.<br>I <sub>DD vBAT</sub> typical value at 2.4 V modified and I <sub>DD vBAT</sub> maximum values<br>added in <i>Table</i> 16: <i>Typical and maximum current consumptions in Stop</i><br><i>and Standby modes.</i> Note added in <i>Table</i> 17: <i>on page</i> 48 and <i>Table</i> 18<br><i>on page</i> 49. ADC1 and ADC2 consumption.<br>t <sub>SU(HSE)</sub> and t <sub>SU(USE)</sub> conditions modified in <i>Table</i> 22, respectively.<br>Maximum values removed from <i>Table</i> 26: <i>Low-power mode wakeup</i><br><i>timings.</i> t <sub>RET</sub> conditions modified in <i>Table</i> 2: <i>Nigure</i> 14: <i>Power supply</i><br><i>scheme corrected.</i><br><i>Figure</i> 20: <i>Typical current consumption in Stop mode with regulator in</i><br><i>Low-power mode versus temperature</i> 4VDD = 3.3 V and 3.6 V added.<br>Note removed below <i>Figure</i> 33: SPI timing diagram - slave<br><i>mode and CPHA</i> = 1(1).<br>Details on unused pins removed from <i>General input/output</i><br><i>characteristics on page</i> 62.<br><i>Table</i> 42: <i>SPI characteristics</i> updated. <i>Table</i> 43: <i>USB startup time</i><br>added in <i>Table</i> 49: <i>ADC accuracy</i> . Note added and I <sub>kig</sub> removed in<br><i>Table</i> 46: <i>ADC ch</i> |

| 19-Apr-2011       13         07-Dec-2012       14         14-May-2013       15 | <ul> <li>Updated footnotes below Table 6: Voltage characteristics on page 37<br/>and Table 7: Current characteristics on page 37</li> <li>Updated tw min in Table 20: High-speed external user clock<br/>characteristics on page 51</li> <li>Updated startup time in Table 23: LSE oscillator characteristics (fLSE =<br/>32.768 kHz) on page 54</li> <li>Added Section 5.3.12: I/O current injection characteristics</li> <li>Updated Section 5.3.13: I/O port characteristics</li> <li>Updated Figure 59: LQFP64, 10 x 10 mm, 64-pin low-profile quad flat<br/>package outline to add pin 1 identification.</li> <li>Replaced VQFN48 package with UQFN48 in cover page packages,<br/>Table 2: STM32F103xx medium-density device features and peripheral<br/>counts, Figure 9: STM32F103xx medium-density device features and peripheral<br/>counts, Table 56: UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra<br/>fine pitch ball grid array package mechanical data, Table 63: Ordering<br/>information endown and undeted Table 60: Devicent</li> </ul> |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                | <ul> <li>Updated Figure 59: LQFP64, 10 x 10 mm, 64-pin low-profile quad flat package outline to add pin 1 identification.</li> <li>Replaced VQFN48 package with UQFN48 in cover page packages, Table 2: STM32F103xx medium-density device features and peripheral counts, Figure 9: STM32F103xx performance line UFQFPN48 pinout, Table 2: STM32F103xx medium-density device features and peripheral counts, Table 56: UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package mechanical data, Table 63: Ordering</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14-May-2013 15                                                                 | Table 2: STM32F103xx medium-density device features and peripheral counts, Figure 9: STM32F103xx performance line UFQFPN48 pinout, Table 2: STM32F103xx medium-density device features and peripheral counts, Table 56: UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array package mechanical data, Table 63: Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                | information scheme and updated Table 62: Package thermal<br>characteristics<br>Added footnote for TFBGA ADC channels in Table 2: STM32F103xx<br>medium-density device features and peripheral counts<br>Updated 'All GPIOs are high current' in Section 2.3.21: GPIOs<br>(general-purpose inputs/outputs)<br>Updated Table 5: Medium-density STM32F103xx pin definitions<br>Corrected Sigma letter in Section 5.1.1: Minimum and maximum values<br>Removed the first sentence in Section 5.3.16: Communications<br>interfaces<br>Added 'V <sub>IN</sub> ' in Table 9: General operating conditions<br>Updated first sentence in Output driving current<br>Added note 5. in Table 24: HSI oscillator characteristics<br>Updated 'V <sub>IL</sub> ' and 'V <sub>IH</sub> ' in Table 35: I/O static characteristics<br>Added notes to Figure 26: Standard I/O input characteristics - CMOS<br>port, Figure 27: Standard I/O input characteristics - TTL port, Figure 28:<br>5 V tolerant I/O input characteristics - TTL port                                      |

| Table 64 | <b>Document revision</b> | history | (continued) |

|----------|--------------------------|---------|-------------|

|          | Document revision        | matory  | (continueu) |