Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 72MHz                                                                 |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB          |

| Peripherals                | DMA, Motor Control PWM, PDR, POR, PVD, PWM, Temp Sensor, WDT          |

| Number of I/O              | 80                                                                    |

| Program Memory Size        | 128KB (128K x 8)                                                      |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                |                                                                       |

| RAM Size                   | 20K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                             |

| Data Converters            | A/D 16x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 100-UFBGA                                                             |

| Supplier Device Package    | 100-UFBGA (7x7)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f103vbi6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Introc | luction   |                                                                            |

|---|--------|-----------|----------------------------------------------------------------------------|

| 2 | Desci  | ription . |                                                                            |

|   | 2.1    | Device    | overview                                                                   |

|   | 2.2    | Full com  | npatibility throughout the family                                          |

|   | 2.3    | Overvie   | w                                                                          |

|   |        | 2.3.1     | ARM <sup>®</sup> Cortex <sup>®</sup> -M3 core with embedded Flash and SRAM |

|   |        | 2.3.2     | Embedded Flash memory14                                                    |

|   |        | 2.3.3     | CRC (cyclic redundancy check) calculation unit                             |

|   |        | 2.3.4     | Embedded SRAM                                                              |

|   |        | 2.3.5     | Nested vectored interrupt controller (NVIC)                                |

|   |        | 2.3.6     | External interrupt/event controller (EXTI)                                 |

|   |        | 2.3.7     | Clocks and startup                                                         |

|   |        | 2.3.8     | Boot modes                                                                 |

|   |        | 2.3.9     | Power supply schemes                                                       |

|   |        | 2.3.10    | Power supply supervisor                                                    |

|   |        | 2.3.11    | Voltage regulator                                                          |

|   |        | 2.3.12    | Low-power modes                                                            |

|   |        | 2.3.13    | DMA                                                                        |

|   |        | 2.3.14    | RTC (real-time clock) and backup registers                                 |

|   |        | 2.3.15    | Timers and watchdogs 17                                                    |

|   |        | 2.3.16    | I <sup>2</sup> C bus                                                       |

|   |        | 2.3.17    | Universal synchronous/asynchronous receiver transmitter (USART) 19         |

|   |        | 2.3.18    | Serial peripheral interface (SPI) 19                                       |

|   |        | 2.3.19    | Controller area network (CAN) 19                                           |

|   |        | 2.3.20    | Universal serial bus (USB) 19                                              |

|   |        | 2.3.21    | GPIOs (general-purpose inputs/outputs)                                     |

|   |        | 2.3.22    | ADC (analog-to-digital converter)                                          |

|   |        | 2.3.23    | Temperature sensor                                                         |

|   |        | 2.3.24    | Serial wire JTAG debug port (SWJ-DP)                                       |

| 3 | Pinou  | its and   | pin description                                                            |

| 4 | Memo   | ory map   | ping                                                                       |

This hardware block provides flexible interrupt management features with minimal interrupt latency.

#### 2.3.6 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 80 GPIOs can be connected to the 16 external interrupt lines.

#### 2.3.7 Clocks and startup

System clock selection is performed on startup, however the internal RC 8 MHz oscillator is selected as default CPU clock on reset. An external 4-16 MHz clock can be selected, in which case it is monitored for failure. If failure is detected, the system automatically switches back to the internal RC oscillator. A software interrupt is generated if enabled. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example on failure of an indirectly used external crystal, resonator or oscillator).

Several prescalers allow the configuration of the AHB frequency, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the AHB and the high-speed APB domains is 72 MHz. The maximum allowed frequency of the low-speed APB domain is 36 MHz. See *Figure 2* for details on the clock tree.

#### 2.3.8 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from User Flash

- Boot from System Memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1. For further details please refer to AN2606.

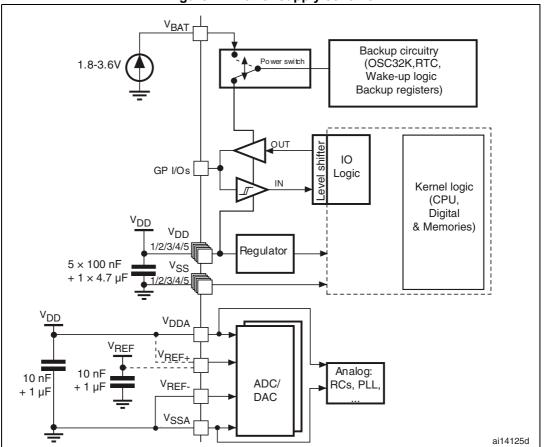

#### 2.3.9 Power supply schemes

- V<sub>DD</sub> = 2.0 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through V<sub>DD</sub> pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 2.0 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 2.4 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

- V<sub>BAT</sub> = 1.8 to 3.6 V: power supply for RTC, external clock 32 kHz oscillator and backup registers (through power switch) when V<sub>DD</sub> is not present.

For more details on how to connect power pins, refer to *Figure 14: Power supply scheme*.

#### 2.3.10 Power supply supervisor

The device has an integrated power-on reset (POR)/power-down reset (PDR) circuitry. It is always active, and ensures proper operation starting from/down to 2 V. The device remains

# 5 Electrical characteristics

# 5.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

#### 5.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean±3ơ).

## 5.1.2 Typical values

Unless otherwise specified, typical data are based on T<sub>A</sub> = 25 °C, V<sub>DD</sub> = 3.3 V (for the 2 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

## 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

## 5.1.4 Loading capacitor

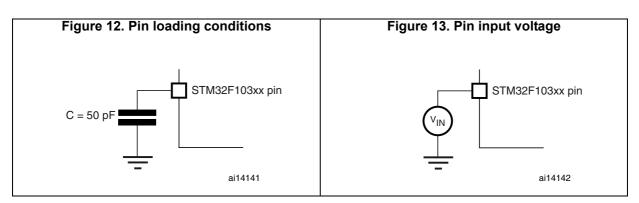

The loading conditions used for pin parameter measurement are shown in *Figure 12*.

#### 5.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in *Figure 13*.

# 5.1.6 Power supply scheme

Figure 14. Power supply scheme

**Caution:** In *Figure 14*, the 4.7  $\mu$ F capacitor must be connected to V<sub>DD3</sub>.

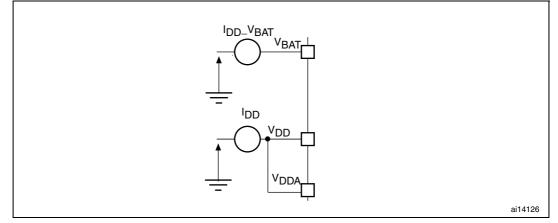

## 5.1.7 Current consumption measurement

#### Figure 15. Current consumption measurement scheme

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| Т <sub>Ј</sub>   | Maximum junction temperature | 150         | °C   |

# 5.3 Operating conditions

# 5.3.1 General operating conditions

| Symbol                          | Parameter                                                                              | -                     | Conditions                                             | Min  | Мах                      | Unit |

|---------------------------------|----------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------|------|--------------------------|------|

| Symbol                          |                                                                                        | ,                     | Conditions                                             |      | WIGA                     | Onit |

| f <sub>HCLK</sub>               | Internal AHB clock frequency                                                           |                       | -                                                      | 0    | 72                       |      |

| f <sub>PCLK1</sub>              | Internal APB1 clock frequency                                                          |                       | -                                                      | 0    | 36                       | MHz  |

| f <sub>PCLK2</sub>              | Internal APB2 clock frequency                                                          |                       | -                                                      | 0    | 72                       |      |

| $V_{DD}$                        | Standard operating voltage                                                             |                       | -                                                      | 2    | 3.6                      |      |

| V <sub>DDA</sub> <sup>(1)</sup> | Analog operating voltage<br>(ADC not used)                                             | Must be               | the same potential                                     | 2    | 3.6                      | v    |

| V DDA                           | A <sup>(1)</sup> Analog operating voltage (ADC used) as V <sub>DD</sub> <sup>(2)</sup> |                       | 2.4                                                    | 3.6  | V                        |      |

| $V_{BAT}$                       | Backup operating voltage                                                               |                       | -                                                      | 1.8  | 3.6                      |      |

|                                 | I/O input voltage FT IO <sup>(3)</sup>                                                 | Standard IO           |                                                        | -0.3 | V <sub>DD</sub> +<br>0.3 |      |

| V <sub>IN</sub>                 |                                                                                        |                       | $2 \text{ V} < \text{V}_{\text{DD}} \le 3.6 \text{ V}$ | -0.3 | 5.5                      | V    |

|                                 |                                                                                        | V <sub>DD</sub> = 2 V | -0.3                                                   | 5.2  |                          |      |

|                                 |                                                                                        | BOOT0                 | ·                                                      | 0    | 5.5                      |      |

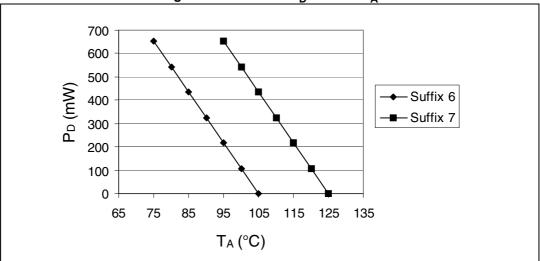

|                                 |                                                                                        | LFBGA100              |                                                        | -    | 454                      |      |

|                                 |                                                                                        | LQFP100               |                                                        | -    | 434                      |      |

|                                 |                                                                                        | UFBGA100              |                                                        | -    | 339                      |      |

| Р                               | Power dissipation at $T_A =$                                                           | TFBGA64               |                                                        | -    | 308                      | m\\/ |

| P <sub>D</sub>                  | 85 °C for suffix 6 or $T_A =$<br>105 °C for suffix 7 <sup>(4)</sup>                    | LQFP64                |                                                        | -    | 444                      | mW   |

|                                 |                                                                                        | LQFP48                |                                                        | -    | 363                      |      |

|                                 |                                                                                        | UFQFPN                | 148                                                    | -    | 624                      |      |

|                                 |                                                                                        | VFQFPN                | 36                                                     | -    | 1000                     |      |

#### Table 9. General operating conditions

# 5.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 11* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                               | Parameter                                        | Conditions                  | Min  | Тур  | Max  | Unit |  |  |  |

|--------------------------------------|--------------------------------------------------|-----------------------------|------|------|------|------|--|--|--|

|                                      |                                                  | PLS[2:0]=000 (rising edge)  | 2.1  | 2.18 | 2.26 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=000 (falling edge) | 2    | 2.08 | 2.16 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=001 (rising edge)  | 2.19 | 2.28 | 2.37 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=001 (falling edge) | 2.09 | 2.18 | 2.27 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=010 (rising edge)  | 2.28 | 2.38 | 2.48 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=010 (falling edge) | 2.18 | 2.28 | 2.38 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=011 (rising edge)  | 2.38 | 2.48 | 2.58 |      |  |  |  |

|                                      | Programmable voltage<br>detector level selection | PLS[2:0]=011 (falling edge) | 2.28 | 2.38 | 2.48 | V    |  |  |  |

| V <sub>PVD</sub>                     |                                                  | PLS[2:0]=100 (rising edge)  | 2.47 | 2.58 | 2.69 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=100 (falling edge) | 2.37 | 2.48 | 2.59 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=101 (rising edge)  | 2.57 | 2.68 | 2.79 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=101 (falling edge) | 2.47 | 2.58 | 2.69 |      |  |  |  |

|                                      |                                                  | PLS[2:0]=110 (rising edge)  | 2.66 | 2.78 | 2.9  |      |  |  |  |

|                                      |                                                  | PLS[2:0]=110 (falling edge) | 2.56 | 2.68 | 2.8  |      |  |  |  |

|                                      |                                                  | PLS[2:0]=111 (rising edge)  | 2.76 | 2.88 | 3    |      |  |  |  |

|                                      |                                                  | PLS[2:0]=111 (falling edge) | 2.66 | 2.78 | 2.9  |      |  |  |  |

| V <sub>PVDhyst</sub> <sup>(2)</sup>  | PVD hysteresis                                   | -                           | -    | 100  | -    | mV   |  |  |  |

|                                      | Power on/power down                              | Falling edge 1.8            |      | 1.88 | 1.96 | V    |  |  |  |

| V <sub>POR/PDR</sub>                 | reset threshold                                  | Rising edge                 | 1.84 | 1.92 | 2.0  | - V  |  |  |  |

| V <sub>PDRhyst</sub> <sup>(2)</sup>  | PDR hysteresis                                   | -                           | -    | 40   | -    | mV   |  |  |  |

| T <sub>RSTTEMPO</sub> <sup>(2)</sup> | Reset temporization                              | -                           | 1    | 2.5  | 4.5  | ms   |  |  |  |

1. The product behavior is guaranteed by design down to the minimum  $V_{\mbox{POR/PDR}}$  value.

2. Guaranteed by design.

|                                |                                                                                                                                                 |                                                                                                        | Тур <sup>(1)</sup> |                                              |                                              | Мах                |                            |      |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------|----------------------------------------------|--------------------|----------------------------|------|

| Symbol                         | Parameter                                                                                                                                       | ameter Conditions                                                                                      |                    | V <sub>DD</sub> /V <sub>BAT</sub><br>= 2.4 V | V <sub>DD</sub> /V <sub>BAT</sub><br>= 3.3 V |                    | T <sub>A</sub> =<br>105 °C | Unit |

| Supply current<br>in Stop mode | Regulator in Run mode, low-speed<br>and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog)        | -                                                                                                      | 23.5               | 24                                           | 200                                          | 370                |                            |      |

|                                | Regulator in Low-power mode, low-<br>speed and high-speed internal RC<br>oscillators and high-speed oscillator<br>OFF (no independent watchdog) | -                                                                                                      | 13.5               | 14                                           | 180                                          | 340                |                            |      |

|                                | Low-speed internal RC oscillator and<br>independent watchdog ON                                                                                 | -                                                                                                      | 2.6                | 3.4                                          | -                                            | -                  | μA                         |      |

|                                | Low-speed internal RC oscillator<br>ON, independent watchdog OFF                                                                                | -                                                                                                      | 2.4                | 3.2                                          | -                                            | -                  |                            |      |

|                                | mode                                                                                                                                            | Low-speed internal RC oscillator and<br>independent watchdog OFF, low-<br>speed oscillator and RTC OFF | -                  | 1.7                                          | 2                                            | 4                  | 5                          |      |

| I <sub>DD_VBAT</sub>           | Backup<br>domain supply<br>current                                                                                                              | Low-speed oscillator and RTC ON                                                                        | 0.9                | 1.1                                          | 1.4                                          | 1.9 <sup>(2)</sup> | 2.2                        |      |

Table 16. Typical and maximum current consumptions in Stop and Standby modes

1. Typical values are measured at  $T_A$  = 25 °C.

2. Guaranteed based on test during characterization.

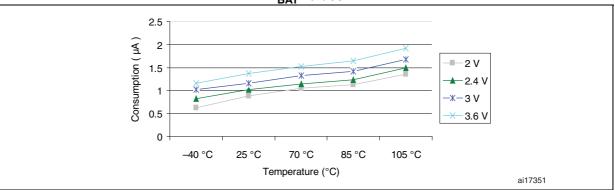

# Figure 18. Typical current consumption on $V_{BAT}$ with RTC on versus temperature at different $V_{BAT}$ values

#### On-chip peripheral current consumption

The current consumption of the on-chip peripherals is given in *Table 19*. The MCU is placed under the following conditions:

- all I/O pins are in input mode with a static value at  $V_{DD}$  or  $V_{SS}$  (no load)

- all peripherals are disabled unless otherwise mentioned

- the given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- ambient operating temperature and V<sub>DD</sub> supply voltage conditions summarized in Table 6

| Perip               | herals                   | μA/MHz |

|---------------------|--------------------------|--------|

|                     | DMA1                     | 16.53  |

| AHB (up to 72 MHz)  | BusMatrix <sup>(1)</sup> | 8.33   |

|                     | APB1-Bridge              | 10.28  |

|                     | TIM2                     | 32.50  |

|                     | TIM3                     | 31.39  |

|                     | TIM4                     | 31.94  |

|                     | SPI2                     | 4.17   |

|                     | USART2                   | 12.22  |

|                     | USART3                   | 12.22  |

| APB1 (up to 36 MHz) | I2C1                     | 10.00  |

|                     | I2C2                     | 10.00  |

|                     | USB                      | 17.78  |

|                     | CAN1                     | 18.06  |

|                     | WWDG                     | 2.50   |

|                     | PWR                      | 1.67   |

|                     | BKP                      | 2.50   |

|                     | IWDG                     | 11.67  |

#### Table 19. Peripheral current consumption

| Symbol                              | Parameter    | Conditions                       | -                       | Min | Тур | Max | Unit |  |  |

|-------------------------------------|--------------|----------------------------------|-------------------------|-----|-----|-----|------|--|--|

|                                     | Startup time |                                  | T <sub>A</sub> = 50 °C  | -   | 1.5 | -   |      |  |  |

|                                     |              |                                  | T <sub>A</sub> = 25 °C  | -   | 2.5 | -   |      |  |  |

|                                     |              | V <sub>DD</sub> is<br>stabilized | T <sub>A</sub> = 10 °C  | -   | 4   | -   | S S  |  |  |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> |              |                                  | T <sub>A</sub> = 0 °C   | -   | 6   | -   |      |  |  |

| <sup>I</sup> SU(LSE)`´              |              |                                  | T <sub>A</sub> = -10 °C | -   | 10  | -   |      |  |  |

|                                     |              |                                  | T <sub>A</sub> = -20 °C | -   | 17  | -   |      |  |  |

|                                     |              |                                  | T <sub>A</sub> = -30 °C | -   | 32  | -   |      |  |  |

|                                     |              |                                  | T <sub>A</sub> = -40 °C | -   | 60  | -   |      |  |  |

Table 23. LSE oscillator characteristics ( $f_{LSE} = 32.768 \text{ kHz}$ )<sup>(1) (2)</sup> (continued)

1. Guaranteed based on test during characterization.

2. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

3. t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

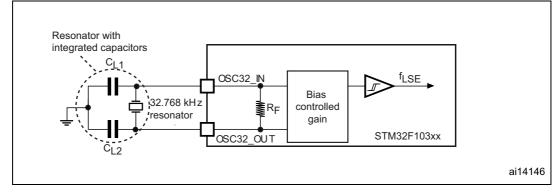

Note: For  $C_{L1}$  and  $C_{L2}$  it is recommended to use high-quality ceramic capacitors in the 5 pF to 15 pF range selected to match the requirements of the crystal or resonator.  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ .

is the series combination of  $C_{L1}$  and  $C_{L2}$ . Load capacitance  $C_L$  has the following formula:  $C_L = C_{L1} \times C_{L2} / (C_{L1} + C_{L2}) + C_{stray}$  where  $C_{stray}$  is the pin capacitance and board or trace PCB-related capacitance. Typically, it is between 2 pF and 7 pF.

**Caution:** To avoid exceeding the maximum value of  $C_{L1}$  and  $C_{L2}$  (15 pF) it is strongly recommended to use a resonator with a load capacitance  $C_L \le 7$  pF. Never use a resonator with a load capacitance of 12.5 pF.

**Example:** if you choose a resonator with a load capacitance of  $C_L = 6 \text{ pF}$ , and  $C_{stray} = 2 \text{ pF}$ , then  $C_{L1} = C_{L2} = 8 \text{ pF}$ .

Figure 25. Typical application with a 32.768 kHz crystal

#### 5.3.7 Internal clock source characteristics

The parameters given in *Table 24* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol                              | Parameter                                           | Тур | Unit |

|-------------------------------------|-----------------------------------------------------|-----|------|

| t <sub>WUSLEEP</sub> <sup>(1)</sup> | Wakeup from Sleep mode                              | 1.8 |      |

|                                     | Wakeup from Stop mode (regulator in run mode)       | 3.6 |      |

| twustop <sup>(1)</sup>              | Wakeup from Stop mode (regulator in low-power mode) | 5.4 | μs   |

| t <sub>WUSTDBY</sub> <sup>(1)</sup> | Wakeup from Standby mode                            | 50  |      |

Table 26. Low-power mode wakeup timings

1. The wakeup times are measured from the wakeup event to the point in which the user application code reads the first instruction.

# 5.3.8 PLL characteristics

The parameters given in *Table 27* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 9*.

| Symbol               | Parameter                      |                    | Unit |                    |      |

|----------------------|--------------------------------|--------------------|------|--------------------|------|

|                      | Parameter                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

| f <sub>PLL_IN</sub>  | PLL input clock <sup>(2)</sup> | 1                  | 8.0  | 25                 | MHz  |

|                      | PLL input clock duty cycle     | 40                 | -    | 60                 | %    |

| f <sub>PLL_OUT</sub> | PLL multiplier output clock    | 16                 | -    | 72                 | MHz  |

| t <sub>LOCK</sub>    | PLL lock time                  | -                  | -    | 200                | μs   |

| Jitter               | Cycle-to-cycle jitter          | -                  | -    | 300                | ps   |

Table 27. PLL characteristics

1. Guaranteed based on test during characterization.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{PLL_OUT}$ .

# 5.3.9 Memory characteristics

#### **Flash memory**

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

| Table 28. Flash memory characteristics |

|----------------------------------------|

|----------------------------------------|

| Symbol             | Parameter               | Conditions                      | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------|-------------------------|---------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>  | 16-bit programming time | T <sub>A</sub> = -40 to +105 °C | 40                 | 52.5 | 70                 | μs   |

| t <sub>ERASE</sub> | Page (1 KB) erase time  | $T_A = -40$ to +105 °C          | 20                 | -    | 40                 | ms   |

| t <sub>ME</sub>    | Mass erase time         | $T_A = -40$ to +105 °C          | 20                 | -    | 40                 | 1115 |

| Symbol            | Parameter           | Conditions                                                                             | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |  |

|-------------------|---------------------|----------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|--|

|                   | Supply current      | Read mode<br>f <sub>HCLK</sub> = 72 MHz with 2 wait<br>states, V <sub>DD</sub> = 3.3 V | -                  | -   | 20                 | mA   |  |

| I <sub>DD</sub>   |                     | Write / Erase modes<br>f <sub>HCLK</sub> = 72 MHz, V <sub>DD</sub> = 3.3 V             | -                  | -   | 5                  | 5    |  |

|                   |                     | Power-down mode / Halt,<br>$V_{DD}$ = 3.0 to 3.6 V                                     | -                  | -   | 50                 | μA   |  |

| V <sub>prog</sub> | Programming voltage | -                                                                                      | 2                  | -   | 3.6                | V    |  |

| Table 28. Flash memory | / characteristics | (continued) |

|------------------------|-------------------|-------------|

|------------------------|-------------------|-------------|

1. Guaranteed by design.

| Symbol           | Parameter      | Conditions                                                                              | Value              |     |     | l lusit |

|------------------|----------------|-----------------------------------------------------------------------------------------|--------------------|-----|-----|---------|

| Symbol           | Farameter      | Parameter Conditions                                                                    | Min <sup>(1)</sup> | Тур | Max | Unit    |

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                 | -   | -   | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                 | -   | -   |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                 | -   | -   | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                 | -   | -   |         |

| Table 29. Flash memory endurance and data retention |

|-----------------------------------------------------|

|-----------------------------------------------------|

1. Guaranteed based on test during characterization.

2. Cycling performed over the whole temperature range.

## 5.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- **Electrostatic discharge (ESD)** (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- **FTB**: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 30*. They are based on the EMS levels and classes defined in application note AN1709.

## 5.3.16 Communications interfaces

# I<sup>2</sup>C interface characteristics

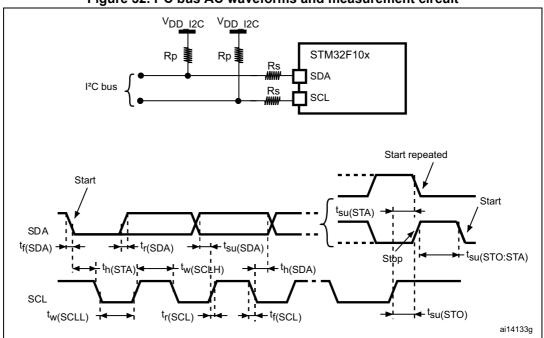

The STM32F103xx performance line  $I^2C$  interface meets the requirements of the standard  $I^2C$  communication protocol with the following restrictions: the I/O pins SDA and SCL are mapped to are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

The I<sup>2</sup>C characteristics are described in *Table 40*. Refer also to *Section 5.3.12: I/O current injection characteristics* for more details on the input/output alternate function characteristics (SDA and SCL).

| Symbol                                     | Parameter                                                            | Standard mode<br>I <sup>2</sup> C <sup>(1)(2)</sup> |                     | Fast mode | Unit               |    |  |

|--------------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------|---------------------|-----------|--------------------|----|--|

|                                            |                                                                      | Min                                                 | Max                 | Min       | Max                |    |  |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                                                   | 4.7                                                 | -                   | 1.3       | -                  |    |  |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                                                  | 4.0                                                 | -                   | 0.6       |                    | μs |  |

| t <sub>su(SDA)</sub>                       | SDA setup time                                                       | 250                                                 | -                   | 100       | -                  |    |  |

| t <sub>h(SDA)</sub>                        | SDA data hold time                                                   | -                                                   | 3450 <sup>(3)</sup> | -         | 900 <sup>(3)</sup> |    |  |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                                                | -                                                   | 1000                | -         | 300                | ns |  |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                                                | -                                                   | 300                 | -         | 300                |    |  |

| t <sub>h(STA)</sub>                        | Start condition hold time                                            | 4.0                                                 | -                   | 0.6       | -                  |    |  |

| t <sub>su(STA)</sub>                       | Repeated Start condition setup time                                  | 4.7                                                 | -                   | 0.6       | -                  | μs |  |

| t <sub>su(STO)</sub>                       | Stop condition setup time                                            | 4.0                                                 | -                   | 0.6       | -                  | μs |  |

| t <sub>w(STO:STA)</sub>                    | Stop to Start condition time (bus free)                              | 4.7                                                 | -                   | 1.3       | -                  | μs |  |

| Cb                                         | Capacitive load for each bus line                                    | -                                                   | 400                 | -         | 400                | pF |  |

| t <sub>SP</sub>                            | Pulse width of spikes that<br>are suppressed by the<br>analog filter | 0                                                   | 50 <sup>(4)</sup>   | 0         | 50 <sup>(4)</sup>  | ns |  |

1. Guaranteed by design.

f<sub>PCLK1</sub> must be at least 2 MHz to achieve standard mode I<sup>2</sup>C frequencies. It must be at least 4 MHz to achieve fast mode I<sup>2</sup>C frequencies. It must be a multiple of 10 MHz to reach the 400 kHz maximum I2C fast mode clock.

3. The maximum Data hold time has only to be met if the interface does not stretch the low period of SCL signal.

4. The minimum width of the spikes filtered by the analog filter is above  $t_{SP}(max)$ .

Figure 32. I<sup>2</sup>C bus AC waveforms and measurement circuit

1. Measurement points are done at CMOS levels:  $0.3V_{DD}$  and  $0.7V_{DD}.$

2. Rs = Series protection resistors, Rp = Pull-up resistors,  $V_{DD_{12C}}$  = I2C bus supply.

| f (kUz)                | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801E                  |

| 300                    | 0x8028                  |

| 200                    | 0x803C                  |

| 100                    | 0x00B4                  |

| 50                     | 0x0168                  |

| 20                     | 0x0384                  |

# Table 41. SCL frequency ( $f_{PCLK1}$ = 36 MHz., $V_{DD_{-12C}}$ = 3.3 V)<sup>(1)(2)</sup>

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed,

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed ±2%. These variations depend on the accuracy of the external components used to design the application.

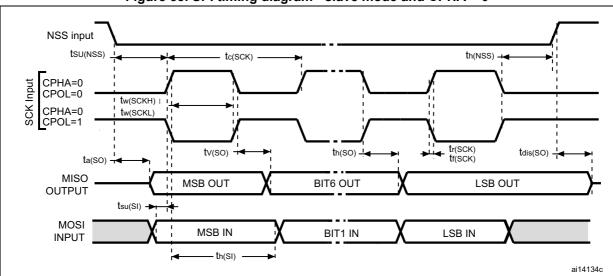

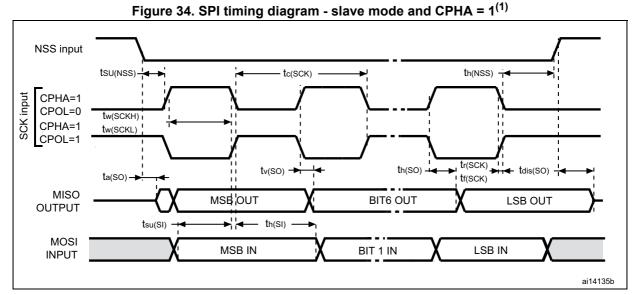

Figure 33. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}.$

#### 5.3.18 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 46* are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DDA}$  supply voltage conditions summarized in *Table 9*.

Note: It is recommended to perform a calibration after each power-up.

| Symbol                           | Parameter                                          | Conditions                                            | Min                                                         | Тур                | Max                | Unit               |

|----------------------------------|----------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------|--------------------|--------------------|--------------------|

| V <sub>DDA</sub>                 | Power supply                                       | -                                                     | 2.4                                                         | -                  | 3.6                | V                  |

| V <sub>REF+</sub>                | Positive reference voltage                         | -                                                     | 2.4                                                         | -                  | V <sub>DDA</sub>   | V                  |

| I <sub>VREF</sub>                | Current on the V <sub>REF</sub> input pin          | -                                                     | -                                                           | 160 <sup>(1)</sup> | 220 <sup>(1)</sup> | μA                 |

| f <sub>ADC</sub>                 | ADC clock frequency                                | -                                                     | 0.6                                                         | -                  | 14                 | MHz                |

| f <sub>S</sub> <sup>(2)</sup>    | Sampling rate                                      | -                                                     | 0.05                                                        | -                  | 1                  | MHz                |

| e (2)                            |                                                    | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 823                | kHz                |

| f <sub>TRIG</sub> <sup>(2)</sup> | External trigger frequency                         |                                                       | -                                                           | -                  | 17                 | 1/f <sub>ADC</sub> |

| V <sub>AIN</sub> <sup>(3)</sup>  | Conversion voltage range                           |                                                       | 0 (V <sub>SSA</sub> or V <sub>REF-</sub><br>tied to ground) | -                  | V <sub>REF+</sub>  | V                  |

| R <sub>AIN</sub> <sup>(2)</sup>  | External input impedance                           | See <i>Equation 1</i> and <i>Table 47</i> for details | -                                                           | -                  | 50                 | kΩ                 |

| R <sub>ADC</sub> <sup>(2)</sup>  | Sampling switch resistance                         | -                                                     | -                                                           | -                  | 1                  | kΩ                 |

| C <sub>ADC</sub> <sup>(2)</sup>  | Internal sample and hold capacitor                 | -                                                     | -                                                           | -                  | 8                  | pF                 |

| + (2)                            | Calibration time                                   | f <sub>ADC</sub> = 14 MHz                             | 5.9                                                         |                    | μs                 |                    |

| t <sub>CAL</sub> <sup>(2)</sup>  |                                                    | -                                                     | 83                                                          |                    | 1/f <sub>ADC</sub> |                    |

| <b>↓</b> (2)                     | Injection trigger conversion                       | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 0.214              | μs                 |

| $t_{lat}^{(2)}$                  | latency                                            | -                                                     | -                                                           | -                  | 3 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| <b>↓</b> (2)                     | Regular trigger conversion                         | f <sub>ADC</sub> = 14 MHz                             | -                                                           | -                  | 0.143              | μs                 |

| t <sub>latr</sub> (2)            | latency                                            | -                                                     | -                                                           | -                  | 2 <sup>(4)</sup>   | 1/f <sub>ADC</sub> |

| ts <sup>(2)</sup>                | Compling time                                      | f <sub>ADC</sub> = 14 MHz                             | 0.107                                                       | -                  | 17.1               | μs                 |

| ι <sub>S</sub> `-΄               | Sampling time                                      | -                                                     | 1.5                                                         | -                  | 239.5              | 1/f <sub>ADC</sub> |

| t <sub>STAB</sub> <sup>(2)</sup> | Power-up time                                      | -                                                     | 0                                                           | 0                  | 1                  | μs                 |

|                                  | Total conversion time                              | f <sub>ADC</sub> = 14 MHz                             | 1                                                           | -                  | 18                 | μs                 |

| t <sub>CONV</sub> <sup>(2)</sup> | Total conversion time<br>(including sampling time) | -                                                     | 14 to 252 (t <sub>S</sub> for sa<br>successive approx       |                    | 12.5 for           | 1/f <sub>ADC</sub> |

1. Guaranteed based on test during characterization.

2. Guaranteed by design.

In devices delivered in VFQFPN and LQFP packages, V<sub>REF+</sub> is internally connected to V<sub>DDA</sub> and V<sub>REF-</sub> is internally connected to V<sub>SSA</sub>. Devices that come in the TFBGA64 package have a V<sub>REF+</sub> pin but no V<sub>REF-</sub> pin (V<sub>REF-</sub> is internally connected to V<sub>SSA</sub>), see *Table 5* and *Figure 7*.

4. For external triggers, a delay of 1/f<sub>PCLK2</sub> must be added to the latency specified in *Table 46*.

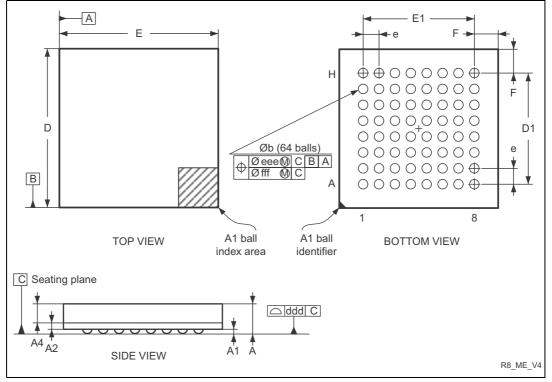

# 6.7 TFBGA64 5 x 5 mm, thin profile fine pitch package information

Figure 59. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch thin profile fine pitch ball grid array package outline

1. Drawing is not to scale.

| Table 59. TFBGA64 – 64-ball, 5 x 5 mm, 0.5 mm pitch, thin profile fine pitch ball grid |

|----------------------------------------------------------------------------------------|

| array package mechanical data                                                          |

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Мах    |

| А      | -           | -     | 1.200 | -                     | -      | 0.0472 |

| A1     | 0.150       | -     | -     | 0.0059                | -      | -      |

| A2     | -           | 0.200 | -     | -                     | 0.0079 | -      |

| A4     | -           | -     | 0.600 | -                     | -      | 0.0236 |

| b      | 0.250       | 0.300 | 0.350 | 0.0098                | 0.0118 | 0.0138 |

| D      | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| D1     | -           | 3.500 | -     | -                     | 0.1378 | -      |

| E      | 4.850       | 5.000 | 5.150 | 0.1909                | 0.1969 | 0.2028 |

| E1     | -           | 3.500 | -     | -                     | 0.1378 | -      |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| F      | -           | 0.750 | -     | -                     | 0.0295 | -      |

Using the values obtained in *Table* 62  $T_{Jmax}$  is calculated as follows:

- For LQFP100, 46 °C/W

- $T_{Jmax}$  = 115 °C + (46 °C/W × 134 mW) = 115 °C + 6.2 °C = 121.2 °C

This is within the range of the suffix 7 version parts (–40 <  $T_J$  < 125 °C).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Table 63: Ordering information scheme*).

# 7 Ordering information scheme

#### Table 63. Ordering information scheme

| Example:                                         | STM32 | F 103 C | 8 T 7 xxx |

|--------------------------------------------------|-------|---------|-----------|

| Device family                                    |       |         |           |

| STM32 = ARM-based 32-bit microcontroller         | ]     |         |           |

|                                                  |       |         |           |

| Product type                                     |       |         |           |

| F = general-purpose                              |       |         |           |

| Device subfamily                                 |       |         |           |

| 103 = performance line                           |       |         |           |

|                                                  |       |         |           |

| Pin count                                        |       |         |           |

| T = 36 pins                                      |       |         |           |

| C = 48 pins                                      |       |         |           |

| R = 64 pins                                      |       |         |           |

| V = 100 pins                                     |       |         |           |

|                                                  |       |         |           |

| Flash memory size                                |       |         |           |

| 8 = 64 Kbytes of Flash memory                    |       |         |           |

| B = 128 Kbytes of Flash memory                   |       |         |           |

| Package                                          |       |         |           |

| H = BGA                                          |       |         |           |

| I = UFBGA                                        |       |         |           |

| T = LQFP                                         |       |         |           |

| U = VFQFPN or UFQFPN                             |       |         |           |

| Temperature range                                |       |         |           |

| 6 = Industrial temperature range, -40 to 85 °C.  |       |         |           |

| 7 = Industrial temperature range, -40 to 105 °C. |       |         |           |

|                                                  |       |         |           |

| Options                                          |       |         |           |

xxx = programmed parts TR = tape and real

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Table 64. Document revision history (continued) |          |                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Date                                            | Revision | Changes                                                                                                                                                                                                                                                                                                      |  |  |

| 14-Mar-2008                                     | 5        | Figure 2: Clock tree on page 12 added.<br>Maximum T <sub>J</sub> value given in Table 8: Thermal characteristics on<br>page 38.<br>CRC feature added (see CRC (cyclic redundancy check) calculation                                                                                                          |  |  |

|                                                 |          | <i>unit on page 9</i> and <i>Figure 11: Memory map on page 34</i> for address).<br>I <sub>DD</sub> modified in <i>Table 16: Typical and maximum current consumptions</i><br><i>in Stop and Standby modes.</i><br>ACC <sub>HSI</sub> modified in <i>Table 24: HSI oscillator characteristics on page 56</i> , |  |  |

|                                                 |          | note 2 removed.<br>P <sub>D</sub> , T <sub>A</sub> and T <sub>J</sub> added, $t_{prog}$ values modified and $t_{prog}$ description<br>clarified in <i>Table 28: Flash memory characteristics on page 57</i> .<br>$t_{RET}$ modified in <i>Table :</i> .                                                      |  |  |

|                                                 |          | V <sub>NF(NRST)</sub> unit corrected in <i>Table 38: NRST pin characteristics on page</i> 67.                                                                                                                                                                                                                |  |  |

|                                                 |          | Table 42: SPI characteristics on page 71 modified.IVREF added to Table 46: ADC characteristics on page 75.Table 48: ADC accuracy - limited test conditions added. Table 49: ADCaccuracy modified.                                                                                                            |  |  |

|                                                 |          | LQFP100 package specifications updated (see <i>Section 6: Package information on page 80</i> ).<br>Recommended LQFP100, LQFP 64, LQFP48 and VFQFPN36 for the add (see <i>Sigure 55</i> , <i>Figure 60</i> , <i>Sigure 61</i> , and <i>Figure 11</i> ).                                                       |  |  |

|                                                 |          | footprints added (see <i>Figure 55</i> , <i>Figure 60</i> , <i>Figure 64</i> and <i>Figure 44</i> ).<br>Section 6.9: Thermal characteristics on page 105 modified,<br>Section 6.9.1 and Section 6.9.2 added.<br>Appendix A: Important notes on page 81 removed.                                              |  |  |

| 21-Mar-2008                                     | 6        | Small text changes. <i>Figure 11: Memory map</i> clarified.<br>In <i>Table :</i> :                                                                                                                                                                                                                           |  |  |

|                                                 |          | <ul> <li>N<sub>END</sub> tested over the whole temperature range</li> <li>cycling conditions specified for t<sub>RET</sub></li> </ul>                                                                                                                                                                        |  |  |

|                                                 |          | - t <sub>RET</sub> min modified at T <sub>A</sub> = 55 °C<br>V <sub>25</sub> , Avg_Slope and T <sub>L</sub> modified in <i>Table 50: TS characteristics</i> .<br>CRC feature removed.                                                                                                                        |  |  |

| 22-May-2008                                     | 7        | CRC feature added back. Small text changes. Section 1: Introduction modified. Section 2.2: Full compatibility throughout the family added.<br>$I_{DD}$ at T <sub>A</sub> max = 105 °C added to Table 16: Typical and maximum                                                                                 |  |  |

|                                                 |          | <i>current consumptions in Stop and Standby modes on page 45.</i><br>I <sub>DD VBAT</sub> removed from <i>Table 21: Typical current consumption in</i>                                                                                                                                                       |  |  |

|                                                 |          | Standby mode on page 47.<br>Values added to Table 41: SCL frequency (fPCLK1= 36<br>MHz.,VDD_I2C = 3.3 V) on page 70.                                                                                                                                                                                         |  |  |

|                                                 |          | Figure 33: SPI timing diagram - slave mode and CPHA = 0 on page 72<br>modified. Equation 1 corrected.<br>$t_{RET}$ at $T_A$ = 105 °C modified in Table : on page 58.                                                                                                                                         |  |  |

|                                                 |          | V <sub>USB</sub> added to <i>Table 44: USB DC electrical characteristics on page 74.</i><br><i>Figure 65: LQFP100 PD max vs. TA on page 107</i> modified.                                                                                                                                                    |  |  |

|                                                 |          | Axx option added to <i>Table 63: Ordering information scheme on page 108</i> .                                                                                                                                                                                                                               |  |  |

| Date        | Revision          | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14-May-2013 | 15<br>(continued) | Updated Figure 53: UFBGA100 - 100-ball, 7 x 7 mm, 0.50 mm pitch,<br>ultra fine pitch ball grid array package outline and Table 56: UFBGA100<br>- 100-ball, 7 x 7 mm, 0.50 mm pitch, ultra fine pitch ball grid array<br>package mechanical data<br>Updated Figure 47: LFBGA100 - 100-ball low-profile fine pitch ball grid<br>array, 10 x10 mm, 0.8 mm pitch, package outline and Table 53:<br>LFBGA100 – 100-ball low-profile fine pitch ball grid array, 10 x 10 mm,<br>0.8 mm pitch, package mechanical data<br>Updated Figure 60: TFBGA64 - 8 x 8 active ball array, 5 x 5 mm, 0.5<br>mm pitch, package outline and Table 59: TFBGA64 - 8 x 8 active ball<br>array, 5 x 5 mm, 0.5 mm pitch, package mechanical data                                                                                                                                                                                                                |

| 05-Aug-2013 | 16                | Updated the reference for 'V <sub>ESD(CDM)</sub> ' in <i>Table 32: ESD absolute maximum ratings</i><br>Corrected 'tf(IO)out' in <i>Figure 30: I/O AC characteristics definition</i><br>Updated <i>Table 52: UFQFPN48 - 48-lead, 7x7 mm, 0.5 mm pitch, ultra thin fine pitch quad flat package mechanical data</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21-Aug-2015 | 17                | Updated <i>Table 3: STM32F103xx family</i> removing the note.<br>Updated <i>Table 63: Ordering information scheme</i> removing the note.<br>Updated <i>Section 6: Package information</i> and added <i>Section : Marking</i><br><i>of engineering samples</i> for all packages.<br>Updated I2C characteristics, added t <sub>SP</sub> parameter and note 4 in<br><i>Table 40: I2C characteristics.</i><br>Updated <i>Figure 32: I2C bus AC waveforms and measurement circuit</i><br>swapping SCLL and SCLH.<br>Updated <i>Figure 33: SPI timing diagram - slave mode and CPHA = 0.</i><br>Updated min/max value notes replacing 'Guaranteed by design, not<br>tested in production" by "guaranteed by design".<br>Updated min/max value notes replacing 'based on characterization, not<br>tested in production" by "Guaranteed based on test during<br>characterization".<br>Updated <i>Table 19: Peripheral current consumption.</i> |

Table 64. Document revision history (continued)