Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 2MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | WDT                                                                     |

| Number of I/O              | 6                                                                       |

| Program Memory Size        | 1KB (512 x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | -                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 8-SOIC (0.209", 5.30mm Width)                                           |

| Supplier Device Package    | 8-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny11l-2su |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Sleep Modes**

| Sleep Modes for the<br>ATtiny11 | To enter the sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruc-<br>tion must be executed. The SM bit in the MCUCR register selects which sleep mode<br>(Idle or Power-down) will be activated by the SLEEP instruction. If an enabled interrupt<br>occurs while the MCU is in a sleep mode, the MCU awakes, executes the interrupt rou-<br>tine, and resumes execution from the instruction following SLEEP. On wake-up from<br>Power Down Mode on pin change, two instruction cycles are executed before the pin<br>change interrupt flag is updated. During these cycles, the prosessor executes intruc-<br>tions, but the interrupt condition is not readable, and the interrupt routine has not startet<br>yet. The contents of the register file and I/O memory are unaltered. If a reset occurs dur-<br>ing Sleep Mode, the MCU wakes up and executes from the Reset vector. |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

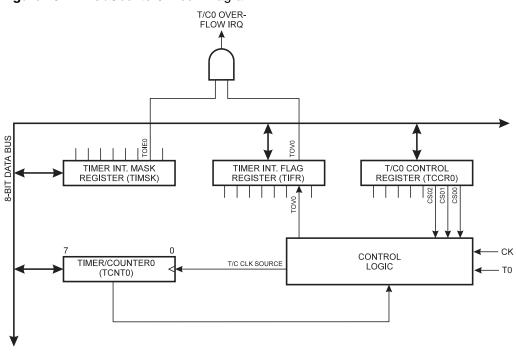

| Idle Mode                       | When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle Mode, stopping the CPU but allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like Timer Overflow interrupt and Watchdog Reset. If wake-up from the Analog Comparator interrupt is not required, the analog comparator can be powered down by setting the ACD-bit in the Analog Comparator Control and Status register – ACSR. This will reduce power consumption in Idle Mode. When the MCU wakes up from Idle mode, the CPU starts program execution immediately.                                                                                                                                                                                                                    |

| Power-down Mode                 | When the SM bit is set (one), the SLEEP instruction forces the MCU into the Power-<br>down Mode. In this mode, the external oscillator is stopped, while the external interrupts<br>and the Watchdog (if enabled) continue operating. Only an external reset, a watchdog<br>reset (if enabled), an external level interrupt (INT0), or an pin change interrupt can wake<br>up the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                 | Note that if a level-triggered or pin change interrupt is used for wake-up from power-<br>down, the changed level must be held for a time longer than the reset delay period of $t_{TOUT}$ . Otherwise, the MCU will fail to wake up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Sleep Modes for the<br>ATtiny12 | To enter the sleep modes, the SE bit in MCUCR must be set (one) and a SLEEP instruc-<br>tion must be executed. The SM bit in the MCUCR register selects which sleep mode<br>(Idle or Power-down) will be activated by the SLEEP instruction. If an enabled interrupt<br>occurs while the MCU is in a sleep mode, the MCU awakes. The CPU is then halted for<br>four cycles, it executes the interrupt routine, and resumes execution from the instruction<br>following SLEEP. The contents of the register file and I/O memory are unaltered. If a<br>reset occurs during sleep mode, the MCU wakes up and executes from the Reset<br>vector.                                                                                                                                                                                                                                                           |

| Idle Mode                       | When the SM bit is cleared (zero), the SLEEP instruction forces the MCU into the Idle Mode stopping the CPU but allowing Timer/Counters, Watchdog and the interrupt system to continue operating. This enables the MCU to wake up from external triggered interrupts as well as internal ones like Timer Overflow interrupt and Watchdog Reset. If wake-up from the Analog Comparator interrupt is not required, the analog comparator can be powered down by setting the ACD-bit in the Analog Comparator Control and Status Register – ACSR. This will reduce power consumption in Idle Mode.                                                                                                                                                                                                                                                                                                         |

| Power-down Mode                 | When the SM bit is set (one), the SLEEP instruction forces the MCU into the Power-<br>down Mode. In this mode, the external oscillator is stopped, while the external interrupts<br>and the Watchdog (if enabled) continue operating. Only an external reset, a watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

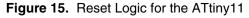

# System Control and Reset

#### **Reset Sources**

The ATtiny11/12 provides three or four sources of reset:

- Power-on Reset. The MCU is reset when the supply voltage is below the power-on reset threshold (V<sub>POT</sub>).

- External Reset. The MCU is reset when a low level is present on the RESET pin for more than 50 ns.

- Watchdog Reset. The MCU is reset when the Watchdog timer period expires and the Watchdog is enabled.

- Brown-out Reset. The MCU is reset when the supply voltage V<sub>CC</sub> falls below a certain voltage (ATtiny12 only).

During reset, all I/O registers are then set to their initial values, and the program starts execution from address \$000. The instruction placed in address \$000 must be an RJMP – relative jump – instruction to the reset handling routine. If the program never enables an interrupt source, the interrupt vectors are not used, and regular program code can be placed at these locations. The circuit diagram in Figure 15 shows the reset logic for the ATtiny11. Figure 16 shows the reset logic for the ATtiny12. Table 7 defines the electrical parameters of the reset circuitry for ATtiny11. Table 9 shows the parameters of the reset circuitry for ATtiny12.

| Symbol                          | Parameter                                  | Min | Тур                 | Max | Units |

|---------------------------------|--------------------------------------------|-----|---------------------|-----|-------|

| v (1)                           | Power-on Reset Threshold Voltage (rising)  | 1.0 | 1.4                 | 1.8 | V     |

| V <sub>POT</sub> <sup>(1)</sup> | Power-on Reset Threshold Voltage (falling) | 0.4 | 0.6                 | 0.8 | V     |

| V <sub>RST</sub>                | RESET Pin Threshold Voltage                |     | 0.6 V <sub>CC</sub> |     | V     |

Note: 1. The Power-on Reset will not work unless the supply voltage has been below  $V_{\text{POT}}$  (falling).

#### Pin Change Interrupt

The pin change interrupt is triggered by any change on any input or I/O pin. Change on pins PB2..0 will always cause an interrupt. Change on pins PB5..3 will cause an interrupt if the pin is configured as input or I/O, as described in the section "Pin Descriptions" on page 5. Observe that, if enabled, the interrupt will trigger even if the changing pin is configured as an output. This feature provides a way of generating a software interrupt. Also observe that the pin change interrupt will trigger even if the pin activity triggers another interrupt, for example, the external interrupt. This implies that one external event might cause several interrupts.

The values on the pins are sampled before detecting edges. If pin change interrupt is enabled, pulses that last longer than one CPU clock period will generate an interrupt. Shorter pulses are not guaranteed to generate an interrupt.

#### **Register Description**

#### MCU Control Register – MCUCR

The MCU Control Register contains control bits for general MCU functions.

| Bit           | 7 | 6     | 5   | 4   | 3 | 2 | 1     | 0     | _     |

|---------------|---|-------|-----|-----|---|---|-------|-------|-------|

| \$35          | - | (PUD) | SE  | SM  | - | - | ISC01 | ISC00 | MCUCR |

| Read/Write    | R | R(/W) | R/W | R/W | R | R | R/W   | R/W   | •     |

| Initial Value | 0 | 0     | 0   | 0   | 0 | 0 | 0     | 0     |       |

Note: The Pull-up Disable (PUD) bit is only available in ATtiny12.

#### • Bit 7 - Res: Reserved Bit

This bit is a reserved bit in the ATtiny11/12 and always reads as zero.

#### • Bit 6 - Res: Reserved Bit in ATtiny11

This bit is a reserved bit in the ATtiny11 and always reads as zero.

#### • Bit 6 - PUD: Pull-up Disable in ATtiny12

Setting this bit, disables all pull-ups on port B. If this bit is cleared, the pull-ups can be individually enabled as described in section "I/O Port B" on page 36.

#### • Bit 5 - SE: Sleep Enable

The SE bit must be set (one) to make the MCU enter the Sleep Mode when the SLEEP instruction is executed. To avoid the MCU entering the Sleep Mode unless it is the programmer's purpose, it is recommended to set the Sleep Enable SE bit just before the execution of the SLEEP instruction.

#### • Bit 4 - SM: Sleep Mode

This bit selects between the two available sleep modes. When SM is cleared (zero), Idle Mode is selected as Sleep Mode. When SM is set (one), Power-down Mode is selected as Sleep Mode. For details, refer to the paragraph "Sleep Modes" below.

#### • Bits 3, 2 - Res: Reserved Bits

These bits are reserved bits in the ATtiny11/12 and always read as zero.

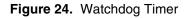

## Watchdog Timer

The Watchdog Timer is clocked from a separate on-chip oscillator. By controlling the Watchdog Timer prescaler, the Watchdog reset interval can be adjusted as shown in Table 19. See characterization data for typical values at other  $V_{CC}$  levels. The WDR – Watchdog Reset – instruction resets the Watchdog Timer. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog reset, the ATtiny11/12 resets and executes from the reset vector. For timing details on the Watchdog reset, refer to page 28.

To prevent unintentional disabling of the watchdog, a special turn-off sequence must be followed when the watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

#### **Register Description**

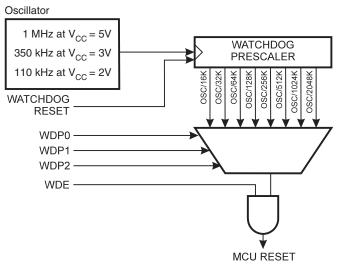

Watchdog Timer Control Register – WDTCR

#### • Bits 7..5 - Res: Reserved Bits

These bits are reserved bits in the ATtiny11/12 and will always read as zero.

#### • Bit 4 - WDTOE: Watchdog Turn-off Enable

This bit must be set (one) when the WDE bit is cleared. Otherwise, the watchdog will not be disabled. Once set, hardware will clear this bit to zero after four clock cycles. Refer to the description of the WDE bit for a watchdog disable procedure.

#### • Bit 3 - WDE: Watchdog Enable

When the WDE is set (one) the Watchdog Timer is enabled, and if the WDE is cleared (zero) the Watchdog Timer function is disabled. WDE can be cleared only when the WDTOE bit is set(one). To disable an enabled watchdog timer, the following procedure must be followed:

## **Analog Comparator**

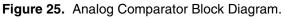

The Analog Comparator compares the input values on the positive input PB0 (AIN0) and negative input PB1 (AIN1). When the voltage on the positive input PB0 (AIN0) is higher than the voltage on the negative input PB1 (AIN1), the Analog Comparator Output (ACO) is set (one). The comparator's output can trigger a separate interrupt, exclusive to the Analog Comparator. The user can select interrupt triggering on comparator output rise, fall or toggle. A block diagram of the comparator and its surrounding logic is shown in Figure 25.

#### **Register Description**

Analog Comparator Control and Status Register – ACSR

| Bit           | 7   | 6       | 5   | 4   | 3    | 2 | 1     | 0     | _    |

|---------------|-----|---------|-----|-----|------|---|-------|-------|------|

| \$08          | ACD | (AINBG) | ACO | ACI | ACIE | - | ACIS1 | ACIS0 | ACSR |

| Read/Write    | R/W | R(/W)   | R   | R/W | R/W  | R | R/W   | R/W   | •    |

| Initial Value | 0   | 0       | Х   | 0   | 0    | 0 | 0     | 0     |      |

Note: AINBG is only available in ATtiny12.

#### • Bit 7 - ACD: Analog Comparator Disable

When this bit is set (one), the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

#### • Bit 6 - AINBG: Analog Comparator Bandgap Select in ATtiny12

In ATtiny12, when this bit is set, a fixed bandgap voltage of  $1.22 \pm 0.05$ V replaces the normal input to the positive input (AIN0) of the comparator. When this bit is cleared, the normal input pin PB0 is applied to the positive input of the comparator.

#### • Bit 6- Res: Reserved Bit in ATtiny11

This bit is a reserved bit in the ATtiny11 and will always read as zero.

#### • Bit 5 - ACO: Analog Comparator Output

ACO is directly connected to the comparator output.

# ATtiny11/12

#### High-voltage Serial Programming Algorithm

To program and verify the ATtiny11/12 in the High-voltage Serial Programming mode, the following sequence is recommended (See instruction formats in Table 23):

- 1. Power-up sequence: Apply 4.5 5.5V between V<sub>CC</sub> and GND. Set PB5 and PB0 to "0" and wait at least 100 ns. Toggle PB3 at least four times with minimum 100 ns pulse-width. Set PB3 to "0". Wait at least 100 ns. Apply 12V to PB5 and wait at least 100 ns before changing PB0. Wait 8 µs before giving any instructions.

- 2. The Flash array is programmed one byte at a time by supplying first the address, then the low and high data byte. The write instruction is self-timed, wait until the PB2 (RDY/BSY) pin goes high.

- 3. The EEPROM array (ATtiny12 only) is programmed one byte at a time by supplying first the address, then the data byte. The write instruction is self-timed, wait until the PB2 (RDY/BSY) pin goes high.

- 4. Any memory location can be verified by using the Read instruction which returns the contents at the selected address at serial output PB2.

- Power-off sequence:Set PB3 to "0". Set PB5 to "1". Turn V<sub>CC</sub> power off.

When writing or reading serial data to the ATtiny11/12, data is clocked on the rising edge of the serial clock, see Figure 27, Figure 28 and Table 24 for details.

# ATtiny11/12

|                                        |                   |                                                | Instructio                                                  |                                                             |                                                            |                                                                                                                                             |

|----------------------------------------|-------------------|------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction                            |                   | Instr.1                                        | Instr.2                                                     | Instr.3                                                     | Instr.4                                                    | Operation Remarks                                                                                                                           |

| Read EEPROM<br>byte (ATtiny12)         | PB0<br>PB1<br>PB2 | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx | 1000_00 0_0110_1100_00                                      |                                                             | Repeat Instr.2 for each new address                        |                                                                                                                                             |

| Write Fuse bits<br>(ATtiny11)          | PB0<br>PB1<br>PB2 | 0_0100_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_000 <b>7_6543</b> _00<br>0_0010_1100_00<br>x_xxxx_xxxx_xx | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br>x_xxxx_xxx             | Wait $t_{WLWH\_PFB}$ after Instr.3 for the<br>Write fuse bits cycle to finish. Write<br><b>7</b> - <b>3</b> = "0" to program the fuse bit.  |

| Write Fuse bits<br>(ATtiny12)          | PB0<br>PB1<br>PB2 | 0_0100_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_ <b>CBA9_8543_</b> 00<br>0_0010_1100_00<br>x_xxxx_xxxx_xx | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br>x_xxxx_xxx             | Wait after Instr.4 until PB2 goes<br>high. Write <b>C</b> - <b>A</b> , <b>9</b> , <b>8</b> , 5 - <b>3</b> = "0" to<br>program the fuse bit. |

| Write Lock bits                        | PB0<br>PB1<br>PB2 | 0_0010_0000_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0210_00<br>0_0010_1100_00<br>x_xxxx_xxxx_xx          | 0_0000_0000_00<br>0_0110_0100_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br>0_0000_0000_00         | Wait after Instr.4 until PB2 goes<br>high. Write <i>2</i> , <i>1</i> = "0" to program<br>the lock bit.                                      |

| Read Fuse bits<br>(ATtiny11)           | PB0<br>PB1<br>PB2 | 0_0000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br>x_xx <b>76_543</b> x_xx |                                                            | Reading <b>7</b> - <b>3</b> = "0" means the fuse bit is programmed.                                                                         |

| Read Fuse bits<br>(ATtiny12)           | PB0<br>PB1<br>PB2 | 0_0000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br><b>C_BA98_543</b> x_xx  |                                                            | Reading <b>C</b> - <b>A</b> , <b>9</b> , <b>8</b> , <b>5</b> - <b>3</b> = "0"<br>means the fuse bit is programmed.                          |

| Read Lock bits                         | PB0<br>PB1<br>PB2 | 0_0000_0100_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0111_1000_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0111_1100_00<br>x_xxxx_ <b>21</b> xx_xx |                                                            | Reading <i>2</i> , <i>1</i> = "0" means the lock bit is programmed.                                                                         |

| Read Signature<br>Bytes                | PB0<br>PB1<br>PB2 | 0_0000_1000_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_00 <b>bb</b> _00<br>0_0000_1100_00<br>x_xxxx_xxxx_xx | 0_0000_0000_00<br>0_0110_1000_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0110_1100_00<br><b>o_0000_000x</b> _xx | Repeat Instr.2 - Instr.4 for each signature byte address                                                                                    |

| Read<br>Calibration Byte<br>(ATtiny12) | PB0<br>PB1<br>PB2 | 0_0000_1000_00<br>0_0100_1100_00<br>x_xxxx_xxx | 0_0000_0000_00<br>0_0000_1100_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0111_1000_00<br>x_xxxx_xxx              | 0_0000_0000_00<br>0_0111_1100_00<br><b>o_0000_000x_</b> xx |                                                                                                                                             |

#### Table 23. High-voltage Serial Programming Instruction Set for ATtiny11/12 (Continued)

Note: **a** = address high bits

$\mathbf{b}$  = address low bits

- $\mathbf{i} = data in$

- **o** = data out

- x = don't care

- *1* = Lock Bit1 *2* = Lock Bit2

- **3** = CKSEL0 Fuse

- 4 = CKSEL1 Fuse

- 5 = CKSEL2 Fuse

- **9**, **6** = RSTDISBL Fuse

- 7 = FSTRT Fuse

- 8 = CKSEL3 Fuse

- $\mathbf{A} = \text{SPIEN Fuse}$

- $\mathbf{B} = \text{BODEN Fuse}$

- C = BODLEVEL Fuse

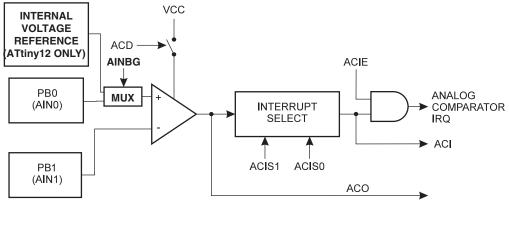

#### Low-voltage Serial Programming Characteristics

| <b>Table 26.</b> Low-voltage Serial Programming Characteristics $T_A = -40^{\circ}C$ to $85^{\circ}C$ , |

|---------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> = 2.2 - 5.5V (Unless otherwise noted)                                                   |

| Symbol              | Parameter                                        | Min                 | Тур | Max | Units |

|---------------------|--------------------------------------------------|---------------------|-----|-----|-------|

| 1/t <sub>CLCL</sub> | Oscillator Frequency ( $V_{CC} = 2.2 - 2.7V$ )   | 0                   |     | 1   | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period (V <sub>CC</sub> = 2.2 - 2.7V) | 1000                |     |     | ns    |

| 1/t <sub>CLCL</sub> | Oscillator Frequency ( $V_{CC} = 2.7 - 4.0V$ )   | 0                   |     | 4   | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period (V <sub>CC</sub> = 2.7 - 4.0V) | 250                 |     |     | ns    |

| 1/t <sub>CLCL</sub> | Oscillator Frequency ( $V_{CC} = 4.0 - 5.5V$ )   | 0                   |     | 8   | MHz   |

| t <sub>CLCL</sub>   | Oscillator Period (V <sub>CC</sub> = 4.0 - 5.5V) | 125                 |     |     | ns    |

| t <sub>SHSL</sub>   | SCK Pulse Width High                             | 2 t <sub>CLCL</sub> |     |     | ns    |

| t <sub>SLSH</sub>   | SCK Pulse Width Low                              | 2 t <sub>CLCL</sub> |     |     | ns    |

| t <sub>ovsh</sub>   | MOSI Setup to SCK High                           | t <sub>CLCL</sub>   |     |     | ns    |

| t <sub>SHOX</sub>   | MOSI Hold after SCK High                         | 2 t <sub>CLCL</sub> |     |     | ns    |

| t <sub>SLIV</sub>   | SCK Low to MISO Valid                            | 10                  | 16  | 32  | ns    |

Table 27. Minimum Wait Delay after the Chip Erase Instruction

| Symbol                | Minimum Wait Delay |

|-----------------------|--------------------|

| t <sub>WD_ERASE</sub> | 6.8 ms             |

| Table 28. | Minimum | Wait Dela | av after | Writing a | Flash or | EEPROM Location | on |

|-----------|---------|-----------|----------|-----------|----------|-----------------|----|

|           |         |           |          |           |          |                 |    |

| Symbol                 | Minimum Wait Delay |

|------------------------|--------------------|

| t <sub>WD_FLASH</sub>  | 3.4 ms             |

| t <sub>WD_EEPROM</sub> | 6.8 ms             |

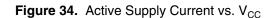

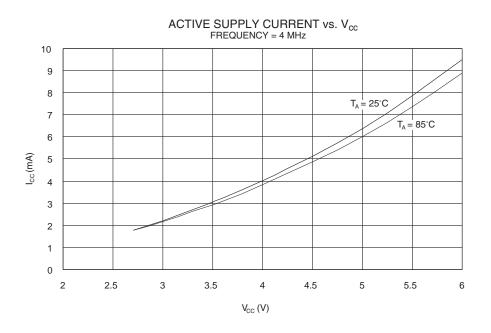

#### DC Characteristics – Preliminary Data (Continued)

T<sub>A</sub> = -40°C to 85°C, V<sub>CC</sub> = 2.7V to 5.5V for ATtiny11, V<sub>CC</sub> = 1.8V to 5.5V for ATtiny12 (Unless otherwise noted)

| Symbol            | Parameter                                  | Condition                                                              | Min | Тур        | Max | Units |

|-------------------|--------------------------------------------|------------------------------------------------------------------------|-----|------------|-----|-------|

| I <sub>cc</sub>   | Power Supply Current                       | Active 1 MHz, V <sub>CC</sub> = 3V<br>(ATtiny12V)                      |     |            | 1.0 | mA    |

|                   |                                            | Active 2 MHz, V <sub>CC</sub> = 3V<br>(ATtiny11L)                      |     |            | 2.0 | mA    |

|                   |                                            | Active 4 MHz, V <sub>CC</sub> = 3V<br>(ATtiny12L)                      |     |            | 2.5 | mA    |

|                   |                                            | Active 6 MHz, V <sub>CC</sub> = 5V<br>(ATtiny11)                       |     |            | 10  | mA    |

|                   |                                            | Active 8 MHz, V <sub>CC</sub> = 5V<br>(ATtiny12)                       |     |            | 10  | mA    |

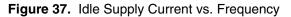

|                   |                                            | Idle 1 MHz, V <sub>CC</sub> = 3V<br>(ATtiny12V)                        |     |            | 0.4 | mA    |

|                   |                                            | Idle 2 MHz, V <sub>CC</sub> = 3V<br>(ATtiny11L)                        |     |            | 0.5 | mA    |

|                   |                                            | Idle 4 MHz, V <sub>CC</sub> = 3V<br>(ATtiny12L)                        |     |            | 1.0 | mA    |

|                   |                                            | Idle 6 MHz, V <sub>CC</sub> = 5V<br>(ATtiny11)                         |     |            | 2.0 | mA    |

|                   |                                            | Idle 8 MHz, V <sub>CC</sub> = 5V<br>(ATtiny12)                         |     |            | 3.5 | mA    |

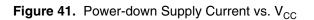

|                   |                                            | Power Down <sup>(5)</sup> , $V_{CC} = 3V$ , WDT enabled                |     | 9.0        | 15  | μA    |

|                   |                                            | Power Down <sup>(5)</sup> , $V_{CC} = 3V$ .<br>WDT disabled (ATtiny12) |     | <1         | 2   | μA    |

|                   |                                            | Power Down <sup>(5)</sup> , $V_{CC} = 3V$ .<br>WDT disabled (ATtiny11) |     | <1         | 5   | μA    |

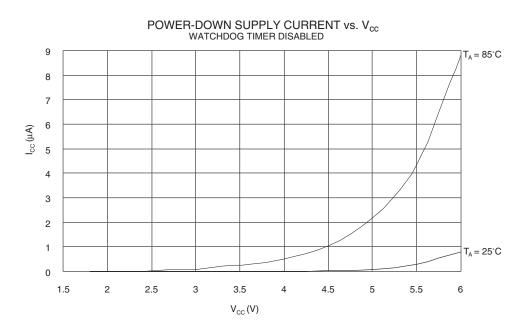

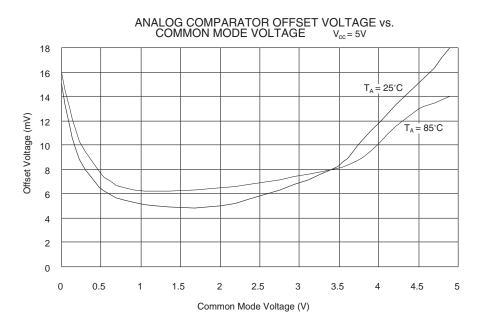

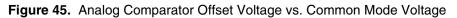

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | $V_{CC} = 5V$ $V_{IN} = V_{CC}/2$                                      |     |            | 40  | mV    |

| ACLK              | Analog Comparator<br>Input Leakage Current | $V_{CC} = 5V$ $V_{IN} = V_{CC}/2$                                      | -50 |            | 50  | nA    |

| T <sub>ACPD</sub> | Analog Comparator<br>Propagation Delay     | $V_{CC} = 2.7V$<br>$V_{CC} = 4.0V$                                     |     | 750<br>500 |     | ns    |

Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low.

2. "Min" means the lowest value where the pin is guaranteed to be read as high.

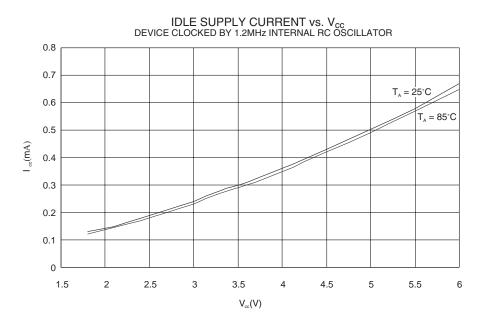

Although each I/O port can sink more than the test conditions (20 mA at V<sub>CC</sub> = 5V, 10 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all I<sub>OL</sub>, for all ports, should not exceed 100 mA.

If  $I_{OL}$  exceeds the test condition,  $V_{OL}$  may exceed the related specification.

Pins are not guaranteed to sink current greater than the listed test conditions.

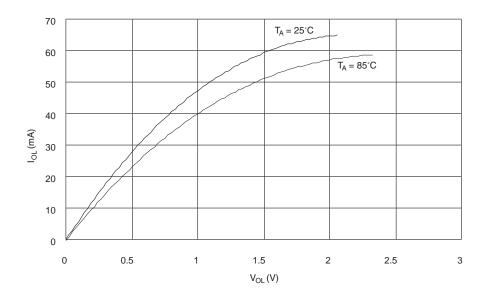

Although each I/O port can source more than the test conditions (3 mA at V<sub>CC</sub> = 5V, 1.5 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the following must be observed:

1] The sum of all  $I_{\mbox{OH}}$  , for all ports, should not exceed 100 mA.

If  $I_{OH}$  exceeds the test condition,  $V_{OH}$  may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

5. Minimum  $V_{CC}$  for Power-down is 1.5V. (On ATtiny12: only with BOD disabled)

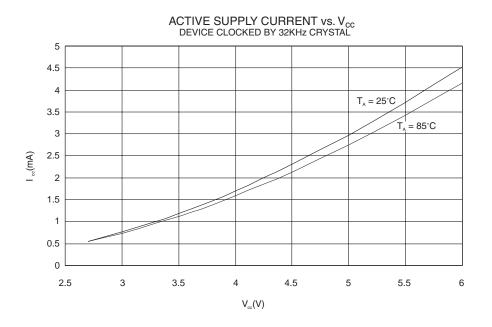

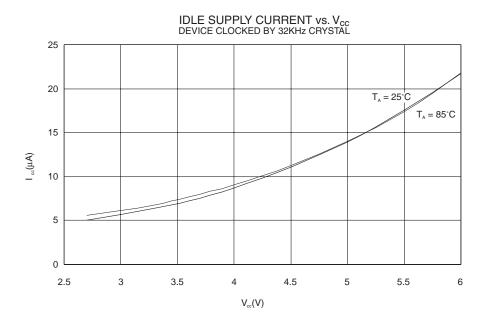

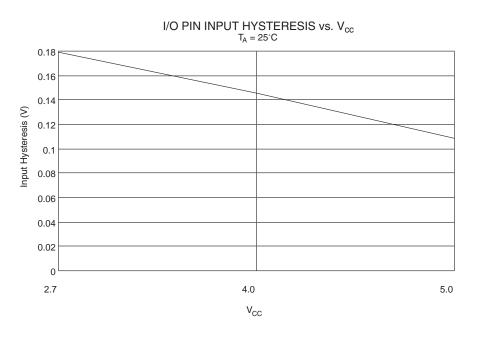

Figure 36. Active Supply Current vs. V<sub>CC</sub>, Device Clocked by External 32kHz Crystal

Analog comparator offset voltage is measured as absolute offset.

ATtiny11/12

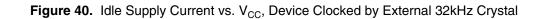

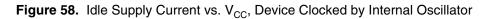

Figure 57. Active Supply Current vs. V<sub>CC</sub>, Device Clocked by External 32kHz Crystal

Figure 67. I/O Pin Sink Current vs. Output Voltage ( $V_{CC} = 5V$ )

Figure 68. I/O Pin Source Current vs. Output Voltage ( $V_{CC} = 5V$ )

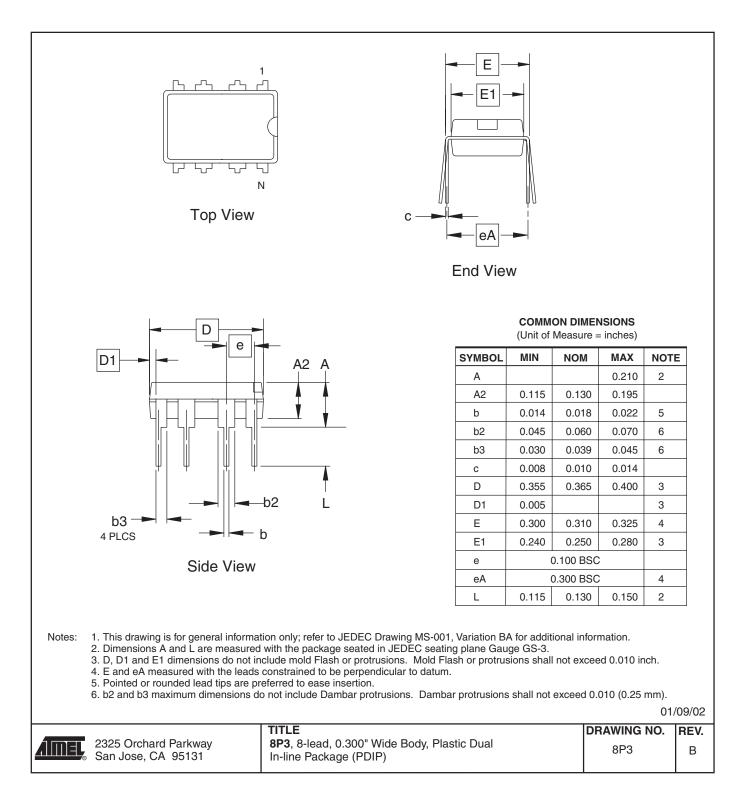

# **Packaging Information**

8P3

## Datasheet Revision History

Please note that the page numbers listed in this section are referring to this document. The revision numbers are referring to the document revision.

- **Rev. 1006F-06/07** 1. "Not recommended for new design".

- Rev. 1006E-07/06 1. Updated chapter layout.

- 2. Updated Power-down in "Sleep Modes for the ATtiny11" on page 20.

- 3. Updated Power-down in "Sleep Modes for the ATtiny12" on page 20.

- 4. Updated Table 16 on page 36.

- 5. Updated "Calibration Byte in ATtiny12" on page 49.

- 6. Updated "Ordering Information" on page 87.

- 7. Updated "Packaging Information" on page 89.

- **Rev. 1006D-07/03** 1. Updated V<sub>BOT</sub> values in Table 9 on page 24.

- Rev. 1006C-09/01 1. N/A

| High-voltage Serial Programming Algorithm         | ) |

|---------------------------------------------------|---|

| Electrical Characteristics 57                     | , |

| Absolute Maximum Ratings 57                       | , |

| DC Characteristics – Preliminary Data 57          | , |

| External Clock Drive Waveforms 59                 |   |

| External Clock Drive ATtiny1159                   | ) |

| External Clock Drive ATtiny12 59                  | ) |

| ATtiny11 Typical Characteristics 60               | ) |

| ATtiny12 Typical Characteristics72                |   |

| Register Summary ATtiny11 81                      | , |

| Register Summary ATtiny12 82                      | ) |

| Instruction Set Summary 83                        | } |

| Ordering Information 85                           | ; |

| Packaging Information                             | ; |

| 8P3                                               |   |

| 8S2                                               |   |

| Data Sheet Change Log for Chip Number 88          | } |

| Changes from Rev. 1006C-09/01 to Rev. 1006D-07/03 | 5 |

| Table of Contents                                 | i |