Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 4MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 96 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce623-04-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16CE62X are 18 and 20-Pin EPROM-based members of the versatile PIC<sup>®</sup> family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with EEPROM data memory.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16CE62X family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CE62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16CE623 and PIC16CE624 have 96 bytes of RAM. The PIC16CE625 has 128 bytes of RAM. Each microcontroller contains a 128x8 EEPROM memory array for storing non-volatile information, such as calibration data or security codes. This memory has an endurance of 1,000,000 erase/write cycles and a retention of 40 plus years.

Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16CE62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low-cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16CE62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and reset. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development, while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16CE62X mid-range microcontroller families.

A simplified block diagram of the PIC16CE62X is shown in Figure 3-1.

The PIC16CE62X series fits perfectly in applications ranging from multi-pocket battery chargers to low-power remote sensors. The EPROM technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high-performance, ease of use and I/O flexibility make the PIC16CE62X very versatile.

# 1.1 <u>Development Support</u>

The PIC16CE62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler is also available.

# 2.0 PIC16CE62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in the PIC16CE62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 2.1 UV Erasable Devices

The UV erasable version, offered in the CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16CE62X.

# 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

# 2.3 <u>Quick-Turn-Programming (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.4 <u>Serialized Quick-Turn-Programming</u> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CE62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CE62X uses a Harvard architecture in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM) and non-volatile memory (EEPROM) for each PIC16CE62X device.

| Device     | Program<br>Memory | RAM<br>Data<br>Memory | EEPROM<br>Data<br>Memory |

|------------|-------------------|-----------------------|--------------------------|

| PIC16CE623 | 512x14            | 96x8                  | 128x8                    |

| PIC16CE624 | 1Kx14             | 96x8                  | 128x8                    |

| PIC16CE625 | 2Kx14             | 128x8                 | 128x8                    |

The PIC16CE62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CE62X family has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CE62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16CE62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

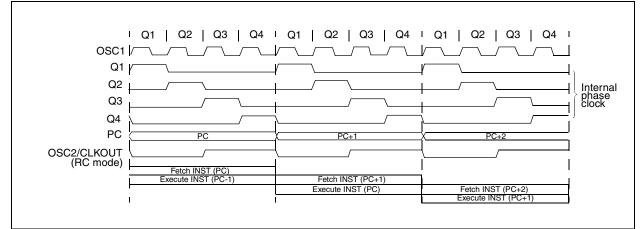

# 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

# 3.2 Instruction Flow/Pipelining

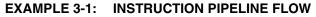

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

# FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

# 6.5 <u>Read Operation</u>

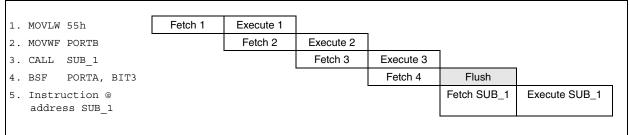

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the EEPROM address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

# 6.6 Current Address Read

The EEPROM contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the EEPROM address with R/W bit set to one, the EEPROM issues an acknowledge and transmits the eight bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-7).

# 6.7 Random Read

Random read operations allow the processor to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the EEPROM as part of a write operation. After the word address is sent, the processor generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the processor issues the control byte again, but with the R/W bit set to a one. The EEPROM will then issue an acknowledge and transmits the eight bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-8).

# 6.8 Sequential Read

Sequential reads are initiated in the same way as a random read except that after the EEPROM transmits the first data byte, the processor issues an acknowledge as opposed to a stop condition in a random read. This directs the EEPROM to transmit the next sequentially addressed 8-bit word (Figure 6-9).

To provide sequential reads, the EEPROM contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation.

# 6.9 Noise Protection

The EEPROM employs a Vcc threshold detector circuit, which disables the internal erase/write logic if the Vcc is below 1.5 volts at nominal conditions.

The SCL and SDA inputs have Schmitt trigger and filter circuits, which suppress noise spikes to assure proper device operation even on a noisy bus.

NOTES:

The code example in Example 8-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 8-1: INITIALIZING COMPARATOR MODULE

| FLAG_REG | F EQU        | 0X20                              |

|----------|--------------|-----------------------------------|

| CLRF     | FLAG_REG     | ;Init flag register               |

| CLRF     | PORTA        | ;Init PORTA                       |

| MOVF     | CMCON,W      | ;Move comparator contents to W    |

| ANDLW    | 0xC0         | ;Mask comparator bits             |

| IORWF    | FLAG_REG,F   | ;Store bits in flag register      |

| MOVLW    | 0x03         | ;Init comparator mode             |

| MOVWF    | CMCON        | ;CM<2:0> = 011                    |

| BSF      | STATUS, RPO  | ;Select Bank1                     |

| MOVLW    | 0x07         | ;Initialize data direction        |

| MOVWF    | TRISA        | ;Set RA<2:0> as inputs            |

|          |              | ;RA<4:3> as outputs               |

|          |              | ;TRISA<7:5> always read `0'       |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| CALL     | DELAY 10     | ;10µs delay                       |

| MOVF     | CMCON, F     | ;Read CMCONtoend change condition |

| BCF      | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF      | STATUS, RPO  | ;Select Bank 1                    |

| BSF      | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| BSF      | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF      | INTCON, GIE  | ;Global interrupt enable          |

|          |              |                                   |

# 8.2 Comparator Operation

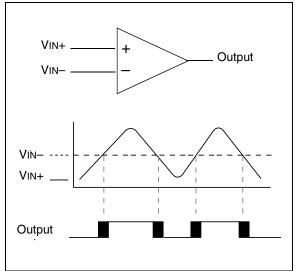

A single comparator is shown in Figure 8-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN–, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN–, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 8-2 represent the uncertainty due to input offsets and response time.

# 8.3 <u>Comparator Reference</u>

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal that is present at VIN– is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 8-2).

FIGURE 8-2: SINGLE COMPARATOR

# 8.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 8.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 8-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 10.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

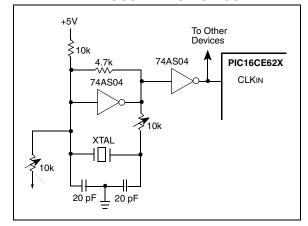

Figure 10-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 10-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

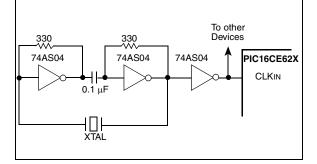

Figure 10-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180° phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

# FIGURE 10-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

#### 10.2.4 RC OSCILLATOR

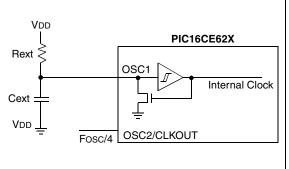

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-5 shows how the R/C combination is connected to the PIC16CE62X. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (i.e., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 14.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 14.0 for variation of oscillator frequency due to VDD for given Rext/Cext values, as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

# FIGURE 10-5: RC OSCILLATOR MODE

#### 10.4.5 TIME-OUT SEQUENCE

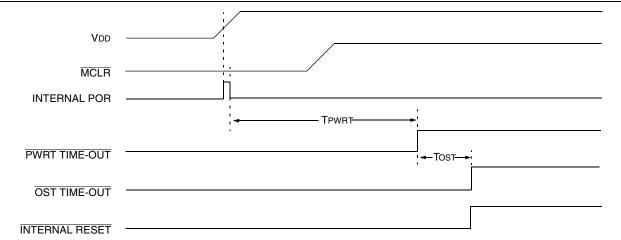

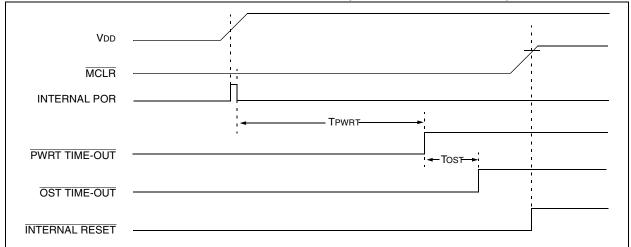

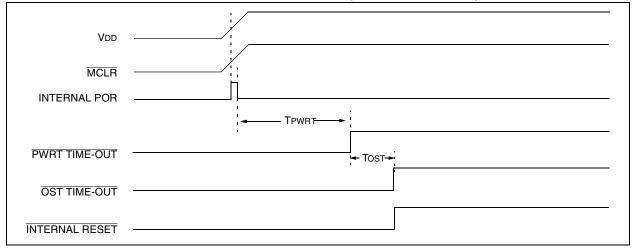

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired, then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no time-out at all. Figure 10-8, Figure 10-9 and Figure 10-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 10-9). This is useful for testing purposes or to synchronize more than one  $\text{PIC}^{\textcircled{B}}$  device operating in parallel.

Table 10-5 shows the reset conditions for some special registers, while Table 10-6 shows the reset conditions for all the registers.

#### 10.4.6 POWER CONTROL (PCON)/STATUS REGISTER

The power control/status register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on power-on-reset. It must then be set by the user and checked on subsequent resets to see if  $\overline{\text{BOR}} = 0$  indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on-reset). It is a '0' on power-on-reset and unaffected otherwise. The user must write a '1' to this bit following a power-on-reset. On a subsequent reset, if POR is '0', it will indicate that a power-on-reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up    |  |

|--------------------------|-------------------|-----------|-------------------|------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0  | PWRTE = 1 | brown-out neset   | from SLEEP |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |  |

| RC                       | 72 ms             | _         | 72 ms             | —          |  |

# TABLE 10-3: TIME-OUT IN VARIOUS SITUATIONS

| POR | BOR | TO | PD |                           |

|-----|-----|----|----|---------------------------|

| 0   | Х   | 1  | 1  | Power-on-reset            |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR |

**Brown-out Reset**

WDT Reset

WDT Wake-up

MCLR reset during normal operation

MCLR reset during SLEEP

# TABLE 10-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Х

u

0

u

Ο

Legend: x = unknown, u = unchanged

0

1

1

1

1

Х

0

0

u

1

1

1

1

1

1

# FIGURE 10-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

### FIGURE 10-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

<sup>© 1998-2013</sup> Microchip Technology Inc.

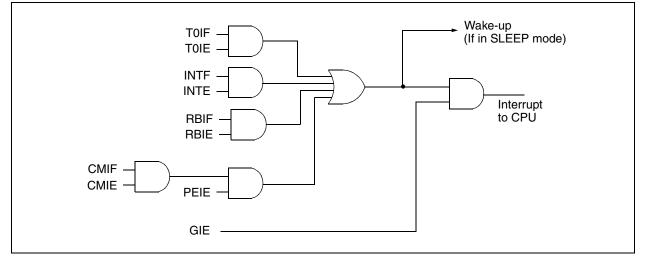

# 10.5 Interrupts

The PIC16CE62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PortB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which re-enable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of

the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends on when the interrupt event occurs (Figure 10-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

# FIGURE 10-15: INTERRUPT LOGIC

# 10.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e. W register and STATUS register). This will have to be implemented in software.

Example 10-1 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x70 in Bank 0 and it must also be defined at 0xF0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 10-1:

- Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 10-1: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP        | ;copy W to temp register,<br>;could be in either bank                  |

|-------|---------------|------------------------------------------------------------------------|

| SWAPF | STATUS,W      | ;swap status to be saved into ${\tt W}$                                |

| BCF   | STATUS, RPO   | ;change to bank 0 regardless<br>;of current bank                       |

| MOVWF | STATUS_TEMP   | ;save status to bank 0<br>;register                                    |

| :     |               |                                                                        |

| :     | (ISR)         |                                                                        |

| :     |               |                                                                        |

| SWAPF | STATUS_TEMP,W | ;swap STATUS_TEMP register<br>;into W, sets bank to original<br>;state |

| MOVWF | STATUS        | ;move W into STATUS register                                           |

| SWAPF | W_TEMP,F      | ;swap W_TEMP                                                           |

| SWAPF | W_TEMP,W      | ;swap W_TEMP into W                                                    |

# 10.7 <u>Watchdog Timer (WDT)</u>

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device have been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 10.1).

# 10.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 10.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

# 11.1 Instruction Descriptions

| ADDLW            | Add Lite                                   | ral and V  | w              |         |

|------------------|--------------------------------------------|------------|----------------|---------|

| Syntax:          | [label] A                                  | ADDLW      | k              |         |

| Operands:        | $0 \le k \le 25$                           | 55         |                |         |

| Operation:       | (W) + k –                                  | → (W)      |                |         |

| Status Affected: | C, DC, Z                                   |            |                |         |

| Encoding:        | 11                                         | 111x       | kkkk           | kkkk    |

| Description:     | The conter<br>added to th<br>result is pla | ne eight b | it literal 'k' | and the |

| Words:           | 1                                          |            |                |         |

| Cycles:          | 1                                          |            |                |         |

| Example          | ADDLW                                      | 0x15       |                |         |

|                  | After Inst                                 | W =        | 0x10<br>0x25   |         |

| ANDLW            | AND Literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:           | 1                                                                                                                   |

| Cycles:          | 1                                                                                                                   |

| Example          | ANDLW 0x5F                                                                                                          |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                     |

| ADDWF            | Add W and f                                                                                                                                                                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                      |

| Status Affected: | C, DC, Z                                                                                                                                                                    |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |

| Words:           | 1                                                                                                                                                                           |

| Cycles:          | 1                                                                                                                                                                           |

| Example          | ADDWF FSR, 0                                                                                                                                                                |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                 |

| ANDWF            | AND W with f                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |

| Status Affected: | Z                                                                                                                                                           |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |

| Words:           | 1                                                                                                                                                           |

| Cycles:          | 1                                                                                                                                                           |

| Example          | ANDWF FSR, 1                                                                                                                                                |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |

| BTFSS            | Bit Test                                                                 | i, Skip if S                                                                                                | Set                                       |                  |

|------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------|

| Syntax:          | [ <i>label</i> ] B                                                       | TFSS f,b                                                                                                    | )                                         |                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b < 7 \end{array}$          | 7                                                                                                           |                                           |                  |

| Operation:       | skip if (f<                                                              | b>) = 1                                                                                                     |                                           |                  |

| Status Affected: | None                                                                     |                                                                                                             |                                           |                  |

| Encoding:        | 01                                                                       | 11bb                                                                                                        | bfff                                      | ffff             |

| Description:     | instruction<br>If bit 'b' is '<br>fetched du<br>execution,<br>executed i | register 'f' is<br>is skipped.<br>1', then the<br>ring the cur<br>is discarde<br>nstead, ma<br>instruction. | next instru<br>rrent instru<br>d and a No | uction<br>Iction |

| Words:           | 1                                                                        |                                                                                                             |                                           |                  |

| Cycles:          | 1(2)                                                                     |                                                                                                             |                                           |                  |

| Example          | HERE<br>FALSE<br>TRUE                                                    |                                                                                                             | FLAG,1<br>PROCESS_                        | _CODE            |

|                  | Before In                                                                | struction                                                                                                   |                                           |                  |

|                  | After Inst                                                               | ruction<br>if FLAG<1><br>PC = a<br>if FLAG<1>                                                               | = 0,<br>address F.                        |                  |

| CLRF             | Clear f                                                               |   |

|------------------|-----------------------------------------------------------------------|---|

| Syntax:          | [label] CLRF f                                                        | _ |

| Operands:        | $0 \leq f \leq 127$                                                   |   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |   |

| Status Affected: | Z                                                                     |   |

| Encoding:        | 00 0001 1fff fff                                                      |   |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |   |

| Words:           | 1                                                                     |   |

| Cycles:          | 1                                                                     |   |

| Example          | CLRF FLAG_REG                                                         |   |

|                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction            |   |

|                  | $FLAG\_REG = 0x00$ $Z = 1$                                            |   |

| CALL             | Call Subroutine                                                                                                                                                                                                                              |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                      |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                         |  |  |  |  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                             |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                         |  |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                            |  |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle instruc-<br>tion |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                            |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                            |  |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                                              |  |  |  |  |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                   |  |  |  |  |

| CLRW             | Clear W                                                               |             |        |  |

|------------------|-----------------------------------------------------------------------|-------------|--------|--|

| Syntax:          | [label] CLRW                                                          |             |        |  |

| Operands:        | None                                                                  |             |        |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |             |        |  |

| Status Affected: | Z                                                                     |             |        |  |

| Encoding:        | 00 0001                                                               | 0000        | 0011   |  |

| Description:     | W register is cleare<br>set.                                          | d. Zero bit | (Z) is |  |

| Words:           | 1                                                                     |             |        |  |

| Cycles:          | 1                                                                     |             |        |  |

| Example          | CLRW                                                                  |             |        |  |

|                  | Before Instruction<br>W =                                             | ו<br>0x5A   |        |  |

|                  | After Instruction                                                     |             |        |  |

|                  | W =<br>Z =                                                            | 0x00<br>1   |        |  |

$\odot$  1998-2013 Microchip Technology Inc.

| CLRWDT           | Clear Watchdog Timer                                                                                                                                     |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                           |  |  |  |  |

| Operands:        | None                                                                                                                                                     |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                   |  |  |  |  |

| Encoding:        | 00 0000 0110 0100                                                                                                                                        |  |  |  |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$ are set.          |  |  |  |  |

| Words:           | 1                                                                                                                                                        |  |  |  |  |

| Cycles:          | 1                                                                                                                                                        |  |  |  |  |

| Example          | CLRWDT                                                                                                                                                   |  |  |  |  |

|                  | Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = 0x00<br>WDT prescaler= 0<br>TO = 1<br>PD = 1                                 |  |  |  |  |

| COMF             | Complement f                                                                                                                                             |  |  |  |  |

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                |  |  |  |  |

| COME             | Complement                                                                                                                                              |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                        |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                             |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                     |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                       |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the result is<br>stored in W. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                       |  |  |  |  |  |  |

| Example          | COMF REG1,0                                                                                                                                             |  |  |  |  |  |  |

|                  | Before InstructionREG1= $0x13$ After InstructionREG1= $0x13$ W= $0xEC$                                                                                  |  |  |  |  |  |  |

|                  |                                                                                                                                                         |  |  |  |  |  |  |

| Decrement f                                                                                                                                     |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                                                                                                                                 |  |  |  |  |  |  |

| [label] DECF f,d                                                                                                                                |  |  |  |  |  |  |

| $0 \le f \le 127$                                                                                                                               |  |  |  |  |  |  |

| d ∈ [0,1]                                                                                                                                       |  |  |  |  |  |  |

| (f) - 1 $\rightarrow$ (dest)                                                                                                                    |  |  |  |  |  |  |

| Z                                                                                                                                               |  |  |  |  |  |  |

| 00 0011 dfff ffff                                                                                                                               |  |  |  |  |  |  |

| Decrement register 'f'. If 'd' is 0, the<br>result is stored in the W register. If 'd'<br>is 1, the result is stored back in regis-<br>ter 'f'. |  |  |  |  |  |  |

| 1                                                                                                                                               |  |  |  |  |  |  |

| 1                                                                                                                                               |  |  |  |  |  |  |

| DECF CNT, 1                                                                                                                                     |  |  |  |  |  |  |

| Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                           |  |  |  |  |  |  |

| Decrement f, Skip if 0                                                                                                                          |  |  |  |  |  |  |

| [ <i>label</i> ] DECFSZ f,d                                                                                                                     |  |  |  |  |  |  |

| $0 \leq f \leq 127$                                                                                                                             |  |  |  |  |  |  |

| d ∈ [0,1]                                                                                                                                       |  |  |  |  |  |  |

|                                                                                                                                                 |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                       |                                                                                    |                                                                                             |                                                        |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                      |                                                                                    |                                                                                             |                                                        |  |  |  |  |

| Status Affected: | None                                                                                                                  |                                                                                    |                                                                                             |                                                        |  |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                     |                                                                                    |                                                                                             |                                                        |  |  |  |  |

| Description:     | The contendecrement<br>placed in t<br>result is placed<br>if the result<br>which is all<br>A NOP is e<br>two-cycle if | ted. If 'd' i<br>he W reg<br>aced back<br>It is 0, the<br>ready feto<br>xecuted in | s 0, the re<br>ister. If 'd' i<br>k in registe<br>next instru-<br>ched, is dis<br>nstead ma | sult is<br>is 1, the<br>er 'f'.<br>uction,<br>scarded. |  |  |  |  |

| Words:           | 1                                                                                                                     |                                                                                    |                                                                                             |                                                        |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                  |                                                                                    |                                                                                             |                                                        |  |  |  |  |

| Example          | HERE<br>CONTINU                                                                                                       | DECF<br>GOTO<br>JE<br>•                                                            | SZ CNI<br>LOC                                                                               |                                                        |  |  |  |  |

|                  | Before In<br>PC<br>After Inst<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC                                                  | = ado<br>ruction<br>= CN<br>= 0,<br>= ado<br>≠ 0,                                  | iress HERE<br>T - 1<br>iress CONT                                                           |                                                        |  |  |  |  |

| RETURN             | Return from Subroutine                                                                                          | RRF              | Rotate Right f through Carry                                                                                                                                                                                                               |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:            | [label] RETURN                                                                                                  | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                   |  |  |  |

| Operands:          | None                                                                                                            | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                          |  |  |  |

| Operation:         | $TOS \rightarrow PC$                                                                                            |                  | $d \in [0,1]$                                                                                                                                                                                                                              |  |  |  |

| Status Affected:   | None                                                                                                            | Operation:       | See description below                                                                                                                                                                                                                      |  |  |  |

| Encoding:          | 00 0000 0000 1000                                                                                               | Status Affected: | С                                                                                                                                                                                                                                          |  |  |  |

| Description:       | Return from subroutine. The stack is                                                                            | Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                                                          |  |  |  |

|                    | POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is                                                             |  |  |  |

| Words:             | 1                                                                                                               |                  | placed back in register 'f'.                                                                                                                                                                                                               |  |  |  |

| Cycles:<br>Example | 2<br>RETURN                                                                                                     |                  | C Register f                                                                                                                                                                                                                               |  |  |  |

|                    | After Interrupt                                                                                                 | Words:           | 1                                                                                                                                                                                                                                          |  |  |  |

|                    | PC = TOS                                                                                                        | Cycles:          | 1                                                                                                                                                                                                                                          |  |  |  |

|                    |                                                                                                                 | Example          | RRF REG1,0                                                                                                                                                                                                                                 |  |  |  |

|                    |                                                                                                                 |                  | Before Instruction       REG1       =       1110       0110         C       =       0       0         After Instruction       REG1       =       1110       0110         W       =       0111       0011         C       =       0       0 |  |  |  |

| RLF              | Rotate Left f t                                                                                                                                                                                               | hrough Carry |    |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----|--|--|

| Syntax:          | [label] RLF                                                                                                                                                                                                   | f,d          |    |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                             |              |    |  |  |

| Operation:       | See description                                                                                                                                                                                               | n below      |    |  |  |

| Status Affected: | С                                                                                                                                                                                                             |              |    |  |  |

| Encoding:        | 00 110                                                                                                                                                                                                        | 1 dfff ff    | ff |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is<br>stored back in register 'f'. |              |    |  |  |

| Words:           | 1                                                                                                                                                                                                             |              |    |  |  |

| Cycles:          | 1                                                                                                                                                                                                             |              |    |  |  |

|                  |                                                                                                                                                                                                               |              |    |  |  |

| Example          | RLF                                                                                                                                                                                                           | REG1,0       |    |  |  |

# SLEEP

| 02221            |                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                                                 |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0011                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Description:     | The power-down status bit, $\overrightarrow{PD}$ is<br>cleared. Time-out status bit, $\overrightarrow{TO}$ is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 10.8 for more details. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                                                |  |  |  |  |  |

#### 13.2 DC CHARACTERISTICS: F

# PIC16LCE62X-04 (Commercial, Industrial)

| DC CHARACTERISTICS |                     | $\begin{array}{rl} 0^{\circ}C &\leq TA \leq +70^{\circ}C \text{ for commercial a} \\ -40^{\circ}C &\leq TA \leq +125^{\circ}C \text{ for extended} \end{array}$ |      |      |           | $0^{\circ}C \le TA \le +85^{\circ}C$ for industrial and<br>$0^{\circ}C \le TA \le +70^{\circ}C$ for commercial and |                                                                                  |

|--------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Param<br>No.       | Sym                 | Characteristic                                                                                                                                                  | Min  | Тур† | Мах       | Units                                                                                                              | Conditions                                                                       |

| D001               | Vdd                 | Supply Voltage                                                                                                                                                  | 2.5  | -    | 5.5       | V                                                                                                                  | See Figure 13-1 through Figure 13-3                                              |

| D002               | Vdr                 | RAM Data Retention<br>Voltage (Note 1)                                                                                                                          | -    | 1.5* | -         | V                                                                                                                  | Device in SLEEP mode                                                             |

| D003               | VPOR                | VDD start voltage to<br>ensure Power-on Reset                                                                                                                   | -    | Vss  | -         | V                                                                                                                  | See section on power-on reset for details                                        |

| D004               | SVDD                | VDD rise rate to ensure<br>Power-on Reset                                                                                                                       | .05* | -    | -         | V/ms                                                                                                               | See section on power-on reset for details                                        |

| D005               | VBOR                | Brown-out Detect Voltage                                                                                                                                        | 3.7  | 4.0  | 4.35      | V                                                                                                                  | BOREN configuration bit is cleared                                               |