Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Dectano                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 896B (512 x 14)                                                            |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce623-04-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

# REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1    | R/W-1                                                                                                                                       | R/W-1                                                       | R/W-1        | R/W-1      | R/W-1                  | R/W-1 | R/W-1 |                                                                                                                   |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------|------------|------------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------|--|--|

| RBPU     | INTEDG                                                                                                                                      | TOCS                                                        | TOSE         | PSA        | PS2                    | PS1   | PS0   | R = Readable bit                                                                                                  |  |  |

| bit7     |                                                                                                                                             |                                                             |              |            |                        |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |  |  |

| bit 7:   | <b>RBPU</b> : PORTB Pull-up Enable bit<br>1 = PORTB pull-ups are disabled<br>0 = PORTB pull-ups are enabled by individual port latch values |                                                             |              |            |                        |       |       |                                                                                                                   |  |  |

| bit 6:   | INTEDG: In<br>1 = Interrup<br>0 = Interrup                                                                                                  | ot on rising                                                | g edge o     | f RB0/INT  |                        |       |       |                                                                                                                   |  |  |

| bit 5:   | <b>TOCS</b> : TMF<br>1 = Transiti<br>0 = Interna                                                                                            | ion on RA                                                   | 4/T0CKI      | pin        | (OUT)                  |       |       |                                                                                                                   |  |  |

| bit 4:   |                                                                                                                                             | ent on hig                                                  | h-to-low     | transition | on RA4/T0<br>on RA4/T0 |       |       |                                                                                                                   |  |  |

| bit 3:   | <b>PSA</b> : Prese<br>1 = Presca<br>0 = Presca                                                                                              | ler is assi                                                 | gned to t    | he WDT     | ) module               |       |       |                                                                                                                   |  |  |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : F                                                                                                                    | Prescaler I                                                 | Rate Sele    | ect bits   |                        |       |       |                                                                                                                   |  |  |

|          | Bit Value                                                                                                                                   | TMR0 Ra                                                     | te WD1       | Γ Rate     |                        |       |       |                                                                                                                   |  |  |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                        | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 :<br>3 1 : | 2<br>4     |                        |       |       |                                                                                                                   |  |  |

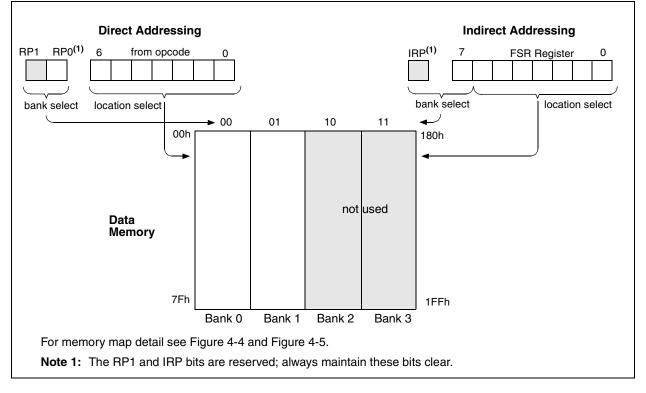

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16CE62X. A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

| EXAMPL    | E 4-1: | INDIRECT ADDRESSING |                      |  |  |  |  |

|-----------|--------|---------------------|----------------------|--|--|--|--|

|           | movlw  | 0x20                | ;initialize pointer  |  |  |  |  |

|           | movwf  | FSR                 | ;to RAM              |  |  |  |  |

| NEXT      | clrf   | INDF                | clear INDF register; |  |  |  |  |

|           | incf   | FSR                 | ;inc pointer         |  |  |  |  |

|           | btfss  | FSR,4               | ;all done?           |  |  |  |  |

|           | goto   | NEXT                | ;no clear next       |  |  |  |  |

|           |        |                     | ;yes continue        |  |  |  |  |

| CONTINUE: |        |                     |                      |  |  |  |  |

# FIGURE 4-7: DIRECT/INDIRECT ADDRESSING PIC16CE62X

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data pin.  |

TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

**Note 2:** This buffer is a Schmitt Trigger input when used in serial programming mode.

# TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx xxxx        | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111        | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111        | 1111 1111                       |

Legend: u = unchanged, x = unknown

**Note:** Shaded bits are not used by PORTB.

# 6.0 EEPROM PERIPHERAL OPERATION

The PIC16CE623/624/625 each have 128 bytes of EEPROM data memory. The EEPROM data memory supports a bi-directional, 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), and are mapped to bit1 and bit2, respectively, of the EEINTF register (SFR 90h). In addition, the power to the EEPROM can be controlled using bit0 (EEVDD) of the EEINTF register. For most applications, all that is required is calls to the following functions:

| ;<br>;<br>; | ; Inputs: EEPROM Address EEADDR           |  |  |  |  |  |  |

|-------------|-------------------------------------------|--|--|--|--|--|--|

| ;           | Outputs: Return 01 in W if OK, else       |  |  |  |  |  |  |

| ΄.          | return 00 in W                            |  |  |  |  |  |  |

| '           |                                           |  |  |  |  |  |  |

| i           | - · · · · · · · · · · · · · · · · · · ·   |  |  |  |  |  |  |

| ;           | Read_Current: Read EEPROM at address      |  |  |  |  |  |  |

| C١          | urrently held by EE device.               |  |  |  |  |  |  |

| ;           | Inputs: NONE                              |  |  |  |  |  |  |

| ;           | Outputs: EEPROM Data EEDATA               |  |  |  |  |  |  |

| ;           | Return 01 in W if OK, else                |  |  |  |  |  |  |

| ;           | return 00 in W                            |  |  |  |  |  |  |

| ;           |                                           |  |  |  |  |  |  |

| ;           | Read Random: Read EEPROM byte at supplied |  |  |  |  |  |  |

| ;           | address                                   |  |  |  |  |  |  |

| ;           | Inputs: EEPROM Address EEADDR             |  |  |  |  |  |  |

| ;           | Outputs: EEPROM Data EEDATA               |  |  |  |  |  |  |

| ;           | Return 01 in W if OK,                     |  |  |  |  |  |  |

|             | else return 00 in W                       |  |  |  |  |  |  |

| '           |                                           |  |  |  |  |  |  |

The code for these functions is available on our web site (www.microchip.com). The code will be accessed by either including the source code FL62XINC.ASM or by linking FLASH62X.ASM. FLASH62.IMC provides external definition to the calling program.

#### 6.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the memory.

For normal data transfer, SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

#### 6.0.2 SERIAL CLOCK

This SCL input is used to synchronize the data transfer to and from the memory.

#### 6.0.3 EEINTF REGISTER

The EEINTF register (SFR 90h) controls the access to the EEPROM. Register 6-1 details the function of each bit. User code must generate the clock and data signals.

### REGISTER 6-1: EEINTF REGISTER (ADDRESS 90h)

| U-0              | U-0                                                                                                                                                                     | U-0       | U-0         | U-0 | R/W-1 | R/W-1 | R/W-1 |                                                                                       |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-----|-------|-------|-------|---------------------------------------------------------------------------------------|--|

|                  | _                                                                                                                                                                       | _         | _           | _   | EESCL | EESDA | EEVDD | R = Readable bit                                                                      |  |

| bit7<br>bit 7-3: | Unimpler                                                                                                                                                                | nented: F | lead as '0' |     |       |       | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 2:           | EESCL: Clock line to the EEPROM<br>1 = Clock high<br>0 = Clock low                                                                                                      |           |             |     |       |       |       |                                                                                       |  |

| bit 1:           | <b>EESDA</b> : Data line to EEPROM<br>1 = Data line is high (pin is tri-stated, line is pulled high by a pull-up resistor)<br>0 = Data line is low                      |           |             |     |       |       |       |                                                                                       |  |

| bit 0:           | <b>EEVDD</b> : VDD control bit for EEPROM<br>1 = VDD is turned on to EEPROM<br>0 = VDD is turned off to EEPROM (all pins are tri-stated and the EEPROM is powered down) |           |             |     |       |       |       |                                                                                       |  |

| Note:            | EESDA, EESCL and EEVDD will read '0' if EEVDD is turned off.                                                                                                            |           |             |     |       |       |       |                                                                                       |  |

NOTES:

The code example in Example 8-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 8-1: INITIALIZING COMPARATOR MODULE

| FLAG_REG | F EQU        | 0X20                              |

|----------|--------------|-----------------------------------|

| CLRF     | FLAG_REG     | ;Init flag register               |

| CLRF     | PORTA        | ;Init PORTA                       |

| MOVF     | CMCON,W      | ;Move comparator contents to W    |

| ANDLW    | 0xC0         | ;Mask comparator bits             |

| IORWF    | FLAG_REG,F   | ;Store bits in flag register      |

| MOVLW    | 0x03         | ;Init comparator mode             |

| MOVWF    | CMCON        | ;CM<2:0> = 011                    |

| BSF      | STATUS, RPO  | ;Select Bank1                     |

| MOVLW    | 0x07         | ;Initialize data direction        |

| MOVWF    | TRISA        | ;Set RA<2:0> as inputs            |

|          |              | ;RA<4:3> as outputs               |

|          |              | ;TRISA<7:5> always read `0'       |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| CALL     | DELAY 10     | ;10µs delay                       |

| MOVF     | CMCON, F     | ;Read CMCONtoend change condition |

| BCF      | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF      | STATUS, RPO  | ;Select Bank 1                    |

| BSF      | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| BSF      | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF      | INTCON, GIE  | ;Global interrupt enable          |

|          |              |                                   |

#### 8.2 Comparator Operation

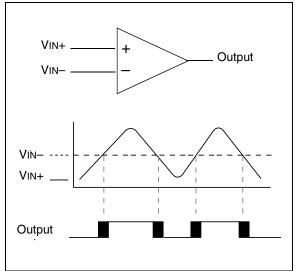

A single comparator is shown in Figure 8-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN–, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN–, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 8-2 represent the uncertainty due to input offsets and response time.

### 8.3 Comparator Reference

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal that is present at VIN– is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 8-2).

FIGURE 8-2: SINGLE COMPARATOR

#### 8.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 8.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 8-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs, otherwise the maximum delay of the comparators should be used (Table 13-1).

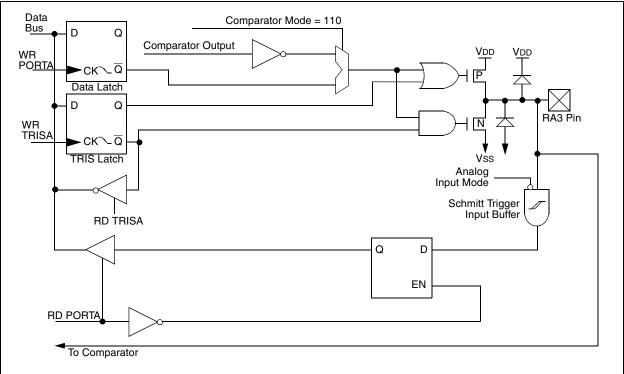

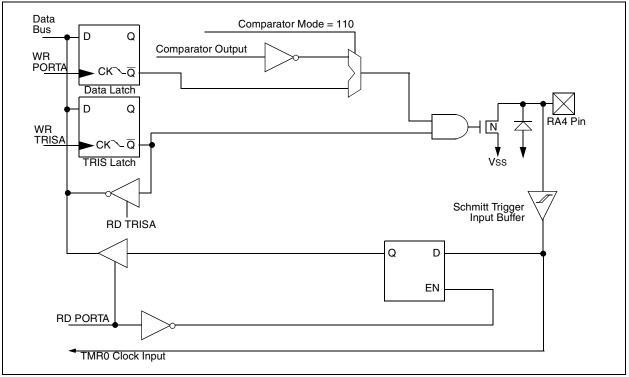

#### 8.5 <u>Comparator Outputs</u>

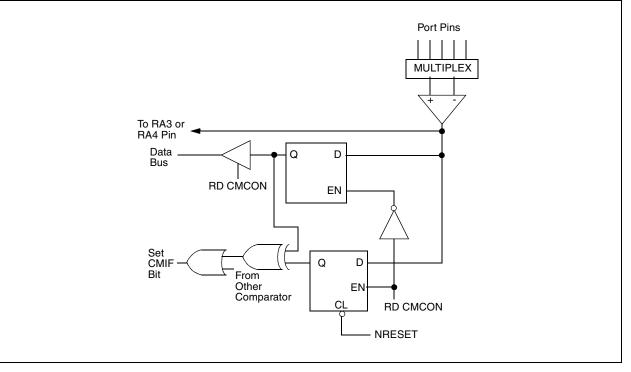

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 8-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

### FIGURE 8-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

# 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

### 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

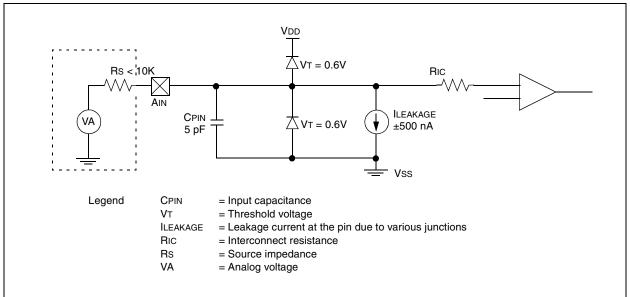

### 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

### FIGURE 8-4: ANALOG INPUT MODEL

# 10.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16CE62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-Up Timer (OST) Brown-out Reset (BOD)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

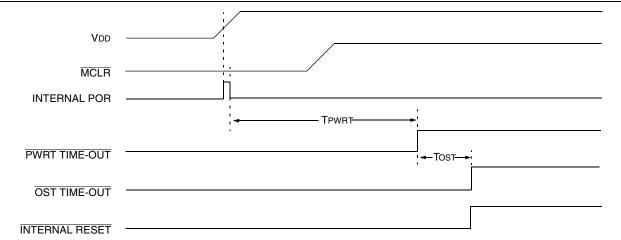

The PIC16CE62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, and is designed to keep the part in reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

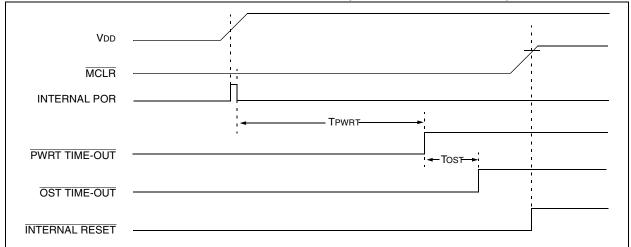

#### FIGURE 10-9: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 2

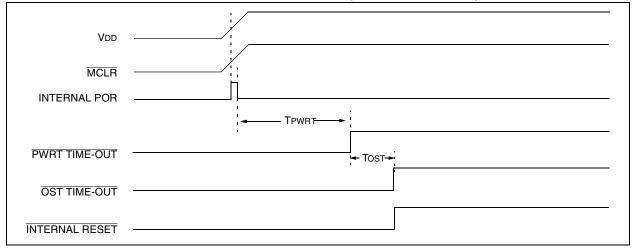

#### FIGURE 10-10: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

<sup>© 1998-2013</sup> Microchip Technology Inc.

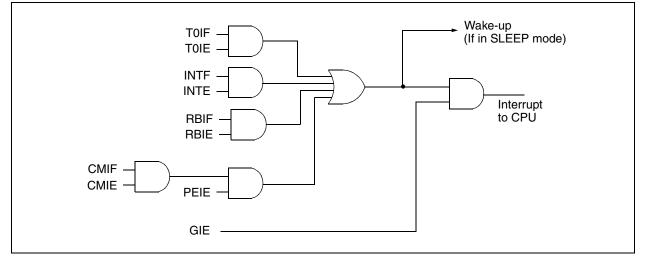

#### 10.5 Interrupts

The PIC16CE62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PortB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which re-enable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of

the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends on when the interrupt event occurs (Figure 10-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

### FIGURE 10-15: INTERRUPT LOGIC

### 10.9 <u>Code Protection</u>

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip  | does   | not   | recommend | code |

|-------|------------|--------|-------|-----------|------|

|       | protecting | windov | ved d | evices.   |      |

#### 10.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. Only the least significant 4 bits of the ID locations are used.

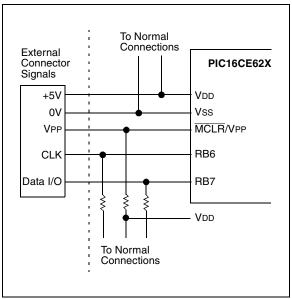

#### 10.11 In-Circuit Serial Programming

The PIC16CE62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specifications (Literature #DS30228).

A typical in-circuit serial programming connection is shown in Figure 10-20.

#### FIGURE 10-20: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

# TABLE 11-2: PIC16CE62X INSTRUCTION SET

| Mnemonic,<br>Operands |         | Description                  | Cycles | 14-Bit Opcode |      |      |      | Status   | Notes |

|-----------------------|---------|------------------------------|--------|---------------|------|------|------|----------|-------|

|                       |         |                              |        | MSb           |      | LSb  |      | Affected |       |

| BYTE-ORIE             | NTED    | FILE REGISTER OPERATIONS     |        |               |      |      |      |          |       |

| ADDWF                 | f, d    | Add W and f                  | 1      | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |

| ANDWF                 | f, d    | AND W with f                 | 1      | 00            | 0101 | dfff | ffff | Z        | 1,2   |

| CLRF                  | f       | Clear f                      | 1      | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                  | -       | Clear W                      | 1      | 00            | 0001 | 0000 | 0011 | Z        |       |

| COMF                  | f, d    | Complement f                 | 1      | 00            | 1001 | dfff | ffff | Z        | 1,2   |

| DECF                  | f, d    | Decrement f                  | 1      | 00            | 0011 | dfff | ffff | Z        | 1,2   |

| DECFSZ                | f, d    | Decrement f, Skip if 0       | 1(2)   | 00            | 1011 | dfff | ffff |          | 1,2,  |

| INCF                  | f, d    | Increment f                  | 1      | 00            | 1010 | dfff | ffff | Z        | 1,2   |

| INCFSZ                | f, d    | Increment f, Skip if 0       | 1(2)   | 00            | 1111 | dfff | ffff |          | 1,2,  |

| IORWF                 | f, d    | Inclusive OR W with f        | 1      | 00            | 0100 | dfff | ffff | Z        | 1,2   |

| MOVF                  | f, d    | Move f                       | 1      | 00            | 1000 | dfff | ffff | Z        | 1,2   |

| MOVWF                 | f       | Move W to f                  | 1      | 00            | 0000 | lfff | ffff |          |       |

| NOP                   | -       | No Operation                 | 1      | 00            | 0000 | 0xx0 | 0000 |          |       |

| RLF                   | f, d    | Rotate Left f through Carry  | 1      | 00            | 1101 | dfff | ffff | С        | 1,2   |

| RRF                   | f, d    | Rotate Right f through Carry | 1      | 00            | 1100 | dfff | ffff | С        | 1,2   |

| SUBWF                 | f, d    | Subtract W from f            | 1      | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |

| SWAPF                 | f, d    | Swap nibbles in f            | 1      | 00            | 1110 | dfff | ffff |          | 1,2   |

| XORWF                 | f, d    | Exclusive OR W with f        | 1      | 00            | 0110 | dfff | ffff | Z        | 1,2   |

| BIT-ORIENT            | FED FIL | E REGISTER OPERATIONS        |        |               |      |      |      | •        |       |

| BCF                   | f, b    | Bit Clear f                  | 1      | 01            | 00bb | bfff | ffff |          | 1,2   |

| BSF                   | f, b    | Bit Set f                    | 1      | 01            | 01bb | bfff | ffff |          | 1,2   |

| BTFSC                 | f, b    | Bit Test f, Skip if Clear    | 1 (2)  | 01            | 10bb | bfff | ffff |          | 3     |

| BTFSS                 | f, b    | Bit Test f, Skip if Set      | 1 (2)  | 01            | 11bb | bfff | ffff |          | 3     |

| LITERAL A             | ND CO   | NTROL OPERATIONS             |        |               |      |      |      |          |       |

| ADDLW                 | k       | Add literal and W            | 1      | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |

| ANDLW                 | k       | AND literal with W           | 1      | 11            | 1001 | kkkk | kkkk | Z        |       |

| CALL                  | k       | Call subroutine              | 2      | 10            | 0kkk | kkkk | kkkk |          |       |

| CLRWDT                | -       | Clear Watchdog Timer         | 1      | 00            | 0000 | 0110 | 0100 | TO,PD    |       |

| GOTO                  | k       | Go to address                | 2      | 10            | 1kkk | kkkk | kkkk |          |       |

| IORLW                 | k       | Inclusive OR literal with W  | 1      | 11            | 1000 | kkkk | kkkk | Z        |       |

| MOVLW                 | k       | Move literal to W            | 1      | 11            | 00xx | kkkk | kkkk |          |       |

| RETFIE                | -       | Return from interrupt        | 2      | 00            | 0000 | 0000 | 1001 |          |       |

| RETLW                 | k       | Return with literal in W     | 2      | 11            | 01xx | kkkk | kkkk |          |       |

| RETURN                | -       | Return from Subroutine       | 2      | 00            | 0000 | 0000 | 1000 |          |       |

|                       | -       | Go into standby mode         | 1      | 00            | 0000 | 0110 | 0011 | TO,PD    |       |

| SLEEP                 |         |                              |        | 1             |      |      |      |          | 1     |

| SUBLW                 | k       | Subtract W from literal      | 1      | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# 11.1 Instruction Descriptions

| ADDLW            | Add Lite                                                                                                                | ral and V | w            |      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------|-----------|--------------|------|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                |           |              |      |  |  |  |

| Operands:        | $0 \le k \le 25$                                                                                                        | 55        |              |      |  |  |  |

| Operation:       | (W) + k –                                                                                                               | → (W)     |              |      |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                |           |              |      |  |  |  |

| Encoding:        | 11                                                                                                                      | 111x      | kkkk         | kkkk |  |  |  |

| Description:     | The contents of the W register are<br>added to the eight bit literal 'k' and the<br>result is placed in the W register. |           |              |      |  |  |  |

| Words:           | 1                                                                                                                       |           |              |      |  |  |  |

| Cycles:          | 1                                                                                                                       |           |              |      |  |  |  |

| Example          | ADDLW                                                                                                                   | 0x15      |              |      |  |  |  |

|                  | After Inst                                                                                                              | W =       | 0x10<br>0x25 |      |  |  |  |

| ANDLW            | AND Literal with W                                                                                                  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |  |  |  |  |  |

| Status Affected: | Z                                                                                                                   |  |  |  |  |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                   |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |

| Words:           | 1                                                                                                                   |  |  |  |  |  |

| Cycles:          | 1                                                                                                                   |  |  |  |  |  |

| Example          | ANDLW 0x5F                                                                                                          |  |  |  |  |  |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                     |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                 |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                           |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                      |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                    |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                           |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                           |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                           |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                                |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                 |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                                |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |

#### 13.2 DC CHARACTERISTICS: F

#### PIC16LCE62X-04 (Commercial, Industrial)

| DC CHARACTERISTICS |                     |                                                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |           |          |                                                                                  |

|--------------------|---------------------|----------------------------------------------------------------|------------------------------------------------------|------|-----------|----------|----------------------------------------------------------------------------------|

| Param<br>No.       | Sym                 | Characteristic                                                 | Min                                                  | Тур† | Max       | Units    | Conditions                                                                       |

| D001               | Vdd                 | Supply Voltage                                                 | 2.5                                                  | -    | 5.5       | V        | See Figure 13-1 through Figure 13-3                                              |

| D002               | Vdr                 | RAM Data Retention<br>Voltage (Note 1)                         | -                                                    | 1.5* | -         | V        | Device in SLEEP mode                                                             |

| D003               | VPOR                | VDD start voltage to<br>ensure Power-on Reset                  | -                                                    | Vss  | -         | V        | See section on power-on reset for details                                        |

| D004               | SVDD                | VDD rise rate to ensure<br>Power-on Reset                      | .05*                                                 | -    | -         | V/ms     | See section on power-on reset for details                                        |

| D005               | VBOR                | Brown-out Detect Voltage                                       | 3.7                                                  | 4.0  | 4.35      | V        | BOREN configuration bit is cleared                                               |

| D010               | IDD                 | Supply Current (Note 2)                                        | -                                                    | 1.2  | 2.0       | mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)*                |

|                    |                     |                                                                | -                                                    | -    | 1.1       | mA       | FOSC = 4 MHz, $VDD = 2.5V$ , $WDT$ disabled,                                     |

|                    |                     |                                                                | -                                                    | 35   | 70        | μA       | XT osc mode, (Note 4)<br>Fosc = 32 kHz, VDD = 2.5V, WDT disabled,<br>LP osc mode |

| D020               | IPD                 | Power Down Current (Note 3)                                    | _                                                    | -    | 2.0       | μA       | VDD = 2.5V                                                                       |

|                    |                     |                                                                | -                                                    | -    | 2.2       | μA       | VDD = 3.0V*                                                                      |

|                    |                     |                                                                | -                                                    | -    | 9.0       | μA       | VDD = 5.5V                                                                       |

|                    |                     |                                                                | -                                                    | -    | 15        | μA       | VDD = 5.5V Extended                                                              |

| D022               | $\Delta$ IWDT       | WDT Current (Note 5)                                           | -                                                    | 6.0  | 10        | μA       | VDD=4.0V                                                                         |

| D022A              | $\Delta$ IBOR       | Brown-out Reset Current                                        | _                                                    | 75   | 12<br>125 | μΑ<br>μΑ | $(125^{\circ}C)$<br>BOD enabled, VDD = 5.0V                                      |

| D023               |                     | (Note 5)<br>Comparator Current for each<br>Comparator (Note 5) | -                                                    | 30   | 60        | μA       | VDD = 4.0V                                                                       |

| D023A              | $\Delta$ IVREF      | VREF Current (Note 5)                                          | -                                                    | 80   | 135       | μA       | VDD = 4.0V                                                                       |

|                    | $\Delta$ IEE Write  | Operating Current                                              | -                                                    |      | 3         | mA       | Vcc = 5.5V, SCL = 400 kHz                                                        |

|                    | $\Delta IEE \ Read$ | Operating Current                                              | -                                                    |      | 1         | mA       |                                                                                  |

|                    | $\Delta IEE$        | Standby Current                                                | -                                                    |      | 30        | μA       | VCC = 3.0V, EE VDD = VCC                                                         |

|                    | $\Delta IEE$        | Standby Current                                                | -                                                    |      | 100       | μA       | VCC = 3.0V, EE VDD = VCC                                                         |

| 1A                 | Fosc                | LP Oscillator Operating Frequency                              | 0                                                    | —    | 200       | kHz      | All temperatures                                                                 |

|                    |                     | RC Oscillator Operating Frequency                              |                                                      | —    | 4         | MHz      | All temperatures                                                                 |

|                    |                     | XT Oscillator Operating Frequency                              | 0                                                    | —    | 4<br>20   | MHz      | All temperatures                                                                 |

|                    |                     | HS Oscillator Operating Frequency                              | -                                                    | _    | 20        | MHz      | All temperatures                                                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

3: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

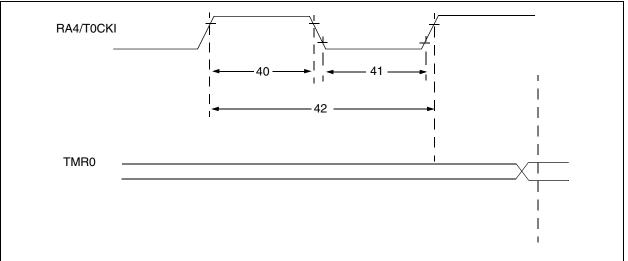

# FIGURE 13-9: TIMER0 CLOCK TIMING

#### **TABLE 13-6:** TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic         |                | Min                    | Тур† | Max | Units | Conditions                            |

|------------------|------|------------------------|----------------|------------------------|------|-----|-------|---------------------------------------|

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 TCY + 20*          | _    | _   | ns    |                                       |

|                  |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 TCY + 20*          | _    | _   | ns    |                                       |

|                  |      |                        | With Prescaler | 10*                    | _    | _   | ns    |                                       |

| 42               | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N |      | _   | ns    | N = prescale value<br>(1, 2, 4,, 256) |

t

These parameters are characterized but not tested. Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

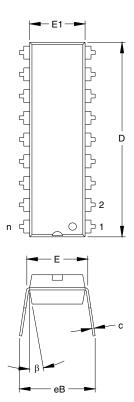

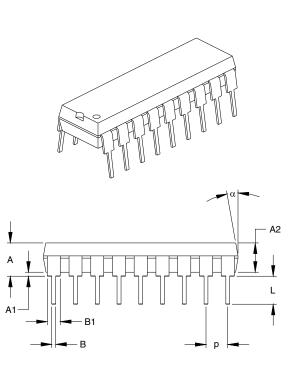

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES*   |      |      | MILLIMETERS |       |       |       |

|----------------------------|-----------|------|------|-------------|-------|-------|-------|

| Dimensio                   | on Limits | MIN  | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n         |      | 18   |             |       | 18    |       |

| Pitch                      | р         |      | .100 |             |       | 2.54  |       |

| Top to Seating Plane       | Α         | .140 | .155 | .170        | 3.56  | 3.94  | 4.32  |

| Molded Package Thickness   | A2        | .115 | .130 | .145        | 2.92  | 3.30  | 3.68  |

| Base to Seating Plane      | A1        | .015 |      |             | 0.38  |       |       |

| Shoulder to Shoulder Width | Е         | .300 | .313 | .325        | 7.62  | 7.94  | 8.26  |

| Molded Package Width       | E1        | .240 | .250 | .260        | 6.10  | 6.35  | 6.60  |

| Overall Length             | D         | .890 | .898 | .905        | 22.61 | 22.80 | 22.99 |

| Tip to Seating Plane       | L         | .125 | .130 | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С         | .008 | .012 | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1        | .045 | .058 | .070        | 1.14  | 1.46  | 1.78  |

| Lower Lead Width           | В         | .014 | .018 | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing        | eB        | .310 | .370 | .430        | 7.87  | 9.40  | 10.92 |

| Mold Draft Angle Top       | α         | 5    | 10   | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β         | 5    | 10   | 15          | 5     | 10    | 15    |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001

Drawing No. C04-007

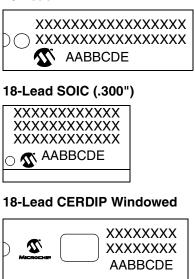

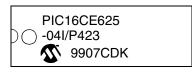

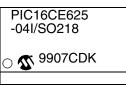

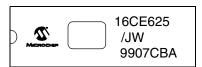

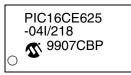

#### 14.1 Package Marking Information

#### **18-Lead PDIP**

#### 20-Lead SSOP

#### Example

# Example

### Example

#### Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                     | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |

# PIC16XXXXX FAMILY

# READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| TO:<br>RE: |                                                                              | Total Pages Sent                          |  |  |  |  |  |

|------------|------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

|            | n: Name                                                                      |                                           |  |  |  |  |  |

| FIU        |                                                                              |                                           |  |  |  |  |  |

|            | Company<br>Address                                                           |                                           |  |  |  |  |  |

|            | City / State / ZIP / Country                                                 |                                           |  |  |  |  |  |

|            | Telephone: ()                                                                | FAX: ()                                   |  |  |  |  |  |

| Арр        | lication (optional):                                                         |                                           |  |  |  |  |  |

| Wo         | uld you like a reply?YN                                                      |                                           |  |  |  |  |  |

|            | ice: PIC16xxxxxx family                                                      | Literature Number: DS40182D               |  |  |  |  |  |

| Que        | estions:                                                                     |                                           |  |  |  |  |  |

| 1.         | What are the best features of this document?                                 |                                           |  |  |  |  |  |

| _          |                                                                              |                                           |  |  |  |  |  |

| 2.         | How does this document meet your hardware and s                              | ottware development needs?                |  |  |  |  |  |

|            |                                                                              |                                           |  |  |  |  |  |

| 3.         | . Do you find the organization of this document easy to follow? If not, why? |                                           |  |  |  |  |  |

|            |                                                                              |                                           |  |  |  |  |  |

| 4.         | What additions to the document do you think would                            | enhance the structure and subject?        |  |  |  |  |  |

|            |                                                                              |                                           |  |  |  |  |  |

| 5.         | What deletions from the document could be made w                             | rithout affecting the overall usefulness? |  |  |  |  |  |

|            |                                                                              |                                           |  |  |  |  |  |

| 6.         | Is there any incorrect or misleading information (what                       | at and where)?                            |  |  |  |  |  |

|            |                                                                              |                                           |  |  |  |  |  |

| 7.         | How would you improve this document?                                         |                                           |  |  |  |  |  |

|            |                                                                              |                                           |  |  |  |  |  |