Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce623-04i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | General Description                           | 3     |

|-------|-----------------------------------------------|-------|

| 2.0   | PIC16CE62X Device Varieties                   | 5     |

| 3.0   | Architectural Overview                        |       |

| 4.0   | Memory Organization                           | 11    |

| 5.0   | I/O Ports                                     |       |

| 6.0   | EEPROM Peripheral Operation                   | 29    |

| 7.0   | Timer0 Module                                 |       |

| 8.0   | Comparator Module                             | 41    |

| 9.0   | Voltage Reference Module                      | 47    |

| 10.0  | Special Features of the CPU                   | 49    |

| 11.0  | Instruction Set Summary                       | 65    |

|       | Development Support                           |       |

|       | Electrical Specifications                     |       |

| 14.0  | Packaging Information                         | 97    |

| Appe  | ndix A: Code for Accessing EEPROM Data Memory | 103   |

| Index |                                               | 105   |

| On Li | ne Support                                    | . 107 |

| Read  | ne Support<br>er Response                     | 108   |

| PIC1  | 6CE62X Product Identification System          | . 109 |

#### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

# 1.0 GENERAL DESCRIPTION

The PIC16CE62X are 18 and 20-Pin EPROM-based members of the versatile PIC<sup>®</sup> family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with EEPROM data memory.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16CE62X family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CE62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16CE623 and PIC16CE624 have 96 bytes of RAM. The PIC16CE625 has 128 bytes of RAM. Each microcontroller contains a 128x8 EEPROM memory array for storing non-volatile information, such as calibration data or security codes. This memory has an endurance of 1,000,000 erase/write cycles and a retention of 40 plus years.

Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16CE62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low-cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16CE62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and reset. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development, while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16CE62X mid-range microcontroller families.

A simplified block diagram of the PIC16CE62X is shown in Figure 3-1.

The PIC16CE62X series fits perfectly in applications ranging from multi-pocket battery chargers to low-power remote sensors. The EPROM technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high-performance, ease of use and I/O flexibility make the PIC16CE62X very versatile.

# 1.1 <u>Development Support</u>

The PIC16CE62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler is also available.

# TABLE 1-1: PIC16CE62X FAMILY OF DEVICES

|             |                                      | PIC16CE623                          | PIC16CE624                          | PIC16CE625                          |

|-------------|--------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                  | 20                                  | 20                                  |

| Momory      | EPROM Program Memory (x14 words)     | 512                                 | 1K                                  | 2K                                  |

| Memory      | Data Memory (bytes)                  | 96                                  | 96                                  | 128                                 |

| Peripherals | EEPROM Data Memory (bytes)           | 128                                 | 128                                 | 128                                 |

|             | Timer Module(s)                      | TMR0                                | TMR0                                | TMR0                                |

| Peripherais | Comparators(s)                       | 2                                   | 2                                   | 2                                   |

|             | Internal Reference Voltage           | Yes                                 | Yes                                 | Yes                                 |

|             | Interrupt Sources                    | 4                                   | 4                                   | 4                                   |

|             | I/O Pins                             | 13                                  | 13                                  | 13                                  |

|             | Voltage Range (Volts)                | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                             |

| Features    | Brown-out Reset                      | Yes                                 | Yes                                 | Yes                                 |

|             | Packages                             | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

All PIC<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16CE62X Family devices use serial programming with clock pin RB6 and data pin RB7.

| Name                                                                                                                    | DIP/<br>SOIC<br>Pin # | SSOP<br>Pin # | l/O/P<br>Type | Buffer<br>Type        | Description                                                                                                                                                                                                       |  |

|-------------------------------------------------------------------------------------------------------------------------|-----------------------|---------------|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| OSC1/CLKIN                                                                                                              | 16                    | 18            | I             | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                             |  |

| OSC2/CLKOUT                                                                                                             | 15                    | 17            | 0             | -                     | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |  |

| MCLR/Vpp                                                                                                                | 4                     | 4             | I/P           | ST                    | Master clear (reset) input/programming voltage input.<br>This pin is an active low reset to the device.                                                                                                           |  |

|                                                                                                                         |                       |               |               |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                               |  |

| RA0/AN0                                                                                                                 | 17                    | 19            | I/O           | ST                    | Analog comparator input                                                                                                                                                                                           |  |

| RA1/AN1                                                                                                                 | 18                    | 20            | I/O           | ST                    | Analog comparator input                                                                                                                                                                                           |  |

| RA2/AN2/VREF                                                                                                            | 1                     | 1             | I/O           | ST                    | Analog comparator input or VREF output                                                                                                                                                                            |  |

| RA3/AN3                                                                                                                 | 2                     | 2             | I/O           | ST                    | Analog comparator input /output                                                                                                                                                                                   |  |

| RA4/T0CKI                                                                                                               | 3                     | 3             | I/O           | ST                    | Can be selected to be the clock input to the Timer0<br>timer/counter or a comparator output. Output is open<br>drain type.                                                                                        |  |

|                                                                                                                         |                       |               |               |                       | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                               |  |

| RB0/INT                                                                                                                 | 6                     | 7             | I/O           | TTL/ST(1)             | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                                        |  |

| RB1                                                                                                                     | 7                     | 8             | I/O           | TTL                   |                                                                                                                                                                                                                   |  |

| RB2                                                                                                                     | 8                     | 9             | I/O           | TTL                   |                                                                                                                                                                                                                   |  |

| RB3                                                                                                                     | 9                     | 10            | I/O           | TTL                   |                                                                                                                                                                                                                   |  |

| RB4                                                                                                                     | 10                    | 11            | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                          |  |

| RB5                                                                                                                     | 11                    | 12            | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                          |  |

| RB6                                                                                                                     | 12                    | 13            | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming clock.                                                                                                                                                                |  |

| RB7                                                                                                                     | 13                    | 14            | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming data.                                                                                                                                                                 |  |

| Vss                                                                                                                     | 5                     | 5,6           | Р             | l –                   | Ground reference for logic and I/O pins.                                                                                                                                                                          |  |

| Vdd                                                                                                                     | 14                    | 15,16         | Р             | —                     | Positive supply for logic and I/O pins.                                                                                                                                                                           |  |

| Legend: O = output I/O = input/output P = power<br>— = Not used I = Input ST = Schmitt Trigger input<br>TTL = TTL input |                       |               |               |                       |                                                                                                                                                                                                                   |  |

**TABLE 3-1: PIC16CE62X PINOUT DESCRIPTION**

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt. **Note 2:** This buffer is a Schmitt Trigger input when used in serial programming mode.

# 4.2 Data Memory Organization

The data memory (Figure 4-4 and Figure 4-5) is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-7Fh (Bank0) on the PIC16CE623/624 and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16CE625 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1. In all three microcontrollers, address space F0h-FFh (Bank1) is mapped to 70-7Fh (Bank0) as common RAM.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $96 \times 8$  in the PIC16CE623/624 and 128 x 8 in the PIC16CE625. Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

### FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16CE623/624

| File<br>Address | 3                                         | -                   | File<br>Address |

|-----------------|-------------------------------------------|---------------------|-----------------|

| 00h             | INDF <sup>(1)</sup>                       | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                                      | OPTION              | 81h             |

| 02h             | PCL                                       | PCL                 | 82h             |

| 03h             | STATUS                                    | STATUS              | 83h             |

| 04h             | FSR                                       | FSR                 | 84h             |

| 05h             | PORTA                                     | TRISA               | 85h             |

| 06h             | PORTB                                     | TRISB               | 86h             |

| 07h             |                                           |                     | 87h             |

| 08h             |                                           |                     | 88h             |

| 09h             |                                           |                     | 89h             |

| 0Ah             | PCLATH                                    | PCLATH              | 8Ah             |

| 0Bh             | INTCON                                    | INTCON              | 8Bh             |

| 0Ch             | PIR1                                      | PIE1                | 8Ch             |

| 0Dh             |                                           |                     | 8Dh             |

| 0Eh             |                                           | PCON                | 8Eh             |

| 0Fh             |                                           |                     | 8Fh             |

| 10h             |                                           | EEINTF              | 90h             |

| 11h             |                                           |                     | 91h             |

| 12h             |                                           |                     | 92h             |

| 13h             |                                           |                     | 93h             |

| 14h             |                                           |                     | 94h             |

| 15h             |                                           |                     | 95h             |

| 16h             |                                           |                     | 96h             |

| 17h             |                                           |                     | 97h             |

| 18h             |                                           |                     | 98h             |

| 19h             |                                           |                     | 99h             |

| 1Ah             |                                           |                     | 9Ah             |

| 1Bh             |                                           |                     | 9Bh             |

| 1Ch             |                                           |                     | 9Ch             |

| 1Dh             |                                           |                     | 9Dh             |

| 1Eh             |                                           |                     | 9Eh             |

| 1Fh             | CMCON                                     | VRCON               | 9Fh             |

| 20h             |                                           |                     | A0h             |

|                 | General<br>Purpose<br>Register            |                     |                 |

|                 |                                           |                     |                 |

|                 |                                           |                     | EFh             |

|                 |                                           | Accesses            | F0h             |

| 7Fh             |                                           | 70h-7Fh             | FFh             |

| / [1]           | Bank 0                                    | Bank 1              |                 |

|                 | blemented data me<br>Not a physical regis | •                   | ead as '0'.     |

#### FIGURE 4-5: DATA MEMORY MAP FOR THE PIC16CE625

| File     |                      |                     | File       |

|----------|----------------------|---------------------|------------|

| Address  | ;                    |                     | Address    |

| 00h      | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h        |

| 01h      | TMR0                 | OPTION              | 81h        |

| 02h      | PCL                  | PCL                 | 82h        |

| 03h      | STATUS               | STATUS              | 83h        |

| 04h      | FSR                  | FSR                 | 84h        |

| 05h      | PORTA                | TRISA               | 85h        |

| 06h      | PORTB                | TRISB               | 86h        |

| 07h      |                      |                     | 87h        |

| 08h      |                      |                     | 88h        |

| 09h      |                      |                     | 89h        |

| 0Ah      | PCLATH               | PCLATH              | 8Ah        |

| 0Bh      | INTCON               | INTCON              | 8Bh        |

| 0Ch      | PIR1                 | PIE1                | 8Ch        |

| 0Dh      |                      |                     | 8Dh        |

| 0Eh      |                      | PCON                | 8Eh        |

| 0Fh      |                      |                     | 8Fh        |

| 10h      |                      | EEINTF              | 90h        |

| 11h      |                      |                     | 91h        |

| 12h      |                      |                     | 92h        |

| 13h      |                      |                     | 93h        |

| 14h      |                      |                     | 94h        |

| 15h      |                      |                     | 95h        |

| 16h      |                      |                     | 96h        |

| 17h      |                      |                     | 97h        |

| 18h      |                      |                     | 98h        |

| 19h      |                      |                     | 99h        |

| 1Ah      |                      |                     | 9Ah        |

| 1Bh      |                      |                     | 9Bh        |

| 1Ch      |                      |                     | 9Ch        |

| 1Dh      |                      |                     | 9Dh        |

| 1Eh      |                      |                     | 9Eh        |

| 1Fh      | CMCON                | VRCON               | 9Fh        |

| 20h      |                      |                     | A0h        |

|          | General              | General             | AUII       |

|          | Purpose<br>Register  | Purpose<br>Register |            |

|          | negistei             | negister            | BFh        |

|          |                      |                     | C0h        |

|          |                      |                     |            |

|          |                      | _                   | F0h        |

|          |                      | Accesses            |            |

| 751      |                      | 70h-7Fh             | FFh        |

| 7Fh I    | Bank 0               | Bank 1              | J FFN      |

| <b>—</b> |                      |                     |            |

|          | plemented data me    |                     | ad as '0'. |

| Note 1:  | Not a physical regis | ster.               |            |

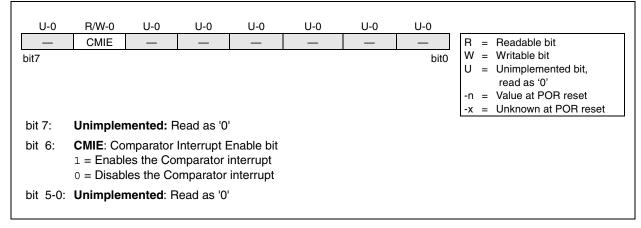

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bit for the comparator interrupt.

# REGISTER 4-4: PIE1 REGISTER (ADDRESS 8CH)

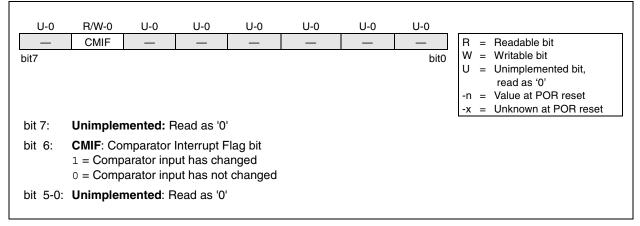

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt   |  |  |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of    |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the global      |  |  |  |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User               |  |  |  |  |  |  |  |

|       | software should ensure the appropriate          |  |  |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling |  |  |  |  |  |  |  |

|       | an interrupt.                                   |  |  |  |  |  |  |  |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

# 5.0 I/O PORTS

The PIC16CE62X parts have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

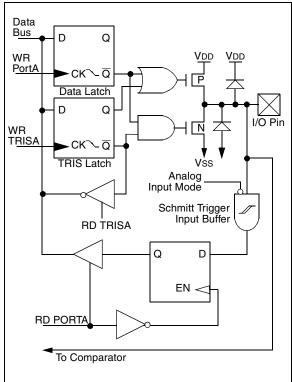

# 5.1 PORTA and TRISA Registers

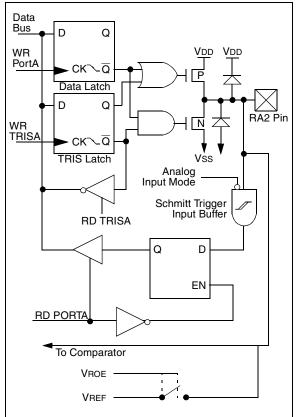

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the TOCKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a hi- impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (Comparator Control Register) register and the VRCON (Voltage Reference Control Register) register. When selected as a comparator input, these pins will read as '0's.

#### FIGURE 5-1: BLOCK DIAGRAM OF RA<1:0> PINS

| Note: | On reset, the TRISA register is set to all  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | inputs. The digital inputs are disabled and |  |  |  |  |  |

|       | the comparator inputs are forced to ground  |  |  |  |  |  |

|       | to reduce excess current consumption.       |  |  |  |  |  |

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### **EXAMPLE 5-1: INITIALIZING PORTA**

| CLRF  | PORTA   |     | ;Initialize PORTA by setting ;output data latches |

|-------|---------|-----|---------------------------------------------------|

| MOVLW | 0X07    |     | ;Turn comparators off and                         |

| MOVWF | CMCON   |     | ;enable pins for I/O                              |

|       |         |     | ;functions                                        |

| BSF   | STATUS, | RP0 | ;Select Bank1                                     |

| MOVLW | 0x1F    |     | ;Value used to initialize                         |

|       |         |     | ;data direction                                   |

| MOVWF | TRISA   |     | ;Set RA<4:0> as inputs                            |

|       |         |     | ;TRISA<7:5> are always                            |

|       |         |     | ;read as '0'.                                     |

#### FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

<sup>© 1998-2013</sup> Microchip Technology Inc.

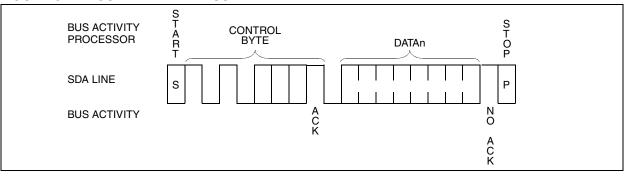

# FIGURE 6-8: RANDOM READ

BUS ACTIVITY

. .

A C K

DATAn

DATAn + 1

DATAn + 2

N O

A C K

DATAn + X

#### 10.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

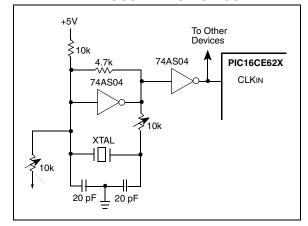

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

Figure 10-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 10-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

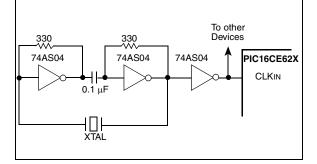

Figure 10-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a  $180^{\circ}$  phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 10-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

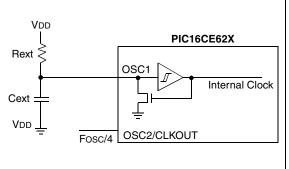

#### 10.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-5 shows how the R/C combination is connected to the PIC16CE62X. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (i.e., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 14.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 14.0 for variation of oscillator frequency due to VDD for given Rext/Cext values, as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

# FIGURE 10-5: RC OSCILLATOR MODE

# TABLE 10-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set and the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

#### TABLE 10-6: INITIALIZATION CONDITION FOR REGISTERS

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | -       | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| INDF     | 00h     | -              | -                                                                                                                                                          | -                                                                                                                 |

| TMR0     | 01h     | XXXX XXXX      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | x000 0000      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | นนนน นนนน                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| EEINTF   | 90h     | 111            | 111                                                                                                                                                        | 111                                                                                                               |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 10-5 for reset value for specific condition.

5: If wake-up was due to comparator input changing , then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

6: If reset was due to brown-out, then PCON bit 0 = 0. All other resets will cause bit 0 = u.

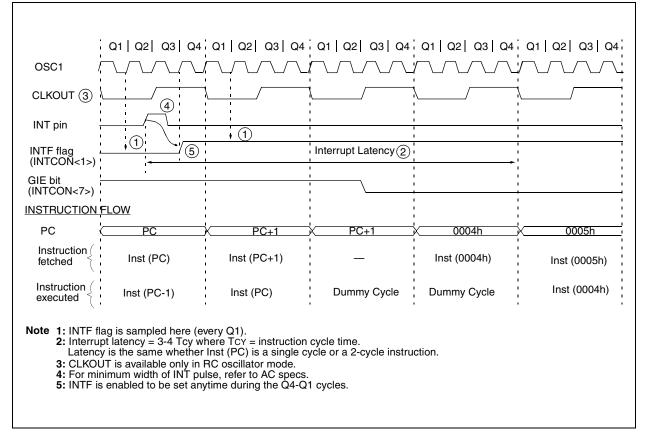

#### 10.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered; either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before re-enabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.8 for details on SLEEP and Figure 10-19 for timing of wake-up from SLEEP through RB0/INT interrupt.

#### 10.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 7.0.

#### 10.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

Note: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

#### 10.5.4 COMPARATOR INTERRUPT

See Section 8.6 for complete description of comparator interrupts.

#### FIGURE 10-16: INT PIN INTERRUPT TIMING

# TABLE 11-2: PIC16CE62X INSTRUCTION SET

| Mnemonic,  |         | Description                  |       | 14-Bit Opcode |      |      |      | Status   | Notes |  |

|------------|---------|------------------------------|-------|---------------|------|------|------|----------|-------|--|

| Operands   |         |                              |       | MSb           |      | LSb  |      | Affected |       |  |

| BYTE-ORIE  | NTED    | FILE REGISTER OPERATIONS     |       |               |      |      |      |          |       |  |

| ADDWF      | f, d    | Add W and f                  | 1     | 00            | 0111 | dfff | ffff | C,DC,Z   | 1,2   |  |

| ANDWF      | f, d    | AND W with f                 | 1     | 00            | 0101 | dfff | ffff | Z        | 1,2   |  |

| CLRF       | f       | Clear f                      | 1     | 00            | 0001 | lfff | ffff | Z        | 2     |  |

| CLRW       | -       | Clear W                      | 1     | 00            | 0001 | 0000 | 0011 | Z        |       |  |

| COMF       | f, d    | Complement f                 | 1     | 00            | 1001 | dfff | ffff | Z        | 1,2   |  |

| DECF       | f, d    | Decrement f                  | 1     | 00            | 0011 | dfff | ffff | Z        | 1,2   |  |

| DECFSZ     | f, d    | Decrement f, Skip if 0       | 1(2)  | 00            | 1011 | dfff | ffff |          | 1,2,  |  |

| INCF       | f, d    | Increment f                  | 1     | 00            | 1010 | dfff | ffff | Z        | 1,2   |  |

| INCFSZ     | f, d    | Increment f, Skip if 0       | 1(2)  | 00            | 1111 | dfff | ffff |          | 1,2,  |  |

| IORWF      | f, d    | Inclusive OR W with f        | 1     | 00            | 0100 | dfff | ffff | Z        | 1,2   |  |

| MOVF       | f, d    | Move f                       | 1     | 00            | 1000 | dfff | ffff | Z        | 1,2   |  |

| MOVWF      | f       | Move W to f                  | 1     | 00            | 0000 | lfff | ffff |          |       |  |

| NOP        | -       | No Operation                 | 1     | 00            | 0000 | 0xx0 | 0000 |          |       |  |

| RLF        | f, d    | Rotate Left f through Carry  | 1     | 00            | 1101 | dfff | ffff | С        | 1,2   |  |

| RRF        | f, d    | Rotate Right f through Carry | 1     | 00            | 1100 | dfff | ffff | С        | 1,2   |  |

| SUBWF      | f, d    | Subtract W from f            | 1     | 00            | 0010 | dfff | ffff | C,DC,Z   | 1,2   |  |

| SWAPF      | f, d    | Swap nibbles in f            | 1     | 00            | 1110 | dfff | ffff |          | 1,2   |  |

| XORWF      | f, d    | Exclusive OR W with f        | 1     | 00            | 0110 | dfff | ffff | Z        | 1,2   |  |

| BIT-ORIENT | FED FIL | E REGISTER OPERATIONS        |       |               |      |      |      | •        |       |  |

| BCF        | f, b    | Bit Clear f                  | 1     | 01            | 00bb | bfff | ffff |          | 1,2   |  |

| BSF        | f, b    | Bit Set f                    | 1     | 01            | 01bb | bfff | ffff |          | 1,2   |  |

| BTFSC      | f, b    | Bit Test f, Skip if Clear    | 1 (2) | 01            | 10bb | bfff | ffff |          | 3     |  |

| BTFSS      | f, b    | Bit Test f, Skip if Set      | 1 (2) | 01            | 11bb | bfff | ffff |          | 3     |  |

| LITERAL A  | ND CO   | NTROL OPERATIONS             |       |               |      |      |      |          |       |  |

| ADDLW      | k       | Add literal and W            | 1     | 11            | 111x | kkkk | kkkk | C,DC,Z   |       |  |

| ANDLW      | k       | AND literal with W           | 1     | 11            | 1001 | kkkk | kkkk | Z        |       |  |

| CALL       | k       | Call subroutine              | 2     | 10            | 0kkk | kkkk | kkkk |          |       |  |

| CLRWDT     | -       | Clear Watchdog Timer         | 1     | 00            | 0000 | 0110 | 0100 | TO,PD    |       |  |

| GOTO       | k       | Go to address                | 2     | 10            | 1kkk | kkkk | kkkk |          |       |  |

| IORLW      | k       | Inclusive OR literal with W  | 1     | 11            | 1000 | kkkk | kkkk | Z        |       |  |

| MOVLW      | k       | Move literal to W            | 1     | 11            | 00xx | kkkk | kkkk |          |       |  |

| RETFIE     | -       | Return from interrupt        | 2     | 00            | 0000 | 0000 | 1001 |          |       |  |

| RETLW      | k       | Return with literal in W     | 2     | 11            | 01xx | kkkk | kkkk |          |       |  |

| RETURN     | -       | Return from Subroutine       | 2     | 00            | 0000 | 0000 | 1000 |          |       |  |

|            | -       | Go into standby mode         | 1     | 00            | 0000 | 0110 | 0011 | TO,PD    |       |  |

| SLEEP      |         |                              |       | 1             |      |      |      |          | 1     |  |

| SUBLW      | k       | Subtract W from literal      | 1     | 11            | 110x | kkkk | kkkk | C,DC,Z   |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                          | PIC120 | PIC14 | PIC160 | 91019 | PIC160 | PIC16F | PIC16 | PIC16C | PIC160 | PIC16F | PIC16C | DTFOIG | 22121919 | PIC18C) | 83CX<br>52CX | кхээн | мсвгх | WCP25 |

|----------------------------------------------------------|--------|-------|--------|-------|--------|--------|-------|--------|--------|--------|--------|--------|----------|---------|--------------|-------|-------|-------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment | >      | >     | >      | >     | >      | >      | >     | >      | >      | >      | >      | >      | >        | >       |              |       |       |       |

|                                                          |        |       |        |       |        |        |       |        |        |        |        | >      | >        |         |              |       |       |       |

| MPLAB <sup>®</sup> C18 Compiler                          |        |       |        |       |        |        |       |        |        |        |        |        |          | >       |              |       |       |       |

| B MPASM/MPLINK                                           | >      | >     | >      | >     | >      | >      | >     | >      | >      | >      | >      | >      | >        | >       | >            | >     |       |       |

| 2 MPLAB <sup>®</sup> -ICE                                | >      | >     | >      | >     | >      | **`    | >     | >      | >      | >      | >      | >      | >        | >       |              |       |       |       |

| PICMASTER/PICMASTER-CE                                   | >      | >     | ~      | >     | >      |        | >     | >      | ~      |        | >      | ~      | ~        |         |              |       |       |       |

| E ICEPIC™ Low-Cost<br>III In-Circuit Emulator            | `      |       | >      | >     | >      |        | >     | >      | >      |        | ~      |        |          |         |              |       |       |       |

| MPLAB <sup>®</sup> -ICD In-Circuit<br>Debugger<br>De     |        |       |        | *>    |        |        | *>    |        |        | >      |        |        |          |         |              |       |       |       |

| 20 PICSTART®Plus<br>E Low-Cost Universal Dev. Kit        | ~      | >     | >      | `     | `      | ×**    | `     | `      | `      | >      | >      | ~      | `        | `       |              |       |       |       |

| ଅଟେ PRO MATE® I<br>Universal Programmer<br>ଦ             | >      | >     | >      | >     | >      | **/    | >     | >      | >      | >      | >      | ~      | ~        | ~       | >            | >     |       |       |

| SIMICE                                                   | >      |       | >      |       |        |        |       |        |        |        |        |        |          |         |              |       |       |       |

| PICDEM-1                                                 |        |       | ~      |       | >      |        | <↓    |        | ~      |        |        | ~      |          |         |              |       |       |       |

| PICDEM-2                                                 |        |       |        | à     |        |        | ∕†    |        |        |        |        |        |          | ~       |              |       |       |       |

| 2 PICDEM-3                                               |        |       |        |       |        |        |       |        |        |        | ~      |        |          |         |              |       |       |       |

| PICDEM-14A                                               |        | >     |        |       |        |        |       |        |        |        |        |        |          |         |              |       |       |       |

| PICDEM-17                                                |        |       |        |       |        |        |       |        |        |        |        |        | ~        |         |              |       |       |       |

| E KEELoo® Evaluation Kit                                 |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              | >     |       |       |

| KEELOQ Transponder Kit                                   |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              | >     |       |       |

| microlD™ Programmer's Kit                                |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       | ~     |       |

| 125 kHz microID Developer's Kit                          |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       | >     |       |

| 25 kHz Anticollision microlD<br>Developer's Kit          |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       | >     |       |

| 13.56 MHz Anticollision microID<br>Developer's Kit       |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       | >     |       |

| MCP2510 CAN Developer's Kit                              |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       |       | >     |

ğ Contact Microcrip reciniology inc. for availability <sup>†</sup> Development tool is available on select devices.

# 13.1 DC CHARACTERISTICS:

# PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended)

| DC CH        | ARACTER            | ISTICS                                                              |        | n <b>d Ope</b> |           | e          | tions (unless otherwise stated) $-40^{\circ}C$ $\leq Ta \leq +85^{\circ}C$ for industrial and $0^{\circ}C$ $\leq Ta \leq +70^{\circ}C$ for commercial and $-40^{\circ}C$ $\leq Ta \leq +125^{\circ}C$ for extended |

|--------------|--------------------|---------------------------------------------------------------------|--------|----------------|-----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym                | Characteristic                                                      | Min    | Тур†           | Max       | Units      | Conditions                                                                                                                                                                                                         |

| D001         | Vdd                | Supply Voltage                                                      | 3.0    | -              | 5.5       | V          | See Figure 13-1 through Figure 13-3                                                                                                                                                                                |

| D002         | Vdr                | RAM Data Retention<br>Voltage (Note 1)                              | -      | 1.5*           | -         | V          | Device in SLEEP mode                                                                                                                                                                                               |

| D003         | VPOR               | VDD start voltage to<br>ensure Power-on Reset                       | -      | Vss            | -         | V          | See section on power-on reset for details                                                                                                                                                                          |

| D004         | SVDD               | VDD rise rate to ensure<br>Power-on Reset                           | 0.05*  | -              | -         | V/ms       | See section on power-on reset for details                                                                                                                                                                          |

| D005         | VBOR               | Brown-out Detect Voltage                                            | 3.7    | 4.0            | 4.35      | V          | BOREN configuration bit is cleared                                                                                                                                                                                 |

| D010         | IDD                | Supply Current (Note 2, 4)                                          | -      | 1.2            | 2.0       | mA         | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)*                                                                                                                                                  |

|              |                    |                                                                     | -      | 0.4            | 1.2       | mA         | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT osc mode, (Note 4)                                                                                                                                                   |

|              |                    |                                                                     | -      | 1.0            | 2.0       | mA         | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS osc mode, (Note 6)                                                                                                                                                  |

|              |                    |                                                                     | -      | 4.0            | 6.0       | mA         | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS osc mode                                                                                                                                                            |

|              |                    |                                                                     | -      | 4.0            | 7.0       | mA         | FOSC = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS osc mode                                                                                                                                                           |

|              |                    |                                                                     | -      | 35             | 70        | μA         | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP osc mode                                                                                                                                                            |

| D020         | IPD                | Power Down Current (Note 3)                                         | -      | -              | 2.2       | μA         | VDD = 3.0V                                                                                                                                                                                                         |

|              |                    |                                                                     | -      | -              | 5.0       | μA         | $VDD = 4.5V^*$                                                                                                                                                                                                     |

|              |                    |                                                                     | _      | -              | 9.0<br>15 | μΑ<br>μΑ   | VDD = 5.5V<br>VDD = 5.5V Extended                                                                                                                                                                                  |

| D022         | ΔIWDT              | WDT Current (Note 5)                                                | -      | 6.0            | 10        | μA         | VDD = 4.0V                                                                                                                                                                                                         |

|              |                    |                                                                     |        |                | 12        | μΑ         | (125°C)                                                                                                                                                                                                            |

| D022A        | $\Delta$ IBOR      | Brown-out Reset Current (Note 5)                                    | -      | 75             | 125       | μA         | $\overline{\text{BOD}}$ enabled, VDD = 5.0V                                                                                                                                                                        |

| D023         | ∆ICOMP             | Comparator Current for each<br>Comparator (Note 5)                  | -      | 30             | 60        | μA         | VDD = 4.0V                                                                                                                                                                                                         |

| D023A        | $\Delta$ IVREF     | VREF Current (Note 5)                                               | -      | 80             | 135       | μA         | VDD = 4.0V                                                                                                                                                                                                         |

|              | $\Delta IEE$ Write | Operating Current                                                   | -      |                | 3         | mA         | Vcc = 5.5V, SCL = 400 kHz                                                                                                                                                                                          |

|              | ∆IEE Read          | Operating Current                                                   | -      |                | 1         | mA         |                                                                                                                                                                                                                    |

|              | ΔIEE               | Standby Current                                                     | -      |                | 30        | μA         | $V_{CC} = 3.0V, EE V_{DD} = V_{CC}$                                                                                                                                                                                |

| 4.4          | ΔIEE               | Standby Current                                                     | -      |                | 100       | μΑ         | Vcc = 3.0V, EE VDD = Vcc                                                                                                                                                                                           |

| 1A           | Fosc               | LP Oscillator Operating Frequency                                   | 0      | -              | 200       | kHz        | All temperatures                                                                                                                                                                                                   |

|              |                    | RC Oscillator Operating Frequency XT Oscillator Operating Frequency | 0<br>0 | _              | 4         | MHz<br>MHz | All temperatures<br>All temperatures                                                                                                                                                                               |

|              |                    | HS Oscillator Operating Frequency                                   | 0      |                | 4<br>20   | MHz        | All temperatures                                                                                                                                                                                                   |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**6:** Commercial temperature range only.

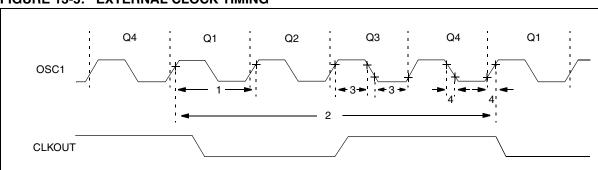

# 13.5 <u>Timing Diagrams and Specifications</u>

# FIGURE 13-5: EXTERNAL CLOCK TIMING

# TABLE 13-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min  | Тур† | Max    | Units | Conditions                         |

|------------------|-------|----------------------------------|------|------|--------|-------|------------------------------------|

| 1A               | Fosc  | External CLKIN Frequency         | DC   | —    | 4      | MHz   | XT and RC osc mode, VDD=5.0V       |

|                  |       | (Note 1)                         | DC   | —    | 20     | MHz   | HS osc mode                        |

|                  |       |                                  | DC   | —    | 200    | kHz   | LP osc mode                        |

|                  |       | Oscillator Frequency             | DC   | —    | 4      | MHz   | RC osc mode, VDD=5.0V              |

|                  |       | (Note 1)                         | 0.1  | —    | 4      | MHz   | XT osc mode                        |

|                  |       |                                  | 1    | —    | 20     | MHz   | HS osc mode                        |

|                  |       |                                  | DC   | -    | 200    | kHz   | LP osc mode                        |

| 1                | Tosc  | External CLKIN Period            | 250  | —    | _      | ns    | XT and RC osc mode                 |

|                  |       | (Note 1)                         | 50   | —    | —      | ns    | HS osc mode                        |

|                  |       |                                  | 5    | —    | —      | μs    | LP osc mode                        |

|                  |       | Oscillator Period                | 250  | —    | _      | ns    | RC osc mode                        |

|                  |       | (Note 1)                         | 250  | —    | 10,000 | ns    | XT osc mode                        |

|                  |       |                                  | 50   | —    | 1,000  | ns    | HS osc mode                        |

|                  |       |                                  | 5    | —    | —      | μS    | LP osc mode                        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200  | —    | DC     | ns    | Tcy=Fosc/4                         |

| 3*               | TosL, | External Clock in (OSC1) High or | 100* | —    | —      | ns    | XT oscillator, Tosc L/H duty cycle |

|                  | TosH  | Low Time                         | 2*   | —    | —      | μs    | LP oscillator, Tosc L/H duty cycle |

|                  |       |                                  | 20*  |      | —      | ns    | HS oscillator, Tosc L/H duty cycle |

| 4*               | TosR, | External Clock in (OSC1) Rise or | 25*  | —    | —      | ns    | XT oscillator                      |

|                  | TosF  | Fall Time                        | 50*  | —    | —      | ns    | LP oscillator                      |

|                  |       |                                  | 15*  | —    | —      | ns    | HS oscillator                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

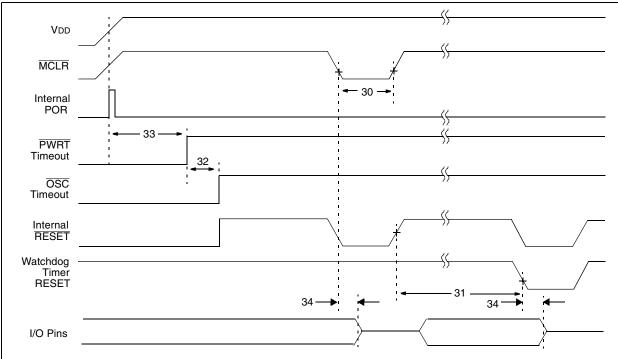

#### FIGURE 13-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

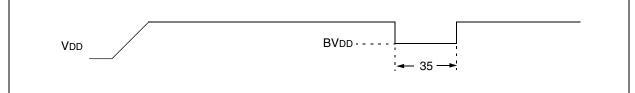

#### FIGURE 13-8: BROWN-OUT RESET TIMING

#### **TABLE 13-5:** RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS