Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

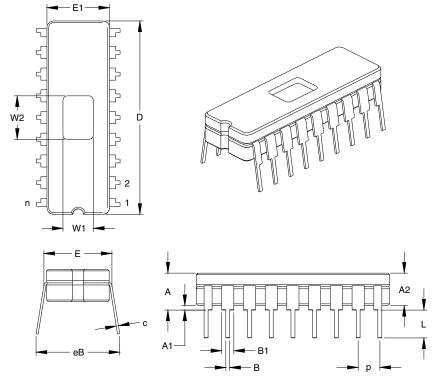

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce623-20i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CE62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CE62X uses a Harvard architecture in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM) and non-volatile memory (EEPROM) for each PIC16CE62X device.

| Device     | Program<br>Memory | RAM<br>Data<br>Memory | EEPROM<br>Data<br>Memory |

|------------|-------------------|-----------------------|--------------------------|

| PIC16CE623 | 512x14            | 96x8                  | 128x8                    |

| PIC16CE624 | 1Kx14             | 96x8                  | 128x8                    |

| PIC16CE625 | 2Kx14             | 128x8                 | 128x8                    |

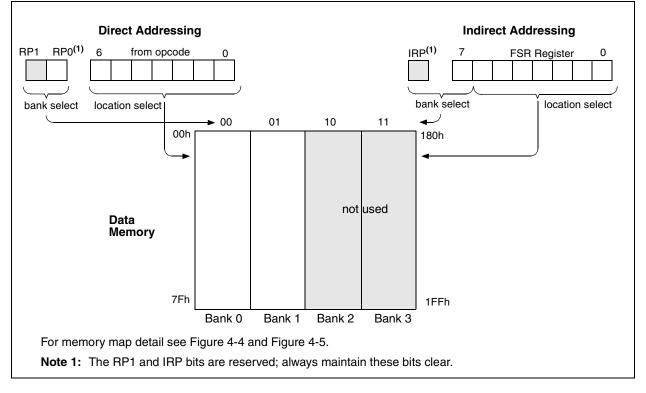

The PIC16CE62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CE62X family has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CE62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16CE62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

# 4.0 MEMORY ORGANIZATION

### 4.1 <u>Program Memory Organization</u>

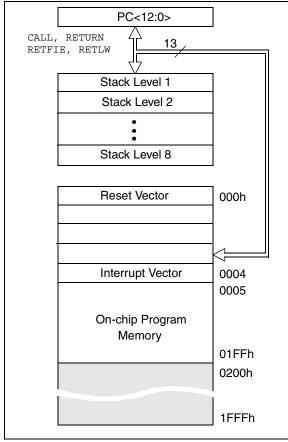

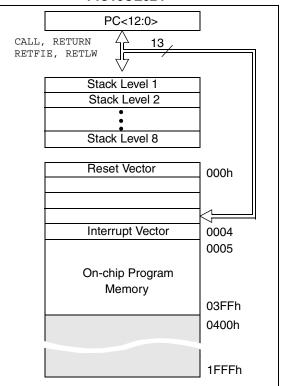

The PIC16CE62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16CE623, 1K x 14 (0000h - 03FFh) for the PIC16CE624 and 2K x 14 (0000h - 07FFh) for the PIC16CE625 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16CE623) or 1K x 14 space (PIC16CE624) or 2K x 14 space (PIC16CE625). The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE623

### FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE624

### FIGURE 4-3: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE625

### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16CE62X. A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

| EXAMPL    | E 4-1: | INDIRECT ADDRESSING |                      |  |  |  |

|-----------|--------|---------------------|----------------------|--|--|--|

|           | movlw  | 0x20                | ;initialize pointer  |  |  |  |

|           | movwf  | FSR                 | ;to RAM              |  |  |  |

| NEXT      | clrf   | INDF                | ;clear INDF register |  |  |  |

|           | incf   | FSR                 | ;inc pointer         |  |  |  |

|           | btfss  | FSR,4               | ;all done?           |  |  |  |

|           | goto   | NEXT                | ;no clear next       |  |  |  |

|           |        |                     | ;yes continue        |  |  |  |

| CONTINUE: |        |                     |                      |  |  |  |

### FIGURE 4-7: DIRECT/INDIRECT ADDRESSING PIC16CE62X

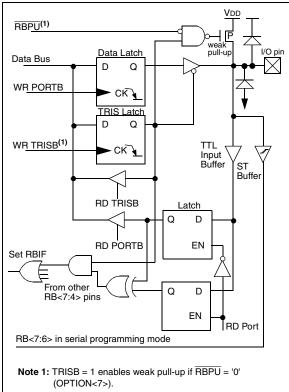

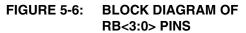

### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a high impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{RBPU}$  (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins of RB<7:4> are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes".)

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data pin.  |

TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

**Note 2:** This buffer is a Schmitt Trigger input when used in serial programming mode.

### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx xxxx        | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111        | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111        | 1111 1111                       |

Legend: u = unchanged, x = unknown

**Note:** Shaded bits are not used by PORTB.

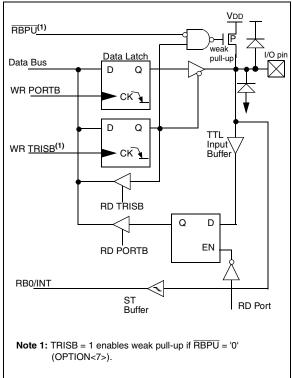

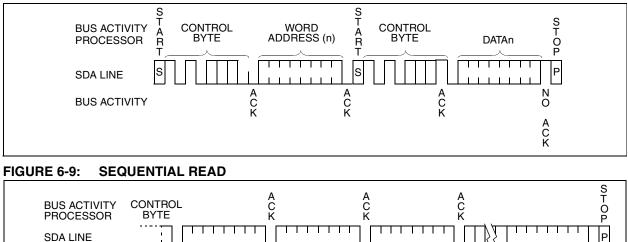

### FIGURE 6-8: RANDOM READ

BUS ACTIVITY

. .

A C K

DATAn

DATAn + 1

DATAn + 2

N O

A C K

DATAn + X

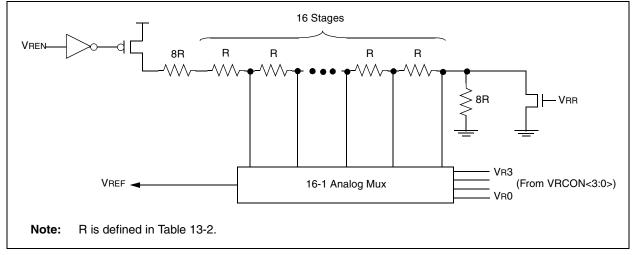

## 9.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 9-1. The block diagram is given in Figure 9-1.

### 9.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1: VREF = (VR<3:0>/24) x VDD

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 13-1). Example 9-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

| R/W-0                                                                                               | R/W-0    | R/W-0      | U-0      | R/W-0         | R/W-0 | R/W-0     | R/W-0 |                                                                                       |

|-----------------------------------------------------------------------------------------------------|----------|------------|----------|---------------|-------|-----------|-------|---------------------------------------------------------------------------------------|

| VREN                                                                                                | VROE     | Vrr        | _        | Vr3           | VR2   | VR1       | VR0   | R = Readable bit                                                                      |

| bit7                                                                                                | •        |            | •        |               |       |           | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7: VREF Enable<br>1 = VREF circuit powered on<br>0 = VREF circuit powered down, no IDD drain    |          |            |          |               |       |           |       |                                                                                       |

| bit 6: VREF Output Enable<br>1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |          |            |          |               |       |           |       |                                                                                       |

| bit 5: VREF Range selection<br>1 = Low Range<br>0 = High Range                                      |          |            |          |               |       |           |       |                                                                                       |

| bit 4:                                                                                              | Unimplem | ented: Re  | ad as '0 | <sup>ji</sup> |       |           |       |                                                                                       |

| bit 3-0:                                                                                            |          | VRR = 1: V | ref = (\ | /R<3:0>/ 2    | -     | 32) * Vdd |       |                                                                                       |

## REGISTER 9-1: VRCON REGISTER (ADDRESS 9Fh)

FIGURE 9-1: VOLTAGE REFERENCE BLOCK DIAGRAM

### 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CE62X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

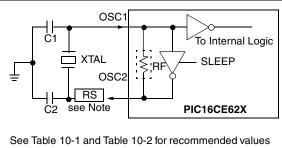

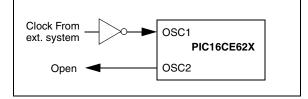

# 10.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 10-1). The PIC16CE62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 10-2).

### FIGURE 10-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

See Table 10-1 and Table 10-2 for recommended values of C1 and C2.

Note: A series resistor may be required for AT strip cut crystals.

### FIGURE 10-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

### TABLE 10-1: CERAMIC RESONATORS, PIC16CE62X

**Ranges Tested:** OSC2 Mode Freq OSC1 XT 455 kHz 68 - 100 pF 68 - 100 pF 15 - 68 pF 15 - 68 pF 2.0 MHz 4.0 MHz 15 - 68 pF 15 - 68 pF HS 10 - 68 pF 10 - 68 pF 8.0 MHz 16.0 MHz 10 - 22 pF 10 - 22 pF

These values are for design guidance only. See notes at bottom of page.

#### TABLE 10-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR, PIC16CE62X

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| XT       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

These values are for design guidance only. See notes at bottom of page.

- 1. Recommended values of C1 and C2 are identical to the ranges tested table.

- 2. Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- 3. Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

© 1998-2013 Microchip Technology Inc.

### 10.3 <u>Reset</u>

The PIC16CE62X differentiates between various kinds of reset:

- a) Power-on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOD)

Some registers are not affected in any reset condition. Their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on reset, MCLR reset, WDT reset and MCLR reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different reset situations as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

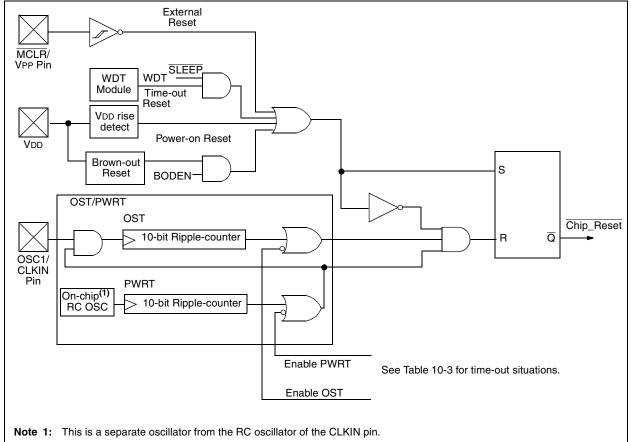

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-6.

The  $\overline{\text{MCLR}}$  reset path has a noise filter to detect and ignore small pulses. See Table 13-5 for pulse width specification.

### FIGURE 10-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                                   |                                               |                     |       |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------|-------|--|--|--|

| Syntax:          | [ <i>label</i> ] B                                                                                                                                                                                                                                                        | [ label ] BTFSS f,b                           |                     |       |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                                                                          |                                               |                     |       |  |  |  |

| Operation:       | skip if (f<                                                                                                                                                                                                                                                               | b>) = 1                                       |                     |       |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                      |                                               |                     |       |  |  |  |

| Encoding:        | 01                                                                                                                                                                                                                                                                        | 11bb                                          | bfff                | ffff  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1' then the next<br>instruction is skipped.<br>If bit 'b' is '1', then the next instruction<br>fetched during the current instruction<br>execution, is discarded and a NOP is<br>executed instead, making this a<br>two-cycle instruction. |                                               |                     |       |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                         |                                               |                     |       |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                      |                                               |                     |       |  |  |  |

| Example          | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                                     |                                               | FLAG, 1<br>PROCESS_ | _CODE |  |  |  |

|                  | Before In                                                                                                                                                                                                                                                                 | struction                                     |                     |       |  |  |  |

|                  | After Inst                                                                                                                                                                                                                                                                | ruction<br>if FLAG<1><br>PC = a<br>if FLAG<1> | = 0,<br>address F.  |       |  |  |  |

| CLRF             | Clear f                                                               |                    |             |           |  |

|------------------|-----------------------------------------------------------------------|--------------------|-------------|-----------|--|

| Syntax:          | [label] (                                                             | CLRF f             |             |           |  |

| Operands:        | $0 \le f \le 12$                                                      | 27                 |             |           |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                    |             |           |  |

| Status Affected: | Z                                                                     |                    |             |           |  |

| Encoding:        | 0 0                                                                   | 0001               | lfff        | ffff      |  |

| Description:     | The conte and the Z                                                   | 0                  | ster 'f' ar | e cleared |  |

| Words:           | 1                                                                     |                    |             |           |  |

| Cycles:          | 1                                                                     |                    |             |           |  |

| Example          | CLRF                                                                  | FLAC               | G_REG       |           |  |

|                  | Before In                                                             | struction          |             |           |  |

|                  | FLAG_REG = 0x5A                                                       |                    |             |           |  |

|                  | After Inst                                                            | ruction<br>Flag Re | EG =        | 0x00      |  |

|                  |                                                                       | Z                  | =           | 1         |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |  |  |  |  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                              |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                          |  |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                             |  |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle instruc-<br>tion. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                             |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                             |  |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                                               |  |  |  |  |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                    |  |  |  |  |

| Clear W                                                               |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| [label] CLRW                                                          |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |

| None                                                                  |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |

| $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |

| Z                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |

| 00                                                                    | 0001                                                                                                          | 0000                                                                                                                                                             | 0011                                                                                                                                                                                          |  |  |  |

| W register set.                                                       | is cleare                                                                                                     | d. Zero bit                                                                                                                                                      | (Z) is                                                                                                                                                                                        |  |  |  |

| 1                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |

| 1                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |

| CLRW                                                                  |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |  |  |

| Before In                                                             | structior                                                                                                     | l                                                                                                                                                                |                                                                                                                                                                                               |  |  |  |

| After Inst                                                            | ruction<br>W =                                                                                                | 0x5A<br>0x00<br>1                                                                                                                                                |                                                                                                                                                                                               |  |  |  |

|                                                                       | $[label]$ None $00h \rightarrow (V \\ 1 \rightarrow Z$ $Z$ $00$ W register set. 1 $CLRW$ Before In After Inst | $[label] CLRW$ None $00h \rightarrow (W)$ $1 \rightarrow Z$ $Z$ $00 0001$ W register is cleared set. $1$ $CLRW$ Before Instruction $W =$ After Instruction $W =$ | $[label] CLRW$ None $00h \rightarrow (W)$ $1 \rightarrow Z$ Z $00  0001  0000$ W register is cleared. Zero bit set. $1$ $1$ $CLRW$ Before Instruction $W = 0x5A$ After Instruction $W = 0x00$ |  |  |  |

$\odot$  1998-2013 Microchip Technology Inc.

| GOTO                              | Unconditional Branch                                                                                                                                                                               | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [ <i>label</i> ] GOTO k                                                                                                                                                                            | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:                         | $0 \le k \le 2047$                                                                                                                                                                                 | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                              |

| Operation:                        | $k \rightarrow PC < 10:0 >$                                                                                                                                                                        |                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                      |

|                                   | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected:                  | None                                                                                                                                                                                               | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |

| Encoding:                         | 10 1kkk kkkk kkkk                                                                                                                                                                                  | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                              |

| Description:<br>Words:<br>Cycles: | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.<br>1 | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. |

| Example                           | GOTO THERE                                                                                                                                                                                         | Words:           | 1                                                                                                                                                                                                                                                                                                                              |

|                                   | After Instruction<br>PC = Address THERE                                                                                                                                                            | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |

|                                   | FC = Addless There                                                                                                                                                                                 | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                    |                  | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                    |                  | •                                                                                                                                                                                                                                                                                                                              |

$\begin{array}{rcl} Before \ Instruction \\ PC & = & address \ HERE \\ After \ Instruction \\ CNT & = & CNT + 1 \\ if \ CNT = & 0, \\ PC & = & address \ CONTINUE \\ if \ CNT \neq & 0, \\ PC & = & address \ HERE \ +1 \\ \end{array}$

| INCF             | Increment f                                                                                                                                                         |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                    |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                         |  |  |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                   |  |  |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                   |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                   |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                   |  |  |  |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                         |  |  |  |  |  |  |  |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                               |  |  |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                            |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                               |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                           |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                      |  |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                      |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                      |  |  |  |  |  |  |  |

| Example          | IORLW 0x35                                                                                                             |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                               |  |  |  |  |  |  |  |

| NOP              | No Operation |       |      |      |  |  |  |  |

|------------------|--------------|-------|------|------|--|--|--|--|

| Syntax:          | [ label ]    | NOP   |      |      |  |  |  |  |

| Operands:        | None         |       |      |      |  |  |  |  |

| Operation:       | No opera     | ition |      |      |  |  |  |  |

| Status Affected: | None         |       |      |      |  |  |  |  |

| Encoding:        | 0 0          | 0000  | 0xx0 | 0000 |  |  |  |  |

| Description:     | No operati   | ion.  |      |      |  |  |  |  |

| Words:           | 1            |       |      |      |  |  |  |  |

| Cycles:          | 1            |       |      |      |  |  |  |  |

| Example          | NOP          |       |      |      |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                             |           |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                    |           |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                              |           |  |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                                                                                                                                                                     |           |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                              |           |  |  |  |  |  |  |

| Encoding:        | 00 0000                                                                                                                                                                                                           | 0000 1001 |  |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a two-cycle<br>instruction. |           |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |           |  |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                 |           |  |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                            |           |  |  |  |  |  |  |

|                  | After Interrupt<br>PC =<br>GIE =                                                                                                                                                                                  | TOS<br>1  |  |  |  |  |  |  |

| OPTION                                       | Load Option Register                                                                                                                                                                                                                                       |  |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:                                      | [label] OPTION                                                                                                                                                                                                                                             |  |  |  |  |  |

| Operands:                                    | None                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Operation:                                   | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected:                             | None                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Encoding:                                    | 00 0000 0110 0010                                                                                                                                                                                                                                          |  |  |  |  |  |

| Description:<br>Words:<br>Cycles:<br>Example | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code<br>compatibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly<br>address it.<br>1<br>1 |  |  |  |  |  |

|                                              | To maintain upward compatibility<br>with future PIC <sup>®</sup> MCU products, do<br>not use this instruction.                                                                                                                                             |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                   |

| Example          | CALL TABLE ;W contains table<br>;offset value<br>;W now has table<br>value                                                                                                          |

| TABLE            | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |

|                  | RETLW kn ; End of table                                                                                                                                                             |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                      |

|                  | After Instruction<br>W = value of k8                                                                                                                                                |

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

### 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

### 13.3 DC CHARACTERISTICS:

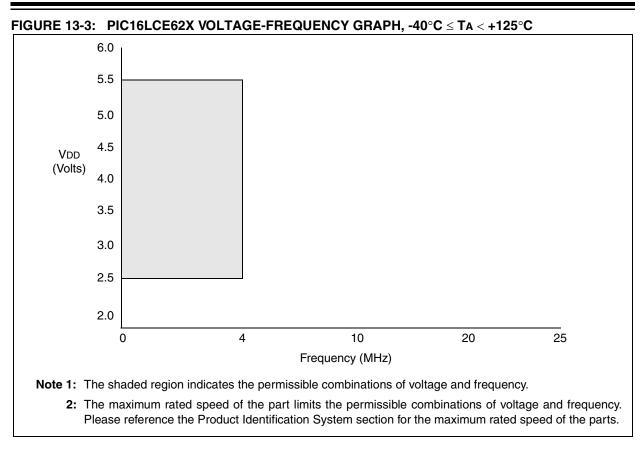

### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended) PIC16LCE62X (Commercial, Industrial)

|                    |       |                                                                 | Standard Opera                                                            | ating ( | Conditions (u | unles | s otherwise stated)                             |  |  |

|--------------------|-------|-----------------------------------------------------------------|---------------------------------------------------------------------------|---------|---------------|-------|-------------------------------------------------|--|--|

|                    |       |                                                                 |                                                                           |         |               |       | +85°C for industrial and                        |  |  |

| DC CHARACTERISTICS |       | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial and       |                                                                           |         |               |       |                                                 |  |  |

|                    |       |                                                                 | $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |         |               |       |                                                 |  |  |

|                    |       |                                                                 | Operating voltag                                                          | e Vdi   | o range as de | scrib | ed in DC spec Table 13-1                        |  |  |

| Parm               | Sym   | Characteristic                                                  | Min                                                                       | Typ†    | Max           | Unit  | Conditions                                      |  |  |

| No.                |       |                                                                 |                                                                           |         |               |       |                                                 |  |  |

|                    | Vi∟   | Input Low Voltage                                               |                                                                           |         |               |       |                                                 |  |  |

|                    |       | I/O ports                                                       |                                                                           |         |               |       |                                                 |  |  |

| D030               |       | with TTL buffer                                                 | Vss                                                                       | _       | 0.8V          | v     | VDD = 4.5V to 5.5V, Otherwise                   |  |  |

|                    |       |                                                                 |                                                                           |         | 0.15VDD       |       |                                                 |  |  |

| D031               |       | with Schmitt Trigger input                                      | Vss                                                                       |         | 0.2VDD        | V     |                                                 |  |  |

| D032               |       | MCLR, RA4/T0CKI,OSC1 (in RC                                     | Vss                                                                       | -       | 0.2VDD        | V     | Note1                                           |  |  |

|                    |       | mode)                                                           |                                                                           |         |               |       |                                                 |  |  |

| D033               |       | OSC1 (in XT and HS)                                             | Vss                                                                       | -       | 0.3Vdd        | V     |                                                 |  |  |

|                    |       | OSC1 (in LP)                                                    | Vss                                                                       | -       | 0.6VDD - 1.0  | V     |                                                 |  |  |

|                    | VIH   | Input High Voltage                                              |                                                                           |         |               |       |                                                 |  |  |

|                    |       | I/O ports                                                       |                                                                           |         |               |       |                                                 |  |  |

| D040               |       | with TTL buffer                                                 | 2.0V                                                                      | -       | VDD           | V     | VDD = 4.5V to 5.5V, Otherwise                   |  |  |

| <b>D</b> 044       |       |                                                                 | .25VDD + 0.8V                                                             |         | VDD           |       |                                                 |  |  |

| D041               |       | with Schmitt Trigger input                                      | 0.8VDD                                                                    |         | VDD           |       |                                                 |  |  |

| D042               |       | MCLR RA4/T0CKI                                                  | 0.8VDD                                                                    | -       | VDD           | V     |                                                 |  |  |

| D043<br>D043A      |       | OSC1 (XT, HS and LP)                                            | 0.7Vdd<br>0.9Vdd                                                          | -       | Vdd           | V     | Note1                                           |  |  |

| D043A              | IPURB | OSC1 (in RC mode)<br>PORTB weak pull-up current                 | 50                                                                        | 200     | 400           | μA    | VDD = 5.0V, VPIN = VSS                          |  |  |

| 0070               | IPUND | Input Leakage Current                                           | 50                                                                        | 200     | 400           | μΑ    | VDD = 5.0V, VPIN = V35                          |  |  |

|                    | lı∟   | (Notes 2, 3)                                                    |                                                                           |         |               |       |                                                 |  |  |

|                    |       | I/O ports (Except PORTA)                                        |                                                                           |         | ±1.0          | μА    | VSS $\leq$ VPIN $\leq$ VDD, pin at hi-impedance |  |  |

| D060               |       | PORTA                                                           | _                                                                         | _       | ±0.5          | μA    |                                                 |  |  |

| D061               |       | RA4/T0CKI                                                       | _                                                                         | _       | ±1.0          | μA    |                                                 |  |  |

| D063               |       | OSC1, MCLR                                                      | _                                                                         | _       | ±5.0          | μA    |                                                 |  |  |

|                    |       |                                                                 |                                                                           |         |               | · ·   | configuration                                   |  |  |

|                    | Vol   | Output Low Voltage                                              |                                                                           |         |               |       |                                                 |  |  |

| D080               |       | I/O ports                                                       | _                                                                         | _       | 0.6           | v     | IOL=8.5 mA, VDD=4.5V, -40° to +85°C             |  |  |

|                    |       | -                                                               | _                                                                         | _       | 0.6           | v     | IOL=7.0 mA, VDD=4.5V, +125°C                    |  |  |

| D083               |       | OSC2/CLKOUT (RC only)                                           | _                                                                         | _       | 0.6           | v     | IOL=1.6 mA, VDD=4.5V, -40° to +85°C             |  |  |

|                    |       |                                                                 | -                                                                         | -       | 0.6           | V     | IOL=1.2 mA, VDD=4.5V, +125°C                    |  |  |

|                    | Voh   | Output High Voltage (Note 3)                                    |                                                                           | 1       |               | 1     |                                                 |  |  |

| D090               |       | I/O ports (Except RA4)                                          | VDD-0.7                                                                   | -       | _             | v     | IOH=-3.0 mA, VDD=4.5V, -40° to +85°C            |  |  |

|                    |       |                                                                 | VDD-0.7                                                                   | -       | -             | v     | IOH=-2.5 mA, VDD=4.5V, +125°С                   |  |  |

| D092               |       | OSC2/CLKOUT (RC only)                                           | VDD-0.7                                                                   | -       | -             | v     | IOH=-1.3 mA, VDD=4.5V, -40° to +85°C            |  |  |

|                    |       |                                                                 | VDD-0.7                                                                   | -       | -             | v     | IOH=-1.0 mA, VDD=4.5V, +125°С                   |  |  |

| *D150              | Vod   | Open-Drain High Voltage                                         |                                                                           |         | 8.5           | V     | RA4 pin                                         |  |  |

|                    |       | Capacitive Loading Specs on                                     |                                                                           |         |               |       |                                                 |  |  |

|                    |       | Output Pins                                                     |                                                                           |         |               |       |                                                 |  |  |

| D100               |       | OSC2 pin                                                        |                                                                           |         | 15            | pF    | In XT, HS and LP modes when external            |  |  |

|                    | 2     |                                                                 |                                                                           |         |               |       | clock used to drive OSC1.                       |  |  |

| D101               | Cio   | All I/O pins/OSC2 (in RC mode)<br>These parameters are characte |                                                                           |         | 50            | pF    |                                                 |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16CE62X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

### 13.5 Timing Diagrams and Specifications

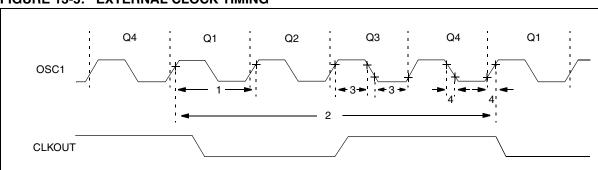

# FIGURE 13-5: EXTERNAL CLOCK TIMING

## TABLE 13-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min  | Тур† | Max    | Units | Conditions                         |

|------------------|-------|----------------------------------|------|------|--------|-------|------------------------------------|

| 1A               | Fosc  | External CLKIN Frequency         | DC   | _    | 4      | MHz   | XT and RC osc mode, VDD=5.0V       |

|                  |       | (Note 1)                         | DC   | —    | 20     | MHz   | HS osc mode                        |

|                  |       |                                  | DC   | —    | 200    | kHz   | LP osc mode                        |

|                  |       | Oscillator Frequency             | DC   | —    | 4      | MHz   | RC osc mode, VDD=5.0V              |