Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 30MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 896B (512 x 14)                                                           |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 96 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce623-30-p |

# 2.0 PIC16CE62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in the PIC16CE62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in the CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART® and PRO MATE® programmers both support programming of the PIC16CE62X.

# 2.2 <u>One-Time-Programmable (OTP)</u> Devices

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

# 2.3 Quick-Turn-Programming (QTP) Devices

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

### 2.4 <u>Serialized Quick-Turn-Programming</u> (<u>SQTP</u><sup>SM</sup>) <u>Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CE62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CE62X uses a Harvard architecture in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM) and non-volatile memory (EEPROM) for each PIC16CE62X device.

| Device     | Program<br>Memory | RAM<br>Data<br>Memory | EEPROM<br>Data<br>Memory |

|------------|-------------------|-----------------------|--------------------------|

| PIC16CE623 | 512x14            | 96x8                  | 128x8                    |

| PIC16CE624 | 1Kx14             | 96x8                  | 128x8                    |

| PIC16CE625 | 2Kx14             | 128x8                 | 128x8                    |

The PIC16CE62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CE62X family has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CE62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16CE62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

**TABLE 3-1:** PIC16CE62X PINOUT DESCRIPTION

| Name         | DIP/<br>SOIC<br>Pin # | SSOP<br>Pin # | I/O/P<br>Type | Buffer<br>Type        | Description                                                                                                                                                                                              |

|--------------|-----------------------|---------------|---------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                    | 18            | I             | ST/CMOS               | Oscillator crystal input/external clock source input.                                                                                                                                                    |

| OSC2/CLKOUT  | 15                    | 17            | 0             | _                     | Oscillator crystal output. Connects to crystal or resonator in crystal oscillator mode. In RC mode, OSC2 pin outputs CLKOUT which has 1/4 the frequency of OSC1, and denotes the instruction cycle rate. |

| MCLR/VPP     | 4                     | 4             | I/P           | ST                    | Master clear (reset) input/programming voltage input. This pin is an active low reset to the device.                                                                                                     |

|              |                       |               |               |                       | PORTA is a bi-directional I/O port.                                                                                                                                                                      |

| RA0/AN0      | 17                    | 19            | I/O           | ST                    | Analog comparator input                                                                                                                                                                                  |

| RA1/AN1      | 18                    | 20            | I/O           | ST                    | Analog comparator input                                                                                                                                                                                  |

| RA2/AN2/VREF | 1                     | 1             | I/O           | ST                    | Analog comparator input or VREF output                                                                                                                                                                   |

| RA3/AN3      | 2                     | 2             | I/O           | ST                    | Analog comparator input /output                                                                                                                                                                          |

| RA4/T0CKI    | 3                     | 3             | I/O           | ST                    | Can be selected to be the clock input to the Timer0 timer/counter or a comparator output. Output is open drain type.                                                                                     |

|              |                       |               |               |                       | PORTB is a bi-directional I/O port. PORTB can be software programmed for internal weak pull-up on all inputs.                                                                                            |

| RB0/INT      | 6                     | 7             | I/O           | TTL/ST <sup>(1)</sup> | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                               |

| RB1          | 7                     | 8             | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB2          | 8                     | 9             | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB3          | 9                     | 10            | I/O           | TTL                   |                                                                                                                                                                                                          |

| RB4          | 10                    | 11            | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB5          | 11                    | 12            | I/O           | TTL                   | Interrupt on change pin.                                                                                                                                                                                 |

| RB6          | 12                    | 13            | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming clock.                                                                                                                                                       |

| RB7          | 13                    | 14            | I/O           | TTL/ST <sup>(2)</sup> | Interrupt on change pin. Serial programming data.                                                                                                                                                        |

| Vss          | 5                     | 5,6           | Р             | _                     | Ground reference for logic and I/O pins.                                                                                                                                                                 |

| VDD          | 14                    | 15,16         | Р             | _                     | Positive supply for logic and I/O pins.                                                                                                                                                                  |

Legend:

O = output

I/O = input/output

P = power

— = Not used

I = Input

ST = Schmitt Trigger input

TTL = TTL input

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt. **Note 2:** This buffer is a Schmitt Trigger input when used in serial programming mode.

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bit for the comparator interrupt.

# REGISTER 4-4: PIE1 REGISTER (ADDRESS 8CH)

| U-0  | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0  |

|------|-------|-----|-----|-----|-----|-----|------|

| _    | CMIE  | _   | _   | _   | _   | _   | _    |

| bit7 |       |     |     |     |     |     | bit0 |

R = Readable bit

W = Writable bit

U = Unimplement

J = Unimplemented bit, read as '0'

-x = Unknown at POR reset

-n = Value at POR reset

bit 7: Unimplemented: Read as '0'

bit 6: CMIE: Comparator Interrupt Enable bit

1 = Enables the Comparator interrupt0 = Disables the Comparator interrupt

bit 5-0: Unimplemented: Read as '0'

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bit for the comparator interrupt.

Note: Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>). User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

### REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR reset -x = Unknown at POR reset

bit 7: Unimplemented: Read as '0'

bit 6: CMIF: Comparator Interrupt Flag bit

1 = Comparator input has changed

0 = Comparator input has not changed

bit 5-0: Unimplemented: Read as '0'

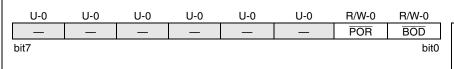

#### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset, an external MCLR reset, WDT reset or a Brown-out Reset.

Note: BOD is unknown on Power-on Reset. It must then be set by the user and checked on subsequent resets to see if BOD is cleared, indicating a brown-out has occurred. The BOD status bit is a "don't care" and is not necessarily predictable if the brown-out circuit is disabled (by programming BODEN bit in the configuration word).

## REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

R = Readable bit W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR reset -x = Unknown at POR reset

bit 7-2: Unimplemented: Read as '0'

bit 1: POR: Power-on Reset Status bit

1 = No Power-on Reset occurred

0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs)

bit 0: BOD: Brown-out Reset Status bit

1 = No Brown-out Reset occurred

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

# 6.0 EEPROM PERIPHERAL OPERATION

The PIC16CE623/624/625 each have 128 bytes of EEPROM data memory. The EEPROM data memory supports a bi-directional, 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), and are mapped to bit1 and bit2, respectively, of the EEINTF register (SFR 90h). In addition, the power to the EEPROM can be controlled using bit0 (EEVDD) of the EEINTF register. For most applications, all that is required is calls to the following functions:

```

; Byte Write: Byte write routine

Inputs: EEPROM Address

EEADDR

EEPROM Data

EEDATA

Outputs: Return 01 in W if OK, else

return 00 in W

; Read Current: Read EEPROM at address

currently held by EE device.

Inputs: NONE

Outputs:

EEPROM Data EEDATA

Return 01 in W if OK, else

return 00 in W

; Read Random: Read EEPROM byte at supplied

address

Inputs: EEPROM Address

EEADDR

Outputs:

EEPROM Data

EEDATA

Return 01 in W if OK,

else return 00 in W

```

The code for these functions is available on our web site (www.microchip.com). The code will be accessed by either including the source code FL62XINC.ASM or by linking FLASH62X.ASM. FLASH62.IMC provides external definition to the calling program.

#### 6.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the memory.

For normal data transfer, SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

#### 6.0.2 SERIAL CLOCK

This SCL input is used to synchronize the data transfer to and from the memory.

#### 6.0.3 EEINTF REGISTER

The EEINTF register (SFR 90h) controls the access to the EEPROM. Register 6-1 details the function of each bit. User code must generate the clock and data signals.

#### REGISTER 6-1: EEINTF REGISTER (ADDRESS 90h)

U-0 U-0 U-0 U-0 U-0 R/W-1 R/W-1 R/W-1 **EESCL EESDA** EEVDD = Readable bit W = Writable bit bit7 bit0 U = Unimplemented bit. read as '0' n = Value at POR reset bit 7-3: **Unimplemented:** Read as '0' **EESCL**: Clock line to the EEPROM bit 2: 1 = Clock high 0 = Clock low **EESDA**: Data line to EEPROM bit 1: 1 = Data line is high (pin is tri-stated, line is pulled high by a pull-up resistor) 0 = Data line is low **EEVDD**: VDD control bit for EEPROM bit 0: 1 = VDD is turned on to EEPROM 0 = VDD is turned off to EEPROM (all pins are tri-stated and the EEPROM is powered down) EESDA, EESCL and EEVDD will read '0' if EEVDD is turned off. Note:

TABLE 8-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Address | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|--------|-------|-------|-------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 1Fh     | CMCON  | C2OUT | C1OUT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000          | 00 0000                         |

| 9Fh     | VRCON  | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000        | 000- 0000                       |

| 0Bh     | INTCON | GIE   | PEIE  | TOIE  | INTE   | RBIE   | TOIF   | INTF   | RBIF   | 0000 000x        | 0000 000u                       |

| 0Ch     | PIR1   |       | CMIF  | _     | _      | _      |        | _      | _      | -0               | -0                              |

| 8Ch     | PIE1   |       | CMIE  | _     | _      | _      |        | _      | _      | -0               | -0                              |

| 85h     | TRISA  | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111           | 1 1111                          |

Legend: - = Unimplemented, read as "0", x = Unknown, u = unchanged

# 10.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16CE62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

#### These are:

- 1. OSC selection

- 2. Reset

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-Up Timer (OST) Brown-out Reset (BOD)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

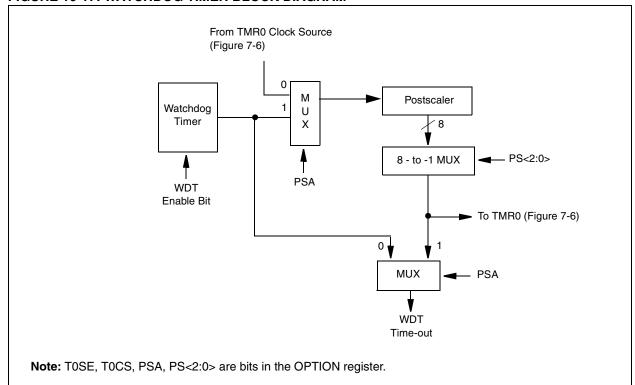

The PIC16CE62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, and is designed to keep the part in reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

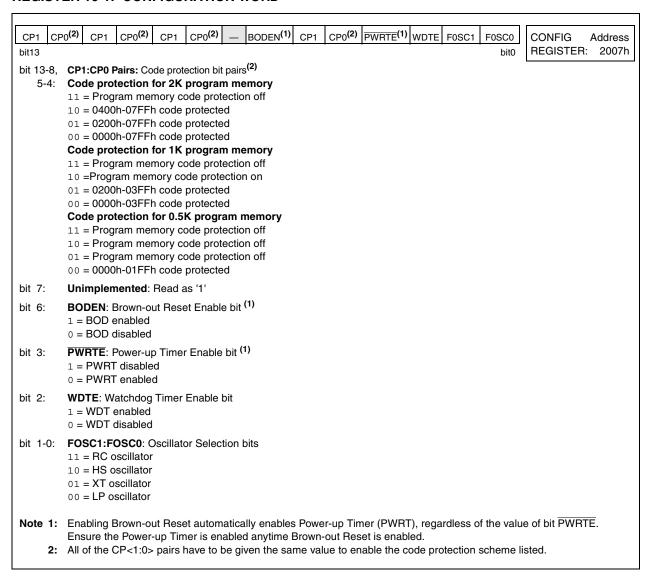

### 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h – 3FFFh), which can be accessed only during programming.

#### REGISTER 10-1: CONFIGURATION WORD

TABLE 10-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

Note 1: When the wake-up is due to an interrupt and global enable bit, GIE is set and the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

TABLE 10-6: INITIALIZATION CONDITION FOR REGISTERS

| Register | Address | Power-on Reset | MCLR Reset during normal operation     MCLR Reset during SLEEP     WDT Reset     Brown-out Reset (1) | Wake-up from SLEEP through interrupt     Wake-up from SLEEP through WDT time-out |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| W        | -       | xxxx xxxx      | uuuu uuuu                                                                                            | uuuu uuuu                                                                        |

| INDF     | 00h     | -              | -                                                                                                    | -                                                                                |

| TMR0     | 01h     | xxxx xxxx      | uuuu uuuu                                                                                            | uuuu uuuu                                                                        |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                            | PC + 1 <sup>(3)</sup>                                                            |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                             | uuuq quuu <sup>(4)</sup>                                                         |

| FSR      | 04h     | xxxx xxxx      | uuuu uuuu                                                                                            | uuuu uuuu                                                                        |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                               | u uuuu                                                                           |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                            | uuuu uuuu                                                                        |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                              | uu uuuu                                                                          |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                               | u uuuu                                                                           |

| INTCON   | 0Bh     | 0000 000x      | 0000 000u                                                                                            | uuuu uqqq <sup>(2)</sup>                                                         |

| PIR1     | 0Ch     | -0             | -0                                                                                                   | -q (2,5)                                                                         |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                            | uuuu uuuu                                                                        |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                               | u uuuu                                                                           |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                            | uuuu uuuu                                                                        |

| PIE1     | 8Ch     | -0             | -0                                                                                                   | -u                                                                               |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                  | uu                                                                               |

| EEINTF   | 90h     | 111            | 111                                                                                                  | 111                                                                              |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                            | uuu- uuuu                                                                        |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

- 2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

- 3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

- 4: See Table 10-5 for reset value for specific condition.

- 5: If wake-up was due to comparator input changing, then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = 1.

- **6:** If reset was due to brown-out, then PCON bit 0 = 0. All other resets will cause bit 0 = u.

### FIGURE 10-17: WATCHDOG TIMER BLOCK DIAGRAM

### FIGURE 10-18: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits | _     | BOREN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION       | RBPU  | INTEDG | T0CS  | T0SE  | PSA   | PS2   | PS1   | PS0   |

Legend: -= Unimplemented location, read as "0", += Reserved for future use

Note: Shaded cells are not used by the Watchdog Timer.

| IORWF            | Inclusive OR W                                                                                 | with f                         |                 |

|------------------|------------------------------------------------------------------------------------------------|--------------------------------|-----------------|

| Syntax:          | [ label ] IORWF                                                                                | f,d                            |                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                     |                                |                 |

| Operation:       | (W) .OR. (f) $\rightarrow$ (d                                                                  | est)                           |                 |

| Status Affected: | Z                                                                                              |                                |                 |

| Encoding:        | 00 0100                                                                                        | dfff                           | ffff            |

| Description:     | Inclusive OR the W<br>register 'f'. If 'd' is 0<br>placed in the W reg<br>result is placed bac | , the result<br>jister. If 'd' | is<br>is 1, the |

| Words:           | 1                                                                                              |                                |                 |

| Cycles:          | 1                                                                                              |                                |                 |

| Example          | IORWF                                                                                          | RESULT,                        | 0               |

|                  | Before Instruction RESULT W After Instruction RESULT W Z                                       | = 0x13<br>= 0x9                | 3               |

|                  |                                                                                                |                                |                 |

| MOVF             | Move f                                                                                                                                                                                                                                                   |      |             |         |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|---------|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                                | MOVF | f,d         |         |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                       |      |             |         |  |  |

| Operation:       | $(f) \rightarrow (des$                                                                                                                                                                                                                                   | st)  |             |         |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                                        |      |             |         |  |  |

| Encoding:        | 0.0                                                                                                                                                                                                                                                      | 1000 | dfff        | ffff    |  |  |

| Description:     | The contents of register f are moved to a destination dependant upon the status of d. If d = 0, destination is W register. If d = 1, the destination is file register f itself. d = 1 is useful to test a file register since status flag Z is affected. |      |             |         |  |  |

| Words:           | 1                                                                                                                                                                                                                                                        |      |             |         |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                        |      |             |         |  |  |

| Example          | MOVF                                                                                                                                                                                                                                                     | FSR, | 0           |         |  |  |

|                  |                                                                                                                                                                                                                                                          |      | ıe in FSR r | egister |  |  |

| MOVLW            | Move Literal to W                                                                          |                     |      |      |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|---------------------|------|------|--|--|--|--|

| Syntax:          | [ label ]                                                                                  | MOVLW               | / k  |      |  |  |  |  |

| Operands:        | $0 \le k \le 25$                                                                           | $0 \leq k \leq 255$ |      |      |  |  |  |  |

| Operation:       | $k\to(W)$                                                                                  | $k \rightarrow (W)$ |      |      |  |  |  |  |

| Status Affected: | None                                                                                       |                     |      |      |  |  |  |  |

| Encoding:        | 11                                                                                         | 00xx                | kkkk | kkkk |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |                     |      |      |  |  |  |  |

| Words:           | 1                                                                                          |                     |      |      |  |  |  |  |

| Cycles:          | 1                                                                                          |                     |      |      |  |  |  |  |

| Example          | MOVLW                                                                                      | 0x5A                |      |      |  |  |  |  |

|                  | After Instruction W = 0x5A                                                                 |                     |      |      |  |  |  |  |

| MOVWF            | Move W                | to f        |        |                              |         |  |  |

|------------------|-----------------------|-------------|--------|------------------------------|---------|--|--|

| Syntax:          | [ label ]             | MOVWI       | = f    |                              |         |  |  |

| Operands:        | $0 \leq f \leq 127$   |             |        |                              |         |  |  |

| Operation:       | $(W) \rightarrow (f)$ | )           |        |                              |         |  |  |

| Status Affected: | None                  |             |        |                              |         |  |  |

| Encoding:        | 00                    | 0000        | 1ff    | f                            | ffff    |  |  |

| Description:     | Move data             | from W r    | egiste | er to i                      | egister |  |  |

| Words:           | 1                     |             |        |                              |         |  |  |

| Cycles:          | 1                     |             |        |                              |         |  |  |

| Example          | MOVWF                 | OPT         | CION   |                              |         |  |  |

|                  | After Inst            | OPTION<br>W | =      | 0xFF<br>0x4F<br>0x4F<br>0x4F | :       |  |  |

NOP No Operation Syntax: [label] NOP Operands: None Operation: No operation Status Affected: None Encoding: 00 0000 0xx0 0000 Description: No operation. Words: 1 Cycles: 1 Example NOP

| RETFIE           | Return fr                                                                           | om Inte                                           | rrupt                                    |                          |

|------------------|-------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------------|--------------------------|

| Syntax:          | [ label ]                                                                           | RETFIE                                            |                                          |                          |

| Operands:        | None                                                                                |                                                   |                                          |                          |

| Operation:       | $TOS \to P$ $1 \to GIE$                                                             | PC,                                               |                                          |                          |

| Status Affected: | None                                                                                |                                                   |                                          |                          |

| Encoding:        | 0 0                                                                                 | 0000                                              | 0000                                     | 1001                     |

| Description:     | Return from<br>and Top of<br>the PC. Int<br>setting Glo<br>GIE (INTC<br>instruction | Stack (To<br>terrupts a<br>obal Interr<br>ON<7>). | OS) is load<br>re enabled<br>rupt Enable | ded in<br>I by<br>e bit, |

| Words:           | 1                                                                                   |                                                   |                                          |                          |

| Cycles:          | 2                                                                                   |                                                   |                                          |                          |

| Example          | RETFIE                                                                              |                                                   |                                          |                          |

|                  |                                                                                     | rrupt<br>PC =<br>GIE =                            | TOS<br>1                                 |                          |

| OPTION             | Load Op                                                                                             | tion Reg                                                     | gister                                                |                            |

|--------------------|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------|----------------------------|

| Syntax:            | [ label ]                                                                                           | OPTION                                                       | 1                                                     |                            |

| Operands:          | None                                                                                                |                                                              |                                                       |                            |

| Operation:         | $(W) \rightarrow OI$                                                                                | PTION                                                        |                                                       |                            |

| Status Affected:   | None                                                                                                |                                                              |                                                       |                            |

| Encoding:          | 00                                                                                                  | 0000                                                         | 0110                                                  | 0010                       |

| Description:       | The conter<br>loaded in t<br>instruction<br>compatibili<br>Since OPT<br>register, th<br>address it. | he OPTIC<br>is supportity with PI<br>TION is a<br>se user ca | ON register<br>rted for coo<br>C16C5X p<br>readable/v | r. This<br>de<br>products. |

| Words:             | 1                                                                                                   |                                                              |                                                       |                            |

| Cycles:<br>Example | 1                                                                                                   | oin unve                                                     | rd com                                                | tibility.                  |

|                    |                                                                                                     | re PIC® N                                                    | rd compa<br>ICU produ<br>action.                      | _                          |

|                    |                                                                                                     |                                                              |                                                       |                            |

| RETLW            | Return with Literal in W                                                                                                                                                |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] RETLW k                                                                                                                                                         |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                     |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                            |  |  |

| Status Affected: | None                                                                                                                                                                    |  |  |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                       |  |  |

| Description:     | The W register is loaded with the eight bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction. |  |  |

| Words:           | 1                                                                                                                                                                       |  |  |

| Cycles:          | 2                                                                                                                                                                       |  |  |

| Example          | CALL TABLE ;W contains table ;offset value ;W now has table value                                                                                                       |  |  |

| TABLE            | ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;  RETLW kn ; End of table                                                                                          |  |  |

|                  | Before Instruction                                                                                                                                                      |  |  |

|                  | W = 0x07                                                                                                                                                                |  |  |

|                  | After Instruction  W = value of k8                                                                                                                                      |  |  |

stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

# 12.11 PICSTART Plus Entry Level Development System

The PICSTART programmer is an easy-to-use, low-cost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PIC devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

### 12.12 <u>SIMICE Entry-Level</u> <u>Hardware Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB-SIM. Both SIMICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PIC 8-bit microcontrollers. SIM-ICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entry-level system development.

# 12.13 PICDEM-1 Low-Cost PIC MCU Demonstration Board

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

# 12.14 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

# 12.15 PICDEM-3 Low-Cost PIC16CXXX Demonstration Board

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

### 12.16 **PICDEM-17**

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756, PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug

**TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP**

|                                                                                        | > | Old | .DIG       | PIC1 | PIC1 | PICI | PIC16 | PIC1 | PIC16 | PIC16 | FIC17 | PIC170 | PIC18 | 93C)<br>52C)<br>54C) | кезн | MCRF        | WCP2 |

|----------------------------------------------------------------------------------------|---|-----|------------|------|------|------|-------|------|-------|-------|-------|--------|-------|----------------------|------|-------------|------|

| MPLAB® C17 Compiler MPLAB® C18 Compiler MPASW/MPLINK MPLAB®-ICE PICMASTER/PICMASTER-CE |   | >   | >          | >    | >    | `    | `     | >    | >     | >     | >     | >      | >     |                      |      |             |      |

| MPLAB® C18 Compiler MPASM/MPLINK MPLAB®-ICE PICMASTER/PICMASTER-CE                     |   |     |            |      |      |      |       |      |       |       | >     | >      |       |                      |      |             |      |

| MPASM/MPLINK MPLAB <sup>®</sup> -ICE PICMASTER/PICMASTER-CE                            |   |     |            |      |      |      |       |      |       |       |       |        | >     |                      |      |             |      |

| MPLAB®-ICE<br>PICMASTER/PICMASTER-CE                                                   | > | >   | >          | >    | >    | >    | >     | >    | >     | >     | >     | >      | >     | >                    | >    |             |      |

| PICMASTER/PICMASTER-CE                                                                 | ^ | >   | ^          | >    | **^  | ^    | ^     | ^    | ^     | `     | >     | ^      | ^     |                      |      |             |      |

|                                                                                        | > | >   | >          | >    |      | >    | >     | >    |       | >     | >     | >      |       |                      |      |             |      |

| ICEPIC™ Low-Cost In-Circuit Emulator                                                   |   | >   | >          | >    |      | >    | >     | >    |       | >     |       |        |       |                      |      |             |      |

| MPLAB <sup>®</sup> -ICD In-Circuit<br>bebugger                                         |   |     | *          |      |      | *>   |       |      | >     |       |       |        |       |                      |      |             |      |

| PICSTART® Plus<br>Low-Cost Universal Dev. Kit                                          | ` | `   | `          | >    | ** ^ | >    | `     | `    | >     | `     | >     | `      | >     |                      |      |             |      |

| PRO MATE® II                                                                           | > | >   | >          | >    | **   | `    | >     | >    | >     | >     | >     | >      | >     | >                    | >    |             |      |

| SIMICE                                                                                 |   | >   |            |      |      |      |       |      |       |       |       |        |       |                      |      |             |      |

| PICDEM-1                                                                               |   | >   |            | >    |      |      |       | ^    |       |       | ^     |        |       |                      |      |             |      |

| PICDEM-2                                                                               |   |     | <b>√</b> † |      |      |      |       |      |       |       |       |        | ^     |                      |      |             |      |

| PICDEM-3                                                                               |   |     |            |      |      |      |       |      |       | ^     |       |        |       |                      |      |             |      |

| PICDEM-14A                                                                             | ^ |     |            |      |      |      |       |      |       |       |       |        |       |                      |      |             |      |

| PICDEM-17                                                                              |   |     |            |      |      |      |       |      |       |       |       | ^      |       |                      |      |             |      |

| KEELOQ® Evaluation Kit                                                                 |   |     |            |      |      |      |       |      |       |       |       |        |       |                      | ^    |             |      |

| KEELOQ Transponder Kit                                                                 |   |     |            |      |      |      |       |      |       |       |       |        |       |                      | >    |             |      |

| microlD <sup>TM</sup> Programmer's Kit                                                 |   |     |            |      |      |      |       |      |       |       |       |        |       |                      |      | >           |      |

| 125 kHz microID Developer's Kit                                                        |   |     |            |      |      |      |       |      |       |       |       |        |       |                      |      | `           |      |

| 125 kHz Anticollision microID<br>Developer's Kit                                       |   |     |            |      |      |      |       |      |       |       |       |        |       |                      |      | `           |      |

| 13.56 MHz Anticollision microlD<br>Developer's Kit                                     |   |     |            |      |      |      |       |      |       |       |       |        |       |                      |      | <i>&gt;</i> |      |

| MCP2510 CAN Developer's Kit                                                            |   |     |            |      |      |      |       |      |       |       |       |        |       |                      |      |             | ^    |

**NOTES:**

### 14.1 Package Marking Information

#### 18-Lead PDIP

### 18-Lead SOIC (.300")

### 18-Lead CERDIP Windowed

#### 20-Lead SSOP

### Example

### Example

### **Example**

### **Example**

Legend: XX...X Customer-specific information

Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

By-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (a)

can be found on the outer packaging for this package.

In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

Note:

| INDEX                               | BTFSC                                               |

|-------------------------------------|-----------------------------------------------------|

| A                                   | BTFSS 6                                             |

| ADDLW Instruction67                 | CALL 6                                              |

| ADDWF Instruction                   | CLRF                                                |

| ANDLW Instruction                   | CLRW                                                |

| ANDWF Instruction 67                | CLRWDT 7                                            |

| Architectural Overview              | COMF                                                |

| Assembler                           | DECF                                                |

| MPASM Assembler77                   | DECFSZ 7                                            |

| _                                   | GOTO                                                |

| В                                   | INCF                                                |

| BCF Instruction                     | INCFSZ                                              |

| Block Diagram                       | IORUV                                               |

| TIMER0                              | MOVF 7                                              |

| TMR0/WDT PRESCALER                  | MOVLW 7                                             |

| Brown-Out Detect (BOD)              | MOVWF                                               |

| BSF Instruction                     | NOP                                                 |

| BTFSS Instruction 69                | OPTION                                              |

| _                                   | RETFIE                                              |

| C                                   | RETLW                                               |

| CALL Instruction69                  | RETURN                                              |

| Clocking Scheme/Instruction Cycle10 | RLF 7                                               |

| CLRF Instruction                    | RRF 7                                               |

| CLRW Instruction                    | SLEEP                                               |

| CLRWDT Instruction                  | SUBLW7                                              |

| CMCON Register41                    | SUBWF7                                              |

| Code Protection                     | SWAPF7                                              |

| COMF Instruction                    | TRIS 7                                              |

| Comparator Configuration            | XORLW 7                                             |

| Comparator Interrupts               | XORWF 7                                             |

| Comparator Module                   | Instruction Set Summary 6                           |

| Comparator Reference                | INT Interrupt                                       |

| Configuration Bits                  | INTCON Register                                     |

| Configuring the Voltage Reference   | Interrupts                                          |

| Crystal Operation                   | IORLW Instruction                                   |

| D                                   | IORWF Instruction                                   |

| _                                   | K                                                   |

| Data Memory Organization            | KeeLoq® Evaluation and Programming Tools 8          |

| DECF Instruction                    | М                                                   |

| DECFSZ Instruction                  | MOVF Instruction7                                   |

| Development Support                 | MOVLW Instruction                                   |

| E                                   | MOVWF Instruction                                   |

| EEPROM Peripheral Operation29       | MPLAB Integrated Development Environment Software 7 |

| Errata2                             | N                                                   |

| External Crystal Oscillator Circuit |                                                     |

| G                                   | NOP Instruction 7                                   |

| General purpose Register File       | 0                                                   |

| GOTO Instruction71                  | One-Time-Programmable (OTP) Devices                 |

| 1                                   | OPTION Instruction 7                                |

| 1                                   | OPTION Register 1                                   |

| I/O Ports                           | Oscillator Configurations5                          |

| I/O Programming Considerations      | Oscillator Start-up Timer (OST)5                    |

| ID Locations                        | P                                                   |

| INCF Instruction                    | Package Marking Information10                       |

|                                     | Packaging Information9                              |

| In-Circuit Serial Programming       | PCL and PCLATH                                      |

| Instruction Flow/Pipelining10       | PCON Register1                                      |

| Instruction Set                     | PICDEM-1 Low-Cost PIC MCU Demo Board                |

| ADDLW                               | PICDEM-2 Low-Cost PIC16CXX Demo Board               |

| ADDWF                               | PICDEM-3 Low-Cost PIC16CXXX Demo Board 7            |

| ANDLW                               | PICSTART® Plus Entry Level Development System 7     |

| ANDWF                               | PIE1 Register1                                      |

| BCF68                               | Pinout Description                                  |

| BSF                                 | PIR1 Register1                                      |

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1998-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769768

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.