Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce624-04e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

### REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1    | R/W-1                                                                                                                                                                                                                                                               | R/W-1                                                                                                                                                             | R/W-1     | R/W-1     | R/W-1         | R/W-1      | R/W-1 |                                                                                                                   |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|---------------|------------|-------|-------------------------------------------------------------------------------------------------------------------|

| RBPU     | INTEDG                                                                                                                                                                                                                                                              | TOCS                                                                                                                                                              | TOSE      | PSA       | PS2           | PS1        | PS0   | R = Readable bit                                                                                                  |

| bit7     |                                                                                                                                                                                                                                                                     |                                                                                                                                                                   |           |           |               |            | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |

| bit 7:   | <b>RBPU</b> : PO<br>1 = PORTE<br>0 = PORTE                                                                                                                                                                                                                          | 3 pull-ups                                                                                                                                                        | are disal | oled      | lividual port | latch valu | es    |                                                                                                                   |

| bit 6:   | INTEDG: In<br>1 = Interrup<br>0 = Interrup                                                                                                                                                                                                                          | ot on rising                                                                                                                                                      | g edge o  | f RB0/INT |               |            |       |                                                                                                                   |

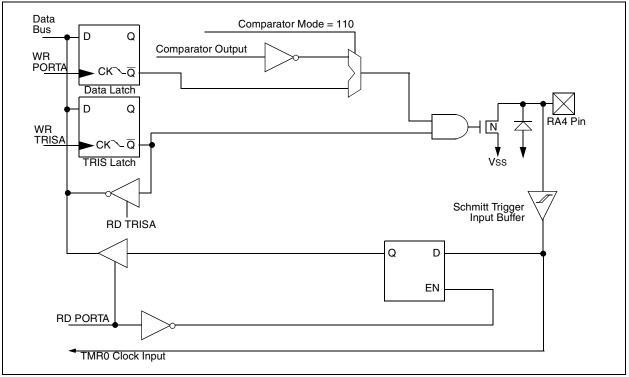

| bit 5:   | <b>TOCS</b> : TMF<br>1 = Transiti<br>0 = Interna                                                                                                                                                                                                                    | ion on RA                                                                                                                                                         | 4/T0CKI   | pin       | (OUT)         |            |       |                                                                                                                   |

| bit 4:   | 1 = Increm                                                                                                                                                                                                                                                          | <b>TOSE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin |           |           |               |            |       |                                                                                                                   |

| bit 3:   | PSA: Prese<br>1 = Presca<br>0 = Presca                                                                                                                                                                                                                              | ler is assi                                                                                                                                                       | gned to t | he WDT    | ) module      |            |       |                                                                                                                   |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : F                                                                                                                                                                                                                                            | Prescaler I                                                                                                                                                       | Rate Sele | ect bits  |               |            |       |                                                                                                                   |

|          | Bit Value                                                                                                                                                                                                                                                           | TMR0 Ra                                                                                                                                                           | te WD1    | Γ Rate    |               |            |       |                                                                                                                   |

|          | 000       1:2       1:1         001       1:4       1:2         010       1:8       1:4         011       1:16       1:8         100       1:32       1:16         101       1:64       1:32         110       1:128       1:64         111       1:256       1:128 |                                                                                                                                                                   |           |           |               |            |       |                                                                                                                   |

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

| R/W-0       | R/W-0                                                                                                                                                                      | R/W-0                                                                                                                                                                                       | R/W-0                                  | R/W-0        | R/W-0     | R/W-0 | R/W-x        |                                                                                                                                       |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|-----------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| GIE<br>bit7 | PEIE                                                                                                                                                                       | TOIE                                                                                                                                                                                        | INTE                                   | RBIE         | TOIF      | INTF  | RBIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |

| bit 7:      |                                                                                                                                                                            |                                                                                                                                                                                             | masked in                              |              |           |       |              |                                                                                                                                       |

| bit 6:      |                                                                                                                                                                            | es all un-r                                                                                                                                                                                 | terrupt En<br>masked pe<br>ipheral int | eripheral ir | nterrupts |       |              |                                                                                                                                       |

| bit 5:      | 1 = Enabl                                                                                                                                                                  | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                                       |                                        |              |           |       |              |                                                                                                                                       |

| bit 4:      | 1 = Enabl                                                                                                                                                                  | INTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                                    |                                        |              |           |       |              |                                                                                                                                       |

| bit 3:      | 1 = Enabl                                                                                                                                                                  | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                  |                                        |              |           |       |              |                                                                                                                                       |

| bit 2:      | <b>TOIF</b> : TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                     |                                                                                                                                                                                             |                                        |              |           |       |              |                                                                                                                                       |

| bit 1:      | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur |                                                                                                                                                                                             |                                        |              |           |       |              |                                                                                                                                       |

| bit 0:      | 1 = When                                                                                                                                                                   | <b>RBIF</b> : RB Port Change Interrupt Flag bit<br>1 = When at least one of the RB<7:4> pins changed state (must be cleared in software)<br>0 = None of the RB<7:4> pins have changed state |                                        |              |           |       |              |                                                                                                                                       |

| Name    | Bit # | Buffer Type           | Function                                                                                                                |

|---------|-------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|

| RB0/INT | bit0  | TTL/ST <sup>(1)</sup> | Input/output or external interrupt input. Internal software programmable weak pull-up.                                  |

| RB1     | bit1  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB2     | bit2  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB3     | bit3  | TTL                   | Input/output pin. Internal software programmable weak pull-up.                                                          |

| RB4     | bit4  | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                               |

| RB5     | bit5  | TTL                   | Input/output pin (with interrupt on change). Internal software programmable weak pull-up.                               |

| RB6     | bit6  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming clock pin. |

| RB7     | bit7  | TTL/ST <sup>(2)</sup> | Input/output pin (with interrupt on change). Internal software programmable weak pull-up. Serial programming data pin.  |

TABLE 5-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger, TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt.

**Note 2:** This buffer is a Schmitt Trigger input when used in serial programming mode.

#### TABLE 5-4: SUMMARY OF REGISTERS ASSOCIATED WITH PORTB

| Address | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 06h     | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx xxxx        | uuuu uuuu                       |

| 86h     | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111        | 1111 1111                       |

| 81h     | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111        | 1111 1111                       |

Legend: u = unchanged, x = unknown

**Note:** Shaded bits are not used by PORTB.

#### 6.3 Write Operations

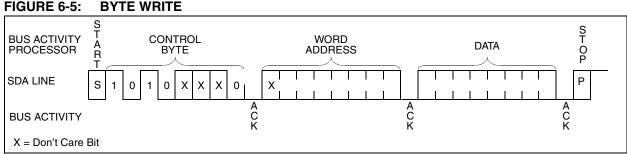

#### BYTE WRITE 6.3.1

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the R/W bit, which is a logic low, is placed onto the bus by the processor. This indicates to the EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer of the EEPROM. After receiving another acknowledge signal from the EEPROM, the processor will transmit the data word to be written into the addressed memory location. The EEPROM acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time, the EEPROM will not generate acknowledge signals (Figure 6-5).

#### 6.3.2 PAGE WRITE

The write control byte, word address and the first data byte are transmitted to the EEPROM in the same way as in a byte write. But instead of generating a stop condition, the processor transmits up to eight data bytes to the EEPROM, which are temporarily stored in the onchip page buffer and will be written into the memory after the processor has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the processor should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin (Figure 6-6).

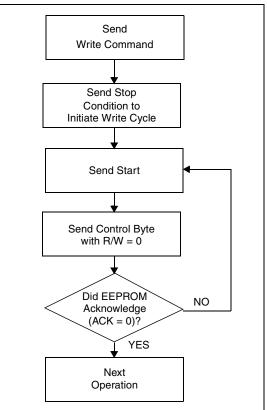

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the EEPROM initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. See Figure 6-4 for flow diagram.

#### FIGURE 6-4: ACKNOWLEDGE POLLING FLOW

#### FIGURE 6-5:

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

## EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| 1.BCF    | STATUS, RPO | ;Skip if already in      |

|----------|-------------|--------------------------|

|          |             | ; Bank 0                 |

| 2.CLRWDT |             | ;Clear WDT               |

| 3.CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| 4.BSF    | STATUS, RPO | ;Bank 1                  |

| 5.MOVLW  | '00101111'b | ;These 3 lines (5, 6, 7) |

| 6.MOVWF  | OPTION      | ; are required only if   |

|          |             | ; desired PS<2:0> are    |

| 7.CLRWDT |             | ; 000 or 001             |

| 8.MOVLW  | '00101xxx'b | ;Set Postscaler to       |

| 9.MOVWF  | OPTION      | ; desired WDT rate       |

| 10.BCF   | STATUS, RPO | ;Return to Bank 0        |

|          |             |                          |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

## EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and<br>;prescaler |

|--------|-------------|------------------------------|

|        |             | /prebearer                   |

| BSF    | STATUS, RPO |                              |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new            |

|        |             | ;prescale value and          |

|        |             | ;clock source                |

| MOVWF  | OPTION_REG  |                              |

| BCF    | STATUS, RPO |                              |

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6       | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|--------|--------|-------------|-------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 01h     | TMR0   | Timer0 | module regi | ister |        |        |        |        |        | xxxx xxxx        | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE        | T0IE  | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x        | 0000 000u                       |

| 81h     | OPTION | RBPU   | INTEDG      | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111        | 1111 1111                       |

| 85h     | TRISA  |        |             | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111           | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged.

Note: Shaded bits are not used by TMR0 module.

#### 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

### 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

#### 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

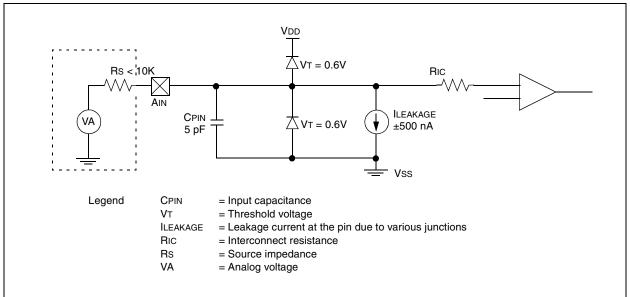

#### 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 8-4: ANALOG INPUT MODEL

### 10.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16CE62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-Up Timer (OST) Brown-out Reset (BOD)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

The PIC16CE62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, and is designed to keep the part in reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 10.4.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired, then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no time-out at all. Figure 10-8, Figure 10-9 and Figure 10-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 10-9). This is useful for testing purposes or to synchronize more than one  $\text{PIC}^{\textcircled{B}}$  device operating in parallel.

Table 10-5 shows the reset conditions for some special registers, while Table 10-6 shows the reset conditions for all the registers.

#### 10.4.6 POWER CONTROL (PCON)/STATUS REGISTER

The power control/status register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on power-on-reset. It must then be set by the user and checked on subsequent resets to see if  $\overline{\text{BOR}} = 0$  indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on-reset). It is a '0' on power-on-reset and unaffected otherwise. The user must write a '1' to this bit following a power-on-reset. On a subsequent reset, if POR is '0', it will indicate that a power-on-reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-------------------|-----------|-------------------|-----------------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0  | PWRTE = 1 | brown-out neset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             | _         | 72 ms             | —                     |  |

#### TABLE 10-3: TIME-OUT IN VARIOUS SITUATIONS

| POR | BOR | TO | PD |                           |

|-----|-----|----|----|---------------------------|

| 0   | Х   | 1  | 1  | Power-on-reset            |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR |

**Brown-out Reset**

WDT Reset

WDT Wake-up

MCLR reset during normal operation

MCLR reset during SLEEP

#### TABLE 10-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Х

u

0

u

Ο

Legend: x = unknown, u = unchanged

0

1

1

1

1

Х

0

0

u

1

1

1

1

1

1

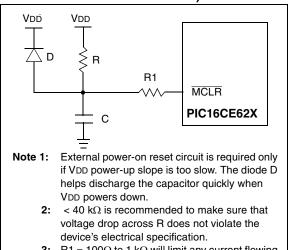

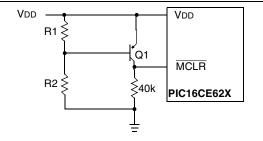

#### FIGURE 10-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

**3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

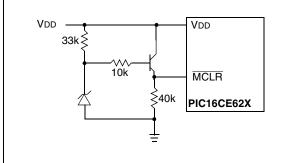

#### FIGURE 10-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal Brown-out Reset circuitry should be disabled when using this circuit.

#### FIGURE 10-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \times \frac{R1}{R1 + R2} = 0.7 V$$

- **2:** Internal brown-out detection should be disabled when using this circuit.

- **3:** Resistors should be adjusted for the characteristics of the transistor.

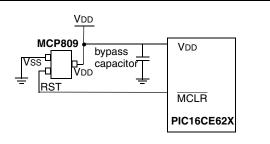

#### FIGURE 10-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

#### 10.6 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (i.e. W register and STATUS register). This will have to be implemented in software.

Example 10-1 stores and restores the STATUS and W registers. The user register, W\_TEMP, must be defined in both banks and must be defined at the same offset from the bank base address (i.e., W\_TEMP is defined at 0x70 in Bank 0 and it must also be defined at 0xF0 in Bank 1). The user register, STATUS\_TEMP, must be defined in Bank 0. The Example 10-1:

- Stores the W register

- Stores the STATUS register in Bank 0

- Executes the ISR code

- Restores the STATUS (and bank select bit register)

- · Restores the W register

#### EXAMPLE 10-1: SAVING THE STATUS AND W REGISTERS IN RAM

| MOVWF | W_TEMP        | ;copy W to temp register,<br>;could be in either bank                  |

|-------|---------------|------------------------------------------------------------------------|

| SWAPF | STATUS,W      | ;swap status to be saved into ${\tt W}$                                |

| BCF   | STATUS, RPO   | ;change to bank 0 regardless<br>;of current bank                       |

| MOVWF | STATUS_TEMP   | ;save status to bank 0<br>;register                                    |

| :     |               |                                                                        |

| :     | (ISR)         |                                                                        |

| :     |               |                                                                        |

| SWAPF | STATUS_TEMP,W | ;swap STATUS_TEMP register<br>;into W, sets bank to original<br>;state |

| MOVWF | STATUS        | ;move W into STATUS register                                           |

| SWAPF | W_TEMP,F      | ;swap W_TEMP                                                           |

| SWAPF | W_TEMP,W      | ;swap W_TEMP into W                                                    |

### 10.7 <u>Watchdog Timer (WDT)</u>

The Watchdog Timer is a free running on-chip RC oscillator which does not require any external components. This RC oscillator is separate from the RC oscillator of the CLKIN pin. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device have been stopped, for example, by execution of a SLEEP instruction. During normal operation, a WDT time-out generates a device RESET. If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the configuration bit WDTE as clear (Section 10.1).

#### 10.7.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler, if assigned to the WDT, and prevent it from timing out and generating a device RESET.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer time-out.

#### 10.7.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 10.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit in the STATUS register is cleared, the  $\overline{TO}$  bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSS, with no external circuitry drawing current from the I/O pin, and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |

|-------|-------------------------------------------|

|       | by a WDT time-out does not drive MCLR     |

|       | pin low.                                  |

#### 10.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register can be used to determine the cause of device reset.  $\overline{PD}$ bit, which is set on power-up is cleared when SLEEP is invoked.  $\overline{TO}$  bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

| If the global interrupts are disabled (GIE is |

|-----------------------------------------------|

| cleared), but any interrupt source has both   |

| its interrupt enable bit and the correspond-  |

| ing interrupt flag bits set, the device will  |

| immediately wake-up from sleep. The           |

| sleep instruction is completely executed.     |

|                                               |

The WDT is cleared when the device wakes-up from sleep, regardless of the source of wake-up.

| Q1 Q2 Q3 Q4 Q1 Q                     | Q2 Q3 Q4 Q1           | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4                           | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 |

|--------------------------------------|-----------------------|--------------|---------------------------------------|------------------|-------------|

|                                      |                       |              |                                       |                  |             |

| CLKOUT(4) \                          |                       | /            |                                       |                  |             |

| INT pin                              |                       |              | · · · · · · · · · · · · · · · · · · · |                  | i           |

| INTF flag<br>(INTCON<1>)             |                       | · · · · ·    | Interrupt Latency                     |                  |             |

| GIE bit<br>(INTCON<7>)               | Processor in<br>SLEEP |              |                                       | י<br>ו<br>ו<br>ו |             |

| INSTRUCTION FLOW                     |                       | · ·          | i I<br>I I                            | 1                | 1<br>1      |

| PC X PC X F                          | PC+1 X PC+2           | X PC+2       | PC + 2                                | (0004h)          | 0005h       |

| Instruction { Inst(PC) = SLEEP Ins   | st(PC + 1)            | Inst(PC + 2) | 1 I                                   | Inst(0004h)      | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1) | EEP                   | Inst(PC + 1) | Dummy cycle                           | Dummy cycle      | Inst(0004h) |

#### FIGURE 10-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**Note 1:** XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay does not occur for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

| CLRWDT           | Clear Watchdog Timer                                                                                                                                     |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                           |  |  |  |  |

| Operands:        | None                                                                                                                                                     |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                   |  |  |  |  |

| Encoding:        | 00 0000 0110 0100                                                                                                                                        |  |  |  |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$ are set.          |  |  |  |  |

| Words:           | 1                                                                                                                                                        |  |  |  |  |

| Cycles:          | 1                                                                                                                                                        |  |  |  |  |

| Example          | CLRWDT                                                                                                                                                   |  |  |  |  |

|                  | Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = 0x00<br>WDT prescaler= 0<br>TO = 1<br>PD = 1                                 |  |  |  |  |

| COMF             | Complement f                                                                                                                                             |  |  |  |  |

| Syntax:          | [label] COMF f,d                                                                                                                                         |  |  |  |  |

| COME             | Complement                                                                                                                                              |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] COMF f,d                                                                                                                                        |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                         |  |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                     |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                       |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the result is<br>stored in W. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                       |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                       |  |  |  |  |  |  |

| Example          | COMF REG1,0                                                                                                                                             |  |  |  |  |  |  |

|                  | Before InstructionREG1= $0x13$ After InstructionREG1= $0x13$ W= $0xEC$                                                                                  |  |  |  |  |  |  |

|                  |                                                                                                                                                         |  |  |  |  |  |  |

| Decrement f                                                                                                                                     |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                 |  |  |  |  |  |

| [label] DECF f,d                                                                                                                                |  |  |  |  |  |

| $0 \le f \le 127$                                                                                                                               |  |  |  |  |  |

| d ∈ [0,1]                                                                                                                                       |  |  |  |  |  |

| (f) - 1 $\rightarrow$ (dest)                                                                                                                    |  |  |  |  |  |

| Z                                                                                                                                               |  |  |  |  |  |

| 00 0011 dfff ffff                                                                                                                               |  |  |  |  |  |

| Decrement register 'f'. If 'd' is 0, the<br>result is stored in the W register. If 'd'<br>is 1, the result is stored back in regis-<br>ter 'f'. |  |  |  |  |  |

| 1                                                                                                                                               |  |  |  |  |  |

| 1                                                                                                                                               |  |  |  |  |  |

| DECF CNT, 1                                                                                                                                     |  |  |  |  |  |

| Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                           |  |  |  |  |  |

| Decrement f, Skip if 0                                                                                                                          |  |  |  |  |  |

| [ <i>label</i> ] DECFSZ f,d                                                                                                                     |  |  |  |  |  |

| $0 \leq f \leq 127$                                                                                                                             |  |  |  |  |  |

| d ∈ [0,1]                                                                                                                                       |  |  |  |  |  |

|                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                           |                                                   |                                   |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------|--|--|--|

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                          |                                                   |                                   |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                      |                                                   |                                   |  |  |  |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                         |                                                   |                                   |  |  |  |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. If the result is 0, the next instruction, which is already fetched, is discarded. A NOP is executed instead making it a two-cycle instruction. |                                                   |                                   |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                         |                                                   |                                   |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                      |                                                   |                                   |  |  |  |

| Example          | HERE<br>CONTINU                                                                                                                                                                                                                                                                                           | DECF<br>GOTO<br>JE<br>•                           | SZ CNI<br>LOC                     |  |  |  |

|                  | Before In<br>PC<br>After Inst<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC                                                                                                                                                                                                                                      | = ado<br>ruction<br>= CN<br>= 0,<br>= ado<br>≠ 0, | iress HERE<br>T - 1<br>iress CONT |  |  |  |

| GOTO                              | Unconditional Branch                                                                                                                                                                               | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:                           | [ <i>label</i> ] GOTO k                                                                                                                                                                            | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Operands:                         | $0 \le k \le 2047$                                                                                                                                                                                 | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Operation:                        | $k \rightarrow PC < 10:0 >$                                                                                                                                                                        |                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                   | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                               |  |  |  |  |

| Status Affected:                  | None                                                                                                                                                                                               | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Encoding:                         | 10 1kkk kkkk kkkk                                                                                                                                                                                  | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Description:<br>Words:<br>Cycles: | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.<br>1 | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. |  |  |  |  |

| Example                           | GOTO THERE                                                                                                                                                                                         | Words:           | 1                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|                                   | After Instruction<br>PC = Address THERE                                                                                                                                                            | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                                   | FC = Addless There                                                                                                                                                                                 | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                                   |                                                                                                                                                                                                    |                  | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|                                   |                                                                                                                                                                                                    |                  | •                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

$\begin{array}{rcl} Before \ Instruction \\ PC &= & address \ HERE \\ After \ Instruction \\ CNT &= & CNT + 1 \\ if \ CNT = & 0, \\ PC &= & address \ CONTINUE \\ if \ CNT \neq & 0, \\ PC &= & address \ HERE \ +1 \\ \end{array}$

| INCF             | Increment f                                                                                                                                                         |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                    |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                     |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                   |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                   |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                   |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                   |  |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                         |  |  |  |  |  |

|                  | Before Instruction $CNT = 0xFF$ $Z = 0$ After Instruction $CNT = 0x00$ $Z = 1$                                                                                      |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                            |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                               |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                           |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                      |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |

| Words:           | 1                                                                                                                      |  |  |  |  |  |

| Cycles:          | 1                                                                                                                      |  |  |  |  |  |

| Example          | IORLW 0x35                                                                                                             |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                               |  |  |  |  |  |

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

#### 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

#### 13.2 DC CHARACTERISTICS: F

#### PIC16LCE62X-04 (Commercial, Industrial)

| DC CHARACTERISTICS |                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$           |      |      |           |                  |                                                                                  |

|--------------------|---------------------|----------------------------------------------------------------|------|------|-----------|------------------|----------------------------------------------------------------------------------|

| Param<br>No.       | Sym                 | Characteristic                                                 | Min  | Тур† | Мах       | Units            | Conditions                                                                       |

| D001               | Vdd                 | Supply Voltage                                                 | 2.5  | -    | 5.5       | V                | See Figure 13-1 through Figure 13-3                                              |

| D002               | Vdr                 | RAM Data Retention<br>Voltage (Note 1)                         | -    | 1.5* | -         | V                | Device in SLEEP mode                                                             |

| D003               | VPOR                | VDD start voltage to<br>ensure Power-on Reset                  | -    | Vss  | -         | V                | See section on power-on reset for details                                        |

| D004               | SVDD                | VDD rise rate to ensure<br>Power-on Reset                      | .05* | -    | -         | V/ms             | See section on power-on reset for details                                        |

| D005               | VBOR                | Brown-out Detect Voltage                                       | 3.7  | 4.0  | 4.35      | V                | BOREN configuration bit is cleared                                               |

| D010               | IDD                 | Supply Current (Note 2)                                        | -    | 1.2  | 2.0       | mA               | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)*                |

|                    |                     |                                                                | -    | -    | 1.1       | mA               | FOSC = 4 MHz, $VDD = 2.5V$ , $WDT$ disabled,                                     |

|                    |                     |                                                                | -    | 35   | 70        | μA               | XT osc mode, (Note 4)<br>Fosc = 32 kHz, VDD = 2.5V, WDT disabled,<br>LP osc mode |

| D020               | IPD                 | Power Down Current (Note 3)                                    | _    | -    | 2.0       | μA               | VDD = 2.5V                                                                       |

|                    |                     |                                                                | -    | -    | 2.2       | μA               | VDD = 3.0V*                                                                      |

|                    |                     |                                                                | -    | -    | 9.0       | μA               | VDD = 5.5V                                                                       |

|                    |                     |                                                                | -    | -    | 15        | μA               | VDD = 5.5V Extended                                                              |

| D022               | $\Delta$ IWDT       | WDT Current (Note 5)                                           | -    | 6.0  | 10        | μA               | VDD=4.0V                                                                         |

| D022A              | $\Delta$ IBOR       | Brown-out Reset Current                                        | _    | 75   | 12<br>125 | μ <b>Α</b><br>μΑ | $(125^{\circ}C)$<br>BOD enabled, VDD = 5.0V                                      |

| D023               |                     | (Note 5)<br>Comparator Current for each<br>Comparator (Note 5) | -    | 30   | 60        | μA               | VDD = 4.0V                                                                       |

| D023A              | $\Delta$ IVREF      | VREF Current (Note 5)                                          | -    | 80   | 135       | μA               | VDD = 4.0V                                                                       |

|                    | $\Delta$ IEE Write  | Operating Current                                              | -    |      | 3         | mA               | Vcc = 5.5V, SCL = 400 kHz                                                        |

|                    | $\Delta IEE \ Read$ | Operating Current                                              | -    |      | 1         | mA               |                                                                                  |

|                    | $\Delta IEE$        | Standby Current                                                | -    |      | 30        | μA               | VCC = 3.0V, EE VDD = VCC                                                         |

|                    | $\Delta IEE$        | Standby Current                                                | -    |      | 100       | μA               | VCC = 3.0V, EE VDD = VCC                                                         |

| 1A                 | Fosc                | LP Oscillator Operating Frequency                              | 0    | —    | 200       | kHz              | All temperatures                                                                 |

|                    |                     | RC Oscillator Operating Frequency                              |      | —    | 4         | MHz              | All temperatures                                                                 |

|                    |                     | XT Oscillator Operating Frequency                              | 0    | —    | 4<br>20   | MHz              | All temperatures                                                                 |

|                    |                     | HS Oscillator Operating Frequency                              | -    |      | 20        | MHz              | All temperatures                                                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.