Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce624-04e-ss |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | General Description                           | 3     |

|-------|-----------------------------------------------|-------|

| 2.0   | PIC16CE62X Device Varieties                   | 5     |

| 3.0   | Architectural Overview                        |       |

| 4.0   | Memory Organization                           | 11    |

| 5.0   | I/O Ports                                     |       |

| 6.0   | EEPROM Peripheral Operation                   | 29    |

| 7.0   | Timer0 Module                                 |       |

| 8.0   | Comparator Module                             | 41    |

| 9.0   | Voltage Reference Module                      | 47    |

| 10.0  | Special Features of the CPU                   | 49    |

| 11.0  | Instruction Set Summary                       | 65    |

|       | Development Support                           |       |

|       | Electrical Specifications                     |       |

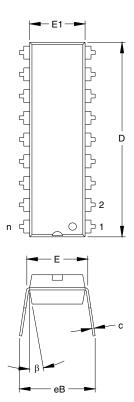

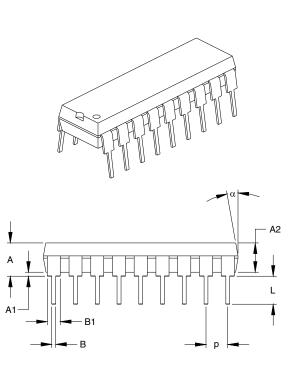

| 14.0  | Packaging Information                         | 97    |

| Appe  | ndix A: Code for Accessing EEPROM Data Memory | 103   |

| Index |                                               | 105   |

| On Li | ne Support                                    | . 107 |

| Read  | ne Support<br>er Response                     | 108   |

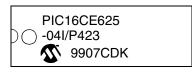

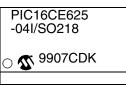

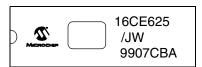

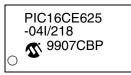

| PIC1  | 6CE62X Product Identification System          | . 109 |

### To Our Valued Customers

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

NOTES:

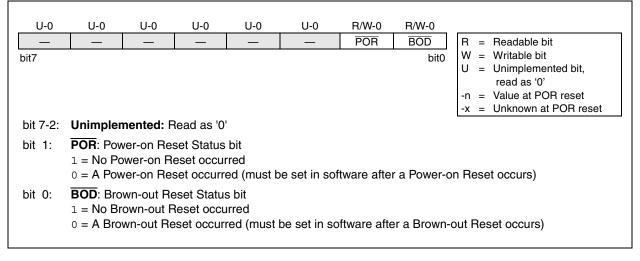

### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset, an external  $\overline{\text{MCLR}}$  reset, WDT reset or a Brown-out Reset.

| Note: | BOD is unknown on Power-on Reset. It        |

|-------|---------------------------------------------|

|       | must then be set by the user and checked    |

|       | on subsequent resets to see if BOD is       |

|       | cleared, indicating a brown-out has         |

|       | occurred. The BOD status bit is a "don't    |

|       | care" and is not necessarily predictable if |

|       | the brown-out circuit is disabled (by       |

|       | programming BODEN bit in the                |

|       | configuration word).                        |

## REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

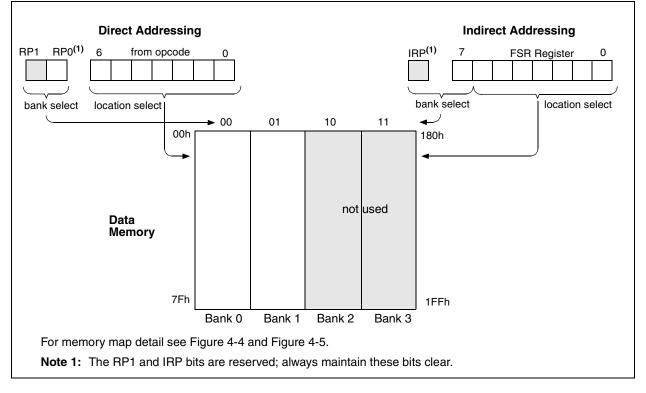

### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16CE62X. A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

| EXAMPLE 4-1: |       | INDIRECT ADDRESSING |                      |  |  |  |

|--------------|-------|---------------------|----------------------|--|--|--|

|              | movlw | 0x20                | ;initialize pointer  |  |  |  |

|              | movwf | FSR                 | ;to RAM              |  |  |  |

| NEXT         | clrf  | INDF                | clear INDF register; |  |  |  |

|              | incf  | FSR                 | ;inc pointer         |  |  |  |

|              | btfss | FSR,4               | ;all done?           |  |  |  |

|              | goto  | NEXT                | ;no clear next       |  |  |  |

|              |       |                     | ;yes continue        |  |  |  |

| CONTINUE:    |       |                     |                      |  |  |  |

## FIGURE 4-7: DIRECT/INDIRECT ADDRESSING PIC16CE62X

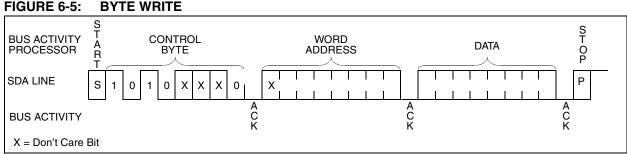

### 6.3 Write Operations

### BYTE WRITE 6.3.1

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the R/W bit, which is a logic low, is placed onto the bus by the processor. This indicates to the EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer of the EEPROM. After receiving another acknowledge signal from the EEPROM, the processor will transmit the data word to be written into the addressed memory location. The EEPROM acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time, the EEPROM will not generate acknowledge signals (Figure 6-5).

### 6.3.2 PAGE WRITE

The write control byte, word address and the first data byte are transmitted to the EEPROM in the same way as in a byte write. But instead of generating a stop condition, the processor transmits up to eight data bytes to the EEPROM, which are temporarily stored in the onchip page buffer and will be written into the memory after the processor has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the processor should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin (Figure 6-6).

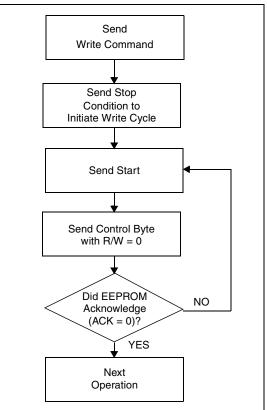

### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the EEPROM initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. See Figure 6-4 for flow diagram.

### FIGURE 6-4: ACKNOWLEDGE POLLING FLOW

### FIGURE 6-5:

### 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

# 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

## 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

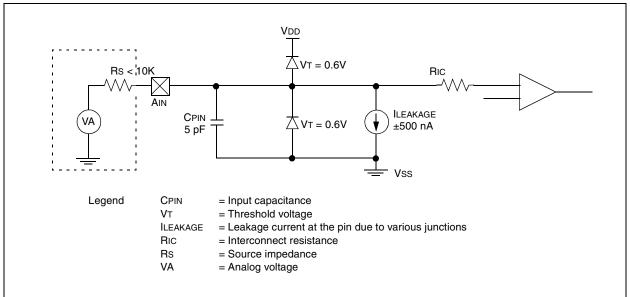

## 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

### FIGURE 8-4: ANALOG INPUT MODEL

| Name   | Bit 7                                    | Bit 6                                                   | Bit 5                                                       | Bit 4                                                            | Bit 3                                                                        | Bit 2                                                                                     | Bit 1                                                                                                 | Bit 0                                                                                                             | Value on:<br>POR                                                                                                              | Value on<br>All Other<br>Resets                                                                                                                                                                                                                                                     |

|--------|------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMCON  | C2OUT                                    | C1OUT                                                   |                                                             | _                                                                | CIS                                                                          | CM2                                                                                       | CM1                                                                                                   | CM0                                                                                                               | 00 0000                                                                                                                       | 00 0000                                                                                                                                                                                                                                                                             |

| VRCON  | VREN                                     | VROE                                                    | VRR                                                         | —                                                                | VR3                                                                          | VR2                                                                                       | VR1                                                                                                   | VR0                                                                                                               | 000- 0000                                                                                                                     | 000- 0000                                                                                                                                                                                                                                                                           |

| INTCON | GIE                                      | PEIE                                                    | TOIE                                                        | INTE                                                             | RBIE                                                                         | T0IF                                                                                      | INTF                                                                                                  | RBIF                                                                                                              | 0000 000x                                                                                                                     | 0000 000u                                                                                                                                                                                                                                                                           |

| PIR1   | _                                        | CMIF                                                    |                                                             | _                                                                | _                                                                            |                                                                                           | _                                                                                                     | _                                                                                                                 | -0                                                                                                                            | -0                                                                                                                                                                                                                                                                                  |

| PIE1   | —                                        | CMIE                                                    | —                                                           | —                                                                | —                                                                            | —                                                                                         | —                                                                                                     | —                                                                                                                 | -0                                                                                                                            | -0                                                                                                                                                                                                                                                                                  |

| TRISA  | —                                        | —                                                       | _                                                           | TRISA4                                                           | TRISA3                                                                       | TRISA2                                                                                    | TRISA1                                                                                                | TRISA0                                                                                                            | 1 1111                                                                                                                        | 1 1111                                                                                                                                                                                                                                                                              |

|        | CMCON<br>VRCON<br>INTCON<br>PIR1<br>PIE1 | CMCON C2OUT<br>VRCON VREN<br>INTCON GIE<br>PIR1<br>PIE1 | CMCONC2OUTC1OUTVRCONVRENVROEINTCONGIEPEIEPIR1—CMIFPIE1—CMIE | CMCONC2OUTC1OUTVRCONVRENVROEVRRINTCONGIEPEIETOIEPIR1CMIFPIE1CMIE | CMCONC2OUTC1OUT—VRCONVRENVROEVRR—INTCONGIEPEIETOIEINTEPIR1—CMIF——PIE1I—CMIEI | CMCONC2OUTC1OUT——CISVRCONVRENVROEVRR—VR3INTCONGIEPEIET0IEINTERBIEPIR1—CMIF———PIE1—CMIE——— | CMCONC2OUTC1OUT——CISCM2VRCONVRENVROEVRR—VR3VR2INTCONGIEPEIETOIEINTERBIETOIFPIR1—CMIF————PIE1—CMIE———— | CMCONC2OUTC1OUT——CISCM2CM1VRCONVRENVROEVRR—VR3VR2VR1INTCONGIEPEIET0IEINTERBIET0IFINTFPIR1—CMIF—————PIE1—CMIE————— | CMCONC2OUTC1OUT——CISCM2CM1CM0VRCONVRENVROEVRR—VR3VR2VR1VR0INTCONGIEPEIETOIEINTERBIETOIFINTFRBIFPIR1—CMIF——————PIE1—CMIE—————— | Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 POR   CMCON C2OUT C1OUT — — CIS CM2 CM1 CM0 00 0000   VRCON VREN VROE VRR — VR3 VR2 VR1 VR0 000- 0000   INTCON GIE PEIE T0IE INTE RBIE T0IF INTF RBIF 0000 000x   PIR1 — CMIE — — — — — - -0 -0   PIE1 — CMIE — — — — — - -0 - |

TABLE 8-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: - = Unimplemented, read as "0", x = Unknown, u = unchanged

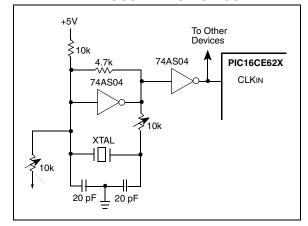

### 10.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

Figure 10-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

### FIGURE 10-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

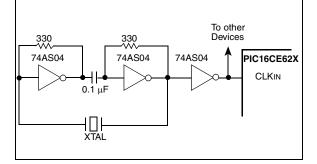

Figure 10-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180° phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 10-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

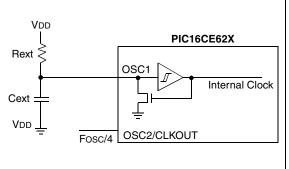

### 10.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-5 shows how the R/C combination is connected to the PIC16CE62X. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (i.e., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 14.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 14.0 for variation of oscillator frequency due to VDD for given Rext/Cext values, as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

# FIGURE 10-5: RC OSCILLATOR MODE

### 10.4.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired, then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no time-out at all. Figure 10-8, Figure 10-9 and Figure 10-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 10-9). This is useful for testing purposes or to synchronize more than one  $\text{PIC}^{\textcircled{B}}$  device operating in parallel.

Table 10-5 shows the reset conditions for some special registers, while Table 10-6 shows the reset conditions for all the registers.

### 10.4.6 POWER CONTROL (PCON)/STATUS REGISTER

The power control/status register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on power-on-reset. It must then be set by the user and checked on subsequent resets to see if  $\overline{\text{BOR}} = 0$  indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on-reset). It is a '0' on power-on-reset and unaffected otherwise. The user must write a '1' to this bit following a power-on-reset. On a subsequent reset, if POR is '0', it will indicate that a power-on-reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-------------------|-----------|-------------------|-----------------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0  | PWRTE = 1 | brown-out neset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             | _         | 72 ms             | —                     |  |

### TABLE 10-3: TIME-OUT IN VARIOUS SITUATIONS

| POR | BOR | TO | PD |                           |

|-----|-----|----|----|---------------------------|

| 0   | Х   | 1  | 1  | Power-on-reset            |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR |

**Brown-out Reset**

WDT Reset

WDT Wake-up

MCLR reset during normal operation

MCLR reset during SLEEP

### TABLE 10-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Х

u

0

u

Ο

Legend: x = unknown, u = unchanged

0

1

1

1

1

Х

0

0

u

1

1

1

1

1

1

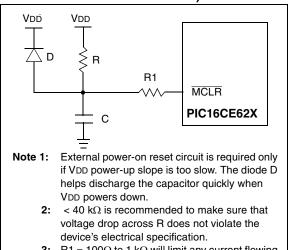

### FIGURE 10-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

**3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

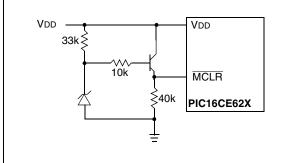

## FIGURE 10-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal Brown-out Reset circuitry should be disabled when using this circuit.

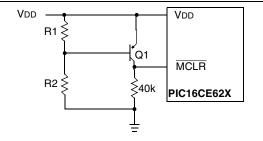

### FIGURE 10-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \times \frac{R1}{R1 + R2} = 0.7 V$$

- **2:** Internal brown-out detection should be disabled when using this circuit.

- **3:** Resistors should be adjusted for the characteristics of the transistor.

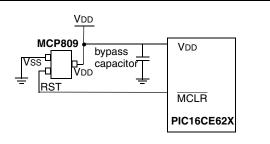

### FIGURE 10-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

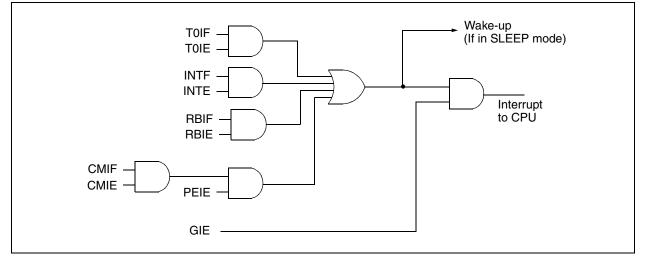

### 10.5 Interrupts

The PIC16CE62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PortB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which re-enable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of

the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends on when the interrupt event occurs (Figure 10-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

### FIGURE 10-15: INTERRUPT LOGIC

| BCF              | Bit Clear                                                          | f             |                        |      |

|------------------|--------------------------------------------------------------------|---------------|------------------------|------|

| Syntax:          | [ <i>label</i> ] B                                                 | CF f,t        | )                      |      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b \leq 7 \end{array}$ | 7             |                        |      |

| Operation:       | $0 \rightarrow (f < b;$                                            | >)            |                        |      |

| Status Affected: | None                                                               |               |                        |      |

| Encoding:        | 01                                                                 | 00bb          | bfff                   | ffff |

| Description:     | Bit 'b' in re                                                      | gister 'f' is | s cleared.             |      |

| Words:           | 1                                                                  |               |                        |      |

| Cycles:          | 1                                                                  |               |                        |      |

| Example          | BCF                                                                | FLAG_         | REG, 7                 |      |

|                  | After Inst                                                         | FLAG_RE       | EG = 0xC7<br>EG = 0x47 |      |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                                        |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                        |  |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                                                                    |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                       |  |  |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                                          |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the next<br>instruction is skipped.<br>If bit 'b' is '0', then the next instruction<br>fetched during the current instruction<br>execution is discarded, and a NOP is<br>executed instead, making this a<br>two-cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                          |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                       |  |  |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                                                                |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                                    |  |  |  |  |

|                  | PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1>=1,<br>PC = address FALSE                                                                                                                                                      |  |  |  |  |

| BSF              | Bit Set f                                                                     |               |        |      |  |

|------------------|-------------------------------------------------------------------------------|---------------|--------|------|--|

| Syntax:          | [ <i>label</i> ] B                                                            | BSF f,b       |        |      |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$           |               |        |      |  |

| Operation:       | $1 \rightarrow (f < b;$                                                       | >)            |        |      |  |

| Status Affected: | None                                                                          |               |        |      |  |

| Encoding:        | 01                                                                            | 01bb          | bfff   | ffff |  |

| Description:     | Bit 'b' in re                                                                 | gister 'f' is | s set. |      |  |

| Words:           | 1                                                                             |               |        |      |  |

| Cycles:          | 1                                                                             |               |        |      |  |

| Example          | BSF                                                                           | FLAG_F        | REG, 7 |      |  |

|                  | Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |               |        |      |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                          |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                    |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                    |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |

| Words:           | 1                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                    |

| Example          | IORWF RESULT, 0                                                                                                                                                      |

|                  | $\begin{array}{rcl} Before \ Instruction \\ RESULT &= & 0x13 \\ W &= & 0x91 \\ After \ Instruction \\ RESULT &= & 0x13 \\ W &= & 0x93 \\ Z &= & 1 \end{array}$       |

| MOVF             | Move f                                                                                                                                                                                                                      |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                            |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                           |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                           |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                           |  |  |  |  |

|                  | to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                           |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                           |  |  |  |  |

| Example          | MOVF FSR, 0                                                                                                                                                                                                                 |  |  |  |  |

|                  | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                     |  |  |  |  |

| MOVLW            | Move Lit                               | eral to V      | V    |      |

|------------------|----------------------------------------|----------------|------|------|

| Syntax:          | [ label ]                              | MOVLW          | / k  |      |

| Operands:        | $0 \le k \le 2\xi$                     | 55             |      |      |

| Operation:       | $k \to (W)$                            |                |      |      |

| Status Affected: | None                                   |                |      |      |

| Encoding:        | 11                                     | 00xx           | kkkk | kkkk |

| Description:     | The eight l<br>register. Th<br>as 0's. |                |      |      |

| Words:           | 1                                      |                |      |      |

| Cycles:          | 1                                      |                |      |      |

| Example          | MOVLW                                  | 0x5A           |      |      |

|                  | After Inst                             | ruction<br>W = | 0x5A |      |

| MOVWF            | Move W to f                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                                                                                                            |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                                                        |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                       |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                          |

| Description:     | Move data from W register to register 'f'.                                                                                                                                                 |

| Words:           | 1                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                          |

| Example          | MOVWF OPTION                                                                                                                                                                               |

|                  | $\begin{array}{rcl} \text{Before Instruction} & & \\ & \text{OPTION} & = & 0xFF \\ W & = & 0x4F \\ \text{After Instruction} & & \\ & \text{OPTION} & = & 0x4F \\ W & = & 0x4F \end{array}$ |

| NOP              | No Oper    | ation |      |      |

|------------------|------------|-------|------|------|

| Syntax:          | [ label ]  | NOP   |      |      |

| Operands:        | None       |       |      |      |

| Operation:       | No opera   | tion  |      |      |

| Status Affected: | None       |       |      |      |

| Encoding:        | 0 0        | 0000  | 0xx0 | 0000 |

| Description:     | No operati | on.   |      |      |

| Words:           | 1          |       |      |      |

| Cycles:          | 1          |       |      |      |

| Example          | NOP        |       |      |      |

| RETFIE           | Return from Ir                                                                                                     | nterrupt                                             |                     |

|------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------|

| Syntax:          | [label] RET                                                                                                        | ΞIE                                                  |                     |

| Operands:        | None                                                                                                               |                                                      |                     |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                            |                                                      |                     |

| Status Affected: | None                                                                                                               |                                                      |                     |

| Encoding:        | 00 000                                                                                                             | 0000                                                 | 1001                |

| Description:     | Return from Inter<br>and Top of Stack<br>the PC. Interrupt<br>setting Global Int<br>GIE (INTCON<7:<br>instruction. | (TOS) is loade<br>s are enabled b<br>errupt Enable b | ed in<br>Py<br>pit, |

| Words:           | 1                                                                                                                  |                                                      |                     |

| Cycles:          | 2                                                                                                                  |                                                      |                     |

| Example          | RETFIE                                                                                                             |                                                      |                     |

|                  | After Interrupt<br>PC =<br>GIE =                                                                                   | TOS<br>1                                             |                     |

| OPTION                                       | Load Option Register                                                                                                                                                                                                                                       |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                      | [label] OPTION                                                                                                                                                                                                                                             |

| Operands:                                    | None                                                                                                                                                                                                                                                       |

| Operation:                                   | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                   |

| Status Affected:                             | None                                                                                                                                                                                                                                                       |

| Encoding:                                    | 00 0000 0110 0010                                                                                                                                                                                                                                          |

| Description:<br>Words:<br>Cycles:<br>Example | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code<br>compatibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly<br>address it.<br>1<br>1 |

|                                              | To maintain upward compatibility<br>with future PIC <sup>®</sup> MCU products, do<br>not use this instruction.                                                                                                                                             |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                   |

| Example          | CALL TABLE ;W contains table<br>;offset value<br>;W now has table<br>value                                                                                                          |

| TABLE            | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |

|                  | RETLW kn ; End of table                                                                                                                                                             |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                      |

|                  | After Instruction<br>W = value of k8                                                                                                                                                |

TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                            | PIC120 | PIC14 | PIC160 | PIC160 | PIC16C | PIC16F | PIC160         | DICI6C | PIC160 | PIC16F8 | PIC16C | DTFDIG | 20712Iq | PIC18C) | 83CX)<br>52CX)<br>54CX) | кхээн | МСВFX | MCP25 |

|------------------------------------------------------------|--------|-------|--------|--------|--------|--------|----------------|--------|--------|---------|--------|--------|---------|---------|-------------------------|-------|-------|-------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment   | >      | >     | >      | >      | >      | >      | >              | >      | >      | >       | >      | >      | >       | >       |                         |       |       |       |

|                                                            |        |       |        |        |        |        |                |        |        |         |        | >      | >       |         |                         |       |       |       |

| MPLAB <sup>®</sup> C18 Compiler                            |        |       |        |        |        |        |                |        |        |         |        |        |         | >       |                         |       |       |       |

| B MPASM/MPLINK                                             | >      | >     | >      | >      | >      | >      | >              | >      | >      | >       | >      | >      | >       | >       | >                       | >     |       |       |

| 2 MPLAB <sup>®</sup> -ICE                                  | >      | >     | >      | >      | >      | **`    | >              | >      | >      | >       | >      | >      | >       | >       |                         |       |       |       |

| PICMASTER/PICMASTER-CE                                     | >      | >     | >      | ~      | >      |        | >              | >      | ~      |         | >      | ~      | ~       |         |                         |       |       |       |

| E ICEPIC™ Low-Cost<br>III In-Circuit Emulator              | `      |       | ~      | >      | >      |        | >              | >      | `      |         | `      |        |         |         |                         |       |       |       |

| MPLAB <sup>®</sup> -ICD In-Circuit<br>Debugger<br>Debugger |        |       |        | *>     |        |        | *              |        |        | >       |        |        |         |         |                         |       |       |       |

| 20 PICSTART®Plus<br>E Low-Cost Universal Dev. Kit          | ~      | >     | ~      | >      | `      | ×**    | ~              | `      | `      | ~       | ~      | >      | `       | `       |                         |       |       |       |

| ସେମ୍ବର MATE® I<br>Universal Programmer<br>ଦ                | >      | >     | >      | >      | >      | **/    | >              | >      | >      | >       | >      | >      | ~       | ~       | >                       | >     |       |       |

| SIMICE                                                     | >      |       | >      |        |        |        |                |        |        |         |        |        |         |         |                         |       |       |       |

| PICDEM-1                                                   |        |       | >      |        | >      |        | ۲ <sup>+</sup> |        | >      |         |        | >      |         |         |                         |       |       |       |

| PICDEM-2                                                   |        |       |        | à      |        |        | <↓<br>↓        |        |        |         |        |        |         | ~       |                         |       |       |       |

| 2 PICDEM-3                                                 |        |       |        |        |        |        |                |        |        |         | ~      |        |         |         |                         |       |       |       |

| PICDEM-14A                                                 |        | >     |        |        |        |        |                |        |        |         |        |        |         |         |                         |       |       |       |

| PICDEM-17                                                  |        |       |        |        |        |        |                |        |        |         |        |        | ~       |         |                         |       |       |       |

| KEELOQ® Evaluation Kit                                     |        |       |        |        |        |        |                |        |        |         |        |        |         |         |                         | `     |       |       |

| KEELOQ Transponder Kit                                     |        |       |        |        |        |        |                |        |        |         |        |        |         |         |                         | >     |       |       |

| microlD™ Programmer's Kit                                  |        |       |        |        |        |        |                |        |        |         |        |        |         |         |                         |       | ~     |       |

| 125 kHz microID Developer's Kit                            |        |       |        |        |        |        |                |        |        |         |        |        |         |         |                         |       | >     |       |

| 25 kHz Anticollision microlD<br>Developer's Kit            |        |       |        |        |        |        |                |        |        |         |        |        |         |         |                         |       | >     |       |

| 13.56 MHz Anticollision microlD<br>Developer's Kit         |        |       |        |        |        |        |                |        |        |         |        |        |         |         |                         |       | >     |       |

| MCP2510 CAN Developer's Kit                                |        |       |        |        |        |        |                |        |        |         |        |        |         |         |                         |       |       | >     |

ğ Contact Microcrip reciniology inc. for availability <sup>†</sup> Development tool is available on select devices.

### 13.3 DC CHARACTERISTICS:

### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended) PIC16LCE62X (Commercial, Industrial)

|       |       |                                | Standard Opera                                       | ating ( | Conditions (u   | Inles | s otherwise stated)                                                                                                |  |  |  |

|-------|-------|--------------------------------|------------------------------------------------------|---------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

|       |       |                                |                                                      |         |                 |       | +85°C for industrial and                                                                                           |  |  |  |

| DC CH | IARAC | TERISTICS                      |                                                      |         | 0°C ≤           | TA≤   | +70°C for commercial and                                                                                           |  |  |  |

|       |       |                                | $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |         |                 |       |                                                                                                                    |  |  |  |

|       |       |                                | Operating voltag                                     | e Vdi   | o range as de   | scrib | ed in DC spec Table 13-1                                                                                           |  |  |  |

| Parm  | Sym   | Characteristic                 | Min                                                  | Typ†    | Max             | Unit  | Conditions                                                                                                         |  |  |  |

| No.   |       |                                |                                                      |         |                 |       |                                                                                                                    |  |  |  |

|       | Vi∟   | Input Low Voltage              |                                                      |         |                 |       |                                                                                                                    |  |  |  |

|       |       | I/O ports                      |                                                      |         |                 |       |                                                                                                                    |  |  |  |

| D030  |       | with TTL buffer                | Vss                                                  | -       | 0.8V<br>0.15Vdd | v     | VDD = 4.5V to 5.5V, Otherwise                                                                                      |  |  |  |

| D031  |       | with Schmitt Trigger input     | Vss                                                  |         | 0.2VDD          | v     |                                                                                                                    |  |  |  |

| D032  |       | MCLR, RA4/T0CKI,OSC1 (in RC    | Vss                                                  | _       | 0.2VDD          | V     | Note1                                                                                                              |  |  |  |

|       |       | mode)                          |                                                      |         |                 | -     |                                                                                                                    |  |  |  |

| D033  |       | OSC1 (in XT and HS)            | Vss                                                  | _       | 0.3VDD          | v     |                                                                                                                    |  |  |  |

|       |       | OSC1 (in LP)                   | Vss                                                  | -       | 0.6Vdd - 1.0    | V     |                                                                                                                    |  |  |  |

|       | Vih   | Input High Voltage             |                                                      |         |                 |       |                                                                                                                    |  |  |  |

|       |       | I/O ports                      |                                                      |         |                 |       |                                                                                                                    |  |  |  |

| D040  |       | with TTL buffer                | 2.0V                                                 | -       | Vdd             | V     | VDD = 4.5V to 5.5V, Otherwise                                                                                      |  |  |  |

|       |       |                                | .25VDD + 0.8V                                        |         | Vdd             |       |                                                                                                                    |  |  |  |

| D041  |       | with Schmitt Trigger input     | 0.8VDD                                               |         | Vdd             |       |                                                                                                                    |  |  |  |

| D042  |       | MCLR RA4/T0CKI                 | 0.8VDD                                               | -       | Vdd             | V     |                                                                                                                    |  |  |  |

| D043  |       | OSC1 (XT, HS and LP)           | 0.7VDD                                               | -       | Vdd             | V     |                                                                                                                    |  |  |  |

| D043A |       | OSC1 (in RC mode)              | 0.9Vdd                                               |         |                 |       | Note1                                                                                                              |  |  |  |

| D070  | IPURB | PORTB weak pull-up current     | 50                                                   | 200     | 400             | μA    | VDD = 5.0V, VPIN = VSS                                                                                             |  |  |  |

|       |       | Input Leakage Current          |                                                      |         |                 |       |                                                                                                                    |  |  |  |

|       | ١L    | (Notes 2, 3)                   |                                                      |         | 110             |       |                                                                                                                    |  |  |  |

| Daca  |       | I/O ports (Except PORTA)       |                                                      |         | ±1.0            | ·     | VSS $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                                                                    |  |  |  |

| D060  |       | PORTA                          | -                                                    | -       | ±0.5            | μA    |                                                                                                                    |  |  |  |

| D061  |       | RA4/T0CKI                      | -                                                    | -       | ±1.0            | μA    |                                                                                                                    |  |  |  |

| D063  |       | OSC1, MCLR                     | -                                                    | -       | ±5.0            | μA    | , ,                                                                                                                |  |  |  |

|       | Vol   | Output Low Voltage             |                                                      |         |                 |       | configuration                                                                                                      |  |  |  |

| D080  | VOL   | I/O ports                      |                                                      | _       | 0.6             | v     | IOL=8.5 mA, VDD=4.5V, -40° to +85°C                                                                                |  |  |  |

| D000  |       |                                | _                                                    | _       | 0.6             | v     | IOL=7.0 mA, VDD=4.5V, +125°C                                                                                       |  |  |  |

| 0002  |       | OSC2/CLKOUT (RC only)          | _                                                    | _       | 0.6             | v     | IOL=7.0 mA, $VDD=4.5V$ , $+125$ C<br>$IOL=1.6$ mA, $VDD=4.5V$ , $-40^{\circ}$ to $+85^{\circ}$ C                   |  |  |  |

| D083  |       | OSCZ/CEROUT (RC OIlly)         | _                                                    | _       | 0.6             | v     | IOL=1.0  IIA,  VDD=4.5  V, -40  IO +83  C<br>$IOL=1.2 \text{ mA}, \text{ VDD}=4.5 \text{ V}, +125^{\circ}\text{C}$ |  |  |  |

|       | Vон   | Output High Voltage (Note 3)   | _                                                    | _       | 0.0             | v     | 10L-1.2 IIIA, VDD-4.3V, +123 C                                                                                     |  |  |  |

| D090  | VOIT  | I/O ports (Except RA4)         | VDD-0.7                                              | _       | _               | v     | IOH=-3.0 mA, VDD=4.5V, -40° to +85°C                                                                               |  |  |  |

| 2000  |       |                                | VDD-0.7<br>VDD-0.7                                   | _       | _               | v     | IOH=-2.5 mA, VDD=4.5V, +125°C                                                                                      |  |  |  |

| D092  |       | OSC2/CLKOUT (RC only)          | VDD-0.7<br>VDD-0.7                                   | _       | _               |       | IOH=-1.3 mA, VDD=4.5V, -40° to +85°C                                                                               |  |  |  |

| DUUL  |       |                                | VDD-0.7<br>VDD-0.7                                   | _       | _               |       | IOH=-1.0 mA, VDD=4.5V, +125°C                                                                                      |  |  |  |

| *D150 | Vod   | Open-Drain High Voltage        |                                                      |         | 8.5             |       | RA4 pin                                                                                                            |  |  |  |

|       |       | Capacitive Loading Specs on    |                                                      |         |                 | -     | 10 <sup></sup>                                                                                                     |  |  |  |

|       |       | Output Pins                    |                                                      |         |                 |       |                                                                                                                    |  |  |  |

| D100  | cosc  | OSC2 pin                       |                                                      |         | 15              | pF    | In XT, HS and LP modes when external                                                                               |  |  |  |