Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce624-04i-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

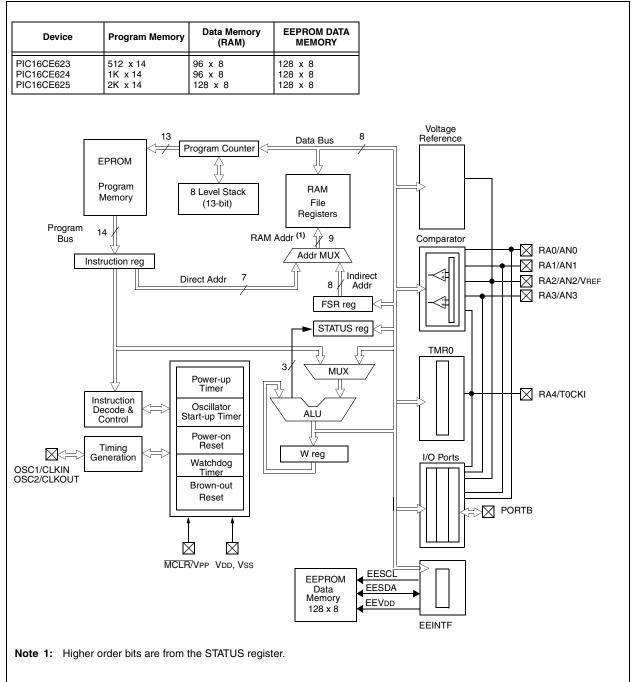

# FIGURE 3-1: BLOCK DIAGRAM

# 4.0 MEMORY ORGANIZATION

## 4.1 <u>Program Memory Organization</u>

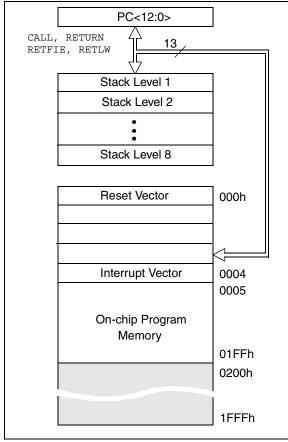

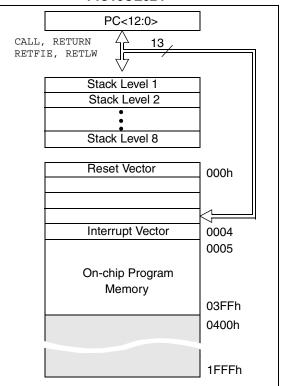

The PIC16CE62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16CE623, 1K x 14 (0000h - 03FFh) for the PIC16CE624 and 2K x 14 (0000h - 07FFh) for the PIC16CE625 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16CE623) or 1K x 14 space (PIC16CE624) or 2K x 14 space (PIC16CE625). The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

## FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE623

## FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE624

### FIGURE 4-3: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE625

## 4.2 Data Memory Organization

The data memory (Figure 4-4 and Figure 4-5) is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-7Fh (Bank0) on the PIC16CE623/624 and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16CE625 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1. In all three microcontrollers, address space F0h-FFh (Bank1) is mapped to 70-7Fh (Bank0) as common RAM.

## 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $96 \times 8$  in the PIC16CE623/624 and 128 x 8 in the PIC16CE625. Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

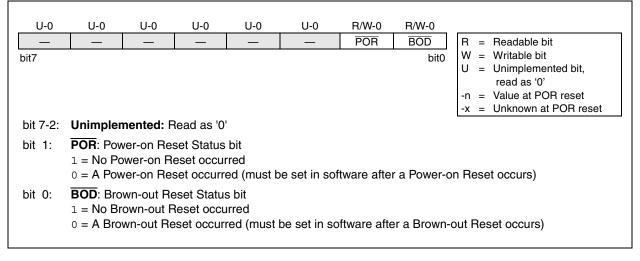

#### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset, an external  $\overline{\text{MCLR}}$  reset, WDT reset or a Brown-out Reset.

| Note: | BOD is unknown on Power-on Reset. It        |

|-------|---------------------------------------------|

|       | must then be set by the user and checked    |

|       | on subsequent resets to see if BOD is       |

|       | cleared, indicating a brown-out has         |

|       | occurred. The BOD status bit is a "don't    |

|       | care" and is not necessarily predictable if |

|       | the brown-out circuit is disabled (by       |

|       | programming BODEN bit in the                |

|       | configuration word).                        |

## REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

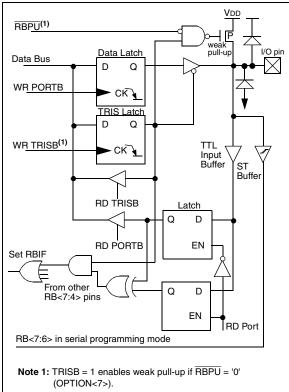

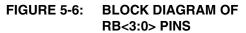

## 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a high impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{RBPU}$  (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins of RB<7:4> are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes".)

| Note: | If a change on the I/O pin should occur       |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|

|       | when the read operation is being executed     |  |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |  |  |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

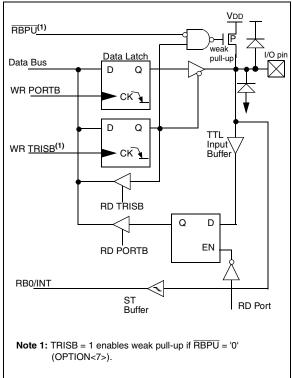

# 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

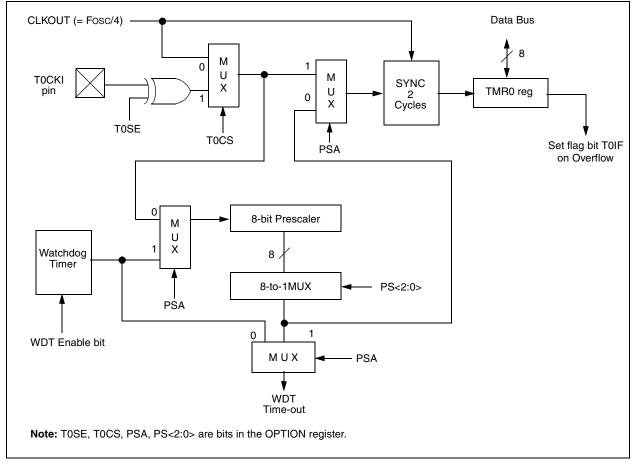

Figure 7-1 is a simplified block diagram of the Timer0 module.

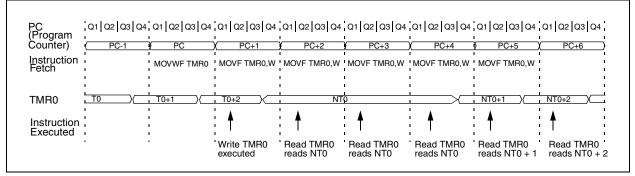

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

## 7.1 <u>Timer0 Interrupt</u>

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

## FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

## 7.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

## 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

## 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

## 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

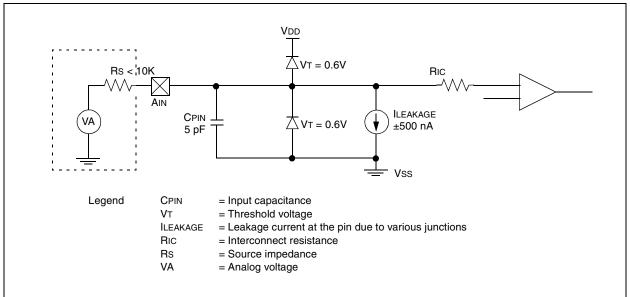

## 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

## FIGURE 8-4: ANALOG INPUT MODEL

## 10.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT), Oscillator Start-up</u> <u>Timer (OST) and Brown-out Reset</u> (BOD)

#### 10.4.1 POWER-ON RESET (POR)

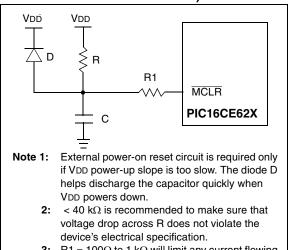

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See electrical specifications for details.

The POR circuit does not produce an internal reset when VDD declines.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 10.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-Up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 10.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on power-on reset or wake-up from SLEEP.

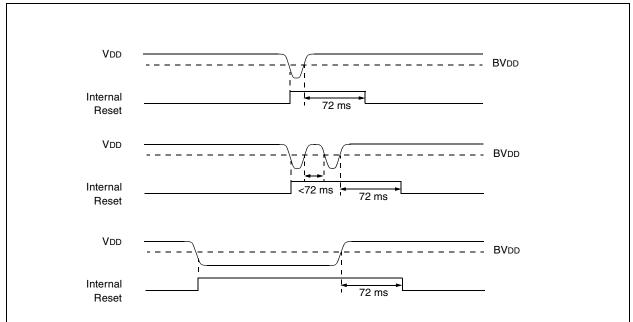

#### 10.4.4 BROWN-OUT RESET (BOD)

The PIC16CE62X members have on-chip Brown-out Reset circuitry. A configuration bit, BOREN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (refer to BVDD parameter D005) for greater than parameter (TBOR) in Table 13-5, the brown-out situation will reset the chip. A reset won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any reset (Power-on, Brown-out, Watch-dog, etc.) the chip will remain in reset until VDD rises above BVDD. The Power-up Timer will then be invoked and will keep the chip in reset an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms reset. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 10-7 shows typical Brown-out situations.

### FIGURE 10-7: BROWN-OUT SITUATIONS

#### 10.4.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired, then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no time-out at all. Figure 10-8, Figure 10-9 and Figure 10-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 10-9). This is useful for testing purposes or to synchronize more than one  $\text{PIC}^{\textcircled{B}}$  device operating in parallel.

Table 10-5 shows the reset conditions for some special registers, while Table 10-6 shows the reset conditions for all the registers.

#### 10.4.6 POWER CONTROL (PCON)/STATUS REGISTER

The power control/status register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on power-on-reset. It must then be set by the user and checked on subsequent resets to see if  $\overline{\text{BOR}} = 0$  indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on-reset). It is a '0' on power-on-reset and unaffected otherwise. The user must write a '1' to this bit following a power-on-reset. On a subsequent reset, if POR is '0', it will indicate that a power-on-reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe                        | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-----------------------------|-----------|-------------------|-----------------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0            | PWRTE = 1 | brown-out neset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc 1024 Tosc |           | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms                       | _         | 72 ms             | —                     |  |

## TABLE 10-3: TIME-OUT IN VARIOUS SITUATIONS

| POR | BOR | TO | PD |                           |

|-----|-----|----|----|---------------------------|

| 0   | Х   | 1  | 1  | Power-on-reset            |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR |

**Brown-out Reset**

WDT Reset

WDT Wake-up

MCLR reset during normal operation

MCLR reset during SLEEP

## TABLE 10-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Х

u

0

u

Ο

Legend: x = unknown, u = unchanged

0

1

1

1

1

Х

0

0

u

1

1

1

1

1

1

## TABLE 10-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set and the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

## TABLE 10-6: INITIALIZATION CONDITION FOR REGISTERS

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | -       | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| INDF     | 00h     | -              | -                                                                                                                                                          | -                                                                                                                 |

| TMR0     | 01h     | XXXX XXXX      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | x000 0000      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | นนนน นนนน                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| EEINTF   | 90h     | 111            | 111                                                                                                                                                        | 111                                                                                                               |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 10-5 for reset value for specific condition.

5: If wake-up was due to comparator input changing , then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

6: If reset was due to brown-out, then PCON bit 0 = 0. All other resets will cause bit 0 = u.

#### FIGURE 10-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

**3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

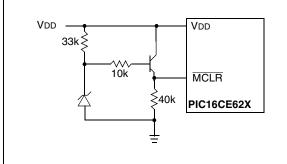

## FIGURE 10-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal Brown-out Reset circuitry should be disabled when using this circuit.

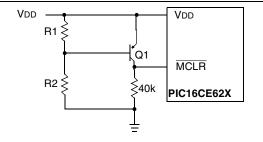

## FIGURE 10-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \times \frac{R1}{R1 + R2} = 0.7 V$$

- **2:** Internal brown-out detection should be disabled when using this circuit.

- **3:** Resistors should be adjusted for the characteristics of the transistor.

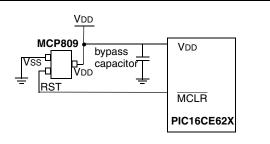

## FIGURE 10-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

#### 10.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit in the STATUS register is cleared, the  $\overline{TO}$  bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSS, with no external circuitry drawing current from the I/O pin, and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated by a WDT time-out does not drive MCLR |  |  |  |  |  |  |

|-------|---------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | by a WDT time-out does not drive MCLR                                           |  |  |  |  |  |  |

|       | pin low.                                                                        |  |  |  |  |  |  |

#### 10.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register can be used to determine the cause of device reset.  $\overline{PD}$ bit, which is set on power-up is cleared when SLEEP is invoked.  $\overline{TO}$  bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

| If the global interrupts are disabled (GIE is |  |  |  |  |  |  |  |

|-----------------------------------------------|--|--|--|--|--|--|--|

| cleared), but any interrupt source has both   |  |  |  |  |  |  |  |

| its interrupt enable bit and the correspond-  |  |  |  |  |  |  |  |

| ing interrupt flag bits set, the device will  |  |  |  |  |  |  |  |

| immediately wake-up from sleep. The           |  |  |  |  |  |  |  |

| sleep instruction is completely executed.     |  |  |  |  |  |  |  |

|                                               |  |  |  |  |  |  |  |

The WDT is cleared when the device wakes-up from sleep, regardless of the source of wake-up.

| Q1 Q2 Q3 Q4 Q1 Q                     | Q2 Q3 Q4 Q1           | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4                           | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 |

|--------------------------------------|-----------------------|--------------|---------------------------------------|------------------|-------------|

|                                      |                       |              |                                       |                  |             |

| CLKOUT(4) \                          |                       | /            |                                       |                  |             |

| INT pin                              |                       |              | · · · · · · · · · · · · · · · · · · · |                  | i           |

| INTF flag<br>(INTCON<1>)             |                       | · · · · ·    | Interrupt Latency                     |                  |             |

| GIE bit<br>(INTCON<7>)               | Processor in<br>SLEEP |              |                                       | י<br>ו<br>ו<br>ו |             |

| INSTRUCTION FLOW                     |                       | · ·          | i I<br>I I                            | 1<br>1           | 1<br>1      |

| PC X PC X F                          | PC+1 X PC+2           | X PC+2       | PC + 2                                | (0004h)          | 0005h       |

| Instruction { Inst(PC) = SLEEP Ins   | st(PC + 1)            | Inst(PC + 2) | 1 I                                   | Inst(0004h)      | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1) | EEP                   | Inst(PC + 1) | Dummy cycle                           | Dummy cycle      | Inst(0004h) |

### FIGURE 10-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**Note 1:** XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay does not occur for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

## 10.9 <u>Code Protection</u>

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip  | does   | not   | recommend | code |

|-------|------------|--------|-------|-----------|------|

|       | protecting | windov | ved d | evices.   |      |

## 10.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. Only the least significant 4 bits of the ID locations are used.

## 10.11 In-Circuit Serial Programming

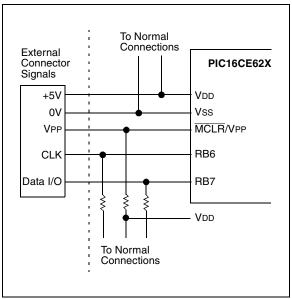

The PIC16CE62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specifications (Literature #DS30228).

A typical in-circuit serial programming connection is shown in Figure 10-20.

### FIGURE 10-20: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

## TABLE 11-2: PIC16CE62X INSTRUCTION SET

| Mnemonic,  |         | Description                  | Cycles |     | 14-Bit Opcode |      |      |          | Notes |  |

|------------|---------|------------------------------|--------|-----|---------------|------|------|----------|-------|--|

| Operands   |         |                              |        | MSb |               | LSb  |      | Affected |       |  |

| BYTE-ORIE  | NTED    | FILE REGISTER OPERATIONS     |        |     |               |      |      |          |       |  |

| ADDWF      | f, d    | Add W and f                  | 1      | 00  | 0111          | dfff | ffff | C,DC,Z   | 1,2   |  |

| ANDWF      | f, d    | AND W with f                 | 1      | 00  | 0101          | dfff | ffff | Z        | 1,2   |  |

| CLRF       | f       | Clear f                      | 1      | 00  | 0001          | lfff | ffff | Z        | 2     |  |

| CLRW       | -       | Clear W                      | 1      | 00  | 0001          | 0000 | 0011 | Z        |       |  |

| COMF       | f, d    | Complement f                 | 1      | 00  | 1001          | dfff | ffff | Z        | 1,2   |  |

| DECF       | f, d    | Decrement f                  | 1      | 00  | 0011          | dfff | ffff | Z        | 1,2   |  |

| DECFSZ     | f, d    | Decrement f, Skip if 0       | 1(2)   | 00  | 1011          | dfff | ffff |          | 1,2,  |  |

| INCF       | f, d    | Increment f                  | 1      | 00  | 1010          | dfff | ffff | Z        | 1,2   |  |

| INCFSZ     | f, d    | Increment f, Skip if 0       | 1(2)   | 00  | 1111          | dfff | ffff |          | 1,2,  |  |

| IORWF      | f, d    | Inclusive OR W with f        | 1      | 00  | 0100          | dfff | ffff | Z        | 1,2   |  |

| MOVF       | f, d    | Move f                       | 1      | 00  | 1000          | dfff | ffff | Z        | 1,2   |  |

| MOVWF      | f       | Move W to f                  | 1      | 00  | 0000          | lfff | ffff |          |       |  |

| NOP        | -       | No Operation                 | 1      | 00  | 0000          | 0xx0 | 0000 |          |       |  |

| RLF        | f, d    | Rotate Left f through Carry  | 1      | 00  | 1101          | dfff | ffff | С        | 1,2   |  |

| RRF        | f, d    | Rotate Right f through Carry | 1      | 00  | 1100          | dfff | ffff | С        | 1,2   |  |

| SUBWF      | f, d    | Subtract W from f            | 1      | 00  | 0010          | dfff | ffff | C,DC,Z   | 1,2   |  |

| SWAPF      | f, d    | Swap nibbles in f            | 1      | 00  | 1110          | dfff | ffff |          | 1,2   |  |

| XORWF      | f, d    | Exclusive OR W with f        | 1      | 00  | 0110          | dfff | ffff | Z        | 1,2   |  |

| BIT-ORIENT | FED FIL | E REGISTER OPERATIONS        |        |     |               |      |      | •        |       |  |

| BCF        | f, b    | Bit Clear f                  | 1      | 01  | 00bb          | bfff | ffff |          | 1,2   |  |

| BSF        | f, b    | Bit Set f                    | 1      | 01  | 01bb          | bfff | ffff |          | 1,2   |  |

| BTFSC      | f, b    | Bit Test f, Skip if Clear    | 1 (2)  | 01  | 10bb          | bfff | ffff |          | 3     |  |

| BTFSS      | f, b    | Bit Test f, Skip if Set      | 1 (2)  | 01  | 11bb          | bfff | ffff |          | 3     |  |

| LITERAL A  | ND CO   | NTROL OPERATIONS             |        |     |               |      |      |          |       |  |

| ADDLW      | k       | Add literal and W            | 1      | 11  | 111x          | kkkk | kkkk | C,DC,Z   |       |  |

| ANDLW      | k       | AND literal with W           | 1      | 11  | 1001          | kkkk | kkkk | Z        |       |  |

| CALL       | k       | Call subroutine              | 2      | 10  | 0kkk          | kkkk | kkkk |          |       |  |

| CLRWDT     | -       | Clear Watchdog Timer         | 1      | 00  | 0000          | 0110 | 0100 | TO,PD    |       |  |

| GOTO       | k       | Go to address                | 2      | 10  | 1kkk          | kkkk | kkkk |          |       |  |

| IORLW      | k       | Inclusive OR literal with W  | 1      | 11  | 1000          | kkkk | kkkk | Z        |       |  |

| MOVLW      | k       | Move literal to W            | 1      | 11  | 00xx          | kkkk | kkkk |          |       |  |

| RETFIE     | -       | Return from interrupt        | 2      | 00  | 0000          | 0000 | 1001 |          |       |  |

| RETLW      | k       | Return with literal in W     | 2      | 11  | 01xx          | kkkk | kkkk |          |       |  |

| RETURN     | -       | Return from Subroutine       | 2      | 00  | 0000          | 0000 | 1000 |          |       |  |

|            | -       | Go into standby mode         | 1      | 00  | 0000          | 0110 | 0011 | TO,PD    |       |  |

| SLEEP      |         |                              |        | 1   |               |      |      |          | 1     |  |

| SUBLW      | k       | Subtract W from literal      | 1      | 11  | 110x          | kkkk | kkkk | C,DC,Z   |       |  |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| BCF              | Bit Clear f                                                         |                         |                        |      |  |  |

|------------------|---------------------------------------------------------------------|-------------------------|------------------------|------|--|--|

| Syntax:          | [ <i>label</i> ] B                                                  | [ <i>label</i> ]BCF f,b |                        |      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |                         |                        |      |  |  |

| Operation:       | $0 \rightarrow (f < b;$                                             | >)                      |                        |      |  |  |

| Status Affected: | None                                                                |                         |                        |      |  |  |

| Encoding:        | 01                                                                  | 00bb                    | bfff                   | ffff |  |  |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |                         |                        |      |  |  |

| Words:           | 1                                                                   |                         |                        |      |  |  |

| Cycles:          | 1                                                                   |                         |                        |      |  |  |

| Example          | BCF                                                                 | FLAG_                   | REG, 7                 |      |  |  |

|                  | After Inst                                                          | FLAG_RE                 | EG = 0xC7<br>EG = 0x47 |      |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                                    |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                                        |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                        |  |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                                                                    |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                       |  |  |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                                          |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the next<br>instruction is skipped.<br>If bit 'b' is '0', then the next instruction<br>fetched during the current instruction<br>execution is discarded, and a NOP is<br>executed instead, making this a<br>two-cycle instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                          |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                       |  |  |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                                                                |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                                    |  |  |  |  |

|                  | PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1>=1,<br>PC = address FALSE                                                                                                                                                      |  |  |  |  |

| BSF              | Bit Set f                                                           |         |                        |  |  |

|------------------|---------------------------------------------------------------------|---------|------------------------|--|--|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |         |                        |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |         |                        |  |  |

| Operation:       | $1 \rightarrow (f < b;$                                             | >)      |                        |  |  |

| Status Affected: | None                                                                |         |                        |  |  |

| Encoding:        | 01 01bb bfff ffff                                                   |         |                        |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |         |                        |  |  |

| Words:           | 1                                                                   |         |                        |  |  |

| Cycles:          | 1                                                                   |         |                        |  |  |

| Example          | BSF                                                                 | FLAG_F  | REG, 7                 |  |  |

|                  | After Inst                                                          | FLAG_RE | EG = 0x0A<br>EG = 0x8A |  |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                       | XORLW                          | Exclusive OR Literal with W                                                               |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                       | Syntax:                        | [ <i>label</i> ] XORLW k                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                       | Operands:                      | 0 ≤ k ≤ 255                                                                               |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>),$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                               | Operation:<br>Status Affected: | (W) .XOR. $k \rightarrow (W)$                                                             |  |  |  |

| Status Affected: | None                                                                                                                                                                    | Encoding:                      | 11 1010 kkkk kkkk                                                                         |  |  |  |

| Encoding:        | 00 1110 dfff ffff                                                                                                                                                       | Description:                   | The contents of the W register are                                                        |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0,<br>the result is placed in W register. If 'd'<br>is 1, the result is placed in register 'f'. | Words:                         | XOR'ed with the eight bit literal 'k'.<br>The result is placed in the<br>W register.<br>1 |  |  |  |

| Words:           | 1                                                                                                                                                                       | Cycles:                        | 1                                                                                         |  |  |  |

| Cycles:          | 1                                                                                                                                                                       | Example:                       | XORLW 0xAF                                                                                |  |  |  |

| Example          | SWAPF REG, 0                                                                                                                                                            |                                | Before Instruction                                                                        |  |  |  |

| ·                | Before Instruction                                                                                                                                                      |                                | W = 0xB5                                                                                  |  |  |  |

|                  | REG1 = 0xA5                                                                                                                                                             |                                | After Instruction                                                                         |  |  |  |

|                  | After Instruction                                                                                                                                                       |                                | W = 0x1A                                                                                  |  |  |  |

|                  | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$                                                                                                             |                                |                                                                                           |  |  |  |

| TRIS                              | Load TRIS Register                                                       |                                       |                                        |              |

|-----------------------------------|--------------------------------------------------------------------------|---------------------------------------|----------------------------------------|--------------|

| Syntax:                           | [ label ]                                                                | TRIS                                  | f                                      |              |

| Operands:                         | $5 \leq f \leq 7$                                                        |                                       |                                        |              |

| Operation:                        | $(W) \rightarrow TF$                                                     | RIS regis                             | ster f;                                |              |

| Status Affected:                  | None                                                                     |                                       |                                        |              |

| Encoding:                         | 0 0                                                                      | 0000                                  | 0110                                   | Offf         |

| Description:<br>Words:<br>Cycles: | The instru-<br>compatibil<br>products.<br>readable a<br>directly ad<br>1 | ity with th<br>Since TR<br>and writab | e PIC16C<br>IS register<br>le, the use | 5X<br>rs are |

| Example                           |                                                                          |                                       |                                        |              |

|                                   |                                                                          | -                                     | rd compa                               | -            |

|                                   | with futu<br>not use t                                                   |                                       | ACU production.                        | ucts, do     |

|                                   |                                                                          |                                       |                                        |              |

|                                   |                                                                          |                                       |                                        |              |

| XORWF            | Exclusive OR W with f                                           |                           |                      |              |  |  |

|------------------|-----------------------------------------------------------------|---------------------------|----------------------|--------------|--|--|

| Syntax:          | [ label ]                                                       | XORWF                     | f,d                  |              |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                           |                      |              |  |  |

| Operation:       | (W) .XOF                                                        | $R.(f) \to (o)$           | dest)                |              |  |  |

| Status Affected: | Z                                                               |                           |                      |              |  |  |

| Encoding:        | 0 0                                                             | 0110                      | dfff                 | f fff        |  |  |

| Description:     |                                                                 | with regis<br>s stored ir | ster 'f'.<br>n the V |              |  |  |

| Words:           | 1                                                               |                           |                      |              |  |  |

| Cycles:          | 1                                                               |                           |                      |              |  |  |

| Example          | XORWF                                                           | REG                       | 1                    |              |  |  |

|                  | Before Instruction                                              |                           |                      |              |  |  |

|                  |                                                                 | REG<br>W                  | =<br>=               | 0xAF<br>0xB5 |  |  |

|                  | After Inst                                                      | ruction                   |                      |              |  |  |

|                  |                                                                 | REG<br>W                  | =<br>=               | 0x1A<br>0xB5 |  |  |

NOTES:

#### 13.2 DC CHARACTERISTICS: F

## PIC16LCE62X-04 (Commercial, Industrial)

| DC CHARACTERISTICS |                     |                                                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |           |                  |                                                                                  |

|--------------------|---------------------|----------------------------------------------------------------|------------------------------------------------------|------|-----------|------------------|----------------------------------------------------------------------------------|

| Param<br>No.       | Sym                 | Characteristic                                                 | Min                                                  | Тур† | Мах       | Units            | Conditions                                                                       |

| D001               | Vdd                 | Supply Voltage                                                 | 2.5                                                  | -    | 5.5       | V                | See Figure 13-1 through Figure 13-3                                              |

| D002               | Vdr                 | RAM Data Retention<br>Voltage (Note 1)                         | -                                                    | 1.5* | -         | V                | Device in SLEEP mode                                                             |

| D003               | VPOR                | VDD start voltage to<br>ensure Power-on Reset                  | -                                                    | Vss  | -         | V                | See section on power-on reset for details                                        |

| D004               | SVDD                | VDD rise rate to ensure<br>Power-on Reset                      | .05*                                                 | -    | -         | V/ms             | See section on power-on reset for details                                        |

| D005               | VBOR                | Brown-out Detect Voltage                                       | 3.7                                                  | 4.0  | 4.35      | V                | BOREN configuration bit is cleared                                               |

| D010               | IDD                 | Supply Current (Note 2)                                        | -                                                    | 1.2  | 2.0       | mA               | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)*                |

|                    |                     |                                                                | -                                                    | -    | 1.1       | mA               | FOSC = 4 MHz, VDD = 2.5V, WDT disabled,                                          |

|                    |                     |                                                                | -                                                    | 35   | 70        | μA               | XT osc mode, (Note 4)<br>Fosc = 32 kHz, VDD = 2.5V, WDT disabled,<br>LP osc mode |

| D020               | IPD                 | Power Down Current (Note 3)                                    | _                                                    | -    | 2.0       | μA               | VDD = 2.5V                                                                       |

|                    |                     |                                                                | -                                                    | -    | 2.2       | μA               | VDD = 3.0V*                                                                      |

|                    |                     |                                                                | -                                                    | -    | 9.0       | μA               | VDD = 5.5V                                                                       |

|                    |                     |                                                                | -                                                    | -    | 15        | μA               | VDD = 5.5V Extended                                                              |

| D022               | $\Delta$ IWDT       | WDT Current (Note 5)                                           | -                                                    | 6.0  | 10        | μA               | VDD=4.0V                                                                         |

| D022A              | $\Delta$ IBOR       | Brown-out Reset Current                                        | _                                                    | 75   | 12<br>125 | μ <b>Α</b><br>μΑ | $(125^{\circ}C)$<br>BOD enabled, VDD = 5.0V                                      |

| D023               |                     | (Note 5)<br>Comparator Current for each<br>Comparator (Note 5) | -                                                    | 30   | 60        | μA               | VDD = 4.0V                                                                       |

| D023A              | $\Delta$ IVREF      | VREF Current (Note 5)                                          | -                                                    | 80   | 135       | μA               | VDD = 4.0V                                                                       |

|                    | $\Delta$ IEE Write  | Operating Current                                              | -                                                    |      | 3         | mA               | Vcc = 5.5V, SCL = 400 kHz                                                        |

|                    | $\Delta IEE \ Read$ | Operating Current                                              | -                                                    |      | 1         | mA               |                                                                                  |

|                    | $\Delta IEE$        | Standby Current                                                | -                                                    |      | 30        | μA               | VCC = 3.0V, EE VDD = VCC                                                         |

|                    | $\Delta IEE$        | Standby Current                                                | -                                                    |      | 100       | μA               | VCC = 3.0V, EE VDD = VCC                                                         |

| 1A                 | Fosc                | LP Oscillator Operating Frequency                              | 0                                                    | —    | 200       | kHz              | All temperatures                                                                 |

|                    |                     | RC Oscillator Operating Frequency                              |                                                      | —    | 4         | MHz              | All temperatures                                                                 |

|                    |                     | XT Oscillator Operating Frequency                              | 0                                                    | —    | 4<br>20   | MHz              | All temperatures                                                                 |

|                    |                     | HS Oscillator Operating Frequency                              | -                                                    |      | 20        | MHz              | All temperatures                                                                 |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

3: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

| Port RB Interrupt                    | 60 |

|--------------------------------------|----|

| PORTA                                |    |

| PORTB                                |    |

| Power Control/Status Register (PCON) | 55 |

| Power-Down Mode (SLEEP)              | 63 |

| Power-On Reset (POR)                 | 54 |

| Power-up Timer (PWRT)                | 54 |

| Prescaler                            |    |

| PRO MATE® II Universal Programmer    | 79 |

| Program Memory Organization          | 11 |

| •                                    |    |

## Q

# R

| 53 |

|----|

| 73 |

| 73 |

| 74 |

| 74 |

| 74 |

|    |

# S

| SEEVAL® Evaluation and Programming System             | 80 |

|-------------------------------------------------------|----|

| Serialized Quick-Turnaround-Production (SQTP) Devices | 5  |

| SLEEP Instruction                                     | 74 |

| Software Simulator (MPLAB-SIM)                        | 78 |

| Special Features of the CPU                           | 49 |

| Special Function Registers                            | 14 |

| Stack                                                 | 20 |

| Status Register                                       | 15 |

| SUBLW Instruction                                     | 75 |

| SUBWF Instruction                                     | 75 |

| SWAPF Instruction                                     | 76 |

#### **T** Timer0

| Timer0                             |

|------------------------------------|

| TIMER0                             |

| TIMER0 (TMR0) Interrupt35          |

| TIMER0 (TMR0) Module               |

| TMR0 with External Clock           |

| Timer1                             |

| Switching Prescaler Assignment     |

| Timing Diagrams and Specifications |

| TMR0 Interrupt                     |

| TRIS Instruction                   |

| TRISA23                            |

| TRISB                              |

| V                                  |

| Voltage Reference Module47         |

| VRCON Register                     |

| W                                  |

| Watchdog Timer (WDT)61             |

| WWW, On-Line Support2              |

| x                                  |

| XORLW Instruction                  |

| XORWF Instruction76                |