Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 18-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce624-20-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | General Description                           | 3     |  |  |  |

|-------|-----------------------------------------------|-------|--|--|--|

| 2.0   | PIC16CE62X Device Varieties                   | 5     |  |  |  |

| 3.0   | Architectural Overview                        |       |  |  |  |

| 4.0   | Memory Organization                           | 11    |  |  |  |

| 5.0   | I/O Ports                                     |       |  |  |  |

| 6.0   | EEPROM Peripheral Operation                   | 29    |  |  |  |

| 7.0   | Timer0 Module                                 |       |  |  |  |

| 8.0   | Comparator Module                             | 41    |  |  |  |

| 9.0   | Voltage Reference Module                      | 47    |  |  |  |

| 10.0  | Special Features of the CPU                   | 49    |  |  |  |

| 11.0  | Instruction Set Summary                       | 65    |  |  |  |

|       | Development Support                           |       |  |  |  |

|       | Electrical Specifications                     |       |  |  |  |

| 14.0  | Packaging Information                         | 97    |  |  |  |

| Appe  | ndix A: Code for Accessing EEPROM Data Memory | 103   |  |  |  |

| Index |                                               | 105   |  |  |  |

| On Li | ne Support                                    | . 107 |  |  |  |

| Read  | On Line Support                               |       |  |  |  |

| PIC1  | 6CE62X Product Identification System          | . 109 |  |  |  |

#### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CE62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CE62X uses a Harvard architecture in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM) and non-volatile memory (EEPROM) for each PIC16CE62X device.

| Device     | Program<br>Memory | RAM<br>Data<br>Memory | EEPROM<br>Data<br>Memory |

|------------|-------------------|-----------------------|--------------------------|

| PIC16CE623 | 512x14            | 96x8                  | 128x8                    |

| PIC16CE624 | 1Kx14             | 96x8                  | 128x8                    |

| PIC16CE625 | 2Kx14             | 128x8                 | 128x8                    |

The PIC16CE62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CE62X family has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CE62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16CE62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

### 4.0 MEMORY ORGANIZATION

### 4.1 <u>Program Memory Organization</u>

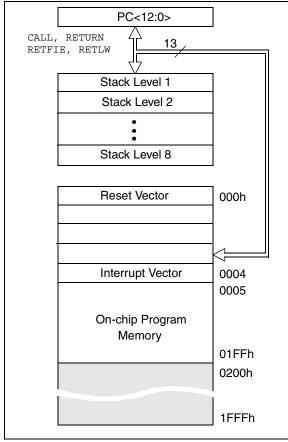

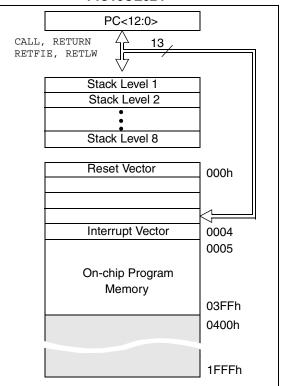

The PIC16CE62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16CE623, 1K x 14 (0000h - 03FFh) for the PIC16CE624 and 2K x 14 (0000h - 07FFh) for the PIC16CE625 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16CE623) or 1K x 14 space (PIC16CE624) or 2K x 14 space (PIC16CE625). The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE623

#### FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE624

#### FIGURE 4-3: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE625

#### 4.2 Data Memory Organization

The data memory (Figure 4-4 and Figure 4-5) is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-7Fh (Bank0) on the PIC16CE623/624 and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16CE625 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1. In all three microcontrollers, address space F0h-FFh (Bank1) is mapped to 70-7Fh (Bank0) as common RAM.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $96 \times 8$  in the PIC16CE623/624 and 128 x 8 in the PIC16CE625. Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

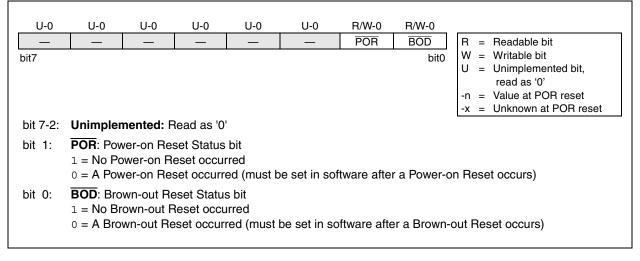

#### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset, an external  $\overline{\text{MCLR}}$  reset, WDT reset or a Brown-out Reset.

| Note: | BOD is unknown on Power-on Reset. It        |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|

|       | must then be set by the user and checked    |  |  |  |  |  |  |  |  |

|       | on subsequent resets to see if BOD is       |  |  |  |  |  |  |  |  |

|       | cleared, indicating a brown-out has         |  |  |  |  |  |  |  |  |

|       | occurred. The BOD status bit is a "don't    |  |  |  |  |  |  |  |  |

|       | care" and is not necessarily predictable if |  |  |  |  |  |  |  |  |

|       | the brown-out circuit is disabled (by       |  |  |  |  |  |  |  |  |

|       | programming BODEN bit in the                |  |  |  |  |  |  |  |  |

|       | configuration word).                        |  |  |  |  |  |  |  |  |

### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

#### 6.2 Device Addressing

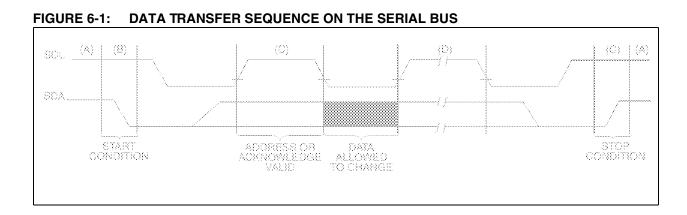

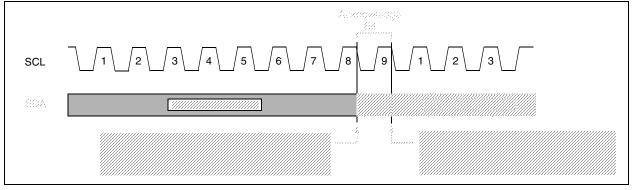

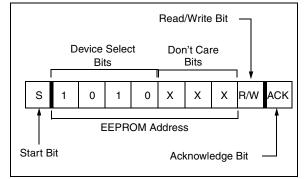

After generating a START condition, the processor transmits a control byte consisting of a EEPROM address and a Read/Write bit that indicates what type of operation is to be performed. The EEPROM address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one, a read operation is selected, and when set to a zero, a write operation is selected. (Figure 6-3). The bus is monitored for its corresponding EEPROM address all the time. It generates an acknowledge bit if the EEPROM address was true and it is not in a programming mode.

#### FIGURE 6-3: CONTROL BYTE FORMAT

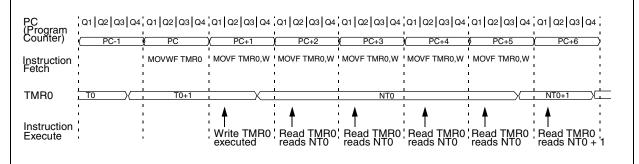

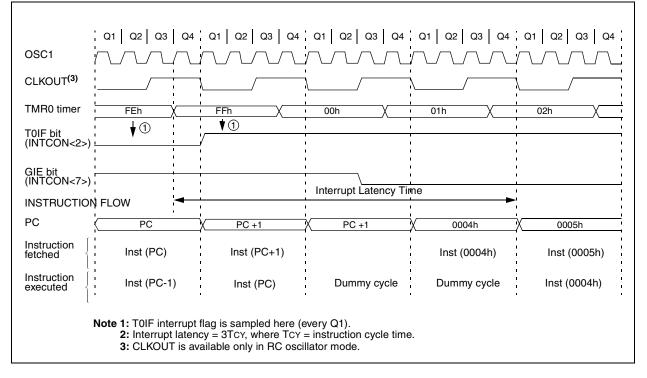

#### FIGURE 7-4: TIMER0 INTERRUPT TIMING

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

## EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| 1.BCF    | STATUS, RPO | ;Skip if already in      |

|----------|-------------|--------------------------|

|          |             | ; Bank 0                 |

| 2.CLRWDT |             | ;Clear WDT               |

| 3.CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| 4.BSF    | STATUS, RPO | ;Bank 1                  |

| 5.MOVLW  | '00101111'b | ;These 3 lines (5, 6, 7) |

| 6.MOVWF  | OPTION      | ; are required only if   |

|          |             | ; desired PS<2:0> are    |

| 7.CLRWDT |             | ; 000 or 001             |

| 8.MOVLW  | '00101xxx'b | ;Set Postscaler to       |

| 9.MOVWF  | OPTION      | ; desired WDT rate       |

| 10.BCF   | STATUS, RPO | ;Return to Bank 0        |

|          |             |                          |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

## EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and<br>;prescaler |

|--------|-------------|------------------------------|

|        |             | /prebearer                   |

| BSF    | STATUS, RPO |                              |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new            |

|        |             | ;prescale value and          |

|        |             | ;clock source                |

| MOVWF  | OPTION_REG  |                              |

| BCF    | STATUS, RPO |                              |

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7  | Bit 6                  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|--------|--------|------------------------|-------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 01h     | TMR0   | Timer0 | Fimer0 module register |       |        |        |        |        |        | xxxx xxxx        | uuuu uuuu                       |

| 0Bh/8Bh | INTCON | GIE    | PEIE                   | T0IE  | INTE   | RBIE   | T0IF   | INTF   | RBIF   | 0000 000x        | 0000 000u                       |

| 81h     | OPTION | RBPU   | INTEDG                 | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111        | 1111 1111                       |

| 85h     | TRISA  |        |                        | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111           | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged.

Note: Shaded bits are not used by TMR0 module.

NOTES:

#### 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs, otherwise the maximum delay of the comparators should be used (Table 13-1).

#### 8.5 <u>Comparator Outputs</u>

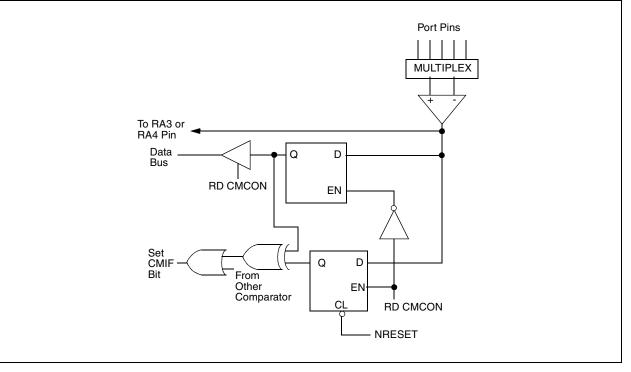

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 8-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 8-3: COMPARATOR OUTPUT BLOCK DIAGRAM

| Name   | Bit 7                                    | Bit 6                                                   | Bit 5                                                       | Bit 4                                                            | Bit 3                                                                        | Bit 2                                                                                     | Bit 1                                                                                                 | Bit 0                                                                                                             | Value on:<br>POR                                                                                                              | Value on<br>All Other<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMCON  | C2OUT                                    | C1OUT                                                   |                                                             | _                                                                | CIS                                                                          | CM2                                                                                       | CM1                                                                                                   | CM0                                                                                                               | 00 0000                                                                                                                       | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VRCON  | VREN                                     | VROE                                                    | VRR                                                         | —                                                                | VR3                                                                          | VR2                                                                                       | VR1                                                                                                   | VR0                                                                                                               | 000- 0000                                                                                                                     | 000- 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTCON | GIE                                      | PEIE                                                    | TOIE                                                        | INTE                                                             | RBIE                                                                         | T0IF                                                                                      | INTF                                                                                                  | RBIF                                                                                                              | 0000 000x                                                                                                                     | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PIR1   | _                                        | CMIF                                                    |                                                             | _                                                                | _                                                                            |                                                                                           | _                                                                                                     | _                                                                                                                 | -0                                                                                                                            | -0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PIE1   | —                                        | CMIE                                                    | —                                                           | —                                                                | —                                                                            | —                                                                                         | —                                                                                                     | —                                                                                                                 | -0                                                                                                                            | -0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TRISA  | —                                        | —                                                       | _                                                           | TRISA4                                                           | TRISA3                                                                       | TRISA2                                                                                    | TRISA1                                                                                                | TRISA0                                                                                                            | 1 1111                                                                                                                        | 1 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | CMCON<br>VRCON<br>INTCON<br>PIR1<br>PIE1 | CMCON C2OUT<br>VRCON VREN<br>INTCON GIE<br>PIR1<br>PIE1 | CMCONC2OUTC1OUTVRCONVRENVROEINTCONGIEPEIEPIR1-CMIFPIE1-CMIE | CMCONC2OUTC1OUTVRCONVRENVROEVRRINTCONGIEPEIETOIEPIR1CMIFPIE1CMIE | CMCONC2OUTC1OUT—VRCONVRENVROEVRR—INTCONGIEPEIETOIEINTEPIR1—CMIF——PIE1I—CMIEI | CMCONC2OUTC1OUT——CISVRCONVRENVROEVRR—VR3INTCONGIEPEIET0IEINTERBIEPIR1—CMIF———PIE1—CMIE——— | CMCONC2OUTC1OUT——CISCM2VRCONVRENVROEVRR—VR3VR2INTCONGIEPEIETOIEINTERBIETOIFPIR1—CMIF————PIE1—CMIE———— | CMCONC2OUTC1OUT——CISCM2CM1VRCONVRENVROEVRR—VR3VR2VR1INTCONGIEPEIET0IEINTERBIET0IFINTFPIR1—CMIF—————PIE1—CMIE————— | CMCONC2OUTC1OUT——CISCM2CM1CM0VRCONVRENVROEVRR—VR3VR2VR1VR0INTCONGIEPEIETOIEINTERBIETOIFINTFRBIFPIR1—CMIF——————PIE1—CMIE—————— | Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         POR           CMCON         C2OUT         C1OUT         —         —         CIS         CM2         CM1         CM0         00 0000           VRCON         VREN         VROE         VRR         —         VR3         VR2         VR1         VR0         000- 0000           INTCON         GIE         PEIE         TOIE         INTE         RBIE         TOIF         INTF         RBIF         0000 000x           PIR1         —         CMIE         —         —         —         —         —         -         -0         -0           PIE1         —         CMIE         —         —         —         —         —         -         -0         - |

TABLE 8-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: - = Unimplemented, read as "0", x = Unknown, u = unchanged

#### 10.9 <u>Code Protection</u>

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

| Note: | Microchip                    | does | not | recommend | code |  |  |  |

|-------|------------------------------|------|-----|-----------|------|--|--|--|

|       | protecting windowed devices. |      |     |           |      |  |  |  |

#### 10.10 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code-identification numbers. These locations are not accessible during normal execution but are readable and writable during program/verify. Only the least significant 4 bits of the ID locations are used.

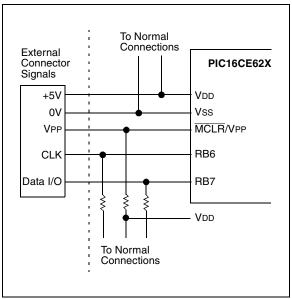

#### 10.11 In-Circuit Serial Programming

The PIC16CE62X microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground, and the programming voltage. This allows customers to manufacture boards with unprogrammed devices, and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a program/verify mode by holding the RB6 and RB7 pins low, while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). RB6 becomes the programming clock and RB7 becomes the programming data. Both RB6 and RB7 are Schmitt Trigger inputs in this mode.

After reset, to place the device into programming/verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending if the command was a load or a read. For complete details of serial programming, please refer to the PIC16C6X/7X/9XX Programming Specifications (Literature #DS30228).

A typical in-circuit serial programming connection is shown in Figure 10-20.

#### FIGURE 10-20: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

### 11.0 INSTRUCTION SET SUMMARY

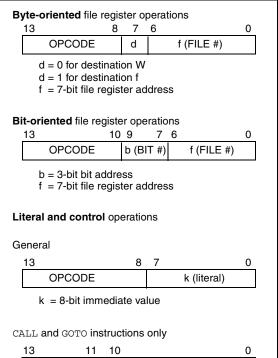

Each PIC16CE62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CE62X instruction set summary in Table 11-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

## TABLE 11-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 11-1 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the three general formats that the instructions can have.

| Note: |      |                        |           | compatibility          |              |

|-------|------|------------------------|-----------|------------------------|--------------|

|       | futu | ire PIC <sup>®</sup> M | ICU produ | ucts, <u>do not us</u> | <u>e</u> the |

|       | OPI  | TION and 1             | rris inst | ructions.              |              |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

## FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

<sup>13

11

10

0</sup> OPCODE

k (literal)

k

11-bit immediate value

<sup>© 1998-2013</sup> Microchip Technology Inc.

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                                                                                   |           |                    |       |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|-------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] B                                                                                                                                                                                                                                                        | TFSS f,b  | )                  |       |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                                                                          |           |                    |       |  |  |  |  |

| Operation:       | skip if (f<                                                                                                                                                                                                                                                               | b>) = 1   |                    |       |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                      |           |                    |       |  |  |  |  |

| Encoding:        | 01                                                                                                                                                                                                                                                                        | 11bb      | bfff               | ffff  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1' then the next<br>instruction is skipped.<br>If bit 'b' is '1', then the next instruction<br>fetched during the current instruction<br>execution, is discarded and a NOP is<br>executed instead, making this a<br>two-cycle instruction. |           |                    |       |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                         |           |                    |       |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                      |           |                    |       |  |  |  |  |

| Example          | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                                     |           | FLAG,1<br>PROCESS_ | _CODE |  |  |  |  |

|                  | Before In                                                                                                                                                                                                                                                                 | struction |                    |       |  |  |  |  |

|                  | PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address FALSE<br>if FLAG<1> = 1,<br>PC = address TRUE                                                                                                                                                   |           |                    |       |  |  |  |  |

| CLRF             | Clear f                                                               |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] CLRF f                                                        |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$                                                     |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |  |  |  |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |  |  |  |

| Encoding:        | 00 0001 1fff fff                                                      |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |  |  |  |  |  |  |

| Words:           | 1                                                                     |  |  |  |  |  |  |

| Cycles:          | 1                                                                     |  |  |  |  |  |  |

| Example          | CLRF FLAG_REG                                                         |  |  |  |  |  |  |

|                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction            |  |  |  |  |  |  |

|                  | $FLAG\_REG = 0x00$ $Z = 1$                                            |  |  |  |  |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                            |  |  |  |  |  |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<4:3>) → PC<12:11>                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                          |  |  |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                             |  |  |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle instruc-<br>tion. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                             |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                             |  |  |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                                               |  |  |  |  |  |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                    |  |  |  |  |  |

| CLRW             | Clear W                                                               |   |  |  |  |

|------------------|-----------------------------------------------------------------------|---|--|--|--|

| Syntax:          | [label] CLRW                                                          |   |  |  |  |

| Operands:        | None                                                                  |   |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |   |  |  |  |

| Status Affected: | Z                                                                     |   |  |  |  |

| Encoding:        | 00 0001 0000 0011                                                     | 1 |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                           | - |  |  |  |

| Words:           | 1                                                                     |   |  |  |  |

| Cycles:          | 1                                                                     |   |  |  |  |

| Example          | CLRW                                                                  |   |  |  |  |

|                  | Before Instruction<br>W = 0x5A                                        |   |  |  |  |

|                  | After Instruction<br>W = 0x00<br>Z = 1                                |   |  |  |  |

$\odot$  1998-2013 Microchip Technology Inc.

NOTES:

#### 13.3 DC CHARACTERISTICS:

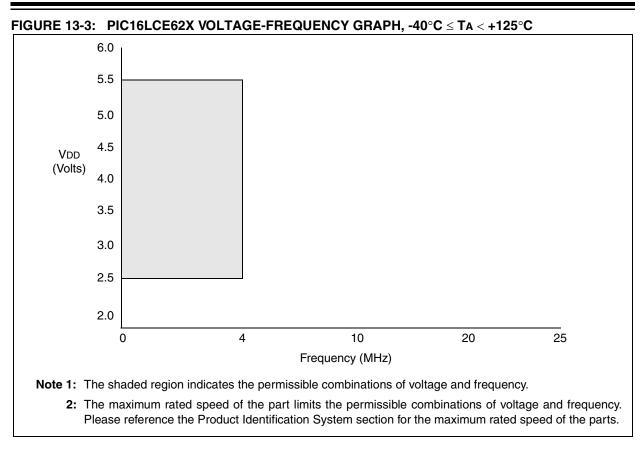

#### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended) PIC16LCE62X (Commercial, Industrial)

|       |       |                                                                | Standard Opera     | ting ( | Conditions (u   | Inles  | s otherwise stated)                                                 |  |  |

|-------|-------|----------------------------------------------------------------|--------------------|--------|-----------------|--------|---------------------------------------------------------------------|--|--|

|       |       |                                                                |                    |        |                 |        | +85°C for industrial and                                            |  |  |

| DC CH | IARAC | TERISTICS                                                      |                    |        | 0°C ≤           | TA≤    | +70°C for commercial and                                            |  |  |

|       |       |                                                                |                    |        |                 |        | +125°C for extended                                                 |  |  |

|       |       | Operating voltage VDD range as described in DC spec Table 13-1 |                    |        |                 |        |                                                                     |  |  |

| Parm  | Sym   | Characteristic                                                 | Min                | Typ†   | Max             | Unit   | Conditions                                                          |  |  |

| No.   |       |                                                                |                    |        |                 |        |                                                                     |  |  |

|       | Vi∟   | Input Low Voltage                                              |                    |        |                 |        |                                                                     |  |  |

|       |       | I/O ports                                                      |                    |        |                 |        |                                                                     |  |  |

| D030  |       | with TTL buffer                                                | Vss                | -      | 0.8V<br>0.15Vdd | v      | VDD = 4.5V to 5.5V, Otherwise                                       |  |  |

| D031  |       | with Schmitt Trigger input                                     | Vss                |        | 0.2VDD          | v      |                                                                     |  |  |

| D032  |       | MCLR, RA4/T0CKI,OSC1 (in RC                                    | Vss                | _      | 0.2VDD          | V      | Note1                                                               |  |  |

|       |       | mode)                                                          |                    |        |                 | -      |                                                                     |  |  |

| D033  |       | OSC1 (in XT and HS)                                            | Vss                | -      | 0.3VDD          | v      |                                                                     |  |  |

|       |       | OSC1 (in LP)                                                   | Vss                | -      | 0.6Vdd - 1.0    | V      |                                                                     |  |  |

|       | Vih   | Input High Voltage                                             |                    |        |                 |        |                                                                     |  |  |

|       |       | I/O ports                                                      |                    |        |                 |        |                                                                     |  |  |

| D040  |       | with TTL buffer                                                | 2.0V               | -      | Vdd             | V      | VDD = 4.5V to 5.5V, Otherwise                                       |  |  |

|       |       |                                                                | .25VDD + 0.8V      |        | Vdd             |        |                                                                     |  |  |

| D041  |       | with Schmitt Trigger input                                     | 0.8VDD             |        | Vdd             |        |                                                                     |  |  |

| D042  |       | MCLR RA4/T0CKI                                                 | 0.8VDD             | -      | Vdd             | V      |                                                                     |  |  |

| D043  |       | OSC1 (XT, HS and LP)                                           | 0.7Vdd             | -      | Vdd             | V      |                                                                     |  |  |

| D043A |       | OSC1 (in RC mode)                                              | 0.9Vdd             |        |                 |        | Note1                                                               |  |  |

| D070  | IPURB | PORTB weak pull-up current                                     | 50                 | 200    | 400             | μA     | VDD = 5.0V, VPIN = VSS                                              |  |  |

|       |       | Input Leakage Current                                          |                    |        |                 |        |                                                                     |  |  |

|       | lı∟   | (Notes 2, 3)                                                   |                    |        |                 |        |                                                                     |  |  |

| Daga  |       | I/O ports (Except PORTA)                                       |                    |        | ±1.0            | ·      | VSS $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                     |  |  |

| D060  |       | PORTA                                                          | -                  | -      | ±0.5            | μA     |                                                                     |  |  |

| D061  |       | RA4/T0CKI                                                      | -                  | -      | ±1.0            | μA     |                                                                     |  |  |

| D063  |       | OSC1, MCLR                                                     | -                  | -      | ±5.0            | μA     | , ,                                                                 |  |  |

|       | Voi   | Output Low Voltage                                             |                    |        |                 |        | configuration                                                       |  |  |

| D080  | Vol   |                                                                |                    | _      | 0.6             | v      |                                                                     |  |  |

| D080  |       | I/O ports                                                      | _                  | -      |                 | V      | IOL=8.5 mA, VDD=4.5V, -40° to +85°C                                 |  |  |

| D000  |       |                                                                | -                  | -      | 0.6             | V      | IOL=7.0 mA, VDD=4.5V, +125°C                                        |  |  |

| D083  |       | OSC2/CLKOUT (RC only)                                          | -                  | _      | 0.6<br>0.6      | V<br>V | IOL=1.6 mA, VDD=4.5V, -40° to +85°C<br>IOL=1.2 mA, VDD=4.5V, +125°C |  |  |

|       | Vон   | Output High Voltage (Note 3)                                   | _                  | _      | 0.0             | v      | IOL=1.2 IIIA, VDD=4.5V, +125 C                                      |  |  |

| D090  | vОп   | I/O ports (Except RA4)                                         | VDD-0.7            | _      | _               | v      | IOH=-3.0 mA, VDD=4.5V, -40° to +85°С                                |  |  |

| 2000  |       |                                                                | VDD-0.7<br>VDD-0.7 |        | _               | v      | IOH=-2.5 mA, VDD=4.5V, +125°C                                       |  |  |

| D092  |       | OSC2/CLKOUT (RC only)                                          | VDD-0.7<br>VDD-0.7 | _      | _               |        | IOH=-1.3 mA, VDD=4.5V, -40° to +85°C                                |  |  |

| 2002  |       |                                                                | VDD-0.7<br>VDD-0.7 | _      | _               |        | IOH=-1.0 mA, VDD=4.5V, -40 IO +85 C                                 |  |  |

| *D150 | Vod   | Open-Drain High Voltage                                        | VDD-0.7            |        | 8.5             |        | RA4 pin                                                             |  |  |

| 2.00  |       | Capacitive Loading Specs on                                    |                    |        | 0.0             |        | ···· · P                                                            |  |  |

|       |       | Output Pins                                                    |                    |        |                 |        |                                                                     |  |  |

| D100  | cosc  | OSC2 pin                                                       |                    |        | 15              | pF     | In XT, HS and LP modes when external                                |  |  |

|       | 2     |                                                                |                    |        |                 |        | clock used to drive OSC1.                                           |  |  |

| D101  | Cio   | All I/O pins/OSC2 (in RC mode)                                 |                    |        | 50              | pF     |                                                                     |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16CE62X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

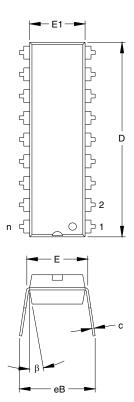

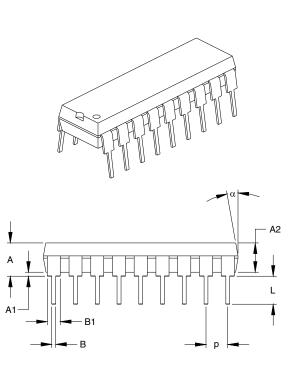

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units     | INCHES* |      |      | MILLIMETERS |       |       |

|----------------------------|-----------|---------|------|------|-------------|-------|-------|

| Dimensio                   | on Limits | MIN     | NOM  | MAX  | MIN         | NOM   | MAX   |

| Number of Pins             | n         |         | 18   |      |             | 18    |       |

| Pitch                      | р         |         | .100 |      |             | 2.54  |       |

| Top to Seating Plane       | Α         | .140    | .155 | .170 | 3.56        | 3.94  | 4.32  |

| Molded Package Thickness   | A2        | .115    | .130 | .145 | 2.92        | 3.30  | 3.68  |

| Base to Seating Plane      | A1        | .015    |      |      | 0.38        |       |       |

| Shoulder to Shoulder Width | Е         | .300    | .313 | .325 | 7.62        | 7.94  | 8.26  |

| Molded Package Width       | E1        | .240    | .250 | .260 | 6.10        | 6.35  | 6.60  |

| Overall Length             | D         | .890    | .898 | .905 | 22.61       | 22.80 | 22.99 |

| Tip to Seating Plane       | L         | .125    | .130 | .135 | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С         | .008    | .012 | .015 | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1        | .045    | .058 | .070 | 1.14        | 1.46  | 1.78  |

| Lower Lead Width           | В         | .014    | .018 | .022 | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing        | eB        | .310    | .370 | .430 | 7.87        | 9.40  | 10.92 |

| Mold Draft Angle Top       | α         | 5       | 10   | 15   | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β         | 5       | 10   | 15   | 5           | 10    | 15    |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001

Drawing No. C04-007

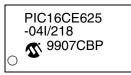

#### 14.1 Package Marking Information

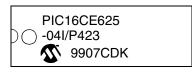

#### **18-Lead PDIP**

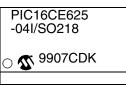

#### 20-Lead SSOP

#### Example

### Example

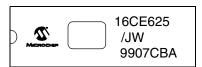

#### Example

#### Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                                     | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Note:  | In the event the full Microchip part number cannot be marked on one line, it will<br>be carried over to the next line, thus limiting the number of available<br>characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

NOTES: