Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                             |

| Supplier Device Package    | 20-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce624-20-ss |

# PIC16CE62X

NOTES:

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CE62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CE62X uses a Harvard architecture in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM) and non-volatile memory (EEPROM) for each PIC16CE62X device.

| Device     | Program<br>Memory | RAM<br>Data<br>Memory | EEPROM<br>Data<br>Memory |

|------------|-------------------|-----------------------|--------------------------|

| PIC16CE623 | 512x14            | 96x8                  | 128x8                    |

| PIC16CE624 | 1Kx14             | 96x8                  | 128x8                    |

| PIC16CE625 | 2Kx14             | 128x8                 | 128x8                    |

The PIC16CE62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CE62X family has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CE62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16CE62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit respectively, bit in subtraction. See the SUBLW and SUBWF instructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

# 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

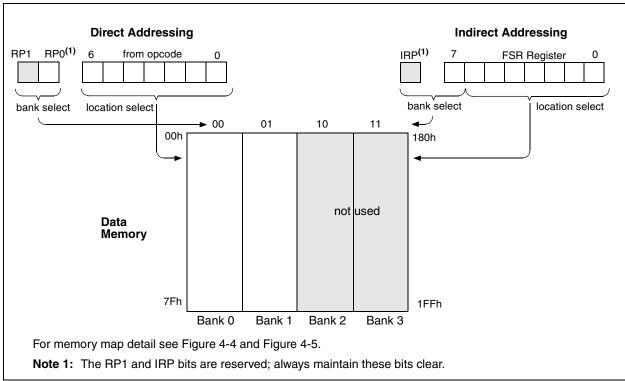

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16CE62X.

A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

#### **EXAMPLE 4-1: INDIRECT ADDRESSING**

movlw 0x20 ;initialize pointer movwf FSR ;to RAM NEXT clrf TNDF ;clear INDF register incf FSR ;inc pointer btfss FSR,4 ;all done? NEXT ;no clear next goto ;yes continue

CONTINUE:

FIGURE 4-7: DIRECT/INDIRECT ADDRESSING PIC16CE62X

### **5.0 I/O PORTS**

The PIC16CE62X parts have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

# 5.1 PORTA and TRISA Registers

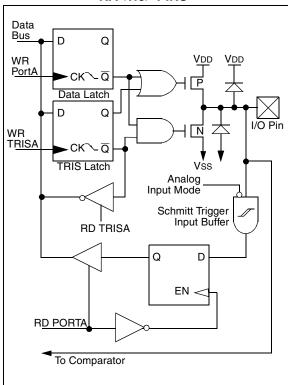

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the TOCKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a hi- impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

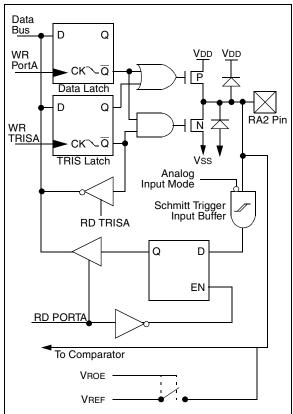

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (Comparator Control Register) register and the VRCON (Voltage Reference Control Register) register. When selected as a comparator input, these pins will read as '0's.

FIGURE 5-1: BLOCK DIAGRAM OF RA<1:0> PINS

On reset, the TRISA register is set to all inputs. The digital inputs are disabled and the comparator inputs are forced to ground to reduce excess current consumption.

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

Note:

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

### **EXAMPLE 5-1: INITIALIZING PORTA**

CLRF PORTA ; Initialize PORTA by setting ;output data latches MOVLW 0X07 ; Turn comparators off and MOVWF CMCON ;enable pins for I/O :functions BSF STATUS, RPO; Select Bank1 MOVIW 0x1F : Value used to initialize :data direction MOVWF TRISA ;Set RA<4:0> as inputs ;TRISA<7:5> are always ;read as '0'.

# FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

# 6.3 Write Operations

#### 6.3.1 BYTE WRITE

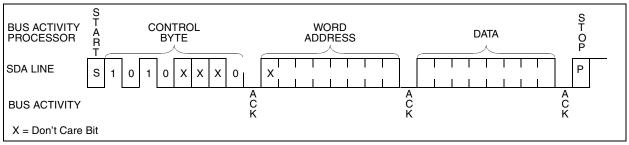

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the R/W bit, which is a logic low, is placed onto the bus by the processor. This indicates to the EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer of the EEPROM. After receiving another acknowledge signal from the EEPROM, the processor will transmit the data word to be written into the addressed memory location. The EEPROM acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time, the EEPROM will not generate acknowledge signals (Figure 6-5).

#### 6.3.2 PAGE WRITE

The write control byte, word address and the first data byte are transmitted to the EEPROM in the same way as in a byte write. But instead of generating a stop condition, the processor transmits up to eight data bytes to the EEPROM, which are temporarily stored in the onchip page buffer and will be written into the memory after the processor has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the processor should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin (Figure 6-6).

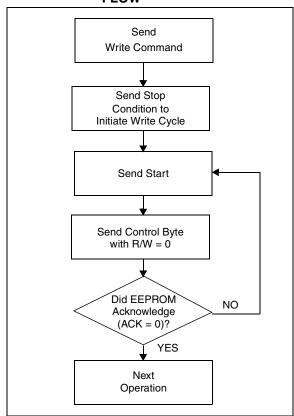

# 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the EEPROM initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/ $\overline{W}$  = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. See Figure 6-4 for flow diagram.

FIGURE 6-4: ACKNOWLEDGE POLLING FLOW

FIGURE 6-5: BYTE WRITE

# 7.0 TIMERO MODULE

The Timer0 module timer/counter has the following features:

- · 8-bit timer/counter

- · Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select

- · Interrupt on overflow from FFh to 00h

- · Edge select for external clock

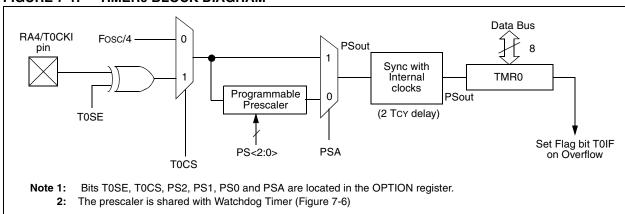

Figure 7-1 is a simplified block diagram of the Timer0 module.

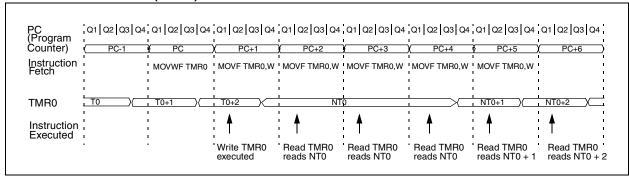

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the ToCS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/ToCKI. The incrementing edge is determined by the source edge (ToSE) control bit (OPTION<4>). Clearing the T0SE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

# 7.1 Timer0 Interrupt

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

### FIGURE 7-1: TIMERO BLOCK DIAGRAM

# FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

# 7.2 <u>Using Timer0 with External Clock</u>

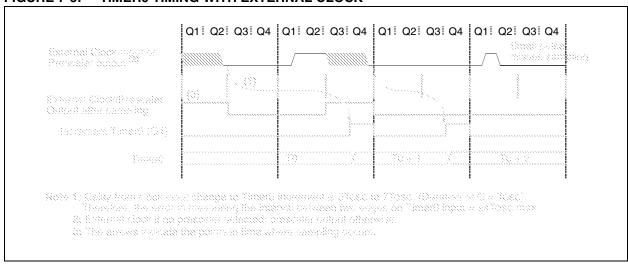

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMERO INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

# 10.2 <u>Oscillator Configurations</u>

#### 10.2.1 OSCILLATOR TYPES

The PIC16CE62X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

LP Low Power CrystalXT Crystal/Resonator

• HS High Speed Crystal/Resonator

• RC Resistor/Capacitor

# 10.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

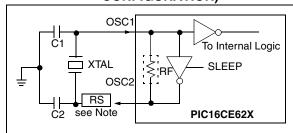

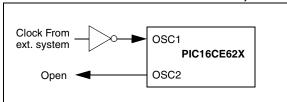

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 10-1). The PIC16CE62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 10-2).

FIGURE 10-1: CRYSTAL OPERATION

(OR CERAMIC RESONATOR)

(HS, XT OR LP OSC

CONFIGURATION)

See Table 10-1 and Table 10-2 for recommended values of C1 and C2.

**Note:** A series resistor may be required for AT strip cut crystals.

FIGURE 10-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

TABLE 10-1: CERAMIC RESONATORS, PIC16CE62X

| Ranges Te | sted:    |             |             |

|-----------|----------|-------------|-------------|

| Mode      | Freq     | OSC1        | OSC2        |

| XT        | 455 kHz  | 68 - 100 pF | 68 - 100 pF |

|           | 2.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |

|           | 4.0 MHz  | 15 - 68 pF  | 15 - 68 pF  |

| HS        | 8.0 MHz  | 10 - 68 pF  | 10 - 68 pF  |

|           | 16.0 MHz | 10 - 22 pF  | 10 - 22 pF  |

These values are for design guidance only. See notes at bottom of page.

TABLE 10-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR, PIC16CE62X

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| XT       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

These values are for design guidance only. See notes at bottom of page.

- Recommended values of C1 and C2 are identical to the ranges tested table.

- 2. Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

# 10.4 Power-on Reset (POR), Power-up Timer (PWRT), Oscillator Start-up Timer (OST) and Brown-out Reset (BOD)

### 10.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See electrical specifications for details.

The POR circuit does not produce an internal reset when VDD declines.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

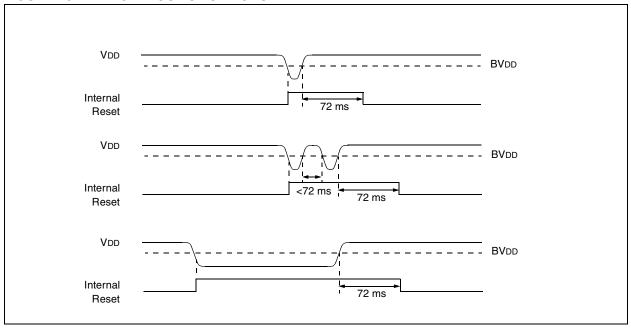

### 10.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-Up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 10.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on power-on reset or wake-up from SLEEP.

### 10.4.4 BROWN-OUT RESET (BOD)

The PIC16CE62X members have on-chip Brown-out Reset circuitry. A configuration bit, BOREN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (refer to BVDD parameter D005) for greater than parameter (TBOR) in Table 13-5, the brown-out situation will reset the chip. A reset won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any reset (Power-on, Brown-out, Watch-dog, etc.) the chip will remain in reset until VDD rises above BVDD. The Power-up Timer will then be invoked and will keep the chip in reset an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms reset. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 10-7 shows typical Brown-out situations.

### 10.4.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired, then OST is activated. The total time-out will vary based on oscillator configuration and PWRTE bit status. For example, in RC mode with PWRTE bit erased (PWRT disabled), there will be no time-out at all. Figure 10-8, Figure 10-9 and Figure 10-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the time-outs will expire. Then bringing MCLR high will begin execution immediately (see Figure 10-9). This is useful for testing purposes or to synchronize more than one PIC® device operating in parallel.

Table 10-5 shows the reset conditions for some special registers, while Table 10-6 shows the reset conditions for all the registers.

# 10.4.6 POWER CONTROL (PCON)/STATUS REGISTER

The power control/status register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{BOR}$  (Brown-out).  $\overline{BOR}$  is unknown on power-on-reset. It must then be set by the user and checked on subsequent resets to see if  $\overline{BOR}=0$  indicating that a brown-out has occurred. The  $\overline{BOR}$  status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is  $\overline{POR}$  (Power-on-reset). It is a '0' on power-on-reset and unaffected otherwise. The user must write a '1' to this bit following a power-on-reset. On a subsequent reset, if  $\overline{POR}$  is '0', it will indicate that a power-on-reset must have occurred (VDD may have gone too low).

TABLE 10-3: TIME-OUT IN VARIOUS SITUATIONS

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up    |

|--------------------------|-------------------|-----------|-------------------|------------|

| Oscillator Configuration | PWRTE = 0         | PWRTE = 1 | Brown-out Heset   | from SLEEP |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc  |

| RC                       | 72 ms             | _         | 72 ms             | _          |

TABLE 10-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

| POR | BOR | TO | PD |                                    |

|-----|-----|----|----|------------------------------------|

| 0   | X   | 1  | 1  | Power-on-reset                     |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR          |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR          |

| 1   | 0   | Х  | Х  | Brown-out Reset                    |

| 1   | 1   | 0  | u  | WDT Reset                          |

| 1   | 1   | 0  | 0  | WDT Wake-up                        |

| 1   | 1   | u  | u  | MCLR reset during normal operation |

| 1   | 1   | 1  | 0  | MCLR reset during SLEEP            |

Legend: x = unknown, u = unchanged

# 11.0 INSTRUCTION SET SUMMARY

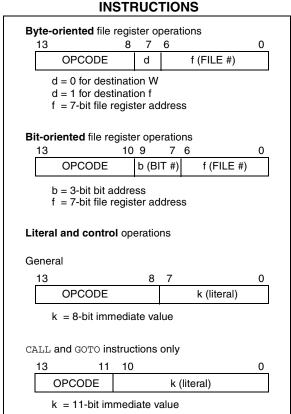

Each PIC16CE62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CE62X instruction set summary in Table 11-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

TABLE 11-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                     |

| W             | Working register (accumulator)                                                                                                                                           |

| b             | Bit address within an 8-bit file register                                                                                                                                |

| k             | Literal field, constant data or label                                                                                                                                    |

| х             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                             |

| label         | Label name                                                                                                                                                               |

| TOS           | Top of Stack                                                                                                                                                             |

| PC            | Program Counter                                                                                                                                                          |

| PCLATH        | Program Counter High Latch                                                                                                                                               |

| GIE           | Global Interrupt Enable bit                                                                                                                                              |

| WDT           | Watchdog Timer/Counter                                                                                                                                                   |

| TO            | Time-out bit                                                                                                                                                             |

| PD            | Power-down bit                                                                                                                                                           |

| dest          | Destination either the W register or the specified register file location                                                                                                |

| []            | Options                                                                                                                                                                  |

| ( )           | Contents                                                                                                                                                                 |

| $\rightarrow$ | Assigned to                                                                                                                                                              |

| <>            | Register bit field                                                                                                                                                       |

| €             | In the set of                                                                                                                                                            |

| italics       | User defined term (font is courier)                                                                                                                                      |

The instruction set is highly orthogonal and is grouped into three basic categories:

- · Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu s$ . If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu s$ .

Table 11-1 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the three general formats that the instructions can have.

**Note:** To maintain upward compatibility with future PIC<sup>®</sup> MCU products, <u>do not use</u> the OPTION and TRIS instructions.

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

| CLRWDT           | Clear Watchdog Timer                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT                                                                                                                                                |

| Operands:        | None                                                                                                                                                          |

| Operation:       | 00h → WDT<br>0 → WDT prescaler,<br>1 → $\overline{\text{TO}}$<br>1 → $\overline{\text{PD}}$                                                                   |

| Status Affected: | TO, PD                                                                                                                                                        |

| Encoding:        | 00 0000 0110 0100                                                                                                                                             |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set. |

| Words:           | 1                                                                                                                                                             |

| Cycles:          | 1                                                                                                                                                             |

| Example          | CLRWDT                                                                                                                                                        |

|                  | Before Instruction  WDT counter = ?  After Instruction                                                                                                        |

|                  | WDT counter = 0x00                                                                                                                                            |

|                  | WDT prescaler= 0                                                                                                                                              |

|                  | <u>TO</u> = 1                                                                                                                                                 |

|                  | PD = 1                                                                                                                                                        |

| DECF             | Decreme                                                 | nt f       |       |                        |            |

|------------------|---------------------------------------------------------|------------|-------|------------------------|------------|

| Syntax:          | [ label ]                                               | DECF f     | ,d    |                        |            |

| Operands:        | $0 \le f \le 12^{n}$ $d \in [0,1]$                      | 7          |       |                        |            |

| Operation:       | $(f) - 1 \rightarrow ($                                 | dest)      |       |                        |            |

| Status Affected: | Z                                                       |            |       |                        |            |

| Encoding:        | 0 0                                                     | 0011       | df:   | ff                     | ffff       |

| Description:     | Decrement<br>result is sto<br>is 1, the re-<br>ter 'f'. | ored in th | e W   | regist                 | er. If 'd' |

| Words:           | 1                                                       |            |       |                        |            |

| Cycles:          | 1                                                       |            |       |                        |            |

| Example          | DECF                                                    | CNT,       | 1     |                        |            |

|                  | After Instr                                             | CNT<br>Z   | = = = | 0x01<br>0<br>0x00<br>1 |            |

| COMF             | Complen                                    | nent f                      |                         |                   |

|------------------|--------------------------------------------|-----------------------------|-------------------------|-------------------|

| Syntax:          | [ label ]                                  | COMF                        | f,d                     |                   |

| Operands:        | $0 \leq f \leq 12$ $d \in [0,1]$           | 7                           |                         |                   |

| Operation:       | $(\overline{f}) \rightarrow (des$          | st)                         |                         |                   |

| Status Affected: | Z                                          |                             |                         |                   |

| Encoding:        | 0.0                                        | 1001                        | dfff                    | ffff              |

| Description:     | The contercompleme stored in V stored back | nted. If 'd<br>V. If 'd' is | ' is 0, th<br>1, the re | ne result is      |

| Words:           | 1                                          |                             |                         |                   |

| Cycles:          | 1                                          |                             |                         |                   |

| Example          | COMF                                       | REG                         | £1,0                    |                   |

|                  | After Inst                                 | REG1                        | = 0:                    | x13<br>x13<br>xEC |

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] DECFSZ f,d                                                                                                                                                                                                                                                                                      |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                        |

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                      |

| Encoding:        | 00 1011 dfff ffff                                                                                                                                                                                                                                                                                         |

| Description:     | The contents of register 'f' are decremented. If 'd' is 0, the result is placed in the W register. If 'd' is 1, the result is placed back in register 'f'. If the result is 0, the next instruction, which is already fetched, is discarded. A NOP is executed instead making it a two-cycle instruction. |

| Words:           | 1                                                                                                                                                                                                                                                                                                         |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                      |

| Example          | HERE DECFSZ CNT, 1 GOTO LOOP CONTINUE  • •                                                                                                                                                                                                                                                                |

|                  | Before Instruction  PC = address HERE  After Instruction  CNT = CNT - 1  if CNT = 0,  PC = address CONTINUE  if CNT \neq 0,                                                                                                                                                                               |

address HERE+1

# 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB® IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER®/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- · In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- · Device Programmers

- PRO MATE® II Universal Programmer

- PICSTART® Plus Entry-Level Prototype Programmer

- · Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ®

# 12.1 <u>MPLAB Integrated Development</u> Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows®-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- · A full featured editor

- A project manager

- · Customizable tool bar and key mapping

- · A status bar

- · On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- · Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

# 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

# 12.3 MPLAB-C17 and MPLAB-C18 C Compilers

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

# PIC16CE62X

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials™ and secure serials. The Total Endurance™ Disk is included to aid in trade-off analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

# 12.18 <u>KEELog Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

**TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP**

| MPLAB® Integrated         /         /           Development Environment         /         /           MPLAB® C17 Compiler         /         /           MPLAB® C18 Compiler         /         /           MPASW/MPLINK         /         /           MPLAB®-ICE         /         /           PICMASTER/PICMASTER-CE         /         / | <b>&gt; &gt;</b> | `<br>`      | d<br>d     | DId | DIG         | PIC | PIC1     | .DIG | PIC1 | PIC1        | 83<br>52<br>54 | нса         | мсв      | МСР |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------|------------|-----|-------------|-----|----------|------|------|-------------|----------------|-------------|----------|-----|

| MPLAB <sup>®</sup> C17 Compiler           MPLAB <sup>®</sup> C18 Compiler           MPASM/MPLINK         ✓           MPLAB <sup>®</sup> -ICE         ✓           PICMASTER/PICMASTER-CE         ✓                                                                                                                                        |                  |             | >          | >   | >           | >   | >        | >    | >    | >           |                |             |          |     |

| MPLAB® C18 Compiler  MPASM/MPLINK  WPLAB®-ICE  MPLABS-ICE  V  V                                                                                                                                                                                                                                                                          |                  |             |            |     |             |     |          | >    | >    |             |                |             |          |     |

| MPLAB®-ICE                                                                                                                                                                                                                                                                                                                               |                  |             |            |     |             |     |          |      |      | >           |                |             |          |     |

| MPLAB®-ICE                                                                                                                                                                                                                                                                                                                               |                  | <i>&gt;</i> | ^          | ^   | >           | >   | >        | >    | >    | >           | >              | >           |          |     |

| PICMASTER/PICMASTER-CE / /                                                                                                                                                                                                                                                                                                               | ^                | **/         | <i>^</i> * | ^   | >           | ^   | ^        | ^    | >    | ^           |                |             |          |     |

|                                                                                                                                                                                                                                                                                                                                          | ^                | ^           | ^          | ^   | >           |     | ^        | ^    | >    |             |                |             |          |     |

| ICEPIC™ Low-Cost /                                                                                                                                                                                                                                                                                                                       | >                | `           | >          | >   | >           |     | >        |      |      |             |                |             |          |     |

| MPLAB <sup>®</sup> -ICD In-Circuit<br>Debugger                                                                                                                                                                                                                                                                                           | *                |             | *          |     |             | >   |          |      |      |             |                |             |          |     |

| PICSTART®Plus Low-Cost Universal Dev. Kit                                                                                                                                                                                                                                                                                                | `                | ** ^        | *          | ,   | >           | >   | >        | >    | >    | >           |                |             |          |     |

| PRO MATE® II                                                                                                                                                                                                                                                                                                                             | · ·              | **/         | *          | ·   | <b>&gt;</b> | >   | <b>,</b> | >    | >    | <b>&gt;</b> | >              | `           |          |     |

| SIMICE                                                                                                                                                                                                                                                                                                                                   |                  |             |            |     |             |     |          |      |      |             |                |             |          |     |

| PICDEM-1                                                                                                                                                                                                                                                                                                                                 |                  | ^           | <b>^</b> ↓ |     | >           |     |          | ^    |      |             |                |             |          |     |

| PICDEM-2                                                                                                                                                                                                                                                                                                                                 | <b>↑</b>         |             | ✓          |     |             |     |          |      |      | ^           |                |             |          |     |

| PICDEM-3                                                                                                                                                                                                                                                                                                                                 |                  |             |            |     |             |     | `        |      |      |             |                |             |          |     |

| PICDEM-14A                                                                                                                                                                                                                                                                                                                               |                  |             |            |     |             |     |          |      |      |             |                |             |          |     |

| PICDEM-17                                                                                                                                                                                                                                                                                                                                |                  |             |            |     |             |     |          |      | `    |             |                |             |          |     |

| KEELOQ® Evaluation Kit                                                                                                                                                                                                                                                                                                                   |                  |             |            |     |             |     |          |      |      |             |                | <i>&gt;</i> |          |     |

| KEELog Transponder Kit                                                                                                                                                                                                                                                                                                                   |                  |             |            |     |             |     |          |      |      |             |                | >           |          |     |

| microID <sup>TM</sup> Programmer's Kit                                                                                                                                                                                                                                                                                                   |                  |             |            |     |             |     |          |      |      |             |                |             | >        |     |

| 125 kHz microID Developer's Kit                                                                                                                                                                                                                                                                                                          |                  |             |            |     |             |     |          |      |      |             |                |             | ^        |     |

| 125 kHz Anticollision microlD<br>Developer's Kit                                                                                                                                                                                                                                                                                         |                  |             |            |     |             |     |          |      |      |             |                |             | >        |     |

| 13.56 MHz Anticollision microlD<br>Developer's Kit                                                                                                                                                                                                                                                                                       |                  |             |            |     |             |     |          |      |      |             |                |             | <b>,</b> |     |

| MCP2510 CAN Developer's Kit                                                                                                                                                                                                                                                                                                              |                  |             |            |     |             |     |          |      |      |             |                |             |          | ^   |

# 13.5 <u>Timing Diagrams and Specifications</u>

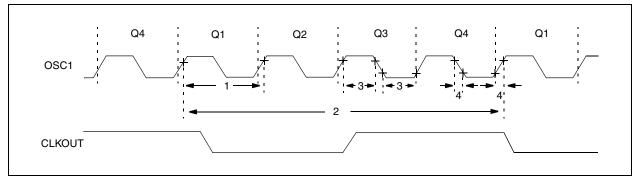

FIGURE 13-5: EXTERNAL CLOCK TIMING

TABLE 13-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter No. | Sym   | Characteristic                   | Min  | Typ† | Max    | Units | Conditions                         |

|---------------|-------|----------------------------------|------|------|--------|-------|------------------------------------|

| 1A            | Fosc  | External CLKIN Frequency         | DC   | _    | 4      | MHz   | XT and RC osc mode, VDD=5.0V       |

|               |       | (Note 1)                         | DC   | _    | 20     | MHz   | HS osc mode                        |

|               |       |                                  | DC   | _    | 200    | kHz   | LP osc mode                        |

|               |       | Oscillator Frequency             | DC   | _    | 4      | MHz   | RC osc mode, VDD=5.0V              |

|               |       | (Note 1)                         | 0.1  | _    | 4      | MHz   | XT osc mode                        |

|               |       |                                  | 1    | _    | 20     | MHz   | HS osc mode                        |

|               |       |                                  | DC   | _    | 200    | kHz   | LP osc mode                        |

| 1             | Tosc  | External CLKIN Period            | 250  | _    | _      | ns    | XT and RC osc mode                 |

|               |       | (Note 1)                         | 50   | _    | _      | ns    | HS osc mode                        |

|               |       |                                  | 5    | _    | _      | μS    | LP osc mode                        |

|               |       | Oscillator Period                | 250  | _    | _      | ns    | RC osc mode                        |

|               |       | (Note 1)                         | 250  | _    | 10,000 | ns    | XT osc mode                        |

|               |       |                                  | 50   | _    | 1,000  | ns    | HS osc mode                        |

|               |       |                                  | 5    | _    | _      | μS    | LP osc mode                        |

| 2             | Tcy   | Instruction Cycle Time (Note 1)  | 200  | _    | DC     | ns    | Tcy=Fosc/4                         |

| 3*            | TosL, | External Clock in (OSC1) High or | 100* | _    | _      | ns    | XT oscillator, Tosc L/H duty cycle |

|               | TosH  | Low Time                         | 2*   | _    | _      | μS    | LP oscillator, Tosc L/H duty cycle |

|               |       |                                  | 20*  | _    | _      | ns    | HS oscillator, Tosc L/H duty cycle |

| 4*            | TosR, | External Clock in (OSC1) Rise or | 25*  |      |        | ns    | XT oscillator                      |

|               | TosF  | Fall Time                        | 50*  | _    | _      | ns    | LP oscillator                      |

|               |       |                                  | 15*  | _    | _      | ns    | HS oscillator                      |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# 13.6 **EEPROM Timing**

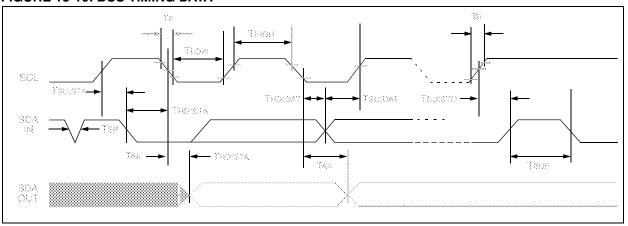

# **FIGURE 13-10: BUS TIMING DATA**

**TABLE 13-7: AC CHARACTERISTICS**

| Parameter                                         | Symbol  | STANDARD<br>MODE |      | Vcc = 4.5 - 5.5V<br>FAST MODE |      | Units  | Remarks                                                       |

|---------------------------------------------------|---------|------------------|------|-------------------------------|------|--------|---------------------------------------------------------------|

|                                                   |         | Min.             | Max. | Min.                          | Max. |        |                                                               |

| Clock frequency                                   | FCLK    | _                | 100  | _                             | 400  | kHz    |                                                               |

| Clock high time                                   | THIGH   | 4000             | _    | 600                           | _    | ns     |                                                               |

| Clock low time                                    | TLOW    | 4700             | _    | 1300                          | _    | ns     |                                                               |

| SDA and SCL rise time                             | TR      | _                | 1000 | _                             | 300  | ns     | (Note 1)                                                      |

| SDA and SCL fall time                             | TF      | _                | 300  | _                             | 300  | ns     | (Note 1)                                                      |

| START condition hold time                         | THD:STA | 4000             | _    | 600                           | _    | ns     | After this period the first clock pulse is generated          |

| START condition setup time                        | Tsu:sta | 4700             | _    | 600                           | _    | ns     | Only relevant for repeated START condition                    |

| Data input hold time                              | THD:DAT | 0                | _    | 0                             | _    | ns     | (Note 2)                                                      |

| Data input setup time                             | TSU:DAT | 250              | _    | 100                           | _    | ns     |                                                               |

| STOP condition setup time                         | Tsu:sto | 4000             | _    | 600                           | —    | ns     |                                                               |

| Output valid from clock                           | TAA     | _                | 3500 | _                             | 900  | ns     | (Note 2)                                                      |

| Bus free time                                     | TBUF    | 4700             | _    | 1300                          | _    | ns     | Time the bus must be free before a new transmission can start |

| Output fall time from VIH minimum to VIL maximum  | TOF     | _                | 250  | 20 + 0.1<br>CB                | 250  | ns     | (Note 1), CB ≤ 100 pF                                         |

| Input filter spike suppression (SDA and SCL pins) | TSP     | _                | 50   |                               | 50   | ns     | (Note 3)                                                      |

| Write cycle time                                  | Twr     | _                | 10   | _                             | 10   | ms     | Byte or Page mode                                             |

| Endurance                                         | _       | 10M<br>1M        | _    | 10M<br>1M                     | _    | cycles | 25°C, VCC = 5.0V, Block<br>Mode (Note 4)                      |

- Note 1: Not 100% tested. CB = total capacitance of one bus line in pF.

- 2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

- 3: The combined TSP and VHYS specifications are due to new Schmitt trigger inputs which provide improved noise spike suppression. This eliminates the need for a TI specification for standard operation.

- 4: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be obtained on our website.

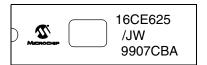

# 14.1 Package Marking Information

### 18-Lead PDIP

# 18-Lead SOIC (.300")

# 18-Lead CERDIP Windowed

### 20-Lead SSOP

# Example

### **Example**

### **Example**

### **Example**

Legend: XX...X Customer-specific information

Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

By-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (a)

can be found on the outer packaging for this package.

In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

Note:

# PIC16CE62X

| Port RB Interrupt                                              |     |

|----------------------------------------------------------------|-----|

| PORTA                                                          | 23  |

| PORTB                                                          |     |

| Power Control/Status Register (PCON)                           | 55  |

| Power-Down Mode (SLEEP)                                        | 63  |

| Power-On Reset (POR)                                           |     |

| Power-up Timer (PWRT)                                          |     |

| Prescaler                                                      |     |

| PRO MATE® II Universal Programmer                              |     |

| Program Memory Organization                                    |     |

|                                                                | 11  |

| Q                                                              |     |

| Quick-Turnaround-Production (QTP) Devices                      | 5   |

| R                                                              |     |

|                                                                |     |

| RC Oscillator                                                  | -   |

| Reset                                                          | 53  |

| RETFIE Instruction                                             | 73  |

| RETLW Instruction                                              | 73  |

| RETURN Instruction                                             | 74  |

| RLF Instruction                                                |     |

| RRF Instruction                                                |     |

| S                                                              |     |

|                                                                |     |

| SEEVAL® Evaluation and Programming System                      |     |

| $Serialized\ Quick-Turn around-Production\ (SQTP)\ Devices\ .$ |     |

| SLEEP Instruction                                              |     |

| Software Simulator (MPLAB-SIM)                                 | 78  |

| Special Features of the CPU                                    | 49  |

| Special Function Registers                                     | 14  |

| Stack                                                          |     |

| Status Register                                                | 15  |

| SUBLW Instruction                                              |     |

| SUBWF Instruction                                              |     |

| SWAPF Instruction                                              |     |

|                                                                | , 0 |

| Т                                                              |     |

| Timer0                                                         |     |

| TIMER0                                                         | 35  |

| TIMER0 (TMR0) Interrupt                                        | 35  |

| TIMER0 (TMR0) Module                                           |     |

| TMR0 with External Clock                                       |     |

| Timer1                                                         |     |

| Switching Prescaler Assignment                                 | 39  |

| Timing Diagrams and Specifications                             |     |

| TMR0 Interrupt                                                 |     |

| TRIS Instruction                                               |     |

| TRISA                                                          |     |

|                                                                |     |

| TRISB                                                          | 26  |

| V                                                              |     |

| Voltage Reference Module                                       | 47  |

| VRCON Register                                                 |     |

| -                                                              | ••  |

| W                                                              |     |

| Watchdog Timer (WDT)                                           |     |

| WWW, On-Line Support                                           | 2   |

| X                                                              |     |

| XORLW Instruction                                              | 76  |

| YORWE Instruction                                              | 76  |