Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                             |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 96 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce624t-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

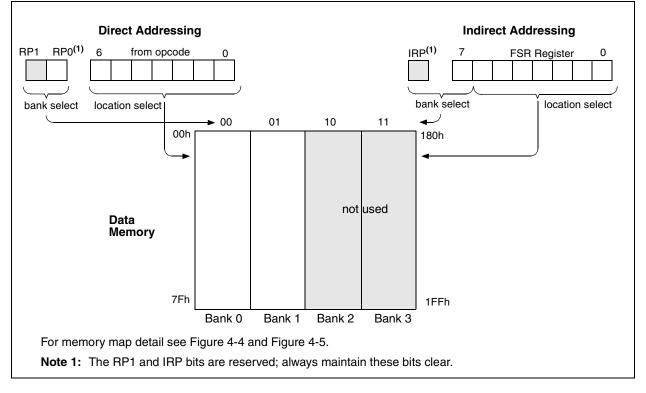

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16CE62X. A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

| EXAMPL    | E 4-1: | INDIRECT ADDRESSING |                      |  |  |  |

|-----------|--------|---------------------|----------------------|--|--|--|

|           | movlw  | 0x20                | ;initialize pointer  |  |  |  |

|           | movwf  | FSR                 | ;to RAM              |  |  |  |

| NEXT      | clrf   | INDF                | clear INDF register; |  |  |  |

|           | incf   | FSR                 | ;inc pointer         |  |  |  |

|           | btfss  | FSR,4               | ;all done?           |  |  |  |

|           | goto   | NEXT                | ;no clear next       |  |  |  |

|           |        |                     | ;yes continue        |  |  |  |

| CONTINUE: |        |                     |                      |  |  |  |

### FIGURE 4-7: DIRECT/INDIRECT ADDRESSING PIC16CE62X

# 5.0 I/O PORTS

The PIC16CE62X parts have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

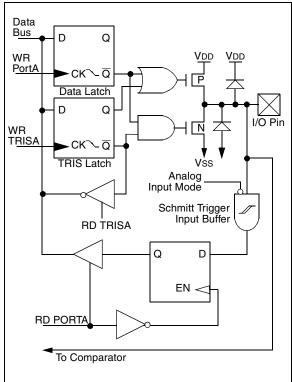

## 5.1 PORTA and TRISA Registers

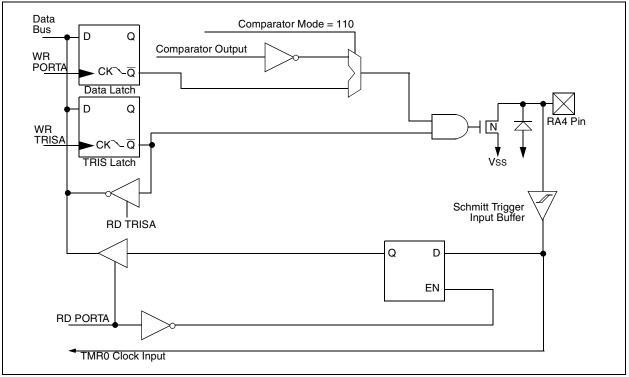

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the TOCKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a hi- impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (Comparator Control Register) register and the VRCON (Voltage Reference Control Register) register. When selected as a comparator input, these pins will read as '0's.

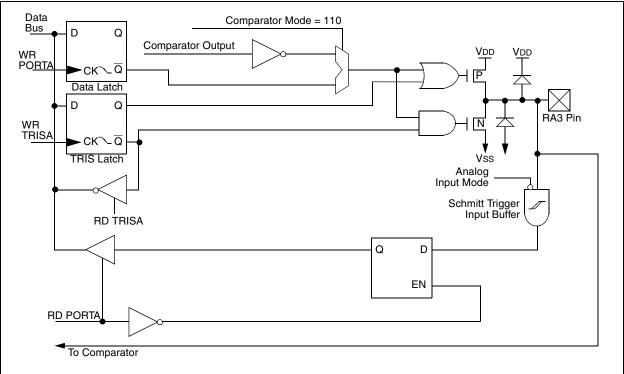

#### FIGURE 5-1: BLOCK DIAGRAM OF RA<1:0> PINS

| Note: | On reset, the TRISA register is set to all  |  |  |

|-------|---------------------------------------------|--|--|

|       | inputs. The digital inputs are disabled and |  |  |

|       | the comparator inputs are forced to ground  |  |  |

|       | to reduce excess current consumption.       |  |  |

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

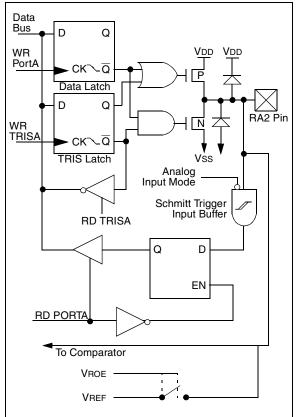

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### **EXAMPLE 5-1: INITIALIZING PORTA**

| CLRF  | PORTA   |     | ;Initialize PORTA by setting ;output data latches |

|-------|---------|-----|---------------------------------------------------|

| MOVLW | 0X07    |     | ;Turn comparators off and                         |

| MOVWF | CMCON   |     | ;enable pins for I/O                              |

|       |         |     | ;functions                                        |

| BSF   | STATUS, | RP0 | ;Select Bank1                                     |

| MOVLW | 0x1F    |     | ;Value used to initialize                         |

|       |         |     | ;data direction                                   |

| MOVWF | TRISA   |     | ;Set RA<4:0> as inputs                            |

|       |         |     | ;TRISA<7:5> are always                            |

|       |         |     | ;read as '0'.                                     |

#### FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

<sup>© 1998-2013</sup> Microchip Technology Inc.

## 6.0 EEPROM PERIPHERAL OPERATION

The PIC16CE623/624/625 each have 128 bytes of EEPROM data memory. The EEPROM data memory supports a bi-directional, 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), and are mapped to bit1 and bit2, respectively, of the EEINTF register (SFR 90h). In addition, the power to the EEPROM can be controlled using bit0 (EEVDD) of the EEINTF register. For most applications, all that is required is calls to the following functions:

| ;<br>;<br>; | Byte_Write: Byte write routine<br>Inputs: EEPROM Address EEADDR<br>EEPROM Data EEDATA |

|-------------|---------------------------------------------------------------------------------------|

| ;           | Outputs: Return 01 in W if OK, else                                                   |

| ΄.          | return 00 in W                                                                        |

| '           |                                                                                       |

| i           | - · · · · · · · · · · · · · · · · · · ·                                               |

| ;           | Read_Current: Read EEPROM at address                                                  |

| C١          | urrently held by EE device.                                                           |

| ;           | Inputs: NONE                                                                          |

| ;           | Outputs: EEPROM Data EEDATA                                                           |

| ;           | Return 01 in W if OK, else                                                            |

| ;           | return 00 in W                                                                        |

| ;           |                                                                                       |

| ;           | Read Random: Read EEPROM byte at supplied                                             |

| ;           | address                                                                               |

| ;           | Inputs: EEPROM Address EEADDR                                                         |

| ;           | Outputs: EEPROM Data EEDATA                                                           |

| ;           | Return 01 in W if OK,                                                                 |

|             | else return 00 in W                                                                   |

| '           |                                                                                       |

The code for these functions is available on our web site (www.microchip.com). The code will be accessed by either including the source code FL62XINC.ASM or by linking FLASH62X.ASM. FLASH62.IMC provides external definition to the calling program.

#### 6.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the memory.

For normal data transfer, SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

#### 6.0.2 SERIAL CLOCK

This SCL input is used to synchronize the data transfer to and from the memory.

#### 6.0.3 EEINTF REGISTER

The EEINTF register (SFR 90h) controls the access to the EEPROM. Register 6-1 details the function of each bit. User code must generate the clock and data signals.

### REGISTER 6-1: EEINTF REGISTER (ADDRESS 90h)

| U-0              | U-0                                                                                                                                                                     | U-0       | U-0         | U-0 | R/W-1 | R/W-1 | R/W-1 |                                                                                       |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------|-----|-------|-------|-------|---------------------------------------------------------------------------------------|

|                  | _                                                                                                                                                                       | _         | _           | _   | EESCL | EESDA | EEVDD | R = Readable bit                                                                      |

| bit7<br>bit 7-3: | Unimpler                                                                                                                                                                | nented: F | lead as '0' |     |       |       | bit0  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 2:           | EESCL: Clock line to the EEPROM<br>1 = Clock high<br>0 = Clock low                                                                                                      |           |             |     |       |       |       |                                                                                       |

| bit 1:           | EESDA: Data line to EEPROM<br>1 = Data line is high (pin is tri-stated, line is pulled high by a pull-up resistor)<br>0 = Data line is low                              |           |             |     |       |       |       |                                                                                       |

| bit 0:           | <b>EEVDD</b> : VDD control bit for EEPROM<br>1 = VDD is turned on to EEPROM<br>0 = VDD is turned off to EEPROM (all pins are tri-stated and the EEPROM is powered down) |           |             |     |       |       |       |                                                                                       |

| Note:            | EESDA, EESCL and EEVDD will read '0' if EEVDD is turned off.                                                                                                            |           |             |     |       |       |       |                                                                                       |

#### 6.3 Write Operations

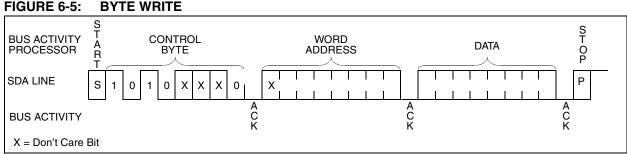

#### BYTE WRITE 6.3.1

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the R/W bit, which is a logic low, is placed onto the bus by the processor. This indicates to the EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer of the EEPROM. After receiving another acknowledge signal from the EEPROM, the processor will transmit the data word to be written into the addressed memory location. The EEPROM acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time, the EEPROM will not generate acknowledge signals (Figure 6-5).

#### 6.3.2 PAGE WRITE

The write control byte, word address and the first data byte are transmitted to the EEPROM in the same way as in a byte write. But instead of generating a stop condition, the processor transmits up to eight data bytes to the EEPROM, which are temporarily stored in the onchip page buffer and will be written into the memory after the processor has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the processor should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin (Figure 6-6).

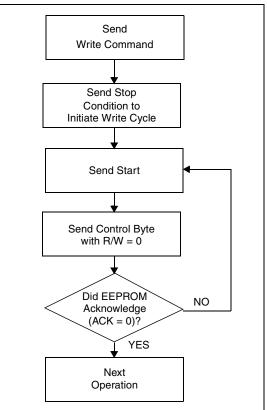

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the EEPROM initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. See Figure 6-4 for flow diagram.

#### FIGURE 6-4: ACKNOWLEDGE POLLING FLOW

### FIGURE 6-5:

## 9.0 VOLTAGE REFERENCE MODULE

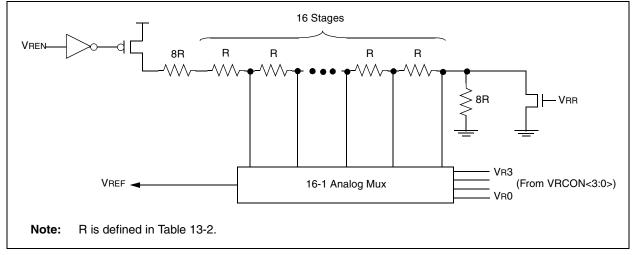

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 9-1. The block diagram is given in Figure 9-1.

### 9.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1: VREF = (VR<3:0>/24) x VDD

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 13-1). Example 9-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

| R/W-0    | R/W-0                                                                                              | R/W-0      | U-0      | R/W-0         | R/W-0 | R/W-0     | R/W-0 |                                                                                       |  |

|----------|----------------------------------------------------------------------------------------------------|------------|----------|---------------|-------|-----------|-------|---------------------------------------------------------------------------------------|--|

| VREN     | VROE                                                                                               | Vrr        | _        | Vr3           | VR2   | VR1       | VR0   | R = Readable bit                                                                      |  |

| bit7     | •                                                                                                  |            | •        |               |       |           | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |

| bit 7:   | 7: VREN: VREF Enable<br>1 = VREF circuit powered on<br>0 = VREF circuit powered down, no IDD drain |            |          |               |       |           |       |                                                                                       |  |

| bit 6:   | VROE: VREF Output Enable<br>1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |            |          |               |       |           |       |                                                                                       |  |

| bit 5:   | VRR: VREF Range selection<br>1 = Low Range<br>0 = High Range                                       |            |          |               |       |           |       |                                                                                       |  |

| bit 4:   | Unimplem                                                                                           | ented: Re  | ad as '0 | <sup>ji</sup> |       |           |       |                                                                                       |  |

| bit 3-0: |                                                                                                    | VRR = 1: V | ref = (\ | /R<3:0>/ 2    | -     | 32) * Vdd |       |                                                                                       |  |

## REGISTER 9-1: VRCON REGISTER (ADDRESS 9Fh)

FIGURE 9-1: VOLTAGE REFERENCE BLOCK DIAGRAM

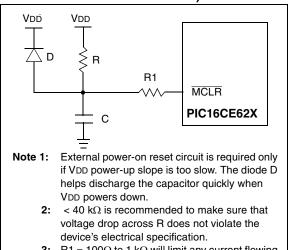

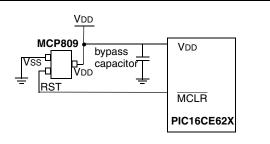

#### FIGURE 10-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

**3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

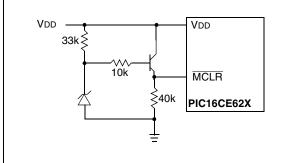

### FIGURE 10-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal Brown-out Reset circuitry should be disabled when using this circuit.

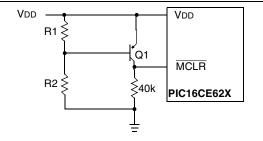

#### FIGURE 10-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \times \frac{R1}{R1 + R2} = 0.7 V$$

- **2:** Internal brown-out detection should be disabled when using this circuit.

- **3:** Resistors should be adjusted for the characteristics of the transistor.

### FIGURE 10-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

| BTFSS            | Bit Test f                                                               | i, Skip if S                                                                                                | Set                                       |                           |  |

|------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|--|

| Syntax:          | [ label ] BTFSS f,b                                                      |                                                                                                             |                                           |                           |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b < 7 \end{array}$          | 7                                                                                                           |                                           |                           |  |

| Operation:       | skip if (f<                                                              | b>) = 1                                                                                                     |                                           |                           |  |

| Status Affected: | None                                                                     |                                                                                                             |                                           |                           |  |

| Encoding:        | 01                                                                       | 11bb                                                                                                        | bfff                                      | ffff                      |  |

| Description:     | instruction<br>If bit 'b' is '<br>fetched du<br>execution,<br>executed i | register 'f' is<br>is skipped.<br>1', then the<br>ring the cur<br>is discarde<br>nstead, ma<br>instruction. | next instru<br>rrent instru<br>d and a No | uction<br>Iction<br>DP is |  |

| Words:           | 1                                                                        |                                                                                                             |                                           |                           |  |

| Cycles:          | 1(2)                                                                     |                                                                                                             |                                           |                           |  |

| Example          | HERE<br>FALSE<br>TRUE                                                    |                                                                                                             | FLAG, 1<br>PROCESS_                       | _CODE                     |  |

|                  | Before In                                                                | struction                                                                                                   |                                           |                           |  |

|                  | After Inst                                                               | ruction<br>if FLAG<1><br>PC = a<br>if FLAG<1>                                                               | = 0,<br>address F                         |                           |  |

| CLRF             | Clear f                                                               |                    |             |           |  |

|------------------|-----------------------------------------------------------------------|--------------------|-------------|-----------|--|

| Syntax:          | [label] (                                                             | CLRF f             |             |           |  |

| Operands:        | $0 \le f \le 12$                                                      | 27                 |             |           |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                    |             |           |  |

| Status Affected: | Z                                                                     |                    |             |           |  |

| Encoding:        | 0 0                                                                   | 0001               | lfff        | ffff      |  |

| Description:     | The conte and the Z                                                   | 0                  | ster 'f' ar | e cleared |  |

| Words:           | 1                                                                     |                    |             |           |  |

| Cycles:          | 1                                                                     |                    |             |           |  |

| Example          | CLRF                                                                  | FLAC               | G_REG       |           |  |

|                  | Before In                                                             | struction          |             |           |  |

|                  |                                                                       | FLAG_RE            | EG =        | 0x5A      |  |

|                  | After Inst                                                            | ruction<br>Flag Re | EG =        | 0x00      |  |

|                  |                                                                       | Z                  | =           | 1         |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                            |  |  |  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<4:3>) $\rightarrow$ PC<12:11>                                                                                                                                              |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                          |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                             |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle instruc-<br>tion. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                             |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                             |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                                               |  |  |  |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                    |  |  |  |

| Clear W                                                              |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [ label ]                                                            | CLRW                                                                                                          |                                                                                                                                                                  |                                                                                                                                                                                               |

| None                                                                 |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |

| $\begin{array}{c} 00h \rightarrow (V \\ 1 \rightarrow Z \end{array}$ | V)                                                                                                            |                                                                                                                                                                  |                                                                                                                                                                                               |

| Z                                                                    |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |

| 00                                                                   | 0001                                                                                                          | 0000                                                                                                                                                             | 0011                                                                                                                                                                                          |

| W register set.                                                      | is cleare                                                                                                     | d. Zero bit                                                                                                                                                      | (Z) is                                                                                                                                                                                        |

| 1                                                                    |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |

| 1                                                                    |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |

| CLRW                                                                 |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |

| Before In                                                            | structior                                                                                                     | l                                                                                                                                                                |                                                                                                                                                                                               |

| After Inst                                                           | ruction<br>W =                                                                                                | 0x5A<br>0x00<br>1                                                                                                                                                |                                                                                                                                                                                               |

|                                                                      | $[label]$ None $00h \rightarrow (V \\ 1 \rightarrow Z$ $Z$ $00$ W register set. 1 $CLRW$ Before In After Inst | $[label] CLRW$ None $00h \rightarrow (W)$ $1 \rightarrow Z$ $Z$ $00 0001$ W register is cleared set. $1$ $CLRW$ Before Instruction $W =$ After Instruction $W =$ | $[label] CLRW$ None $00h \rightarrow (W)$ $1 \rightarrow Z$ Z $00  0001  0000$ W register is cleared. Zero bit set. $1$ $1$ $CLRW$ Before Instruction $W = 0x5A$ After Instruction $W = 0x00$ |

$\odot$  1998-2013 Microchip Technology Inc.

| IORWF            | Inclusive OR W with f                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                          |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                    |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                    |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |

| Words:           | 1                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                    |

| Example          | IORWF RESULT, 0                                                                                                                                                      |

|                  | $\begin{array}{rcl} Before \ Instruction \\ RESULT &= & 0x13 \\ W &= & 0x91 \\ After \ Instruction \\ RESULT &= & 0x13 \\ W &= & 0x93 \\ Z &= & 1 \end{array}$       |

| MOVF             | Move f                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                             |  |  |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                  | to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Example          | MOVF FSR, 0                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                     |  |  |  |  |  |  |  |

| MOVLW            | Move Literal to W                                                                          |   |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|---|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |   |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                          |   |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |   |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                       |   |  |  |  |  |  |  |  |

| Encoding:        | 11 00xx kkkk kkk                                                                           | c |  |  |  |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |   |  |  |  |  |  |  |  |

| Words:           | 1                                                                                          |   |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                          |   |  |  |  |  |  |  |  |

| Example          | MOVLW 0x5A                                                                                 |   |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                              |   |  |  |  |  |  |  |  |

| MOVWF            | Move W to f                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                                                                                                            |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                                                        |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                       |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                          |

| Description:     | Move data from W register to register 'f'.                                                                                                                                                 |

| Words:           | 1                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                          |

| Example          | MOVWF OPTION                                                                                                                                                                               |

|                  | $\begin{array}{rcl} \text{Before Instruction} & & \\ & \text{OPTION} & = & 0xFF \\ W & = & 0x4F \\ \text{After Instruction} & & \\ & \text{OPTION} & = & 0x4F \\ W & = & 0x4F \end{array}$ |

NOTES:

## 13.1 DC CHARACTERISTICS:

### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended)

|              |                           |                                                                        | $\begin{array}{l lllllllllllllllllllllllllllllllllll$ |      |           |            |                                                                   |  |

|--------------|---------------------------|------------------------------------------------------------------------|-------------------------------------------------------|------|-----------|------------|-------------------------------------------------------------------|--|

| Param<br>No. | Sym                       | Characteristic                                                         | Min                                                   | Тур† | Max       | Units      | Conditions                                                        |  |

| D001         | Vdd                       | Supply Voltage                                                         | 3.0                                                   | -    | 5.5       | V          | See Figure 13-1 through Figure 13-3                               |  |

| D002         | Vdr                       | RAM Data Retention<br>Voltage (Note 1)                                 | -                                                     | 1.5* | -         | V          | Device in SLEEP mode                                              |  |

| D003         | VPOR                      | VDD start voltage to<br>ensure Power-on Reset                          | -                                                     | Vss  | -         | V          | See section on power-on reset for details                         |  |

| D004         | SVDD                      | VDD rise rate to ensure<br>Power-on Reset                              | 0.05*                                                 | -    | -         | V/ms       | See section on power-on reset for details                         |  |

| D005         | VBOR                      | Brown-out Detect Voltage                                               | 3.7                                                   | 4.0  | 4.35      | V          | BOREN configuration bit is cleared                                |  |

| D010         | IDD                       | Supply Current (Note 2, 4)                                             | -                                                     | 1.2  | 2.0       | mA         | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)* |  |

|              |                           |                                                                        | -                                                     | 0.4  | 1.2       | mA         | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT osc mode, (Note 4)  |  |

|              |                           |                                                                        | -                                                     | 1.0  | 2.0       | mA         | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS osc mode, (Note 6) |  |

|              |                           |                                                                        | -                                                     | 4.0  | 6.0       | mA         | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS osc mode           |  |

|              |                           |                                                                        | -                                                     | 4.0  | 7.0       | mA         | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS osc mode          |  |

|              |                           |                                                                        | -                                                     | 35   | 70        | μA         | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP osc mode           |  |

| D020         | IPD                       | Power Down Current (Note 3)                                            | -                                                     | -    | 2.2       | μA         | VDD = 3.0V                                                        |  |

|              |                           |                                                                        | -                                                     | -    | 5.0       | μA         | VDD = 4.5V*                                                       |  |

|              |                           |                                                                        | _                                                     | _    | 9.0<br>15 | μΑ<br>μΑ   | VDD = 5.5V<br>VDD = 5.5V Extended                                 |  |

| D022         | ΔIWDT                     | WDT Current (Note 5)                                                   | _                                                     | 6.0  | 10        | μΑ         | VDD = 4.0V                                                        |  |

| 2022         |                           |                                                                        |                                                       | 0.0  | 12        | μA         | (125°C)                                                           |  |

| D022A        | $\Delta$ IBOR             | Brown-out Reset Current (Note 5)                                       | -                                                     | 75   | 125       | μA         | BOD enabled, VDD = 5.0V                                           |  |

| D023         | ∆ICOMP                    | Comparator Current for each<br>Comparator (Note 5)                     | -                                                     | 30   | 60        | μA         | VDD = 4.0V                                                        |  |

| D023A        | $\Delta$ IVREF            | VREF Current (Note 5)                                                  | -                                                     | 80   | 135       | μA         | VDD = 4.0V                                                        |  |

|              | $\Delta \text{IEE Write}$ | Operating Current                                                      | -                                                     |      | 3         | mA         | Vcc = 5.5V, SCL = 400 kHz                                         |  |

|              | $\Delta$ IEE Read         | Operating Current                                                      | -                                                     |      | 1         | mA         |                                                                   |  |

|              | ΔIEE                      | Standby Current                                                        | -                                                     |      | 30        | μA         | $V_{CC} = 3.0V, EE V_{DD} = V_{CC}$                               |  |

|              | ΔIEE                      | Standby Current                                                        | -                                                     |      | 100       | μ <b>A</b> | Vcc = 3.0V, EE VDD = Vcc                                          |  |

| 1A           | Fosc                      | LP Oscillator Operating Frequency                                      | 0                                                     | -    | 200       | kHz        | All temperatures                                                  |  |

|              |                           | RC Oscillator Operating Frequency                                      | 0                                                     | -    | 4         | MHz<br>MHz | All temperatures                                                  |  |

|              |                           | XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0                                                     | _    | 4<br>20   | MHZ        | All temperatures<br>All temperatures                              |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{\text{MCLR}}$  = VDD; WDT enabled/disabled as specified.

3: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**6:** Commercial temperature range only.

#### 13.3 DC CHARACTERISTICS:

#### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended) PIC16LCE62X (Commercial, Industrial)

|       |       |                                | Standard Opera     | ating ( | Conditions (u   | Inles | s otherwise stated)                                                                                                |

|-------|-------|--------------------------------|--------------------|---------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------|

|       |       |                                |                    |         |                 |       | +85°C for industrial and                                                                                           |

| DC CH | IARAC | TERISTICS                      |                    |         | 0°C ≤           | TA≤   | +70°C for commercial and                                                                                           |

|       |       |                                |                    |         | -40°C ≤         | TA≤   | +125°C for extended                                                                                                |

|       |       |                                | Operating voltag   | e Vdi   | o range as de   | scrib | ed in DC spec Table 13-1                                                                                           |

| Parm  | Sym   | Characteristic                 | Min                | Typ†    | Max             | Unit  | Conditions                                                                                                         |

| No.   |       |                                |                    |         |                 |       |                                                                                                                    |

|       | Vi∟   | Input Low Voltage              |                    |         |                 |       |                                                                                                                    |

|       |       | I/O ports                      |                    |         |                 |       |                                                                                                                    |

| D030  |       | with TTL buffer                | Vss                | -       | 0.8V<br>0.15Vdd | v     | VDD = 4.5V to 5.5V, Otherwise                                                                                      |

| D031  |       | with Schmitt Trigger input     | Vss                |         | 0.2VDD          | v     |                                                                                                                    |

| D032  |       | MCLR, RA4/T0CKI,OSC1 (in RC    | Vss                | _       | 0.2VDD          | V     | Note1                                                                                                              |

|       |       | mode)                          |                    |         |                 | -     |                                                                                                                    |

| D033  |       | OSC1 (in XT and HS)            | Vss                | _       | 0.3VDD          | v     |                                                                                                                    |

|       |       | OSC1 (in LP)                   | Vss                | -       | 0.6Vdd - 1.0    | V     |                                                                                                                    |

|       | Vih   | Input High Voltage             |                    |         |                 |       |                                                                                                                    |

|       |       | I/O ports                      |                    |         |                 |       |                                                                                                                    |

| D040  |       | with TTL buffer                | 2.0V               | -       | Vdd             | V     | VDD = 4.5V to 5.5V, Otherwise                                                                                      |

|       |       |                                | .25VDD + 0.8V      |         | Vdd             |       |                                                                                                                    |

| D041  |       | with Schmitt Trigger input     | 0.8VDD             |         | Vdd             |       |                                                                                                                    |

| D042  |       | MCLR RA4/T0CKI                 | 0.8VDD             | -       | Vdd             | V     |                                                                                                                    |

| D043  |       | OSC1 (XT, HS and LP)           | 0.7VDD             | -       | Vdd             | V     |                                                                                                                    |

| D043A |       | OSC1 (in RC mode)              | 0.9Vdd             |         |                 |       | Note1                                                                                                              |

| D070  | IPURB | PORTB weak pull-up current     | 50                 | 200     | 400             | μA    | VDD = 5.0V, VPIN = VSS                                                                                             |

|       |       | Input Leakage Current          |                    |         |                 |       |                                                                                                                    |

|       | ١L    | (Notes 2, 3)                   |                    |         | 110             |       |                                                                                                                    |

| Daca  |       | I/O ports (Except PORTA)       |                    |         | ±1.0            | •     | VSS $\leq$ VPIN $\leq$ VDD, pin at hi-impedance                                                                    |

| D060  |       | PORTA                          | -                  | -       | ±0.5            | μA    |                                                                                                                    |

| D061  |       | RA4/T0CKI                      | -                  | -       | ±1.0            | μA    |                                                                                                                    |

| D063  |       | OSC1, MCLR                     | -                  | -       | ±5.0            | μA    | , ,                                                                                                                |

|       | Vol   | Output Low Voltage             |                    |         |                 |       | configuration                                                                                                      |

| D080  | VOL   | I/O ports                      |                    | _       | 0.6             | v     | IOL=8.5 mA, VDD=4.5V, -40° to +85°C                                                                                |

| D000  |       |                                | _                  | _       | 0.6             | v     | IOL=7.0 mA, VDD=4.5V, +125°C                                                                                       |

| 0002  |       | OSC2/CLKOUT (RC only)          | _                  | _       | 0.6             | v     | IOL=7.0 mA, $VDD=4.5V$ , $+125$ C<br>$IOL=1.6$ mA, $VDD=4.5V$ , $-40^{\circ}$ to $+85^{\circ}$ C                   |

| D083  |       | OSCZ/CEROUT (RC OIlly)         | _                  | _       | 0.6             | v     | IOL=1.0  IIA,  VDD=4.5  V, -40  IO +83  C<br>$IOL=1.2 \text{ mA}, \text{ VDD}=4.5 \text{ V}, +125^{\circ}\text{C}$ |

|       | Vон   | Output High Voltage (Note 3)   | _                  | _       | 0.0             | v     | 10L-1.2 IIIA, VDD-4.3V, +123 C                                                                                     |

| D090  | VOIT  | I/O ports (Except RA4)         | VDD-0.7            | _       | _               | v     | IOH=-3.0 mA, VDD=4.5V, -40° to +85°C                                                                               |

| 2000  |       |                                | VDD-0.7<br>VDD-0.7 | _       | _               | v     | IOH=-2.5 mA, VDD=4.5V, +125°C                                                                                      |

| D092  |       | OSC2/CLKOUT (RC only)          | VDD-0.7<br>VDD-0.7 | _       | _               |       | IOH=-1.3 mA, VDD=4.5V, -40° to +85°C                                                                               |

| DUUL  |       |                                | VDD-0.7<br>VDD-0.7 | _       | _               |       | IOH=-1.0 mA, VDD=4.5V, +125°C                                                                                      |

| *D150 | Vod   | Open-Drain High Voltage        |                    |         | 8.5             |       | RA4 pin                                                                                                            |

|       |       | Capacitive Loading Specs on    |                    |         |                 | -     | 10 <sup></sup>                                                                                                     |

|       |       | Output Pins                    |                    |         |                 |       |                                                                                                                    |

| D100  | cosc  | OSC2 pin                       |                    |         | 15              | pF    | In XT, HS and LP modes when external                                                                               |

|       | 2     |                                |                    |         |                 |       | clock used to drive OSC1.                                                                                          |

| D101  | Cio   | All I/O pins/OSC2 (in RC mode) |                    |         | 50              | pF    |                                                                                                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16CE62X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

### TABLE 13-1: COMPARATOR SPECIFICATIONS

| Param No. | Characteristics                           | Sym    | Min  | Тур   | Max       | Units | Comments   |

|-----------|-------------------------------------------|--------|------|-------|-----------|-------|------------|

| D300      | Input offset voltage                      | VIOFF  |      | ± 5.0 | ± 10      | mV    |            |

| D301      | Input common mode voltage                 | VICM   | 0    |       | Vdd - 1.5 | V     |            |

| D302      | CMRR                                      | CMRR   | +55* |       |           | db    |            |

| 300       | Response Time <sup>(1)</sup>              | TRESP  |      | 150*  | 400*      | ns    | PIC16CE62X |

| 301       | Comparator Mode Change to<br>Output Valid | Тмс2ov |      |       | 10*       | μS    |            |

Operating Conditions: VDD range as described in Table 12-1, -40°C<TA<+125°C. .

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

#### TABLE 13-2: VOLTAGE REFERENCE SPECIFICATIONS

Operating Conditions: VDD range as described in Table 12-1, -40°C<TA<+125°C.

| Param<br>No. | Characteristics              | Sym  | Min    | Тур | Мах                          | Units      | Comments                                |

|--------------|------------------------------|------|--------|-----|------------------------------|------------|-----------------------------------------|

| D310         | Resolution                   | VRES | VDD/24 |     | Vdd/32                       | LSB        |                                         |

| D311         | Absolute Accuracy            | Vraa |        |     | <u>+</u> 1/4<br><u>+</u> 1/2 | LSB<br>LSB | Low Range (VRR=1)<br>High Range (VRR=0) |

| D312         | Unit Resistor Value (R)      | VRur |        | 2K* |                              | Ω          | Figure 9-1                              |

| 310          | Settling Time <sup>(1)</sup> | TSET |        |     | 10*                          | μS         |                                         |

\* These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

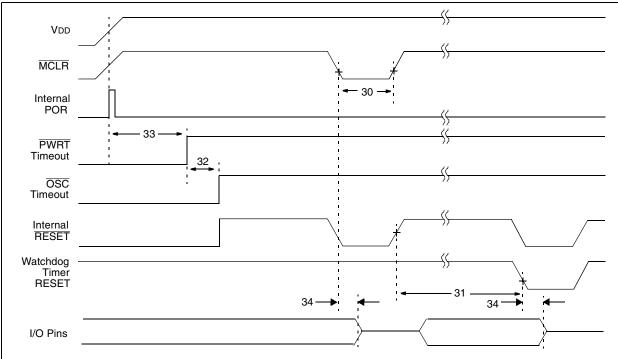

#### FIGURE 13-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

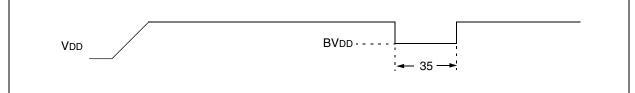

#### FIGURE 13-8: BROWN-OUT RESET TIMING

#### **TABLE 13-5:** RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min  | Тур†      | Max  | Units | Conditions                                         |

|------------------|-------|--------------------------------------------------|------|-----------|------|-------|----------------------------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 2000 | _         | _    | ns    | -40° to +85°C                                      |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7*   | 18        | 33*  | ms    | $VDD = 5.0V, -40^{\circ} \text{ to } +85^{\circ}C$ |

| 32               | Tost  | Oscillation Start-up Timer Period                | _    | 1024 Tosc | _    | _     | Tosc = OSC1 period                                 |

| 33               | Tpwrt | Power-up Timer Period                            | 28*  | 72        | 132* | ms    | $VDD = 5.0V, -40^{\circ} \text{ to } +85^{\circ}C$ |

| 34               | Tioz  | I/O hi-impedance from MCLR low                   |      | —         | 2.0  | μS    |                                                    |

| 35               | TBOR  | Brown-out Reset Pulse Width                      | 100* | —         |      | μs    | $3.7V \leq V\text{DD} \leq 4.3V$                   |

These parameters are characterized but not tested. Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

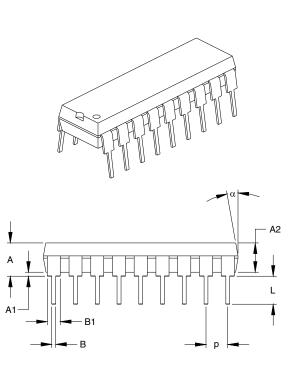

#### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units |      | INCHES* |      | MILLIMETERS |       |       |

|----------------------------|-------|------|---------|------|-------------|-------|-------|

| Dimensio                   | MIN   | NOM  | MAX     | MIN  | NOM         | MAX   |       |

| Number of Pins             | n     |      | 18      |      |             | 18    |       |

| Pitch                      | р     |      | .100    |      |             | 2.54  |       |

| Top to Seating Plane       | Α     | .140 | .155    | .170 | 3.56        | 3.94  | 4.32  |

| Molded Package Thickness   | A2    | .115 | .130    | .145 | 2.92        | 3.30  | 3.68  |

| Base to Seating Plane      | A1    | .015 |         |      | 0.38        |       |       |

| Shoulder to Shoulder Width | Е     | .300 | .313    | .325 | 7.62        | 7.94  | 8.26  |

| Molded Package Width       | E1    | .240 | .250    | .260 | 6.10        | 6.35  | 6.60  |

| Overall Length             | D     | .890 | .898    | .905 | 22.61       | 22.80 | 22.99 |

| Tip to Seating Plane       | L     | .125 | .130    | .135 | 3.18        | 3.30  | 3.43  |

| Lead Thickness             | С     | .008 | .012    | .015 | 0.20        | 0.29  | 0.38  |

| Upper Lead Width           | B1    | .045 | .058    | .070 | 1.14        | 1.46  | 1.78  |

| Lower Lead Width           | В     | .014 | .018    | .022 | 0.36        | 0.46  | 0.56  |

| Overall Row Spacing        | eB    | .310 | .370    | .430 | 7.87        | 9.40  | 10.92 |

| Mold Draft Angle Top       | α     | 5    | 10      | 15   | 5           | 10    | 15    |

| Mold Draft Angle Bottom    | β     | 5    | 10      | 15   | 5           | 10    | 15    |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001

Drawing No. C04-007

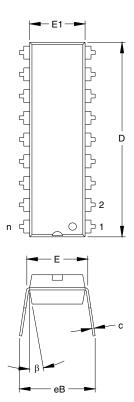

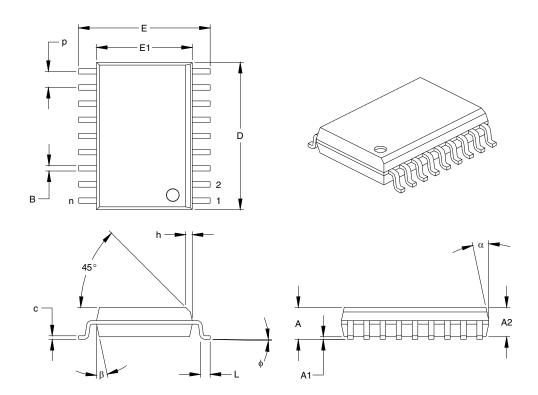

### 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Limits<br>n | MIN                                         | NOM                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                            |                                                                                                                                                                                                                                     |