Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

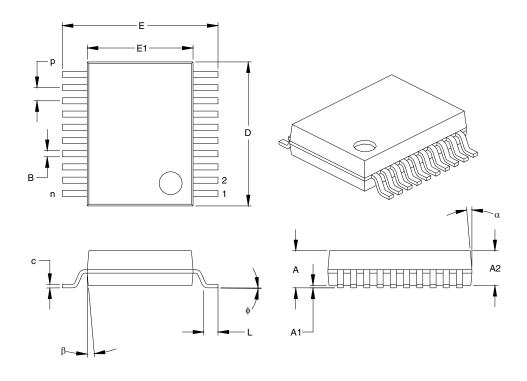

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce625-04e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Name         | DIP/<br>SOIC<br>Pin # | SSOP<br>Pin #                   | l/O/P<br>Type | Buffer<br>Type          | Description                                                                                                                                                                                                       |

|--------------|-----------------------|---------------------------------|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                    | 18                              | I             | ST/CMOS                 | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT  | 15                    | 17                              | 0             | -                       | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp     | 4                     | 4                               | I/P           | ST                      | Master clear (reset) input/programming voltage input.<br>This pin is an active low reset to the device.                                                                                                           |

|              |                       |                                 |               |                         | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0      | 17                    | 19                              | I/O           | ST                      | Analog comparator input                                                                                                                                                                                           |

| RA1/AN1      | 18                    | 20                              | I/O           | ST                      | Analog comparator input                                                                                                                                                                                           |

| RA2/AN2/VREF | 1                     | 1                               | I/O           | ST                      | Analog comparator input or VREF output                                                                                                                                                                            |

| RA3/AN3      | 2                     | 2                               | I/O           | ST                      | Analog comparator input /output                                                                                                                                                                                   |

| RA4/T0CKI    | 3                     | 3                               | I/O           | ST                      | Can be selected to be the clock input to the Timer0<br>timer/counter or a comparator output. Output is open<br>drain type.                                                                                        |

|              |                       |                                 |               |                         | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                               |

| RB0/INT      | 6                     | 7                               | I/O           | TTL/ST(1)               | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                                        |

| RB1          | 7                     | 8                               | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB2          | 8                     | 9                               | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB3          | 9                     | 10                              | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB4          | 10                    | 11                              | I/O           | TTL                     | Interrupt on change pin.                                                                                                                                                                                          |

| RB5          | 11                    | 12                              | I/O           | TTL                     | Interrupt on change pin.                                                                                                                                                                                          |

| RB6          | 12                    | 13                              | I/O           | TTL/ST <sup>(2)</sup>   | Interrupt on change pin. Serial programming clock.                                                                                                                                                                |

| RB7          | 13                    | 14                              | I/O           | TTL/ST <sup>(2)</sup>   | Interrupt on change pin. Serial programming data.                                                                                                                                                                 |

| Vss          | 5                     | 5,6                             | Р             | l –                     | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| Vdd          | 14                    | 15,16                           | Р             | —                       | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Legend:      |                       | utput<br>Not used<br>: TTL inpu | 1 :           | O = input/or<br>= Input | utput P = power<br>ST = Schmitt Trigger input                                                                                                                                                                     |

**TABLE 3-1: PIC16CE62X PINOUT DESCRIPTION**

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt. **Note 2:** This buffer is a Schmitt Trigger input when used in serial programming mode.

### 4.2 Data Memory Organization

The data memory (Figure 4-4 and Figure 4-5) is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-7Fh (Bank0) on the PIC16CE623/624 and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16CE625 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1. In all three microcontrollers, address space F0h-FFh (Bank1) is mapped to 70-7Fh (Bank0) as common RAM.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $96 \times 8$  in the PIC16CE623/624 and 128 x 8 in the PIC16CE625. Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

#### FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16CE623/624

| File<br>Address | 3                                                                                         | -                   | File<br>Address |  |  |

|-----------------|-------------------------------------------------------------------------------------------|---------------------|-----------------|--|--|

| 00h             | INDF <sup>(1)</sup>                                                                       | INDF <sup>(1)</sup> | 80h             |  |  |

| 01h             | TMR0                                                                                      | OPTION              | 81h             |  |  |

| 02h             | PCL                                                                                       | PCL                 | 82h             |  |  |

| 03h             | STATUS                                                                                    | STATUS              | 83h             |  |  |

| 04h             | FSR                                                                                       | FSR                 | 84h             |  |  |

| 05h             | PORTA                                                                                     | TRISA               | 85h             |  |  |

| 06h             | PORTB                                                                                     | TRISB               | 86h             |  |  |

| 07h             |                                                                                           |                     | 87h             |  |  |

| 08h             |                                                                                           |                     | 88h             |  |  |

| 09h             |                                                                                           |                     | 89h             |  |  |

| 0Ah             | PCLATH                                                                                    | PCLATH              | 8Ah             |  |  |

| 0Bh             | INTCON                                                                                    | INTCON              | 8Bh             |  |  |

| 0Ch             | PIR1                                                                                      | PIE1                | 8Ch             |  |  |

| 0Dh             |                                                                                           |                     | 8Dh             |  |  |

| 0Eh             |                                                                                           | PCON                | 8Eh             |  |  |

| 0Fh             |                                                                                           |                     | 8Fh             |  |  |

| 10h             |                                                                                           | EEINTF              | 90h             |  |  |

| 11h             |                                                                                           |                     | 91h             |  |  |

| 12h             |                                                                                           |                     | 92h             |  |  |

| 13h             |                                                                                           |                     | 93h             |  |  |

| 14h             |                                                                                           |                     | 94h             |  |  |

| 15h             |                                                                                           |                     | 95h             |  |  |

| 16h             |                                                                                           |                     | 96h             |  |  |

| 17h             |                                                                                           |                     | 97h             |  |  |

| 18h             |                                                                                           |                     | 98h             |  |  |

| 19h             |                                                                                           |                     | 99h             |  |  |

| 1Ah             |                                                                                           |                     | 9Ah             |  |  |

| 1Bh             |                                                                                           |                     | 9Bh             |  |  |

| 1Ch             |                                                                                           |                     | 9Ch             |  |  |

| 1Dh             |                                                                                           |                     | 9Dh             |  |  |

| 1Eh             |                                                                                           |                     | 9Eh             |  |  |

| 1Fh             | CMCON                                                                                     | VRCON               | 9Fh             |  |  |

| 20h             |                                                                                           |                     | A0h             |  |  |

|                 | General<br>Purpose<br>Register                                                            |                     |                 |  |  |

|                 |                                                                                           |                     |                 |  |  |

|                 |                                                                                           |                     | EFh             |  |  |

|                 |                                                                                           | Accesses            | F0h             |  |  |

| 7Fh             |                                                                                           | 70h-7Fh             | FFh             |  |  |

| / [1]           | Bank 0                                                                                    | Bank 1              |                 |  |  |

|                 | Unimplemented data memory locations, read as '0'. <b>Note 1:</b> Not a physical register. |                     |                 |  |  |

#### FIGURE 4-5: DATA MEMORY MAP FOR THE PIC16CE625

| File     |                      |                     | File       |

|----------|----------------------|---------------------|------------|

| Address  | ;                    |                     | Address    |

| 00h      | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h        |

| 01h      | TMR0                 | OPTION              | 81h        |

| 02h      | PCL                  | PCL                 | 82h        |

| 03h      | STATUS               | STATUS              | 83h        |

| 04h      | FSR                  | FSR                 | 84h        |

| 05h      | PORTA                | TRISA               | 85h        |

| 06h      | PORTB                | TRISB               | 86h        |

| 07h      |                      |                     | 87h        |

| 08h      |                      |                     | 88h        |

| 09h      |                      |                     | 89h        |

| 0Ah      | PCLATH               | PCLATH              | 8Ah        |

| 0Bh      | INTCON               | INTCON              | 8Bh        |

| 0Ch      | PIR1                 | PIE1                | 8Ch        |

| 0Dh      |                      |                     | 8Dh        |

| 0Eh      |                      | PCON                | 8Eh        |

| 0Fh      |                      |                     | 8Fh        |

| 10h      |                      | EEINTF              | 90h        |

| 11h      |                      |                     | 91h        |

| 12h      |                      |                     | 92h        |

| 13h      |                      |                     | 93h        |

| 14h      |                      |                     | 94h        |

| 15h      |                      |                     | 95h        |

| 16h      |                      |                     | 96h        |

| 17h      |                      |                     | 97h        |

| 18h      |                      |                     | 98h        |

| 19h      |                      |                     | 99h        |

| 1Ah      |                      |                     | 9Ah        |

| 1Bh      |                      |                     | 9Bh        |

| 1Ch      |                      |                     | 9Ch        |

| 1Dh      |                      |                     | 9Dh        |

| 1Eh      |                      |                     | 9Eh        |

| 1Fh      | CMCON                | VRCON               | 9Fh        |

| 20h      |                      |                     | A0h        |

|          | General              | General             | AUII       |

|          | Purpose<br>Register  | Purpose<br>Register |            |

|          | negistei             | negister            | BFh        |

|          |                      |                     | C0h        |

|          |                      |                     |            |

|          |                      | _                   | F0h        |

|          |                      | Accesses            |            |

| 751      |                      | 70h-7Fh             | FFh        |

| 7Fh I    | Bank 0               | Bank 1              | J FFN      |

| <b>—</b> |                      |                     |            |

|          | plemented data me    |                     | ad as '0'. |

| Note 1:  | Not a physical regis | ster.               |            |

#### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

# REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1    | R/W-1                                                                                                                                                                    | R/W-1                                                       | R/W-1        | R/W-1     | R/W-1         | R/W-1      | R/W-1 |                                                                                                                   |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------|-----------|---------------|------------|-------|-------------------------------------------------------------------------------------------------------------------|

| RBPU     | INTEDG                                                                                                                                                                   | TOCS                                                        | TOSE         | PSA       | PS2           | PS1        | PS0   | R = Readable bit                                                                                                  |

| bit7     |                                                                                                                                                                          |                                                             |              |           |               |            | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |

| bit 7:   | <b>RBPU</b> : PO<br>1 = PORTE<br>0 = PORTE                                                                                                                               | 3 pull-ups                                                  | are disal    | oled      | lividual port | latch valu | es    |                                                                                                                   |

| bit 6:   | INTEDG: In<br>1 = Interrup<br>0 = Interrup                                                                                                                               | ot on rising                                                | g edge o     | f RB0/INT |               |            |       |                                                                                                                   |

| bit 5:   | <b>TOCS</b> : TMF<br>1 = Transiti<br>0 = Interna                                                                                                                         | ion on RA                                                   | 4/T0CKI      | pin       | (OUT)         |            |       |                                                                                                                   |

| bit 4:   | bit 4: <b>T0SE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin |                                                             |              |           |               |            |       |                                                                                                                   |

| bit 3:   |                                                                                                                                                                          |                                                             |              |           |               |            |       |                                                                                                                   |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : F                                                                                                                                                 | Prescaler I                                                 | Rate Sele    | ect bits  |               |            |       |                                                                                                                   |

|          | Bit Value                                                                                                                                                                | TMR0 Ra                                                     | te WD1       | Γ Rate    |               |            |       |                                                                                                                   |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                                     | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 :<br>3 1 : | 2<br>4    |               |            |       |                                                                                                                   |

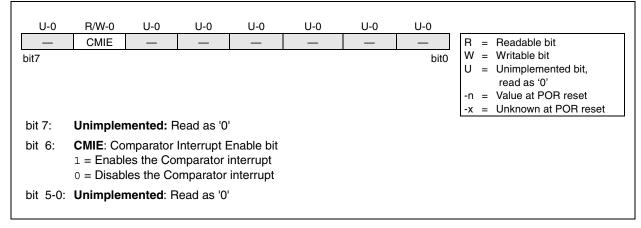

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bit for the comparator interrupt.

### REGISTER 4-4: PIE1 REGISTER (ADDRESS 8CH)

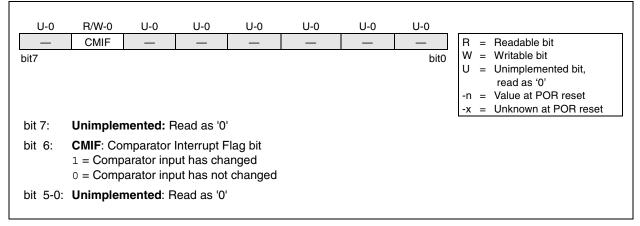

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt   |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|

|       | condition occurs, regardless of the state of    |  |  |  |  |

|       | its corresponding enable bit or the global      |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User               |  |  |  |  |

|       | software should ensure the appropriate          |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling |  |  |  |  |

|       | an interrupt.                                   |  |  |  |  |

### REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

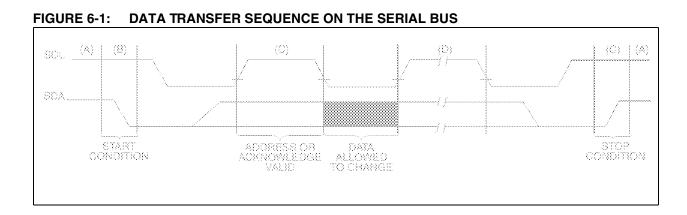

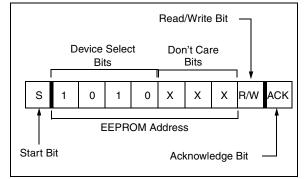

### 6.2 Device Addressing

After generating a START condition, the processor transmits a control byte consisting of a EEPROM address and a Read/Write bit that indicates what type of operation is to be performed. The EEPROM address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one, a read operation is selected, and when set to a zero, a write operation is selected. (Figure 6-3). The bus is monitored for its corresponding EEPROM address all the time. It generates an acknowledge bit if the EEPROM address was true and it is not in a programming mode.

### FIGURE 6-3: CONTROL BYTE FORMAT

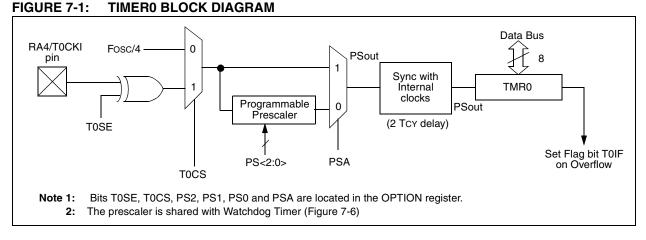

# 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

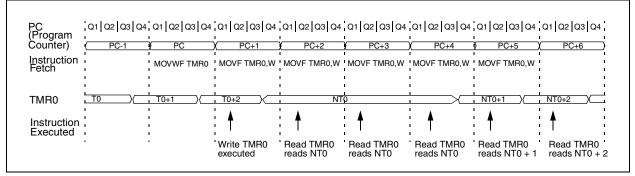

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

### 7.1 <u>Timer0 Interrupt</u>

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

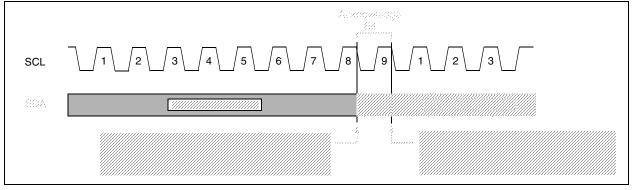

### FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

The code example in Example 8-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 8-1: INITIALIZING COMPARATOR MODULE

| FLAG_REG | F EQU        | 0X20                              |

|----------|--------------|-----------------------------------|

| CLRF     | FLAG_REG     | ;Init flag register               |

| CLRF     | PORTA        | ;Init PORTA                       |

| MOVF     | CMCON,W      | ;Move comparator contents to W    |

| ANDLW    | 0xC0         | ;Mask comparator bits             |

| IORWF    | FLAG_REG,F   | ;Store bits in flag register      |

| MOVLW    | 0x03         | ;Init comparator mode             |

| MOVWF    | CMCON        | ;CM<2:0> = 011                    |

| BSF      | STATUS, RPO  | ;Select Bank1                     |

| MOVLW    | 0x07         | ;Initialize data direction        |

| MOVWF    | TRISA        | ;Set RA<2:0> as inputs            |

|          |              | ;RA<4:3> as outputs               |

|          |              | ;TRISA<7:5> always read `0'       |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| CALL     | DELAY 10     | ;10µs delay                       |

| MOVF     | CMCON, F     | ;Read CMCONtoend change condition |

| BCF      | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF      | STATUS, RPO  | ;Select Bank 1                    |

| BSF      | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| BSF      | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF      | INTCON, GIE  | ;Global interrupt enable          |

|          |              |                                   |

#### 8.2 Comparator Operation

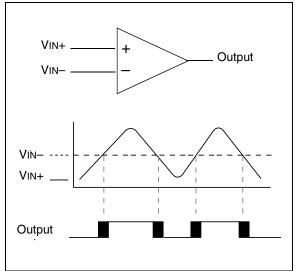

A single comparator is shown in Figure 8-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN–, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN–, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 8-2 represent the uncertainty due to input offsets and response time.

### 8.3 <u>Comparator Reference</u>

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal that is present at VIN– is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 8-2).

FIGURE 8-2: SINGLE COMPARATOR

#### 8.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 8.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 8-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

# 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

## 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

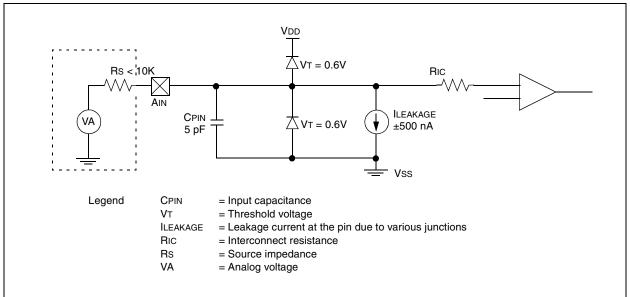

## 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

### FIGURE 8-4: ANALOG INPUT MODEL

# 10.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16CE62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-Up Timer (OST) Brown-out Reset (BOD)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

The PIC16CE62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, and is designed to keep the part in reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 10.2 Oscillator Configurations

#### 10.2.1 OSCILLATOR TYPES

The PIC16CE62X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

# 10.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

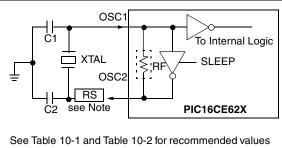

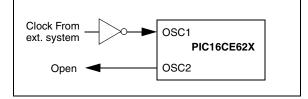

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 10-1). The PIC16CE62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 10-2).

#### FIGURE 10-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

See Table 10-1 and Table 10-2 for recommended values of C1 and C2.

Note: A series resistor may be required for AT strip cut crystals.

### FIGURE 10-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

#### TABLE 10-1: CERAMIC RESONATORS, PIC16CE62X

**Ranges Tested:** OSC2 Mode Freq OSC1 XT 455 kHz 68 - 100 pF 68 - 100 pF 15 - 68 pF 15 - 68 pF 2.0 MHz 4.0 MHz 15 - 68 pF 15 - 68 pF HS 10 - 68 pF 10 - 68 pF 8.0 MHz 16.0 MHz 10 - 22 pF 10 - 22 pF

These values are for design guidance only. See notes at bottom of page.

#### TABLE 10-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR, PIC16CE62X

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| XT       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

These values are for design guidance only. See notes at bottom of page.

- 1. Recommended values of C1 and C2 are identical to the ranges tested table.

- 2. Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- 3. Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

© 1998-2013 Microchip Technology Inc.

| CLRWDT           | Clear Watchdog Timer                                                                                                                                     |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] CLRWDT                                                                                                                                         |  |  |  |  |

| Operands:        | None                                                                                                                                                     |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                   |  |  |  |  |

| Encoding:        | 00 0000 0110 0100                                                                                                                                        |  |  |  |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$ are set.          |  |  |  |  |

| Words:           | 1                                                                                                                                                        |  |  |  |  |

| Cycles:          | 1                                                                                                                                                        |  |  |  |  |

| Example          | CLRWDT                                                                                                                                                   |  |  |  |  |

|                  | Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = 0x00<br>WDT prescaler= 0<br>TO = 1<br>PD = 1                                 |  |  |  |  |

| COMF             | Complement f                                                                                                                                             |  |  |  |  |

| Syntax:          | [label] COMF f,d                                                                                                                                         |  |  |  |  |

| COME             | Complement                                                                                                                                              |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] COMF f,d                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                             |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                     |  |  |  |  |

| Status Affected: | Z                                                                                                                                                       |  |  |  |  |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                       |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the result is<br>stored in W. If 'd' is 1, the result is<br>stored back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                       |  |  |  |  |

| Cycles:          | 1                                                                                                                                                       |  |  |  |  |

| Example          | COMF REG1,0                                                                                                                                             |  |  |  |  |

|                  | Before InstructionREG1= $0x13$ After InstructionREG1= $0x13$ W= $0xEC$                                                                                  |  |  |  |  |

|                  |                                                                                                                                                         |  |  |  |  |

| Decrement f                                                                                                                          |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                                                                                                                      |  |  |  |  |

| [label] DECF f,d                                                                                                                     |  |  |  |  |

| $0 \le f \le 127$                                                                                                                    |  |  |  |  |

| d ∈ [0,1]                                                                                                                            |  |  |  |  |

| (f) - 1 $\rightarrow$ (dest)                                                                                                         |  |  |  |  |

| Z                                                                                                                                    |  |  |  |  |

| 00 0011 dfff ffff                                                                                                                    |  |  |  |  |

| Decrement register 'f'. If 'd' is 0, the result is stored in the W register. If 'd' is 1, the result is stored back in register 'f'. |  |  |  |  |

| 1                                                                                                                                    |  |  |  |  |

| 1                                                                                                                                    |  |  |  |  |

| DECF CNT, 1                                                                                                                          |  |  |  |  |

| Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                |  |  |  |  |

| Decrement f, Skip if 0                                                                                                               |  |  |  |  |

| [ <i>label</i> ] DECFSZ f,d                                                                                                          |  |  |  |  |

| $0 \leq f \leq 127$                                                                                                                  |  |  |  |  |

| d ∈ [0,1]                                                                                                                            |  |  |  |  |

|                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                |                                                   |                                   |      |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------|------|--|--|

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                                                                                                                                                                                                                               |                                                   |                                   |      |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                           |                                                   |                                   |      |  |  |

| Encoding:        | 00                                                                                                                                                                                                                                                                                                                             | 1011                                              | dfff                              | ffff |  |  |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. |                                                   |                                   |      |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                                              |                                                   |                                   |      |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |                                                   |                                   |      |  |  |

| Example          | HERE DECFSZ CNT, 1<br>GOTO LOOP<br>CONTINUE •<br>•                                                                                                                                                                                                                                                                             |                                                   |                                   |      |  |  |

|                  | Before In<br>PC<br>After Inst<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC                                                                                                                                                                                                                                                           | = ado<br>ruction<br>= CN<br>= 0,<br>= ado<br>≠ 0, | iress HERE<br>T - 1<br>iress CONT |      |  |  |

| NOP              | No Operation  |      |      |      |  |  |  |  |  |

|------------------|---------------|------|------|------|--|--|--|--|--|

| Syntax:          | [ label ]     | NOP  |      |      |  |  |  |  |  |

| Operands:        | None          |      |      |      |  |  |  |  |  |

| Operation:       | No operation  |      |      |      |  |  |  |  |  |

| Status Affected: | None          |      |      |      |  |  |  |  |  |

| Encoding:        | 0 0           | 0000 | 0xx0 | 0000 |  |  |  |  |  |

| Description:     | No operation. |      |      |      |  |  |  |  |  |

| Words:           | 1             |      |      |      |  |  |  |  |  |

| Cycles:          | 1             |      |      |      |  |  |  |  |  |

| Example          | NOP           |      |      |      |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                             |        |          |      |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|------|--|--|--|--|

| Syntax:          | [label] F                                                                                                                                                                                                         | RETFIE |          |      |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                              |        |          |      |  |  |  |  |

| Operation:       | $TOS \rightarrow PC$ ,<br>1 $\rightarrow GIE$                                                                                                                                                                     |        |          |      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                              |        |          |      |  |  |  |  |

| Encoding:        | 0.0                                                                                                                                                                                                               | 0000   | 0000     | 1001 |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top of Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a two-cycle<br>instruction. |        |          |      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |        |          |      |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                 |        |          |      |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                            |        |          |      |  |  |  |  |

|                  | After Intern<br>PC<br>Gl                                                                                                                                                                                          |        | TOS<br>1 |      |  |  |  |  |

| OPTION                                       | Load Option Register                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                      | [ label ] OPTION                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Operands:                                    | None                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Operation:                                   | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Status Affected:                             | None                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Encoding:                                    | 00 0000 0110 0010                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Description:<br>Words:<br>Cycles:<br>Example | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code<br>compatibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly<br>address it.<br>1<br>1 |  |  |  |  |  |  |

|                                              | To maintain upward compatibility<br>with future PIC <sup>®</sup> MCU products, do<br>not use this instruction.                                                                                                                                             |  |  |  |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                 |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                   |

| Example          | CALL TABLE ;W contains table<br>;offset value<br>;W now has table<br>value                                                                                                          |

| TABLE            | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |

|                  | RETLW kn ; End of table                                                                                                                                                             |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                      |

|                  | After Instruction<br>W = value of k8                                                                                                                                                |

NOTES:

# 13.1 DC CHARACTERISTICS:

### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS |                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$                |        |      |           |            |                                                                   |

|--------------------|---------------------------|---------------------------------------------------------------------|--------|------|-----------|------------|-------------------------------------------------------------------|

| Param<br>No.       | Sym                       | Characteristic                                                      | Min    | Тур† | Max       | Units      | Conditions                                                        |

| D001               | Vdd                       | Supply Voltage                                                      | 3.0    | -    | 5.5       | V          | See Figure 13-1 through Figure 13-3                               |

| D002               | Vdr                       | RAM Data Retention<br>Voltage (Note 1)                              | -      | 1.5* | -         | V          | Device in SLEEP mode                                              |

| D003               | VPOR                      | VDD start voltage to<br>ensure Power-on Reset                       | -      | Vss  | -         | V          | See section on power-on reset for details                         |

| D004               | SVDD                      | VDD rise rate to ensure<br>Power-on Reset                           | 0.05*  | -    | -         | V/ms       | See section on power-on reset for details                         |

| D005               | VBOR                      | Brown-out Detect Voltage                                            | 3.7    | 4.0  | 4.35      | V          | BOREN configuration bit is cleared                                |

| D010               | IDD                       | Supply Current (Note 2, 4)                                          | -      | 1.2  | 2.0       | mA         | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)* |

|                    |                           |                                                                     | -      | 0.4  | 1.2       | mA         | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT osc mode, (Note 4)  |

|                    |                           |                                                                     | -      | 1.0  | 2.0       | mA         | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS osc mode, (Note 6) |

|                    |                           |                                                                     | -      | 4.0  | 6.0       | mA         | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS osc mode           |

|                    |                           |                                                                     | -      | 4.0  | 7.0       | mA         | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS osc mode          |

|                    |                           |                                                                     | -      | 35   | 70        | μA         | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP osc mode           |

| D020               | IPD                       | Power Down Current (Note 3)                                         | -      | -    | 2.2       | μA         | VDD = 3.0V                                                        |

|                    |                           |                                                                     | -      | -    | 5.0       | μA         | VDD = 4.5V*                                                       |

|                    |                           |                                                                     | _      | -    | 9.0<br>15 | μΑ<br>μΑ   | VDD = 5.5V<br>VDD = 5.5V Extended                                 |

| D022               | ΔIWDT                     | WDT Current (Note 5)                                                | - 1    | 6.0  | 10        | μΑ         | VDD = 4.0V                                                        |

|                    |                           |                                                                     |        |      | 12        | μA         | (125°C)                                                           |

| D022A              | $\Delta$ IBOR             | Brown-out Reset Current (Note 5)                                    | -      | 75   | 125       | μA         | BOD enabled, VDD = 5.0V                                           |

| D023               | ∆ICOMP                    | Comparator Current for each<br>Comparator (Note 5)                  | -      | 30   | 60        | μA         | VDD = 4.0V                                                        |

| D023A              | $\Delta$ IVREF            | VREF Current (Note 5)                                               | -      | 80   | 135       | μA         | VDD = 4.0V                                                        |

|                    | $\Delta \text{IEE Write}$ | Operating Current                                                   | -      |      | 3         | mA         | Vcc = 5.5V, SCL = 400 kHz                                         |

|                    | ∆IEE Read                 | Operating Current                                                   | -      |      | 1         | mA         |                                                                   |

|                    | ΔIEE                      | Standby Current                                                     | -      |      | 30        | μA         | $V_{CC} = 3.0V, EE V_{DD} = V_{CC}$                               |

| 4.4                | ΔIEE                      | Standby Current                                                     | -      |      | 100       | μΑ         | Vcc = 3.0V, EE VDD = Vcc                                          |

| 1A                 | Fosc                      | LP Oscillator Operating Frequency                                   | 0      | -    | 200       | kHz        | All temperatures                                                  |

|                    |                           | RC Oscillator Operating Frequency XT Oscillator Operating Frequency | 0<br>0 | _    | 4         | MHz<br>MHz | All temperatures<br>All temperatures                              |

|                    |                           | HS Oscillator Operating Frequency                                   | 0      | _    | 4<br>20   | MHz        | All temperatures                                                  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**6:** Commercial temperature range only.

#### 13.2 DC CHARACTERISTICS: F

#### PIC16LCE62X-04 (Commercial, Industrial)

| DC CHARACTERISTICS |                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$           |          |      |           |          |                                                                                  |  |  |

|--------------------|---------------------|----------------------------------------------------------------|----------|------|-----------|----------|----------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym                 | Characteristic                                                 | Min Typ† |      | Max       | Units    | Conditions                                                                       |  |  |

| D001               | Vdd                 | Supply Voltage                                                 | 2.5      | -    | 5.5       | V        | See Figure 13-1 through Figure 13-3                                              |  |  |

| D002               | Vdr                 | RAM Data Retention<br>Voltage (Note 1)                         | -        | 1.5* | -         | V        | Device in SLEEP mode                                                             |  |  |

| D003               | VPOR                | VDD start voltage to<br>ensure Power-on Reset                  | -        | Vss  | -         | V        | See section on power-on reset for details                                        |  |  |

| D004               | SVDD                | VDD rise rate to ensure<br>Power-on Reset                      | .05*     | -    | -         | V/ms     | See section on power-on reset for details                                        |  |  |

| D005               | VBOR                | Brown-out Detect Voltage                                       | 3.7      | 4.0  | 4.35      | V        | BOREN configuration bit is cleared                                               |  |  |

| D010               | IDD                 | Supply Current (Note 2)                                        | -        | 1.2  | 2.0       | mA       | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)*                |  |  |

|                    |                     |                                                                | -        | -    | 1.1       | mA       | FOSC = 4 MHz, VDD = 2.5V, WDT disabled,                                          |  |  |

|                    |                     |                                                                | -        | 35   | 70        | μA       | XT osc mode, (Note 4)<br>Fosc = 32 kHz, VDD = 2.5V, WDT disabled,<br>LP osc mode |  |  |

| D020               | IPD                 | Power Down Current (Note 3)                                    | _        | -    | 2.0       | μA       | VDD = 2.5V                                                                       |  |  |

|                    |                     |                                                                | -        | -    | 2.2       | μA       | VDD = 3.0V*                                                                      |  |  |

|                    |                     |                                                                | -        | -    | 9.0       | μA       | VDD = 5.5V                                                                       |  |  |

|                    |                     |                                                                | -        | -    | 15        | μA       | VDD = 5.5V Extended                                                              |  |  |

| D022               | $\Delta$ IWDT       | WDT Current (Note 5)                                           | -        | 6.0  | 10        | μA       | VDD=4.0V                                                                         |  |  |

| D022A              |                     | Brown-out Reset Current                                        | _        | 75   | 12<br>125 | μΑ<br>μΑ | $(125^{\circ}C)$<br>BOD enabled, VDD = 5.0V                                      |  |  |

| D023               |                     | (Note 5)<br>Comparator Current for each<br>Comparator (Note 5) | -        | 30   | 60        | μA       | VDD = 4.0V                                                                       |  |  |

| D023A              | $\Delta$ IVREF      | VREF Current (Note 5)                                          | -        | 80   | 135       | μA       | VDD = 4.0V                                                                       |  |  |