Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 13                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | 128 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 18-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce625-20-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 GENERAL DESCRIPTION

The PIC16CE62X are 18 and 20-Pin EPROM-based members of the versatile PIC<sup>®</sup> family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with EEPROM data memory.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16CE62X family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CE62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16CE623 and PIC16CE624 have 96 bytes of RAM. The PIC16CE625 has 128 bytes of RAM. Each microcontroller contains a 128x8 EEPROM memory array for storing non-volatile information, such as calibration data or security codes. This memory has an endurance of 1,000,000 erase/write cycles and a retention of 40 plus years.

Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16CE62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low-cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16CE62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and reset. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development, while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16CE62X mid-range microcontroller families.

A simplified block diagram of the PIC16CE62X is shown in Figure 3-1.

The PIC16CE62X series fits perfectly in applications ranging from multi-pocket battery chargers to low-power remote sensors. The EPROM technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high-performance, ease of use and I/O flexibility make the PIC16CE62X very versatile.

#### 1.1 <u>Development Support</u>

The PIC16CE62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler is also available.

| Name         | DIP/<br>SOIC<br>Pin # | SSOP<br>Pin #                   | l/O/P<br>Type | Buffer<br>Type          | Description                                                                                                                                                                                                       |

|--------------|-----------------------|---------------------------------|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                    | 18                              | I             | ST/CMOS                 | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT  | 15                    | 17                              | 0             | -                       | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp     | 4                     | 4                               | I/P           | ST                      | Master clear (reset) input/programming voltage input.<br>This pin is an active low reset to the device.                                                                                                           |

|              |                       |                                 |               |                         | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0      | 17                    | 19                              | I/O           | ST                      | Analog comparator input                                                                                                                                                                                           |

| RA1/AN1      | 18                    | 20                              | I/O           | ST                      | Analog comparator input                                                                                                                                                                                           |

| RA2/AN2/VREF | 1                     | 1                               | I/O           | ST                      | Analog comparator input or VREF output                                                                                                                                                                            |

| RA3/AN3      | 2                     | 2                               | I/O           | ST                      | Analog comparator input /output                                                                                                                                                                                   |

| RA4/T0CKI    | 3                     | 3                               | I/O           | ST                      | Can be selected to be the clock input to the Timer0<br>timer/counter or a comparator output. Output is open<br>drain type.                                                                                        |

|              |                       |                                 |               |                         | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                               |

| RB0/INT      | 6                     | 7                               | I/O           | TTL/ST(1)               | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                                        |

| RB1          | 7                     | 8                               | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB2          | 8                     | 9                               | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB3          | 9                     | 10                              | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB4          | 10                    | 11                              | I/O           | TTL                     | Interrupt on change pin.                                                                                                                                                                                          |

| RB5          | 11                    | 12                              | I/O           | TTL                     | Interrupt on change pin.                                                                                                                                                                                          |

| RB6          | 12                    | 13                              | I/O           | TTL/ST <sup>(2)</sup>   | Interrupt on change pin. Serial programming clock.                                                                                                                                                                |

| RB7          | 13                    | 14                              | I/O           | TTL/ST <sup>(2)</sup>   | Interrupt on change pin. Serial programming data.                                                                                                                                                                 |

| Vss          | 5                     | 5,6                             | Р             | l –                     | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| Vdd          | 14                    | 15,16                           | Р             | —                       | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Legend:      |                       | utput<br>Not used<br>: TTL inpu | 1:            | O = input/or<br>= Input | utput P = power<br>ST = Schmitt Trigger input                                                                                                                                                                     |

**TABLE 3-1: PIC16CE62X PINOUT DESCRIPTION**

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt. **Note 2:** This buffer is a Schmitt Trigger input when used in serial programming mode.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The special registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7                  | Bit 6              | Bit 5       | Bit 4         | Bit 3        | Bit 2        | Bit 1        | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>resets <sup>(1)</sup> |

|---------|---------------|------------------------|--------------------|-------------|---------------|--------------|--------------|--------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 00h     | INDF          | Addressin<br>register) | ig this locat      | ion uses co | ontents of F  | SR to addre  | ess data me  | emory (not a | a physical | xxxx xxxx             | xxxx xxxx                                      |

| 01h     | TMR0          | Timer0 M               | odule's Reg        | jister      |               |              |              |              |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          |              |              |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>     | RP1 <sup>(2)</sup> | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | I            |              | I          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         |                        |                    |             | RA4           | RA3          | RA2          | RA1          | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                    | RB6                | RB5         | RB4           | RB3          | RB2          | RB1          | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h     | Unimplemented |                        | 1                  |             | 1             |              | 1            |              | 1          | -                     | -                                              |

| 08h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 09h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 0Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | —                      | CMIF               | —           | —             | —            | —            | —            | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                        |                    |             |               |              |              |              |            | —                     | _                                              |

| 1Fh     | CMCON         | C2OUT                  | C10UT              | _           |               | CIS          | CM2          | CM1          | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 80h     | INDF          | Addressin<br>register) | ig this locat      | ion uses co | ontents of F  | SR to addre  | ess data me  | emory (not a | a physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                   | INTEDG             | TOCS        | T0SE          | PSA          | PS2          | PS1          | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          | 1            |              | 1          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP                    | RP1                | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | 1            |              | 1          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                      |                    |             | TRISA4        | TRISA3       | TRISA2       | TRISA1       | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7                 | TRISB6             | TRISB5      | TRISB4        | TRISB3       | TRISB2       | TRISB1       | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 88h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 89h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | T0IF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                      | CMIE               | _           | —             | _            | —            | _            | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Eh     | PCON          | —                      | —                  | —           | _             | —            | —            | POR          | BOD        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 90h     | EEINTF        | —                      | —                  | —           | _             | —            | EESCL        | EESDA        | EEVDD      | 111                   | 111                                            |

| 9Fh     | VRCON         | VREN                   | VROE               | VRR         | _             | VR3          | VR2          | VR1          | VR0        | 000- 0000             | 000- 0000                                      |

#### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16CE62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non power-up) resets include MCLR reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

Note 2: IRP & RPI bits are reserved; always maintain these bits clear.

#### 4.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the status register as 000uu1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any status bit. For other instructions, not affecting any status bits, see the "Instruction Set Summary".

| Note 1: | The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16CE62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products. |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note 2: | The <u>C</u> and <u>DC</u> bits operate as a Borrow<br>and Digit Borrow out bit, respectively, in<br>subtraction. See the SUBLW and SUBWF<br>instructions for examples.                                                               |

#### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

| Reserved    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0       | R-1         | R-1         | R/W-x                          | R/W-x       | R/W-x          |              |             |                                                                                                                 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|--------------------------------|-------------|----------------|--------------|-------------|-----------------------------------------------------------------------------------------------------------------|

| IRP<br>bit7 | RP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RP0         | TO          | PD          | Z                              | DC          | C<br>bit0      | W<br>U<br>-n | =<br>=<br>= | Readable bit<br>Writable bit<br>Unimplemented bit,<br>read as '0'<br>Value at POR reset<br>Unknown at POR reset |

| bit 7:      | IRP: The I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RP bit is r | eserved o   | n the PIC1  | 6CE62X, al                     | lways main  | itain this bit |              |             | Unknown at FUR leset                                                                                            |

| bit 6:5     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |             |             |                                |             |                |              |             |                                                                                                                 |

| bit 4:      | TO: Time-out bit<br>1 = After power-up, CLRWDT instruction, or SLEEP instruction<br>0 = A WDT time-out occurred                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |             |             |                                |             |                |              |             |                                                                                                                 |

| bit 3:      | <b>PD</b> : Power<br>1 = After p<br>0 = By exe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ower-up o   | or by the C |             |                                |             |                |              |             |                                                                                                                 |

| bit 2:      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | sult of an  |             |             | peration is z<br>peration is r |             |                |              |             |                                                                                                                 |

| bit 1:      | 1 = A carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | y-out from  | the 4th lo  | w order bit | of the resu                    | It occurred |                | or bor       | row         | the polarity is reversed)                                                                                       |

| bit 0:      | <ul> <li>0 = No carry-out from the 4th low order bit of the result</li> <li>C: Carry/borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions)</li> <li>1 = A carry-out from the most significant bit of the result occurred</li> <li>0 = No carry-out from the most significant bit of the result occurred</li> <li>Note: For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of the source register.</li> </ul> |             |             |             |                                |             |                |              |             |                                                                                                                 |

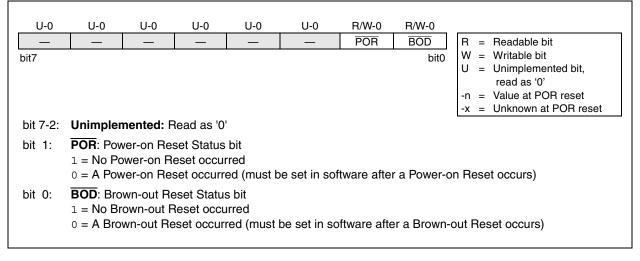

#### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset, an external  $\overline{\text{MCLR}}$  reset, WDT reset or a Brown-out Reset.

| Note: | BOD is unknown on Power-on Reset. It        |

|-------|---------------------------------------------|

|       | must then be set by the user and checked    |

|       | on subsequent resets to see if BOD is       |

|       | cleared, indicating a brown-out has         |

|       | occurred. The BOD status bit is a "don't    |

|       | care" and is not necessarily predictable if |

|       | the brown-out circuit is disabled (by       |

|       | programming BODEN bit in the                |

|       | configuration word).                        |

#### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

NOTES:

#### 6.5 <u>Read Operation</u>

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the EEPROM address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

#### 6.6 Current Address Read

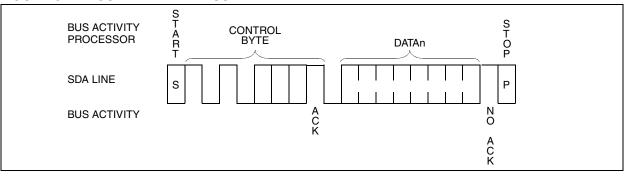

The EEPROM contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the EEPROM address with R/W bit set to one, the EEPROM issues an acknowledge and transmits the eight bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-7).

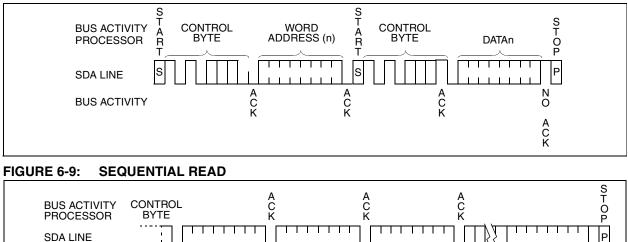

#### 6.7 Random Read

Random read operations allow the processor to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the EEPROM as part of a write operation. After the word address is sent, the processor generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the processor issues the control byte again, but with the R/W bit set to a one. The EEPROM will then issue an acknowledge and transmits the eight bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-8).

#### 6.8 Sequential Read

Sequential reads are initiated in the same way as a random read except that after the EEPROM transmits the first data byte, the processor issues an acknowledge as opposed to a stop condition in a random read. This directs the EEPROM to transmit the next sequentially addressed 8-bit word (Figure 6-9).

To provide sequential reads, the EEPROM contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation.

#### 6.9 Noise Protection

The EEPROM employs a Vcc threshold detector circuit, which disables the internal erase/write logic if the Vcc is below 1.5 volts at nominal conditions.

The SCL and SDA inputs have Schmitt trigger and filter circuits, which suppress noise spikes to assure proper device operation even on a noisy bus.

#### FIGURE 6-8: RANDOM READ

BUS ACTIVITY

. .

A C K

DATAn

DATAn + 1

DATAn + 2

N O

A C K

DATAn + X

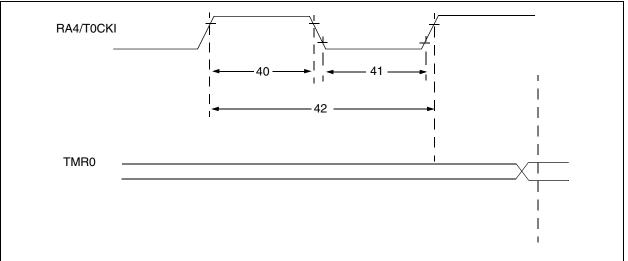

#### 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

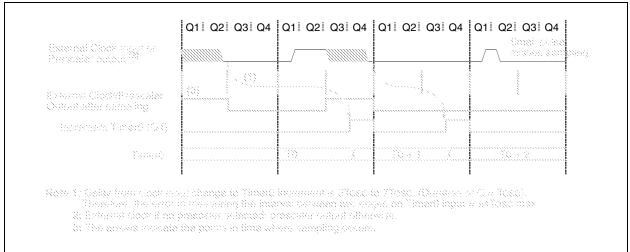

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

The code example in Example 8-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 8-1: INITIALIZING COMPARATOR MODULE

| FLAG_REG | F EQU        | 0X20                              |

|----------|--------------|-----------------------------------|

| CLRF     | FLAG_REG     | ;Init flag register               |

| CLRF     | PORTA        | ;Init PORTA                       |

| MOVF     | CMCON,W      | ;Move comparator contents to W    |

| ANDLW    | 0xC0         | ;Mask comparator bits             |

| IORWF    | FLAG_REG,F   | ;Store bits in flag register      |

| MOVLW    | 0x03         | ;Init comparator mode             |

| MOVWF    | CMCON        | ;CM<2:0> = 011                    |

| BSF      | STATUS, RPO  | ;Select Bank1                     |

| MOVLW    | 0x07         | ;Initialize data direction        |

| MOVWF    | TRISA        | ;Set RA<2:0> as inputs            |

|          |              | ;RA<4:3> as outputs               |

|          |              | ;TRISA<7:5> always read `0'       |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| CALL     | DELAY 10     | ;10µs delay                       |

| MOVF     | CMCON, F     | ;Read CMCONtoend change condition |

| BCF      | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF      | STATUS, RPO  | ;Select Bank 1                    |

| BSF      | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| BSF      | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF      | INTCON, GIE  | ;Global interrupt enable          |

|          |              |                                   |

#### 8.2 Comparator Operation

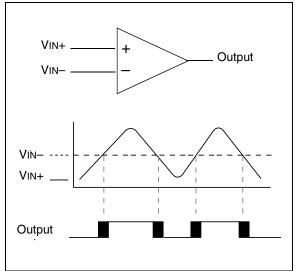

A single comparator is shown in Figure 8-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN–, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN–, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 8-2 represent the uncertainty due to input offsets and response time.

#### 8.3 <u>Comparator Reference</u>

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal that is present at VIN– is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 8-2).

FIGURE 8-2: SINGLE COMPARATOR

#### 8.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 8.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 8-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

#### 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

#### 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

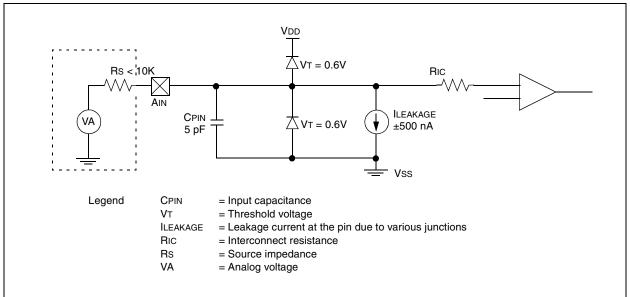

#### 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 8-4: ANALOG INPUT MODEL

| Name   | Bit 7                                    | Bit 6                                                   | Bit 5                                                       | Bit 4                                                            | Bit 3                                                                        | Bit 2                                                                                     | Bit 1                                                                                                 | Bit 0                                                                                                             | Value on:<br>POR                                                                                                              | Value on<br>All Other<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMCON  | C2OUT                                    | C1OUT                                                   |                                                             | _                                                                | CIS                                                                          | CM2                                                                                       | CM1                                                                                                   | CM0                                                                                                               | 00 0000                                                                                                                       | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VRCON  | VREN                                     | VROE                                                    | VRR                                                         | —                                                                | VR3                                                                          | VR2                                                                                       | VR1                                                                                                   | VR0                                                                                                               | 000- 0000                                                                                                                     | 000- 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTCON | GIE                                      | PEIE                                                    | TOIE                                                        | INTE                                                             | RBIE                                                                         | T0IF                                                                                      | INTF                                                                                                  | RBIF                                                                                                              | 0000 000x                                                                                                                     | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PIR1   | _                                        | CMIF                                                    |                                                             | _                                                                | _                                                                            |                                                                                           | _                                                                                                     | _                                                                                                                 | -0                                                                                                                            | -0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PIE1   | —                                        | CMIE                                                    | —                                                           | —                                                                | —                                                                            | —                                                                                         | —                                                                                                     | —                                                                                                                 | -0                                                                                                                            | -0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TRISA  | —                                        | —                                                       | _                                                           | TRISA4                                                           | TRISA3                                                                       | TRISA2                                                                                    | TRISA1                                                                                                | TRISA0                                                                                                            | 1 1111                                                                                                                        | 1 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | CMCON<br>VRCON<br>INTCON<br>PIR1<br>PIE1 | CMCON C2OUT<br>VRCON VREN<br>INTCON GIE<br>PIR1<br>PIE1 | CMCONC2OUTC1OUTVRCONVRENVROEINTCONGIEPEIEPIR1-CMIFPIE1-CMIE | CMCONC2OUTC1OUTVRCONVRENVROEVRRINTCONGIEPEIETOIEPIR1CMIFPIE1CMIE | CMCONC2OUTC1OUT—VRCONVRENVROEVRR—INTCONGIEPEIETOIEINTEPIR1—CMIF——PIE1I—CMIEI | CMCONC2OUTC1OUT——CISVRCONVRENVROEVRR—VR3INTCONGIEPEIET0IEINTERBIEPIR1—CMIF———PIE1—CMIE——— | CMCONC2OUTC1OUT——CISCM2VRCONVRENVROEVRR—VR3VR2INTCONGIEPEIETOIEINTERBIETOIFPIR1—CMIF————PIE1—CMIE———— | CMCONC2OUTC1OUT——CISCM2CM1VRCONVRENVROEVRR—VR3VR2VR1INTCONGIEPEIET0IEINTERBIET0IFINTFPIR1—CMIF—————PIE1—CMIE————— | CMCONC2OUTC1OUT——CISCM2CM1CM0VRCONVRENVROEVRR—VR3VR2VR1VR0INTCONGIEPEIETOIEINTERBIETOIFINTFRBIFPIR1—CMIF——————PIE1—CMIE—————— | Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         POR           CMCON         C2OUT         C1OUT         —         —         CIS         CM2         CM1         CM0         00 0000           VRCON         VREN         VROE         VRR         —         VR3         VR2         VR1         VR0         000- 0000           INTCON         GIE         PEIE         T0IE         INTE         RBIE         T0IF         INTF         RBIF         0000 000x           PIR1         —         CMIE         —         —         —         —         —         -         -0         -0           PIE1         —         CMIE         —         —         —         —         —         -         -0         - |

TABLE 8-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: - = Unimplemented, read as "0", x = Unknown, u = unchanged

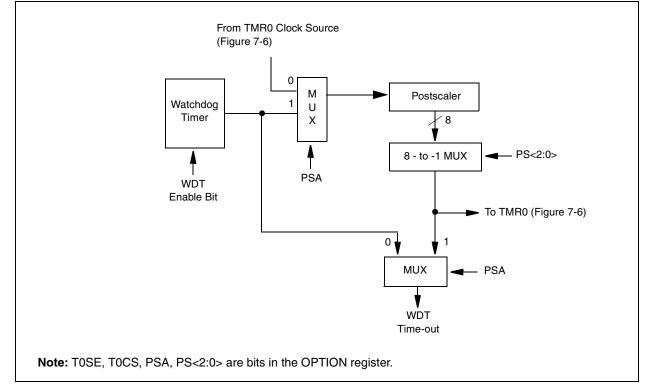

#### FIGURE 10-17: WATCHDOG TIMER BLOCK DIAGRAM

#### FIGURE 10-18: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits |       | BOREN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION       | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: - = Unimplemented location, read as "0", + = Reserved for future use

Note: Shaded cells are not used by the Watchdog Timer.

| RETURN             | Return from Subroutine                                                                                              | RRF              | Rotate Right f through Carry                                                                                                                                                                                                               |

|--------------------|---------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:            | [label] RETURN                                                                                                      | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                   |

| Operands:          | None                                                                                                                | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                          |

| Operation:         | $TOS \rightarrow PC$                                                                                                |                  | $d \in [0,1]$                                                                                                                                                                                                                              |

| Status Affected:   | None                                                                                                                | Operation:       | See description below                                                                                                                                                                                                                      |

| Encoding:          | 00 0000 0000 1000                                                                                                   | Status Affected: | С                                                                                                                                                                                                                                          |

| Description:       | Return from subroutine. The stack is                                                                                | Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                                                          |

|                    | POPed and the top of the stack (TOS)Description:is loaded into the program counter.This is a two cycle instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is                                                             |

| Words:             | 1                                                                                                                   |                  | placed back in register 'f'.                                                                                                                                                                                                               |

| Cycles:<br>Example | 2<br>RETURN                                                                                                         |                  | C Register f                                                                                                                                                                                                                               |

|                    | After Interrupt                                                                                                     | Words:           | 1                                                                                                                                                                                                                                          |

|                    | PC = TOS                                                                                                            | Cycles:          | 1                                                                                                                                                                                                                                          |

|                    |                                                                                                                     | Example          | RRF REG1,0                                                                                                                                                                                                                                 |

|                    |                                                                                                                     |                  | Before Instruction       REG1       =       1110       0110         C       =       0       0         After Instruction       REG1       =       1110       0110         W       =       0111       0011         C       =       0       0 |

| RLF              | Rotate Left f t                                                   | hrough Carry                                                                                                                |         |

|------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|

| Syntax:          | [label] RLF                                                       | f,d                                                                                                                         |         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$ |                                                                                                                             |         |

| Operation:       | See description                                                   | n below                                                                                                                     |         |

| Status Affected: | С                                                                 |                                                                                                                             |         |

| Encoding:        | 00 110                                                            | 1 dfff ff                                                                                                                   | ff      |

| Description:     | one bit to the left<br>Flag. If 'd' is 0, th                      | register 'f' are rota<br>t through the Carry<br>ne result is placed<br>f 'd' is 1, the result<br>egister 'f'.<br>Register f | /<br>in |

| Words:           | 1                                                                 |                                                                                                                             |         |

| Cycles:          | 1                                                                 |                                                                                                                             |         |

|                  |                                                                   |                                                                                                                             |         |

| Example          | RLF                                                               | REG1,0                                                                                                                      |         |

### SLEEP

| 02221            |                                                                                                                                                                                                                                                |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                                |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                           |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                           |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                         |  |  |  |  |

| Encoding:        | 00 0000 0110 0011                                                                                                                                                                                                                              |  |  |  |  |

| Description:     | The power-down status bit, PD is<br>cleared. Time-out status bit, TO is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 10.8 for more details. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                              |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                              |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                          |  |  |  |  |

#### 13.3 DC CHARACTERISTICS:

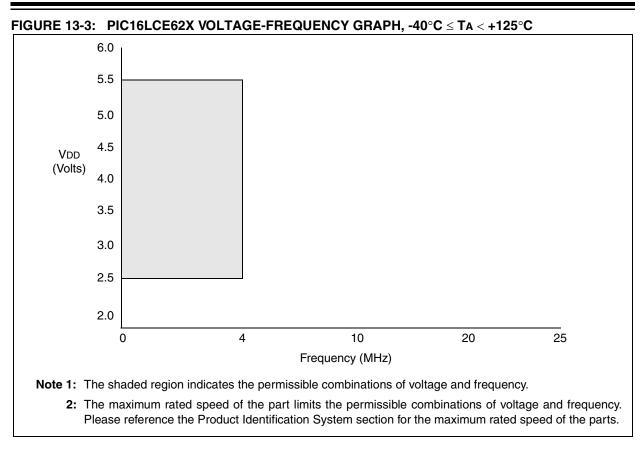

#### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended) PIC16LCE62X (Commercial, Industrial)

|                    |       |                                                                 | Standard Opera                                                 | ting ( | Conditions (u | Inles | s otherwise stated)                             |  |  |  |

|--------------------|-------|-----------------------------------------------------------------|----------------------------------------------------------------|--------|---------------|-------|-------------------------------------------------|--|--|--|

|                    |       |                                                                 |                                                                |        |               |       | +85°C for industrial and                        |  |  |  |

| DC CHARACTERISTICS |       |                                                                 | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial and      |        |               |       |                                                 |  |  |  |

|                    |       |                                                                 | $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended           |        |               |       |                                                 |  |  |  |

|                    |       |                                                                 | Operating voltage VDD range as described in DC spec Table 13-1 |        |               |       |                                                 |  |  |  |

| Parm               | Sym   | Characteristic                                                  | Min                                                            | Typ†   | Max           | Unit  | Conditions                                      |  |  |  |

| No.                |       |                                                                 |                                                                |        |               |       |                                                 |  |  |  |

|                    | Vi∟   | Input Low Voltage                                               |                                                                |        |               |       |                                                 |  |  |  |

|                    |       | I/O ports                                                       |                                                                |        |               |       |                                                 |  |  |  |

| D030               |       | with TTL buffer                                                 | Vss                                                            | _      | 0.8V          | V     | VDD = 4.5V to 5.5V, Otherwise                   |  |  |  |

|                    |       |                                                                 |                                                                |        | 0.15VDD       |       |                                                 |  |  |  |

| D031               |       | with Schmitt Trigger input                                      | Vss                                                            |        | 0.2VDD        | V     |                                                 |  |  |  |

| D032               |       | MCLR, RA4/T0CKI,OSC1 (in RC                                     | Vss                                                            | -      | 0.2VDD        | V     | Note1                                           |  |  |  |

|                    |       | mode)                                                           |                                                                |        |               |       |                                                 |  |  |  |

| D033               |       | OSC1 (in XT and HS)                                             | Vss                                                            | -      | 0.3Vdd        | V     |                                                 |  |  |  |

|                    |       | OSC1 (in LP)                                                    | Vss                                                            | -      | 0.6VDD - 1.0  | V     |                                                 |  |  |  |

|                    | VIH   | Input High Voltage                                              |                                                                |        |               |       |                                                 |  |  |  |

|                    |       | I/O ports                                                       |                                                                |        |               |       |                                                 |  |  |  |

| D040               |       | with TTL buffer                                                 | 2.0V                                                           | -      | VDD           | V     | VDD = 4.5V to 5.5V, Otherwise                   |  |  |  |

| <b>D</b> 044       |       |                                                                 | .25VDD + 0.8V                                                  |        | VDD           |       |                                                 |  |  |  |

| D041               |       | with Schmitt Trigger input                                      | 0.8VDD                                                         |        | VDD           | .,    |                                                 |  |  |  |

| D042               |       | MCLR RA4/T0CKI                                                  | 0.8VDD                                                         | -      | VDD           | V     |                                                 |  |  |  |

| D043<br>D043A      |       | OSC1 (XT, HS and LP)                                            | 0.7Vdd<br>0.9Vdd                                               | -      | Vdd           | V     | Note1                                           |  |  |  |