Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | ОТР                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce625-20e-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 1-1: PIC16CE62X FAMILY OF DEVICES

|             |                                      | PIC16CE623                          | PIC16CE624                          | PIC16CE625                          |

|-------------|--------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                  | 20                                  | 20                                  |

| Momoriy     | EPROM Program Memory (x14 words)     | 512                                 | 1K                                  | 2K                                  |

| Memory      | Data Memory (bytes)                  | 96                                  | 96                                  | 128                                 |

|             | EEPROM Data Memory (bytes)           | 128                                 | 128                                 | 128                                 |

| Peripherals | Timer Module(s)                      | TMR0                                | TMR0                                | TMR0                                |

| Peripherais | Comparators(s)                       | 2                                   | 2                                   | 2                                   |

|             | Internal Reference Voltage           | Yes                                 | Yes                                 | Yes                                 |

|             | Interrupt Sources                    | 4                                   | 4                                   | 4                                   |

|             | I/O Pins                             | 13                                  | 13                                  | 13                                  |

|             | Voltage Range (Volts)                | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                             |

| Features    | Brown-out Reset                      | Yes                                 | Yes                                 | Yes                                 |

|             | Packages                             | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

All PIC<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16CE62X Family devices use serial programming with clock pin RB6 and data pin RB7.

NOTES:

## 5.3 <u>I/O Programming Considerations</u>

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read modify write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (i.e.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ; ; PORTB<7:6> have external pull-up and are not ; connected to other circuitry ; PORT latch PORT pins ; ; BCF PORTB. 7 ; 01pp pppp 11pp pppp BCF PORTB, 6 ;10pp pppp 11pp pppp BSF STATUS, RPO ; BCF TRISB, 7 ; 10pp pppp 11pp pppp BCF TRISB, 6 ;10pp pppp 10pp pppp ; ; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused ; RB7 to be latched as the pin value (High).

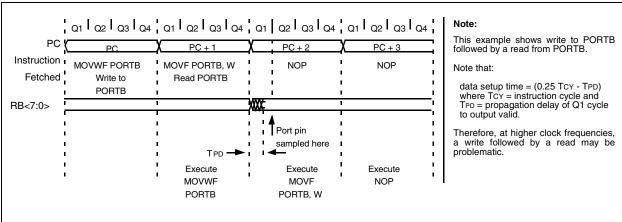

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with an NOP or another instruction not accessing this I/O port.

#### FIGURE 5-7: SUCCESSIVE I/O OPERATION

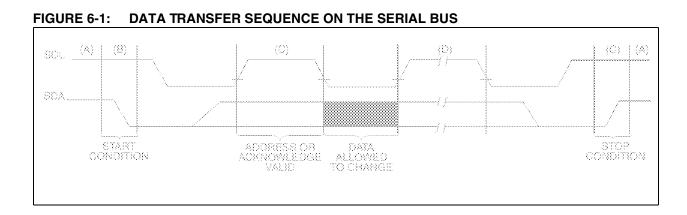

### 6.1 Bus Characteristics

In this section, the term "processor" refers to the portion of the PIC16CE62X that interfaces to the EEPROM through software manipulating the EEINTF register. The following **bus protocol** is to be used with the EEPROM data memory.

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted by the EEPROM as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 6-1).

#### 6.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

#### 6.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### 6.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### 6.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the processor and is theoretically unlimited, although only the last sixteen will be stored when doing a write operation. When an overwrite does occur, it will replace data in a first-in, first-out fashion.

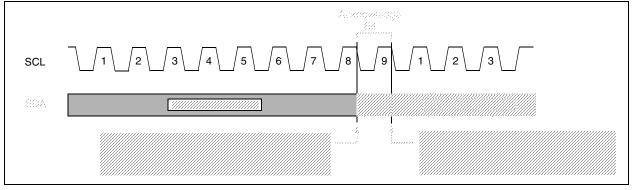

#### 6.1.5 ACKNOWLEDGE

The EEPROM will generate an acknowledge after the reception of each byte. The processor must generate an extra clock pulse which is associated with this acknowledge bit.

| Note: | Acknowledge bits are not generated if an   |

|-------|--------------------------------------------|

|       | internal programming cycle is in progress. |

When the EEPROM acknowledges, it pulls down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. The processor must signal an end of data to the EEPROM by not generating an acknowledge bit on the last byte that has been clocked out of the EEPROM. In this case, the EEPROM must leave the data line HIGH to enable the processor to generate the STOP condition (Figure 6-2).

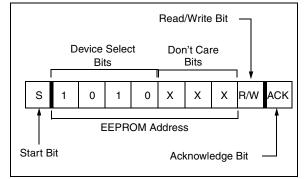

## 6.2 Device Addressing

After generating a START condition, the processor transmits a control byte consisting of a EEPROM address and a Read/Write bit that indicates what type of operation is to be performed. The EEPROM address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one, a read operation is selected, and when set to a zero, a write operation is selected. (Figure 6-3). The bus is monitored for its corresponding EEPROM address all the time. It generates an acknowledge bit if the EEPROM address was true and it is not in a programming mode.

## FIGURE 6-3: CONTROL BYTE FORMAT

#### 6.3 Write Operations

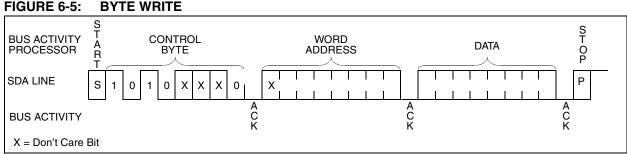

#### BYTE WRITE 6.3.1

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the R/W bit, which is a logic low, is placed onto the bus by the processor. This indicates to the EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer of the EEPROM. After receiving another acknowledge signal from the EEPROM, the processor will transmit the data word to be written into the addressed memory location. The EEPROM acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time, the EEPROM will not generate acknowledge signals (Figure 6-5).

#### 6.3.2 PAGE WRITE

The write control byte, word address and the first data byte are transmitted to the EEPROM in the same way as in a byte write. But instead of generating a stop condition, the processor transmits up to eight data bytes to the EEPROM, which are temporarily stored in the onchip page buffer and will be written into the memory after the processor has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the processor should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin (Figure 6-6).

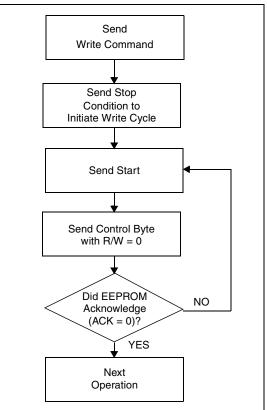

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the EEPROM initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. See Figure 6-4 for flow diagram.

#### FIGURE 6-4: ACKNOWLEDGE POLLING FLOW

## FIGURE 6-5:

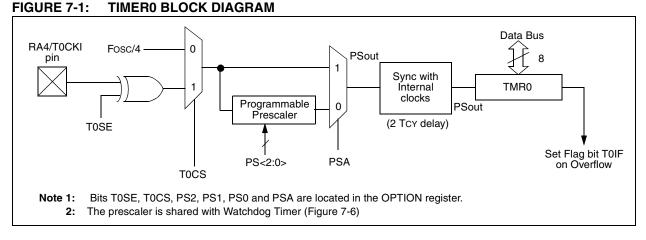

# 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

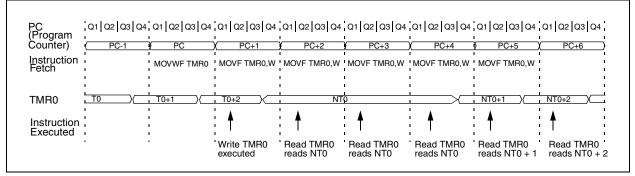

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

## 7.1 <u>Timer0 Interrupt</u>

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

## FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

NOTES:

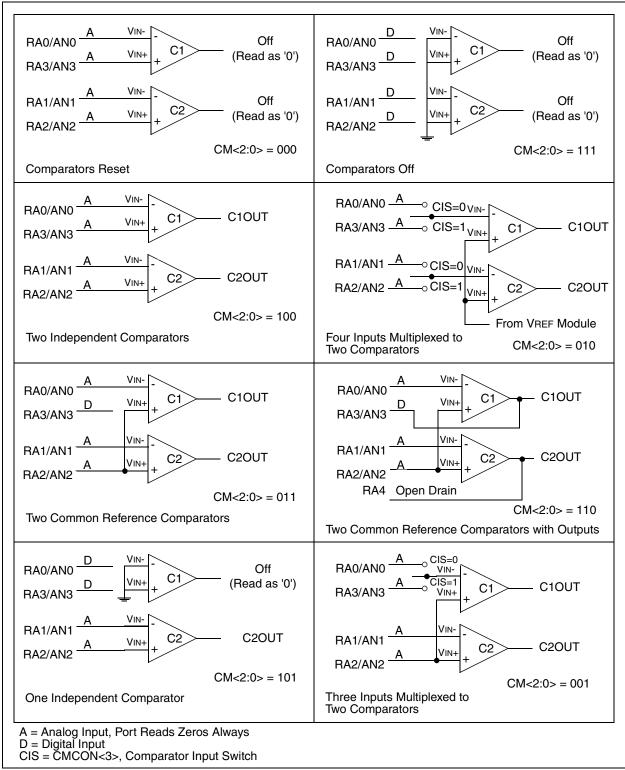

## 8.1 <u>Comparator Configuration</u>

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 8-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 13-1.

Note: Comparator interrupts should be disabled during a comparator mode change, otherwise a false interrupt may occur.

FIGURE 8-1: COMPARATOR I/O OPERATING MODES

#### 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs, otherwise the maximum delay of the comparators should be used (Table 13-1).

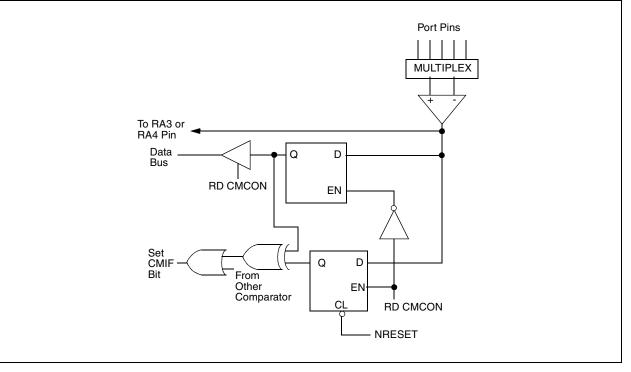

### 8.5 <u>Comparator Outputs</u>

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 8-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

## FIGURE 8-3: COMPARATOR OUTPUT BLOCK DIAGRAM

# 11.0 INSTRUCTION SET SUMMARY

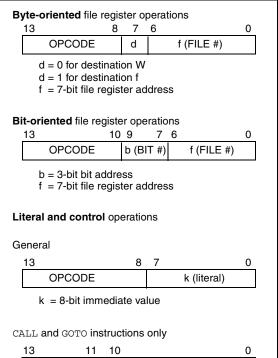

Each PIC16CE62X instruction is a 14-bit word divided into an OPCODE which specifies the instruction type and one or more operands which further specify the operation of the instruction. The PIC16CE62X instruction set summary in Table 11-2 lists **byte-oriented**, **bit-oriented**, and **literal and control** operations. Table 11-1 shows the opcode field descriptions.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an eight or eleven bit constant or literal value.

# TABLE 11-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                                    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                                           |

| W             | Working register (accumulator)                                                                                                                                                 |

| b             | Bit address within an 8-bit file register                                                                                                                                      |

| k             | Literal field, constant data or label                                                                                                                                          |

| x             | Don't care location (= 0 or 1)<br>The assembler will generate code with $x = 0$ . It is the<br>recommended form of use for compatibility with all<br>Microchip software tools. |

| d             | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1                                                                   |

| label         | Label name                                                                                                                                                                     |

| TOS           | Top of Stack                                                                                                                                                                   |

| PC            | Program Counter                                                                                                                                                                |

| PCLATH        | Program Counter High Latch                                                                                                                                                     |

| GIE           | Global Interrupt Enable bit                                                                                                                                                    |

| WDT           | Watchdog Timer/Counter                                                                                                                                                         |

| TO            | Time-out bit                                                                                                                                                                   |

| PD            | Power-down bit                                                                                                                                                                 |

| dest          | Destination either the W register or the specified register file location                                                                                                      |

| []            | Options                                                                                                                                                                        |

| ()            | Contents                                                                                                                                                                       |

| $\rightarrow$ | Assigned to                                                                                                                                                                    |

| <>            | Register bit field                                                                                                                                                             |

| ∈             | In the set of                                                                                                                                                                  |

| italics       | User defined term (font is courier)                                                                                                                                            |

The instruction set is highly orthogonal and is grouped into three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

All instructions are executed within one single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles with the second cycle executed as a NOP. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Table 11-1 lists the instructions recognized by the MPASM assembler.

Figure 11-1 shows the three general formats that the instructions can have.

| Note: |      |                        |           | compatibility          |              |

|-------|------|------------------------|-----------|------------------------|--------------|

|       | futu | ire PIC <sup>®</sup> M | ICU produ | ucts, <u>do not us</u> | <u>e</u> the |

|       | OPI  | TION and 1             | rris inst | ructions.              |              |

All examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

# FIGURE 11-1: GENERAL FORMAT FOR INSTRUCTIONS

<sup>13 11 10</sup> OPCODE k (literal)

k = 11-bit immediate value

| GOTO                              | Unconditional Branch                                                                                                                                                                               | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [ <i>label</i> ] GOTO k                                                                                                                                                                            | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:                         | $0 \le k \le 2047$                                                                                                                                                                                 | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                              |

| Operation:                        | $k \rightarrow PC < 10:0 >$                                                                                                                                                                        |                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                      |

|                                   | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected:                  | None                                                                                                                                                                                               | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |

| Encoding:                         | 10 1kkk kkkk kkkk                                                                                                                                                                                  | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                              |

| Description:<br>Words:<br>Cycles: | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.<br>1 | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. |

| Example                           | GOTO THERE                                                                                                                                                                                         | Words:           | 1                                                                                                                                                                                                                                                                                                                              |

|                                   | After Instruction<br>PC = Address THERE                                                                                                                                                            | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |

|                                   | FC = Addless There                                                                                                                                                                                 | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                    |                  | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                    |                  | •                                                                                                                                                                                                                                                                                                                              |

$\begin{array}{rcl} Before \ Instruction \\ PC &= & address \ HERE \\ After \ Instruction \\ CNT &= & CNT + 1 \\ if \ CNT = & 0, \\ PC &= & address \ CONTINUE \\ if \ CNT \neq & 0, \\ PC &= & address \ HERE \ +1 \\ \end{array}$

| INCF             | Increment f                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                   |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                   |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |

| Words:           | 1                                                                                                                                                                   |

| Cycles:          | 1                                                                                                                                                                   |

| Example          | INCF CNT, 1                                                                                                                                                         |

|                  | Before Instruction $CNT = 0xFF$ $Z = 0$ After Instruction $CNT = 0x00$ $Z = 1$                                                                                      |

| IORLW            | Inclusive OR Literal with W                                                                                            |  |  |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                               |  |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                      |  |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                           |  |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |  |  |  |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                      |  |  |  |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                      |  |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                      |  |  |  |  |  |  |  |  |

| Example          | IORLW 0x35                                                                                                             |  |  |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                               |  |  |  |  |  |  |  |  |

TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                          | PIC120 | PIC14 | PIC160 | 91019 | PIC160 | PIC16F | PIC16 | PIC16C | PIC160 | PIC16F | PIC16C | DTFOIG | 22121919 | PIC18C) | 83CX<br>52CX | кхээн | мсвех | WCP25 |

|----------------------------------------------------------|--------|-------|--------|-------|--------|--------|-------|--------|--------|--------|--------|--------|----------|---------|--------------|-------|-------|-------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment | >      | >     | >      | >     | >      | >      | >     | >      | >      | >      | >      | >      | >        | >       |              |       |       |       |

|                                                          |        |       |        |       |        |        |       |        |        |        |        | >      | >        |         |              |       |       |       |

| MPLAB <sup>®</sup> C18 Compiler                          |        |       |        |       |        |        |       |        |        |        |        |        |          | >       |              |       |       |       |

| B MPASM/MPLINK                                           | >      | >     | >      | >     | >      | >      | >     | >      | >      | >      | >      | >      | >        | >       | >            | >     |       |       |

| 2 MPLAB <sup>®</sup> -ICE                                | >      | >     | >      | >     | >      | **`    | >     | >      | >      | >      | >      | >      | >        | >       |              |       |       |       |

| PICMASTER/PICMASTER-CE                                   | >      | >     | ~      | >     | >      |        | >     | >      | ~      |        | >      | ~      | ~        |         |              |       |       |       |

| E ICEPIC™ Low-Cost<br>III In-Circuit Emulator            | `      |       | >      | >     | >      |        | >     | >      | >      |        | ~      |        |          |         |              |       |       |       |

| MPLAB <sup>®</sup> -ICD In-Circuit<br>Debugger<br>De     |        |       |        | *>    |        |        | *>    |        |        | >      |        |        |          |         |              |       |       |       |

| 20 PICSTART®Plus<br>E Low-Cost Universal Dev. Kit        | ~      | >     | >      | `     | `      | ×**    | `     | `      | `      | >      | >      | ~      | `        | `       |              |       |       |       |

| ଅଟେ PRO MATE® I<br>Universal Programmer<br>ଦ             | >      | >     | >      | >     | >      | **/    | >     | >      | >      | >      | >      | ~      | ~        | ~       | >            | >     |       |       |

| SIMICE                                                   | >      |       | >      |       |        |        |       |        |        |        |        |        |          |         |              |       |       |       |

| PICDEM-1                                                 |        |       | ~      |       | >      |        | <↓    |        | ~      |        |        | ~      |          |         |              |       |       |       |

| PICDEM-2                                                 |        |       |        | à     |        |        | à     |        |        |        |        |        |          | ~       |              |       |       |       |

| 2 PICDEM-3                                               |        |       |        |       |        |        |       |        |        |        | ~      |        |          |         |              |       |       |       |

| PICDEM-14A                                               |        | >     |        |       |        |        |       |        |        |        |        |        |          |         |              |       |       |       |

| PICDEM-17                                                |        |       |        |       |        |        |       |        |        |        |        |        | ~        |         |              |       |       |       |

| E KEELoo® Evaluation Kit                                 |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              | >     |       |       |

| KEELOQ Transponder Kit                                   |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              | >     |       |       |

| microlD™ Programmer's Kit                                |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       | ~     |       |

| 125 kHz microID Developer's Kit                          |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       | >     |       |

| 25 kHz Anticollision microlD<br>Developer's Kit          |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       | >     |       |

| 13.56 MHz Anticollision microID<br>Developer's Kit       |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       | >     |       |

| MCP2510 CAN Developer's Kit                              |        |       |        |       |        |        |       |        |        |        |        |        |          |         |              |       |       | >     |

ğ Contact Microcrip reciniology inc. for availability <sup>†</sup> Development tool is available on select devices.

#### 13.2 DC CHARACTERISTICS: F

#### PIC16LCE62X-04 (Commercial, Industrial)

| DC CH        | ARACTERI            | STICS                                                          |      |      |           |                  |                                                                                  |  |

|--------------|---------------------|----------------------------------------------------------------|------|------|-----------|------------------|----------------------------------------------------------------------------------|--|

| Param<br>No. | Sym                 | Characteristic                                                 | Min  | Тур† | Мах       | Units            | Conditions                                                                       |  |

| D001         | Vdd                 | Supply Voltage                                                 | 2.5  | -    | 5.5       | V                | See Figure 13-1 through Figure 13-3                                              |  |

| D002         | Vdr                 | RAM Data Retention<br>Voltage (Note 1)                         | -    | 1.5* | -         | V                | Device in SLEEP mode                                                             |  |

| D003         | VPOR                | VDD start voltage to<br>ensure Power-on Reset                  | -    | Vss  | -         | V                | See section on power-on reset for details                                        |  |

| D004         | SVDD                | VDD rise rate to ensure<br>Power-on Reset                      | .05* | -    | -         | V/ms             | See section on power-on reset for details                                        |  |

| D005         | VBOR                | Brown-out Detect Voltage                                       | 3.7  | 4.0  | 4.35      | V                | BOREN configuration bit is cleared                                               |  |

| D010         | IDD                 | Supply Current (Note 2)                                        | -    | 1.2  | 2.0       | mA               | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)*                |  |

|              |                     |                                                                | -    | -    | 1.1       | mA               | FOSC = 4 MHz, $VDD = 2.5V$ , $WDT$ disabled,                                     |  |

|              |                     |                                                                | -    | 35   | 70        | μA               | XT osc mode, (Note 4)<br>Fosc = 32 kHz, VDD = 2.5V, WDT disabled,<br>LP osc mode |  |

| D020         | IPD                 | Power Down Current (Note 3)                                    | _    | -    | 2.0       | μA               | VDD = 2.5V                                                                       |  |

|              |                     |                                                                | -    | -    | 2.2       | μA               | VDD = 3.0V*                                                                      |  |

|              |                     |                                                                | -    | -    | 9.0       | μA               | VDD = 5.5V                                                                       |  |

|              |                     |                                                                | -    | -    | 15        | μA               | VDD = 5.5V Extended                                                              |  |

| D022         | $\Delta$ IWDT       | WDT Current (Note 5)                                           | -    | 6.0  | 10        | μA               | VDD=4.0V                                                                         |  |

| D022A        | $\Delta$ IBOR       | Brown-out Reset Current                                        | _    | 75   | 12<br>125 | μ <b>Α</b><br>μΑ | $(125^{\circ}C)$<br>BOD enabled, VDD = 5.0V                                      |  |

| D023         |                     | (Note 5)<br>Comparator Current for each<br>Comparator (Note 5) | -    | 30   | 60        | μA               | VDD = 4.0V                                                                       |  |

| D023A        | $\Delta$ IVREF      | VREF Current (Note 5)                                          | -    | 80   | 135       | μA               | VDD = 4.0V                                                                       |  |

|              | $\Delta$ IEE Write  | Operating Current                                              | -    |      | 3         | mA               | Vcc = 5.5V, SCL = 400 kHz                                                        |  |

|              | $\Delta IEE \ Read$ | Operating Current                                              | -    |      | 1         | mA               |                                                                                  |  |

|              | $\Delta IEE$        | Standby Current                                                | -    |      | 30        | μA               | VCC = 3.0V, EE VDD = VCC                                                         |  |

|              | $\Delta IEE$        | Standby Current                                                | -    |      | 100       | μA               | VCC = 3.0V, EE VDD = VCC                                                         |  |

| 1A           | Fosc                | LP Oscillator Operating Frequency                              | 0    | —    | 200       | kHz              | All temperatures                                                                 |  |

|              |                     | RC Oscillator Operating Frequency                              |      | —    | 4         | MHz              | All temperatures                                                                 |  |

|              |                     | XT Oscillator Operating Frequency                              | 0    | —    | 4<br>20   | MHz              | All temperatures                                                                 |  |

|              |                     | HS Oscillator Operating Frequency                              | -    |      | 20        | MHz              | All temperatures                                                                 |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

MCLR = VDD; WDT enabled/disabled as specified.

3: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or Vss.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kΩ.

5: The  $\Delta$  current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

6: Commercial temperature range only.

## TABLE 13-1: COMPARATOR SPECIFICATIONS

| Param No. | Characteristics                           | Sym    | Min  | Тур   | Max       | Units | Comments   |

|-----------|-------------------------------------------|--------|------|-------|-----------|-------|------------|

| D300      | Input offset voltage                      | VIOFF  |      | ± 5.0 | ± 10      | mV    |            |

| D301      | Input common mode voltage                 | VICM   | 0    |       | Vdd - 1.5 | V     |            |

| D302      | CMRR                                      | CMRR   | +55* |       |           | db    |            |

| 300       | Response Time <sup>(1)</sup>              | TRESP  |      | 150*  | 400*      | ns    | PIC16CE62X |

| 301       | Comparator Mode Change to<br>Output Valid | Тмс2ov |      |       | 10*       | μS    |            |

Operating Conditions: VDD range as described in Table 12-1, -40°C<TA<+125°C. .

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

#### TABLE 13-2: VOLTAGE REFERENCE SPECIFICATIONS

Operating Conditions: VDD range as described in Table 12-1, -40°C<TA<+125°C.

| Param<br>No. | Characteristics              | Sym  | Min    | Тур | Мах                          | Units      | Comments                                |

|--------------|------------------------------|------|--------|-----|------------------------------|------------|-----------------------------------------|

| D310         | Resolution                   | VRES | VDD/24 |     | Vdd/32                       | LSB        |                                         |

| D311         | Absolute Accuracy            | Vraa |        |     | <u>+</u> 1/4<br><u>+</u> 1/2 | LSB<br>LSB | Low Range (VRR=1)<br>High Range (VRR=0) |

| D312         | Unit Resistor Value (R)      | VRur |        | 2K* |                              | Ω          | Figure 9-1                              |

| 310          | Settling Time <sup>(1)</sup> | TSET |        |     | 10*                          | μS         |                                         |

\* These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

## 13.5 Timing Diagrams and Specifications

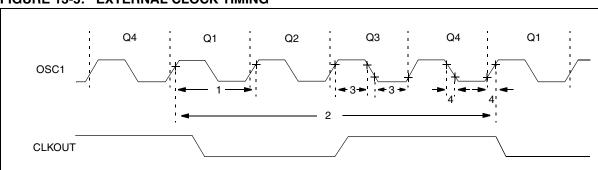

# FIGURE 13-5: EXTERNAL CLOCK TIMING

# TABLE 13-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min  | Тур† | Max    | Units | Conditions                         |

|------------------|-------|----------------------------------|------|------|--------|-------|------------------------------------|

| 1A               | Fosc  | External CLKIN Frequency         | DC   | _    | 4      | MHz   | XT and RC osc mode, VDD=5.0V       |

|                  |       | (Note 1)                         | DC   | —    | 20     | MHz   | HS osc mode                        |

|                  |       |                                  | DC   | —    | 200    | kHz   | LP osc mode                        |

|                  |       | Oscillator Frequency             | DC   | —    | 4      | MHz   | RC osc mode, VDD=5.0V              |

|                  |       | (Note 1)                         | 0.1  | —    | 4      | MHz   | XT osc mode                        |

|                  |       |                                  | 1    | —    | 20     | MHz   | HS osc mode                        |

|                  |       |                                  | DC   | -    | 200    | kHz   | LP osc mode                        |

| 1                | Tosc  | External CLKIN Period            | 250  | —    | _      | ns    | XT and RC osc mode                 |

|                  |       | (Note 1)                         | 50   | —    | —      | ns    | HS osc mode                        |

|                  |       |                                  | 5    | —    | —      | μs    | LP osc mode                        |

|                  |       | Oscillator Period                | 250  | —    | _      | ns    | RC osc mode                        |

|                  |       | (Note 1)                         | 250  | —    | 10,000 | ns    | XT osc mode                        |

|                  |       |                                  | 50   | —    | 1,000  | ns    | HS osc mode                        |

|                  |       |                                  | 5    | —    | —      | μS    | LP osc mode                        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200  | —    | DC     | ns    | Tcy=Fosc/4                         |

| 3*               | TosL, | External Clock in (OSC1) High or | 100* | —    | —      | ns    | XT oscillator, Tosc L/H duty cycle |

|                  | TosH  | Low Time                         | 2*   | —    | —      | μs    | LP oscillator, Tosc L/H duty cycle |

|                  |       |                                  | 20*  |      | —      | ns    | HS oscillator, Tosc L/H duty cycle |

| 4*               | TosR, | External Clock in (OSC1) Rise or | 25*  | —    | —      | ns    | XT oscillator                      |

|                  | TosF  | Fall Time                        | 50*  | —    | —      | ns    | LP oscillator                      |

|                  |       |                                  | 15*  | —    | —      | ns    | HS oscillator                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

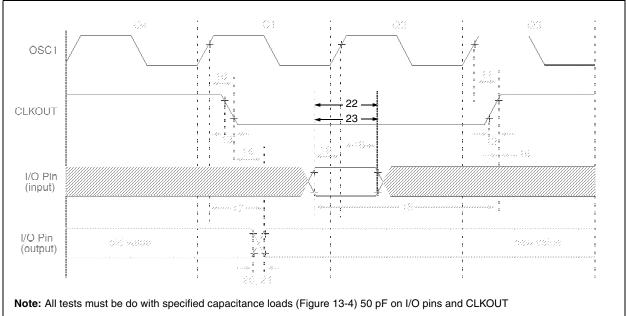

# FIGURE 13-6: CLKOUT AND I/O TIMING

| Parameter # | Sym      | Characteristic                                                        | Min          | Тур† | Мах | Units |

|-------------|----------|-----------------------------------------------------------------------|--------------|------|-----|-------|

| 10*         | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                       | —            | 75   | 200 | ns    |

| 11*         | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup> <sup>(1)</sup>               | _            | 75   | 200 | ns    |

| 12*         | TckR     | CLKOUT rise time <sup>(1)</sup>                                       | _            | 35   | 100 | ns    |

| 13*         | TckF     | CLKOUT fall time <sup>(1)</sup>                                       | _            | 35   | 100 | ns    |

| 14*         | TckL2ioV | CLKOUT ↓ to Port out valid <sup>(1)</sup>                             | _            | —    | 20  | ns    |

| 15*         | TioV2ckH | Port in valid before CLKOUT $\uparrow$ <sup>(1)</sup>                 | Tosc +200 ns | —    |     | ns    |

| 16*         | TckH2iol | Port in hold after CLKOUT ↑ <sup>(1)</sup>                            | 0            | —    |     | ns    |

| 17*         | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid                                    | —            | 50   | 150 | ns    |

| 18*         | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | 100          | —    | _   | ns    |

| 19*         | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in setup time)             | 0            | —    | _   | ns    |

| 20*         | TioR     | Port output rise time                                                 | —            | 10   | 40  | ns    |

| 21*         | TioF     | Port output fall time                                                 | —            | 10   | 40  | ns    |

| 22*         | Tinp     | RB0/INT pin high or low time                                          | 25           | —    | _   | ns    |

| 23          | Trbp     | RB<7:4> change interrupt high or low time                             | Тсү          | —    | _   | ns    |

|  | TABLE 13-4: | <b>CLKOUT AND I/O TIMING REQUIREMENTS</b> |

|--|-------------|-------------------------------------------|

|--|-------------|-------------------------------------------|

\* These parameters are characterized but not tested

+ Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

NOTES:

NOTES:

# PIC16CE62X PRODUCT IDENTIFICATION SYSTEM

To order or to obtain information, e.g., on pricing or delivery, please use the listed part numbers, and refer to the factory or the listed sales offices.

| PART NOXX X /XX XXX |                                                                                                                                                                                      |                                                                                            |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Pattern:            | 3-Digit Pattern Code for QTP (blank otherwise)                                                                                                                                       |                                                                                            |

| Package:            | P = PDIP<br>SO = SOIC (Gull Wing, 300 mil body)<br>SS = SSOP (209 mil)                                                                                                               |                                                                                            |

|                     | JW* = Windowed CERDIP Example<br>a) PIC10                                                                                                                                            | 6CE623-04/P301 =                                                                           |

| Range:              | $ \begin{array}{rcl} I &=& -40^\circ \mbox{C to } +85^\circ \mbox{C} & & age, 4 \\ E &=& -40^\circ \mbox{C to } +125^\circ \mbox{C} & & \mbox{QTP} \\ b) \mbox{ PIC10} \end{array} $ | mercial temp., PDIP pack-<br>4 MHz, normal VDD limits,<br>pattern #301.<br>6CE623-04I/SO = |

| Frequency<br>Range: |                                                                                                                                                                                      | strial temp., SOIC pack-<br>4MHz, industrial VDD lim-                                      |

| Device:             | PIC16CE62X :VDD range 3.0V to 5.5V<br>PIC16CE62XT:VDD range 3.0V to 5.5V (Tape and R                                                                                                 | leel)                                                                                      |

|                     |                                                                                                                                                                                      |                                                                                            |

|                     |                                                                                                                                                                                      |                                                                                            |

|                     |                                                                                                                                                                                      |                                                                                            |

\* JW Devices are UV erasable and can be programmed to any device configuration. JW Devices meet the electrical requirement of each oscillator type.

### Sales and Support

#### Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

1. Your local Microchip sales office

2. The Microchip Worldwide Site (www.microchip.com)