Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 20MHz                                                                       |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

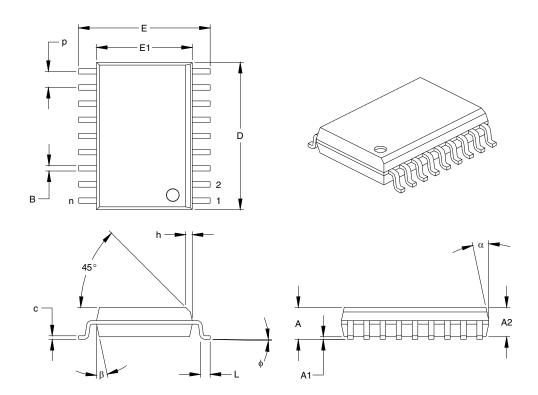

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce625-20i-so |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

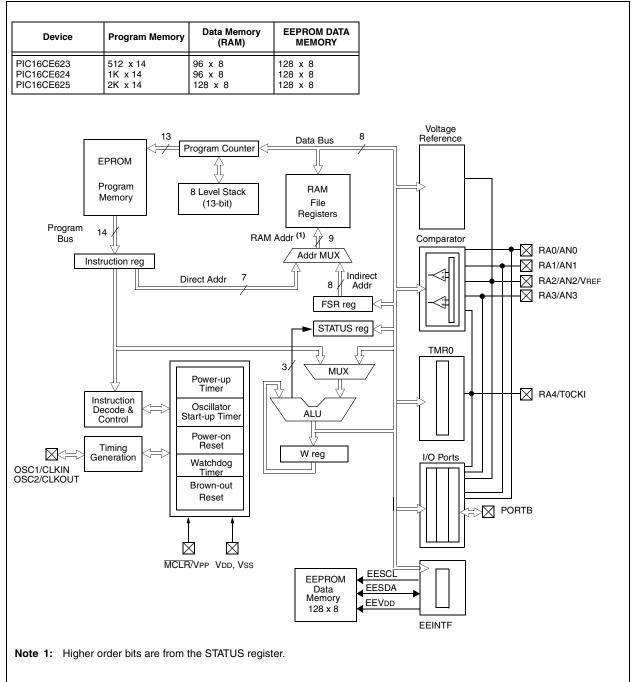

# 1.0 GENERAL DESCRIPTION

The PIC16CE62X are 18 and 20-Pin EPROM-based members of the versatile PIC<sup>®</sup> family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with EEPROM data memory.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16CE62X family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CE62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16CE623 and PIC16CE624 have 96 bytes of RAM. The PIC16CE625 has 128 bytes of RAM. Each microcontroller contains a 128x8 EEPROM memory array for storing non-volatile information, such as calibration data or security codes. This memory has an endurance of 1,000,000 erase/write cycles and a retention of 40 plus years.

Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16CE62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low-cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16CE62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and reset. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development, while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16CE62X mid-range microcontroller families.

A simplified block diagram of the PIC16CE62X is shown in Figure 3-1.

The PIC16CE62X series fits perfectly in applications ranging from multi-pocket battery chargers to low-power remote sensors. The EPROM technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high-performance, ease of use and I/O flexibility make the PIC16CE62X very versatile.

# 1.1 <u>Development Support</u>

The PIC16CE62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler is also available.

# FIGURE 3-1: BLOCK DIAGRAM

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The special registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7                  | Bit 6                                                                                        | Bit 5       | Bit 4         | Bit 3        | Bit 2        | Bit 1        | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>resets <sup>(1)</sup> |

|---------|---------------|------------------------|----------------------------------------------------------------------------------------------|-------------|---------------|--------------|--------------|--------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                        |                                                                                              |             |               |              |              |              |            |                       |                                                |

| 00h     | INDF          | Addressin<br>register) | Addressing this location uses contents of FSR to address data memory (not a physic register) |             |               |              |              |              |            | xxxx xxxx             | xxxx xxxx                                      |

| 01h     | TMR0          | Timer0 M               | odule's Reg                                                                                  | jister      |               |              |              |              |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program (              | Counter's (F                                                                                 | PC) Least S | Significant B | yte          |              |              |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>     | RP1 <sup>(2)</sup>                                                                           | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da            | ata memory                                                                                   | address p   | ointer        |              | I            |              | I          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         |                        |                                                                                              |             | RA4           | RA3          | RA2          | RA1          | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                    | RB6                                                                                          | RB5         | RB4           | RB3          | RB2          | RB1          | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h     | Unimplemented |                        | 1                                                                                            |             | 1             |              | 1            |              | 1          | -                     | -                                              |

| 08h     | Unimplemented |                        |                                                                                              |             |               |              |              |              |            | -                     | _                                              |

| 09h     | Unimplemented |                        |                                                                                              |             |               |              |              |              |            | -                     | _                                              |

| 0Ah     | PCLATH        | _                      |                                                                                              | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                    | PEIE                                                                                         | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | —                      | CMIF                                                                                         | —           | —             | —            | —            | —            | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                        |                                                                                              |             |               |              |              |              |            | —                     | _                                              |

| 1Fh     | CMCON         | C2OUT                  | C10UT                                                                                        | _           |               | CIS          | CM2          | CM1          | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                        |                                                                                              |             |               |              |              |              |            |                       |                                                |

| 80h     | INDF          | Addressin<br>register) | ig this locat                                                                                | ion uses co | ontents of F  | SR to addre  | ess data me  | emory (not a | a physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                   | INTEDG                                                                                       | TOCS        | T0SE          | PSA          | PS2          | PS1          | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program (              | Counter's (F                                                                                 | PC) Least S | Significant B | yte          | 1            |              | 1          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP                    | RP1                                                                                          | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da            | ata memory                                                                                   | address p   | ointer        |              | 1            |              | 1          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                      |                                                                                              |             | TRISA4        | TRISA3       | TRISA2       | TRISA1       | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7                 | TRISB6                                                                                       | TRISB5      | TRISB4        | TRISB3       | TRISB2       | TRISB1       | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h     | Unimplemented |                        |                                                                                              |             |               |              |              |              |            | -                     | -                                              |

| 88h     | Unimplemented |                        |                                                                                              |             |               |              |              |              |            | -                     | -                                              |

| 89h     | Unimplemented |                        |                                                                                              |             |               |              |              |              |            | -                     | -                                              |

| 8Ah     | PCLATH        | _                      |                                                                                              | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                    | PEIE                                                                                         | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                      | CMIE                                                                                         | _           | —             | _            | —            | _            | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                        |                                                                                              |             |               |              |              |              |            | -                     | -                                              |

| 8Eh     | PCON          | —                      | —                                                                                            | —           | _             | —            | —            | POR          | BOD        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                        |                                                                                              |             |               |              |              |              |            | -                     | -                                              |

| 90h     | EEINTF        | —                      | —                                                                                            | —           | _             | —            | EESCL        | EESDA        | EEVDD      | 111                   | 111                                            |

| 9Fh     | VRCON         | VREN                   | VROE                                                                                         | VRR         | _             | VR3          | VR2          | VR1          | VR0        | 000- 0000             | 000- 0000                                      |

### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16CE62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non power-up) resets include MCLR reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

Note 2: IRP & RPI bits are reserved; always maintain these bits clear.

#### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

# REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1    | R/W-1                                                                                                                                                                                                                                                               | R/W-1                                                                                                                          | R/W-1     | R/W-1     | R/W-1 | R/W-1 | R/W-1 |                                                                                                                   |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------|--|

| RBPU     | INTEDG                                                                                                                                                                                                                                                              | TOCS                                                                                                                           | TOSE      | PSA       | PS2   | PS1   | PS0   | R = Readable bit                                                                                                  |  |

| bit7     |                                                                                                                                                                                                                                                                     |                                                                                                                                |           |           |       |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |  |

| bit 7:   |                                                                                                                                                                                                                                                                     |                                                                                                                                |           |           |       |       |       |                                                                                                                   |  |

| bit 6:   | INTEDG: In<br>1 = Interrup<br>0 = Interrup                                                                                                                                                                                                                          | ot on rising                                                                                                                   | g edge o  | f RB0/INT |       |       |       |                                                                                                                   |  |

| bit 5:   | 1 = Transiti                                                                                                                                                                                                                                                        | <b>T0CS</b> : TMR0 Clock Source Select bit<br>1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT) |           |           |       |       |       |                                                                                                                   |  |

| bit 4:   | <b>T0SE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin                                                                                                   |                                                                                                                                |           |           |       |       |       |                                                                                                                   |  |

| bit 3:   | PSA: Prescaler Assignment bit<br>1 = Prescaler is assigned to the WDT<br>0 = Prescaler is assigned to the Timer0 module                                                                                                                                             |                                                                                                                                |           |           |       |       |       |                                                                                                                   |  |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : F                                                                                                                                                                                                                                            | Prescaler I                                                                                                                    | Rate Sele | ect bits  |       |       |       |                                                                                                                   |  |

|          | Bit Value                                                                                                                                                                                                                                                           | TMR0 Ra                                                                                                                        | te WD1    | Γ Rate    |       |       |       |                                                                                                                   |  |

|          | 000       1:2       1:1         001       1:4       1:2         010       1:8       1:4         011       1:16       1:8         100       1:32       1:16         101       1:64       1:32         110       1:128       1:64         111       1:256       1:128 |                                                                                                                                |           |           |       |       |       |                                                                                                                   |  |

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

### REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

| R/W-0       | R/W-0                                                                                                                                                                                       | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-x        |                                                                                                                                       |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| GIE<br>bit7 | PEIE                                                                                                                                                                                        | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |  |

| bit 7:      |                                                                                                                                                                                             |       |       |       |       |       |              |                                                                                                                                       |  |

| bit 6:      | <ul> <li>PEIE: Peripheral Interrupt Enable bit</li> <li>1 = Enables all un-masked peripheral interrupts</li> <li>0 = Disables all peripheral interrupts</li> </ul>                          |       |       |       |       |       |              |                                                                                                                                       |  |

| bit 5:      | <b>T0IE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                                       |       |       |       |       |       |              |                                                                                                                                       |  |

| bit 4:      | INTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                                    |       |       |       |       |       |              |                                                                                                                                       |  |

| bit 3:      | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                  |       |       |       |       |       |              |                                                                                                                                       |  |

| bit 2:      | <b>TOIF</b> : TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                      |       |       |       |       |       |              |                                                                                                                                       |  |

| bit 1:      | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur                  |       |       |       |       |       |              |                                                                                                                                       |  |

| bit 0:      | <b>RBIF</b> : RB Port Change Interrupt Flag bit<br>1 = When at least one of the RB<7:4> pins changed state (must be cleared in software)<br>0 = None of the RB<7:4> pins have changed state |       |       |       |       |       |              |                                                                                                                                       |  |

### 6.1 Bus Characteristics

In this section, the term "processor" refers to the portion of the PIC16CE62X that interfaces to the EEPROM through software manipulating the EEINTF register. The following **bus protocol** is to be used with the EEPROM data memory.

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted by the EEPROM as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 6-1).

#### 6.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

#### 6.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### 6.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### 6.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the processor and is theoretically unlimited, although only the last sixteen will be stored when doing a write operation. When an overwrite does occur, it will replace data in a first-in, first-out fashion.

#### 6.1.5 ACKNOWLEDGE

The EEPROM will generate an acknowledge after the reception of each byte. The processor must generate an extra clock pulse which is associated with this acknowledge bit.

| Note: | Acknowledge bits are not generated if an   |

|-------|--------------------------------------------|

|       | internal programming cycle is in progress. |

When the EEPROM acknowledges, it pulls down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. The processor must signal an end of data to the EEPROM by not generating an acknowledge bit on the last byte that has been clocked out of the EEPROM. In this case, the EEPROM must leave the data line HIGH to enable the processor to generate the STOP condition (Figure 6-2).

NOTES:

#### EXAMPLE 9-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x07        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | outputs        |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank 0   |

| CALL  | DELAY10     | ; | 10µs delay     |

#### 9.2 <u>Voltage Reference Accuracy/Error</u>

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 9-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 13-2.

### 9.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

### 9.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

### 9.5 <u>Connection Considerations</u>

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 9-2 shows an example buffering technique.

# VREF Nodule Voltage Reference Output Impedance

# FIGURE 9-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

Note 1: R is dependent upon the Voltage Reference Configuration VRCON<3:0> and VRCON<5>.

### TABLE 9-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR / BOD | Value On<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000             | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000               | 00 0000                         |

| 85h     | TRISA | _     | _     |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                | 1 1111                          |

Legend: - = Unimplemented, read as "0"

| CLRWDT           | Clear Watchdog Timer                                                                                                                                     |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                                           |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                     |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow WDT \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \end{array}$ |  |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0100                                                                                                                                        |  |  |  |  |  |  |

| Description:     | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{TO}$ and $\overline{PD}$ are set.          |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                        |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                        |  |  |  |  |  |  |

| Example          | CLRWDT                                                                                                                                                   |  |  |  |  |  |  |

|                  | Before Instruction<br>WDT counter = ?<br>After Instruction<br>WDT counter = $0x00$<br>WDT prescaler = $0$<br>TO = $1$<br>PD = $1$                        |  |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                             |  |  |  |  |  |  |

| Syntax:          | [label] COMF f,d                                                                                                                                         |  |  |  |  |  |  |

| COME             | Complement                                                                                                                                              |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] COMF f,d                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                         |

| Operation:       | $(\overline{f}) \rightarrow (dest)$                                                                                                                     |

| Status Affected: | Z                                                                                                                                                       |

| Encoding:        | 00 1001 dfff ffff                                                                                                                                       |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is 0, the result is<br>stored in W. If 'd' is 1, the result is<br>stored back in register 'f'. |

| Words:           | 1                                                                                                                                                       |

| Cycles:          | 1                                                                                                                                                       |

| Example          | COMF REG1,0                                                                                                                                             |

|                  | Before InstructionREG1= $0x13$ After InstructionREG1= $0x13$ W= $0xEC$                                                                                  |

|                  |                                                                                                                                                         |

| Decrement f                                                                                                                                     |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                                                                                                                                 |  |  |  |  |  |

| [label] DECF f,d                                                                                                                                |  |  |  |  |  |

| $0 \leq f \leq 127$                                                                                                                             |  |  |  |  |  |

| d ∈ [0,1]                                                                                                                                       |  |  |  |  |  |

| (f) - 1 $\rightarrow$ (dest)                                                                                                                    |  |  |  |  |  |

| Z                                                                                                                                               |  |  |  |  |  |

| 00 0011 dfff ffff                                                                                                                               |  |  |  |  |  |

| Decrement register 'f'. If 'd' is 0, the<br>result is stored in the W register. If 'd'<br>is 1, the result is stored back in regis-<br>ter 'f'. |  |  |  |  |  |

| 1                                                                                                                                               |  |  |  |  |  |

| 1                                                                                                                                               |  |  |  |  |  |

| DECF CNT, 1                                                                                                                                     |  |  |  |  |  |

| Before Instruction<br>CNT = 0x01<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                           |  |  |  |  |  |

| Decrement f, Skip if 0                                                                                                                          |  |  |  |  |  |

| [ <i>label</i> ] DECFSZ f,d                                                                                                                     |  |  |  |  |  |

| $0 \leq f \leq 127$                                                                                                                             |  |  |  |  |  |

| d ∈ [0,1]                                                                                                                                       |  |  |  |  |  |

|                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                       |                                                                                    |                                                                                             |                                                        |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|

| Operation:       | (f) - 1 $\rightarrow$ (dest); skip if result = 0                                                                      |                                                                                    |                                                                                             |                                                        |  |  |

| Status Affected: | None                                                                                                                  |                                                                                    |                                                                                             |                                                        |  |  |

| Encoding:        | 00                                                                                                                    | 1011                                                                               | dfff                                                                                        | ffff                                                   |  |  |

| Description:     | The contendecrement<br>placed in t<br>result is placed<br>if the result<br>which is all<br>A NOP is e<br>two-cycle if | ted. If 'd' i<br>he W reg<br>aced back<br>It is 0, the<br>ready feto<br>xecuted in | s 0, the re<br>ister. If 'd' i<br>k in registe<br>next instru-<br>ched, is dis<br>nstead ma | sult is<br>is 1, the<br>er 'f'.<br>uction,<br>scarded. |  |  |

| Words:           | 1                                                                                                                     |                                                                                    |                                                                                             |                                                        |  |  |

| Cycles:          | 1(2)                                                                                                                  |                                                                                    |                                                                                             |                                                        |  |  |

| Example          | HERE<br>CONTINU                                                                                                       | DECF<br>GOTO<br>JE<br>•                                                            | SZ CNI<br>LOC                                                                               |                                                        |  |  |

|                  | Before In<br>PC<br>After Inst<br>CNT<br>if CNT<br>PC<br>if CNT<br>PC                                                  | = ado<br>ruction<br>= CN<br>= 0,<br>= ado<br>≠ 0,                                  | iress HERE<br>T - 1<br>iress CONT                                                           |                                                        |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                    |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                          |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                    |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                    |  |  |  |  |  |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                    |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                    |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                    |  |  |  |  |  |

| Example          | IORWF RESULT, 0                                                                                                                                                      |  |  |  |  |  |

|                  | $\begin{array}{rcl} Before \ Instruction \\ RESULT &= & 0x13 \\ W &= & 0x91 \\ After \ Instruction \\ RESULT &= & 0x13 \\ W &= & 0x93 \\ Z &= & 1 \end{array}$       |  |  |  |  |  |

| MOVF             | Move f                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                           |  |  |  |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                  | to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Example          | MOVF FSR, 0                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                     |  |  |  |  |  |  |  |

| MOVLW            | Move Literal to W                                                                          |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                          |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                        |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                       |  |  |  |  |  |  |  |

| Encoding:        | 11 00xx kkkk kkkk                                                                          |  |  |  |  |  |  |  |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                          |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                          |  |  |  |  |  |  |  |

| Example          | MOVLW 0x5A                                                                                 |  |  |  |  |  |  |  |

|                  | After Instruction<br>W = 0x5A                                                              |  |  |  |  |  |  |  |

| MOVWF            | Move W to f                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                                                                                                            |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                                                        |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                       |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                          |

| Description:     | Move data from W register to register 'f'.                                                                                                                                                 |

| Words:           | 1                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                          |

| Example          | MOVWF OPTION                                                                                                                                                                               |

|                  | $\begin{array}{rcl} \text{Before Instruction} & & \\ & \text{OPTION} & = & 0xFF \\ W & = & 0x4F \\ \text{After Instruction} & & \\ & \text{OPTION} & = & 0x4F \\ W & = & 0x4F \end{array}$ |

| RETURN             | Return from Subroutine                                                                                          | RRF              | Rotate Right f through Carry                                                                                                                                                                                                               |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:            | [label] RETURN                                                                                                  | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                   |  |  |  |  |

| Operands:          | None                                                                                                            | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                          |  |  |  |  |

| Operation:         | $TOS \rightarrow PC$                                                                                            |                  | $d \in [0,1]$                                                                                                                                                                                                                              |  |  |  |  |

| Status Affected:   | None                                                                                                            | Operation:       | See description below                                                                                                                                                                                                                      |  |  |  |  |

| Encoding:          | 00 0000 0000 1000                                                                                               | Status Affected: | С                                                                                                                                                                                                                                          |  |  |  |  |

| Description:       | Return from subroutine. The stack is                                                                            | Encoding:        | 00 1100 dfff ffff                                                                                                                                                                                                                          |  |  |  |  |

|                    | POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is                                                             |  |  |  |  |

| Words:             | 1                                                                                                               |                  | placed back in register 'f'.                                                                                                                                                                                                               |  |  |  |  |

| Cycles:<br>Example | 2<br>RETURN                                                                                                     |                  | C Register f                                                                                                                                                                                                                               |  |  |  |  |

|                    | After Interrupt                                                                                                 | Words:           | 1                                                                                                                                                                                                                                          |  |  |  |  |

|                    | PC = TOS                                                                                                        | Cycles:          | 1                                                                                                                                                                                                                                          |  |  |  |  |

|                    |                                                                                                                 | Example          | RRF REG1,0                                                                                                                                                                                                                                 |  |  |  |  |

|                    |                                                                                                                 |                  | Before Instruction       REG1       =       1110       0110         C       =       0       0         After Instruction       REG1       =       1110       0110         W       =       0111       0011         C       =       0       0 |  |  |  |  |

| RLF              | Rotate Left f t                                                   | hrough Carry                                                                                                                |         |

|------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|

| Syntax:          | [label] RLF                                                       | f,d                                                                                                                         |         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$ |                                                                                                                             |         |

| Operation:       | See description                                                   | n below                                                                                                                     |         |

| Status Affected: | С                                                                 |                                                                                                                             |         |

| Encoding:        | 00 110                                                            | 1 dfff ff                                                                                                                   | ff      |

| Description:     | one bit to the left<br>Flag. If 'd' is 0, th                      | register 'f' are rota<br>t through the Carry<br>ne result is placed<br>f 'd' is 1, the result<br>egister 'f'.<br>Register f | /<br>in |

| Words:           | 1                                                                 |                                                                                                                             |         |

| Cycles:          | 1                                                                 |                                                                                                                             |         |

|                  |                                                                   |                                                                                                                             |         |

| Example          | RLF                                                               | REG1,0                                                                                                                      |         |

# SLEEP

| 02221            |                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ prescaler, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                                                 |  |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Encoding:        | 00 0000 0110 0011                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Description:     | The power-down status bit, $\overrightarrow{PD}$ is<br>cleared. Time-out status bit, $\overrightarrow{TO}$ is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 10.8 for more details. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Example:         | SLEEP                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

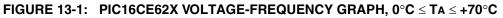

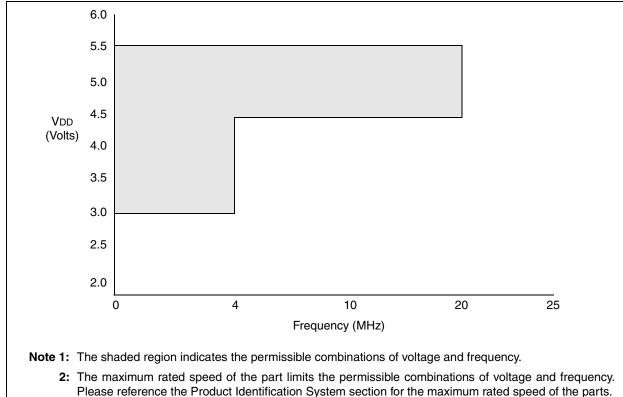

**2:** The maximum rated speed of the part limits the permissible combinations of voltage and frequency. Please reference the Product Identification System section for the maximum rated speed of the parts.

# 13.1 DC CHARACTERISTICS:

### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS |                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for industrial an<br>0°C0°C $\leq$ TA $\leq$ +70°C for commercial<br>$-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended |        |      |           |            |                                                                   |

|--------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|-----------|------------|-------------------------------------------------------------------|

| Param<br>No.       | Sym                | Characteristic                                                                                                                                                                                                                                |        | Тур† | Мах       | Units      | Conditions                                                        |

| D001               | Vdd                | Supply Voltage                                                                                                                                                                                                                                | 3.0    | -    | 5.5       | V          | See Figure 13-1 through Figure 13-3                               |

| D002               | Vdr                | RAM Data Retention<br>Voltage (Note 1)                                                                                                                                                                                                        | -      | 1.5* | -         | V          | Device in SLEEP mode                                              |

| D003               | VPOR               | VDD start voltage to<br>ensure Power-on Reset                                                                                                                                                                                                 | -      | Vss  | -         | V          | See section on power-on reset for details                         |

| D004               | SVDD               | VDD rise rate to ensure<br>Power-on Reset                                                                                                                                                                                                     | 0.05*  | -    | -         | V/ms       | See section on power-on reset for details                         |

| D005               | VBOR               | Brown-out Detect Voltage                                                                                                                                                                                                                      | 3.7    | 4.0  | 4.35      | V          | BOREN configuration bit is cleared                                |

| D010               | IDD                | Supply Current (Note 2, 4)                                                                                                                                                                                                                    | -      | 1.2  | 2.0       | mA         | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)* |

|                    |                    |                                                                                                                                                                                                                                               | -      | 0.4  | 1.2       | mA         | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT osc mode, (Note 4)  |

|                    |                    |                                                                                                                                                                                                                                               | -      | 1.0  | 2.0       | mA         | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS osc mode, (Note 6) |

|                    |                    |                                                                                                                                                                                                                                               | -      | 4.0  | 6.0       | mA         | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS osc mode           |

|                    |                    |                                                                                                                                                                                                                                               | -      | 4.0  | 7.0       | mA         | FOSC = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS osc mode          |

|                    |                    |                                                                                                                                                                                                                                               | -      | 35   | 70        | μA         | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP osc mode           |

| D020               | IPD                | Power Down Current (Note 3)                                                                                                                                                                                                                   | -      | -    | 2.2       | μA         | VDD = 3.0V                                                        |

|                    |                    |                                                                                                                                                                                                                                               | -      | -    | 5.0       | μA         | $VDD = 4.5V^*$                                                    |

|                    |                    |                                                                                                                                                                                                                                               | _      | -    | 9.0<br>15 | μΑ<br>μΑ   | VDD = 5.5V<br>VDD = 5.5V Extended                                 |