Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 128 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                   |

| Data Converters            |                                                                             |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce625t-04-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

### REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

| R/W-0       | R/W-0                                                                                                                                                                                                                                  | R/W-0       | R/W-0                                  | R/W-0        | R/W-0     | R/W-0 | R/W-x        |                                                                                                                                       |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------|--------------|-----------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| GIE<br>bit7 | PEIE                                                                                                                                                                                                                                   | TOIE        | INTE                                   | RBIE         | TOIF      | INTF  | RBIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |

| bit 7:      |                                                                                                                                                                                                                                        |             | masked in                              |              |           |       |              |                                                                                                                                       |

| bit 6:      |                                                                                                                                                                                                                                        | es all un-r | terrupt En<br>masked pe<br>ipheral int | eripheral ir | nterrupts |       |              |                                                                                                                                       |

| bit 5:      | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                                                                                  |             |                                        |              |           |       |              |                                                                                                                                       |

| bit 4:      | INTE: RB0/INT External Interrupt Enable bit<br>1 = Enables the RB0/INT external interrupt<br>0 = Disables the RB0/INT external interrupt                                                                                               |             |                                        |              |           |       |              |                                                                                                                                       |

| bit 3:      | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                             |             |                                        |              |           |       |              |                                                                                                                                       |

| bit 2:      | <b>TOIF</b> : TMR0 Overflow Interrupt Flag bit<br>1 = TMR0 register has overflowed (must be cleared in software)<br>0 = TMR0 register did not overflow                                                                                 |             |                                        |              |           |       |              |                                                                                                                                       |

| bit 1:      | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur                                                             |             |                                        |              |           |       |              |                                                                                                                                       |

| bit 0:      | <ul> <li><b>RBIF</b>: RB Port Change Interrupt Flag bit</li> <li>1 = When at least one of the RB&lt;7:4&gt; pins changed state (must be cleared in software)</li> <li>0 = None of the RB&lt;7:4&gt; pins have changed state</li> </ul> |             |                                        |              |           |       |              |                                                                                                                                       |

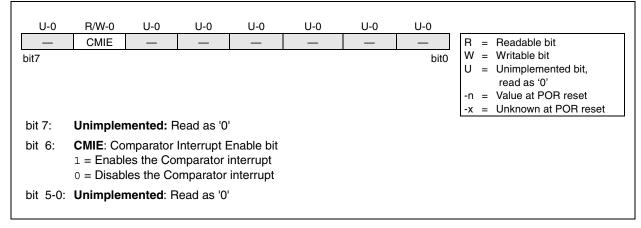

### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bit for the comparator interrupt.

### REGISTER 4-4: PIE1 REGISTER (ADDRESS 8CH)

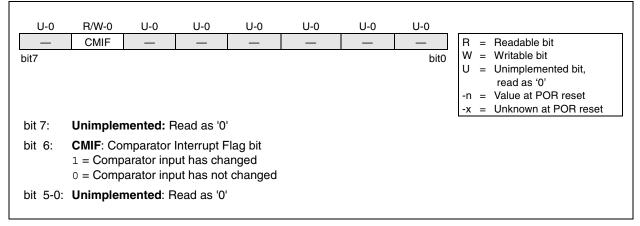

### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt   |

|-------|-------------------------------------------------|

|       | condition occurs, regardless of the state of    |

|       | its corresponding enable bit or the global      |

|       | enable bit, GIE (INTCON<7>). User               |

|       | software should ensure the appropriate          |

|       | interrupt flag bits are clear prior to enabling |

|       | an interrupt.                                   |

### REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

NOTES:

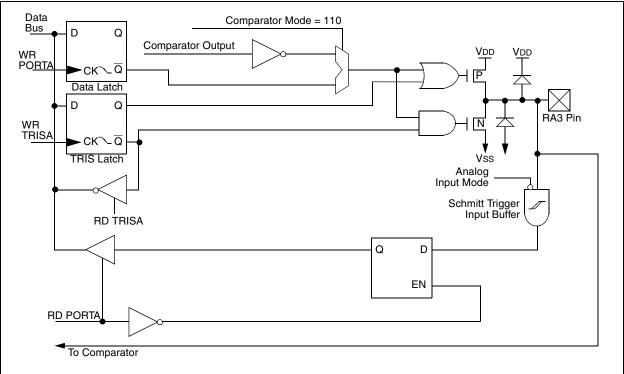

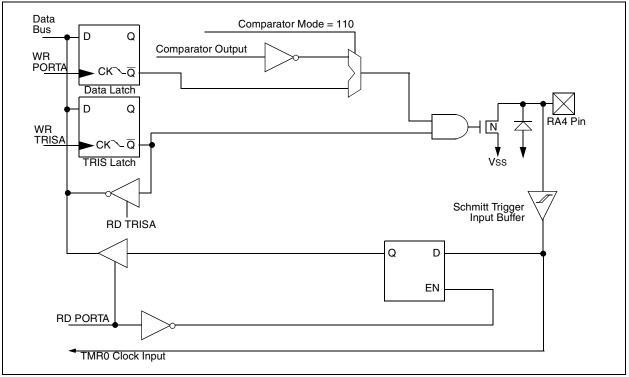

### TABLE 5-1:PORTA FUNCTIONS

| Name         | Bit # | Buffer<br>Type | Function                                                                                          |  |

|--------------|-------|----------------|---------------------------------------------------------------------------------------------------|--|

| RA0/AN0      | bit0  | ST             | Input/output or comparator input                                                                  |  |

| RA1/AN1      | bit1  | ST             | Input/output or comparator input                                                                  |  |

| RA2/AN2/VREF | bit2  | ST             | Input/output or comparator input or VREF output                                                   |  |

| RA3/AN3      | bit3  | ST             | Input/output or comparator input/output                                                           |  |

| RA4/T0CKI    | bit4  | ST             | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |  |

Legend: ST = Schmitt Trigger input

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 05h     | PORTA | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | x 0000           | u 0000                          |

| 85h     | TRISA | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111           | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C1OUT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000          | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   |        | VR3    | VR2    | VR1    | VR0    | 000- 0000        | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged

Note: Shaded bits are not used by PORTA.

### 5.3 <u>I/O Programming Considerations</u>

### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read modify write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (i.e.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ; ; PORTB<7:6> have external pull-up and are not ; connected to other circuitry ; PORT latch PORT pins ; ; BCF PORTB. 7 ; 01pp pppp 11pp pppp BCF PORTB, 6 ; 10pp pppp 11pp pppp BSF STATUS, RPO ; BCF TRISB, 7 ; 10pp pppp 11pp pppp BCF TRISB, 6 ; 10pp pppp 10pp pppp ; ; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused ; RB7 to be latched as the pin value (High).

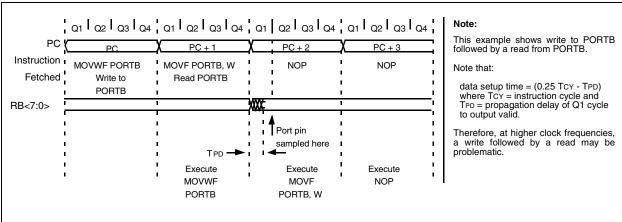

### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with an NOP or another instruction not accessing this I/O port.

### FIGURE 5-7: SUCCESSIVE I/O OPERATION

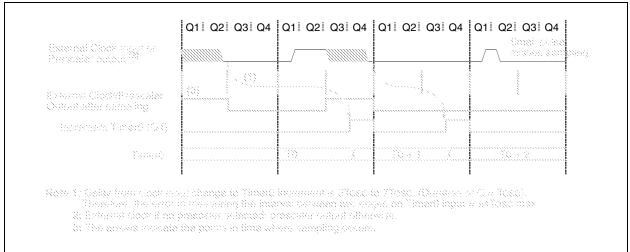

### 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

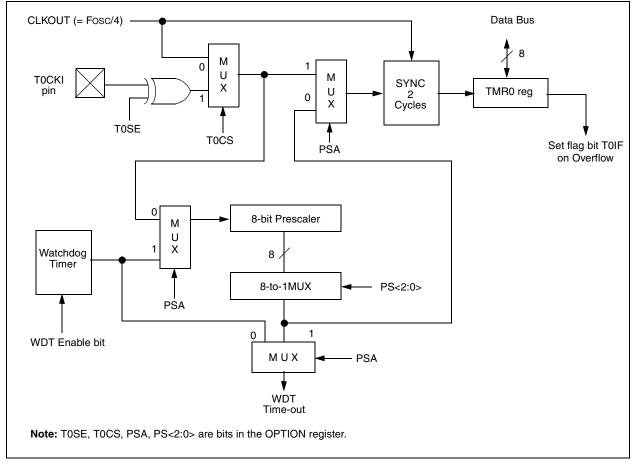

### 7.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

### 10.2 Oscillator Configurations

### 10.2.1 OSCILLATOR TYPES

The PIC16CE62X can be operated in four different oscillator options. The user can program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

- LP Low Power Crystal

- XT Crystal/Resonator

- HS High Speed Crystal/Resonator

- RC Resistor/Capacitor

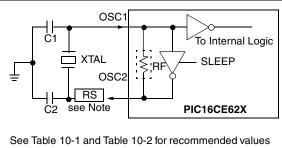

# 10.2.2 CRYSTAL OSCILLATOR / CERAMIC RESONATORS

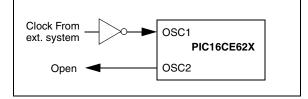

In XT, LP or HS modes, a crystal or ceramic resonator is connected to the OSC1 and OSC2 pins to establish oscillation (Figure 10-1). The PIC16CE62X oscillator design requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device can have an external clock source to drive the OSC1 pin (Figure 10-2).

### FIGURE 10-1: CRYSTAL OPERATION (OR CERAMIC RESONATOR) (HS, XT OR LP OSC CONFIGURATION)

See Table 10-1 and Table 10-2 for recommended values of C1 and C2.

Note: A series resistor may be required for AT strip cut crystals.

### FIGURE 10-2: EXTERNAL CLOCK INPUT OPERATION (HS, XT OR LP OSC CONFIGURATION)

### TABLE 10-1: CERAMIC RESONATORS, PIC16CE62X

**Ranges Tested:** OSC2 Mode Freq OSC1 XT 455 kHz 68 - 100 pF 68 - 100 pF 15 - 68 pF 15 - 68 pF 2.0 MHz 4.0 MHz 15 - 68 pF 15 - 68 pF HS 10 - 68 pF 10 - 68 pF 8.0 MHz 16.0 MHz 10 - 22 pF 10 - 22 pF

These values are for design guidance only. See notes at bottom of page.

### TABLE 10-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR, PIC16CE62X

| Osc Type | Crystal<br>Freq | Cap. Range<br>C1 | Cap. Range<br>C2 |

|----------|-----------------|------------------|------------------|

| LP       | 32 kHz          | 33 pF            | 33 pF            |

|          | 200 kHz         | 15 pF            | 15 pF            |

| XT       | 200 kHz         | 47-68 pF         | 47-68 pF         |

|          | 1 MHz           | 15 pF            | 15 pF            |

|          | 4 MHz           | 15 pF            | 15 pF            |

| HS       | 4 MHz           | 15 pF            | 15 pF            |

|          | 8 MHz           | 15-33 pF         | 15-33 pF         |

|          | 20 MHz          | 15-33 pF         | 15-33 pF         |

These values are for design guidance only. See notes at bottom of page.

- 1. Recommended values of C1 and C2 are identical to the ranges tested table.

- 2. Higher capacitance increases the stability of oscillator, but also increases the start-up time.

- 3. Since each resonator/crystal has its own characteristics, the user should consult the resonator/crystal manufacturer for appropriate values of external components.

- 4. Rs may be required in HS mode, as well as XT mode, to avoid overdriving crystals with low drive level specification.

© 1998-2013 Microchip Technology Inc.

### 10.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit in the STATUS register is cleared, the  $\overline{TO}$  bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSS, with no external circuitry drawing current from the I/O pin, and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|

|       | by a WDT time-out does not drive MCLR     |  |  |  |  |

|       | pin low.                                  |  |  |  |  |

### 10.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register can be used to determine the cause of device reset.  $\overline{PD}$ bit, which is set on power-up is cleared when SLEEP is invoked.  $\overline{TO}$  bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

| Note: | If the global interrupts are disabled (GIE is |

|-------|-----------------------------------------------|

|       | cleared), but any interrupt source has both   |

|       | its interrupt enable bit and the correspond-  |

|       | ing interrupt flag bits set, the device will  |

|       | immediately wake-up from sleep. The           |

|       | sleep instruction is completely executed.     |

The WDT is cleared when the device wakes-up from sleep, regardless of the source of wake-up.

|                                             |              |              | Q1   Q2   Q3   Q4                      | Q1 Q2 Q3 Q4                           | Q1 Q2 Q3 Q4 |

|---------------------------------------------|--------------|--------------|----------------------------------------|---------------------------------------|-------------|

|                                             |              |              | $\mathcal{A} \cup \cup \cup \cup \cup$ | $/ \cup \cup \cup \cup$               |             |

| CLKOUT(4)                                   | -\           | /            | <u>\</u> /                             | \/                                    |             |

| INT pin                                     |              |              | ,<br>,<br>,                            | ı<br>I                                |             |

| INTF flag<br>(INTCON<1>)                    |              |              | Interrupt Latency                      | · · · · · · · · · · · · · · · · · · · |             |

|                                             |              |              | 1                                      | 1 · · · ·                             |             |

| GIE bit<br>(INTCON<7>)                      | Processor in | <br>         |                                        | I                                     |             |

|                                             | SLEEP        |              |                                        |                                       |             |

| INSTRUCTION FLOW                            |              |              |                                        |                                       |             |

| PC X PC X PC+1                              | PC+2         | PC+2         | X PC + 2                               | X 0004h                               | X 0005h     |

| Instruction { Inst(PC) = SLEEP Inst(PC + 1) | 1            | Inst(PC + 2) | 1<br>1<br>1                            | Inst(0004h)                           | Inst(0005h) |

| Instruction Inst(PC - 1) SLEEP              | 1            | Inst(PC + 1) | Dummy cycle                            | Dummy cycle                           | Inst(0004h) |

|                                             |              |              |                                        |                                       |             |

### FIGURE 10-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**Note 1:** XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay does not occur for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

| IORWF            | Inclusive OR W with f                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                          |

| Operation:       | (W) .OR. (f) $\rightarrow$ (dest)                                                                                                                                    |

| Status Affected: | Z                                                                                                                                                                    |

| Encoding:        | 00 0100 dfff ffff                                                                                                                                                    |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |

| Words:           | 1                                                                                                                                                                    |

| Cycles:          | 1                                                                                                                                                                    |

| Example          | IORWF RESULT, 0                                                                                                                                                      |

|                  | $\begin{array}{rcl} Before \ Instruction \\ RESULT &= & 0x13 \\ W &= & 0x91 \\ After \ Instruction \\ RESULT &= & 0x13 \\ W &= & 0x93 \\ Z &= & 1 \end{array}$       |

| MOVF             | Move f                                                                                                                                                                                                                      |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                            |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>d $\in [0,1]$                                                                                                                                                                                          |  |  |  |  |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                    |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                           |  |  |  |  |

| Encoding:        | 00 1000 dfff ffff                                                                                                                                                                                                           |  |  |  |  |

|                  | to a destination dependant upon the status of d. If $d = 0$ , destination is W register. If $d = 1$ , the destination is file register f itself. $d = 1$ is useful to test a file register since status flag Z is affected. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                           |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                           |  |  |  |  |

| Example          | MOVF FSR, 0                                                                                                                                                                                                                 |  |  |  |  |

|                  | After Instruction<br>W = value in FSR register<br>Z = 1                                                                                                                                                                     |  |  |  |  |

| MOVLW            | Move Literal to W                                                                          |

|------------------|--------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                        |

| Operation:       | $k \rightarrow (W)$                                                                        |

| Status Affected: | None                                                                                       |

| Encoding:        | 11 00xx kkkk kkkk                                                                          |

| Description:     | The eight bit literal 'k' is loaded into W register. The don't cares will assemble as 0's. |

| Words:           | 1                                                                                          |

| Cycles:          | 1                                                                                          |

| Example          | MOVLW 0x5A                                                                                 |

|                  | After Instruction<br>W = 0x5A                                                              |

| MOVWF            | Move W to f                                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] MOVWF f                                                                                                                                                                                                            |

| Operands:        | $0 \leq f \leq 127$                                                                                                                                                                                                        |

| Operation:       | $(W) \rightarrow (f)$                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                       |

| Encoding:        | 00 0000 1fff ffff                                                                                                                                                                                                          |

| Description:     | Move data from W register to register<br>'f'.                                                                                                                                                                              |

| Words:           | 1                                                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                                                          |

| Example          | MOVWF OPTION                                                                                                                                                                                                               |

|                  | $\begin{array}{rcl} \text{Before Instruction} & & \\ & \text{OPTION} & = & 0 \text{xFF} \\ W & = & 0 \text{x4F} \\ \text{After Instruction} & & \\ & \text{OPTION} & = & 0 \text{x4F} \\ W & = & 0 \text{x4F} \end{array}$ |

| NOP              | No Oper    | ation |      |      |

|------------------|------------|-------|------|------|

| Syntax:          | [ label ]  | NOP   |      |      |

| Operands:        | None       |       |      |      |

| Operation:       | No opera   | ition |      |      |

| Status Affected: | None       |       |      |      |

| Encoding:        | 0 0        | 0000  | 0xx0 | 0000 |

| Description:     | No operati | ion.  |      |      |

| Words:           | 1          |       |      |      |

| Cycles:          | 1          |       |      |      |

| Example          | NOP        |       |      |      |

| RETFIE           | Return from Int                                                 | terrupt   |

|------------------|-----------------------------------------------------------------|-----------|

| Syntax:          | [label] RETF                                                    | IE        |

| Operands:        | None                                                            |           |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$         |           |

| Status Affected: | None                                                            |           |

| Encoding:        | 00 0000                                                         | 0000 1001 |

| Description:     | and Top of Stack (<br>the PC. Interrupts<br>setting Global Inte |           |

| Words:           | 1                                                               |           |

| Cycles:          | 2                                                               |           |

| Example          | RETFIE                                                          |           |

|                  | After Interrupt<br>PC =<br>GIE =                                | TOS<br>1  |

| OPTION                                       | Load Option Register                                                                                                                                                                                                                                       |  |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:                                      | [label] OPTION                                                                                                                                                                                                                                             |  |  |  |

| Operands:                                    | None                                                                                                                                                                                                                                                       |  |  |  |

| Operation:                                   | $(W) \rightarrow OPTION$                                                                                                                                                                                                                                   |  |  |  |

| Status Affected:                             | None                                                                                                                                                                                                                                                       |  |  |  |

| Encoding:                                    | 00 0000 0110 0010                                                                                                                                                                                                                                          |  |  |  |

| Description:<br>Words:<br>Cycles:<br>Example | The contents of the W register are<br>loaded in the OPTION register. This<br>instruction is supported for code<br>compatibility with PIC16C5X products.<br>Since OPTION is a readable/writable<br>register, the user can directly<br>address it.<br>1<br>1 |  |  |  |

|                                              | To maintain upward compatibility<br>with future PIC <sup>®</sup> MCU products, do<br>not use this instruction.                                                                                                                                             |  |  |  |

| RETLW            | Return with Literal in W                                                                                                                                                            |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                                                                                                   |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                        |

| Status Affected: | None                                                                                                                                                                                |

| Encoding:        | 11 01xx kkkk kkkk                                                                                                                                                                   |

| Description:     | The W register is loaded with the eight<br>bit literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                   |

| Cycles:          | 2                                                                                                                                                                                   |

| Example          | CALL TABLE ;W contains table<br>;offset value<br>;W now has table<br>value                                                                                                          |

| TABLE            | ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;                                                                                                                         |

|                  | RETLW kn ; End of table                                                                                                                                                             |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                      |

|                  | After Instruction<br>W = value of k8                                                                                                                                                |

# 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

### 12.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

### 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

### 12.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script. stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

### 12.11 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PIC devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

### 12.12 <u>SIMICE Entry-Level</u> <u>Hardware Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB-SIM. Both SIMICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PIC 8-bit microcontrollers. SIM-ICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entry-level system development.

### 12.13 <u>PICDEM-1 Low-Cost PIC MCU</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

### 12.14 <u>PICDEM-2 Low-Cost PIC16CXX</u> <u>Demonstration Board</u>

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

### 12.15 <u>PICDEM-3 Low-Cost PIC16CXXX</u> <u>Demonstration Board</u>

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

## 12.16 PICDEM-17

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756, PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

### 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

NOTES:

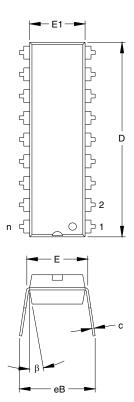

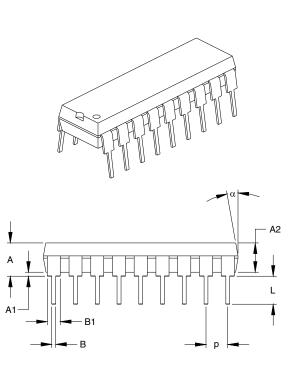

### 18-Lead Plastic Dual In-line (P) – 300 mil (PDIP)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units     | INCHES* |      | MILLIMETERS |       | 3     |       |

|----------------------------|-----------|---------|------|-------------|-------|-------|-------|

| Dimensio                   | on Limits | MIN     | NOM  | MAX         | MIN   | NOM   | MAX   |

| Number of Pins             | n         |         | 18   |             |       | 18    |       |

| Pitch                      | р         |         | .100 |             |       | 2.54  |       |

| Top to Seating Plane       | Α         | .140    | .155 | .170        | 3.56  | 3.94  | 4.32  |

| Molded Package Thickness   | A2        | .115    | .130 | .145        | 2.92  | 3.30  | 3.68  |

| Base to Seating Plane      | A1        | .015    |      |             | 0.38  |       |       |

| Shoulder to Shoulder Width | Е         | .300    | .313 | .325        | 7.62  | 7.94  | 8.26  |

| Molded Package Width       | E1        | .240    | .250 | .260        | 6.10  | 6.35  | 6.60  |

| Overall Length             | D         | .890    | .898 | .905        | 22.61 | 22.80 | 22.99 |

| Tip to Seating Plane       | L         | .125    | .130 | .135        | 3.18  | 3.30  | 3.43  |

| Lead Thickness             | С         | .008    | .012 | .015        | 0.20  | 0.29  | 0.38  |

| Upper Lead Width           | B1        | .045    | .058 | .070        | 1.14  | 1.46  | 1.78  |

| Lower Lead Width           | В         | .014    | .018 | .022        | 0.36  | 0.46  | 0.56  |

| Overall Row Spacing        | eB        | .310    | .370 | .430        | 7.87  | 9.40  | 10.92 |

| Mold Draft Angle Top       | α         | 5       | 10   | 15          | 5     | 10    | 15    |

| Mold Draft Angle Bottom    | β         | 5       | 10   | 15          | 5     | 10    | 15    |

\*Controlling Parameter

Notes:

Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" (0.254mm) per side. JEDEC Equivalent: MS-001

Drawing No. C04-007

| Port RB Interrupt                    | 60 |

|--------------------------------------|----|

| PORTA                                |    |

| PORTB                                |    |

| Power Control/Status Register (PCON) | 55 |

| Power-Down Mode (SLEEP)              | 63 |

| Power-On Reset (POR)                 | 54 |

| Power-up Timer (PWRT)                | 54 |

| Prescaler                            |    |

| PRO MATE® II Universal Programmer    | 79 |

| Program Memory Organization          | 11 |

| •                                    |    |

## Q

# R

| 53 |

|----|

| 73 |

| 73 |

| 74 |

| 74 |

| 74 |

|    |

# S

| SEEVAL® Evaluation and Programming System             | 80 |

|-------------------------------------------------------|----|

| Serialized Quick-Turnaround-Production (SQTP) Devices | 5  |

| SLEEP Instruction                                     | 74 |

| Software Simulator (MPLAB-SIM)                        | 78 |

| Special Features of the CPU                           | 49 |

| Special Function Registers                            | 14 |

| Stack                                                 | 20 |

| Status Register                                       | 15 |

| SUBLW Instruction                                     | 75 |

| SUBWF Instruction                                     | 75 |

| SWAPF Instruction                                     | 76 |

### **T** Timer0

| Timer0                             |

|------------------------------------|

| TIMER0                             |

| TIMER0 (TMR0) Interrupt35          |

| TIMER0 (TMR0) Module               |

| TMR0 with External Clock           |

| Timer1                             |

| Switching Prescaler Assignment     |

| Timing Diagrams and Specifications |

| TMR0 Interrupt                     |

| TRIS Instruction                   |

| TRISA23                            |

| TRISB                              |

| V                                  |

| Voltage Reference Module47         |

| VRCON Register                     |

| W                                  |

| Watchdog Timer (WDT)61             |

| WWW, On-Line Support2              |

| x                                  |

| XORLW Instruction                  |

| XORWF Instruction76                |

NOTES:

# Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820