Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            |                                                                              |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16ce625t-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

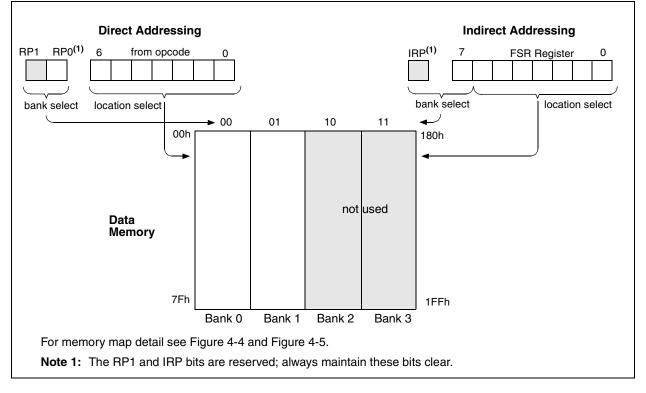

#### 4.2 Data Memory Organization

The data memory (Figure 4-4 and Figure 4-5) is partitioned into two Banks which contain the General Purpose Registers and the Special Function Registers. Bank 0 is selected when the RP0 bit is cleared. Bank 1 is selected when the RP0 bit (STATUS <5>) is set. The Special Function Registers are located in the first 32 locations of each Bank. Register locations 20-7Fh (Bank0) on the PIC16CE623/624 and 20-7Fh (Bank0) and A0-BFh (Bank1) on the PIC16CE625 are General Purpose Registers implemented as static RAM. Some special purpose registers are mapped in Bank 1. In all three microcontrollers, address space F0h-FFh (Bank1) is mapped to 70-7Fh (Bank0) as common RAM.

#### 4.2.1 GENERAL PURPOSE REGISTER FILE

The register file is organized as  $96 \times 8$  in the PIC16CE623/624 and 128 x 8 in the PIC16CE625. Each is accessed either directly or indirectly through the File Select Register FSR (Section 4.4).

# PIC16CE62X

#### 4.2.2.2 OPTION REGISTER

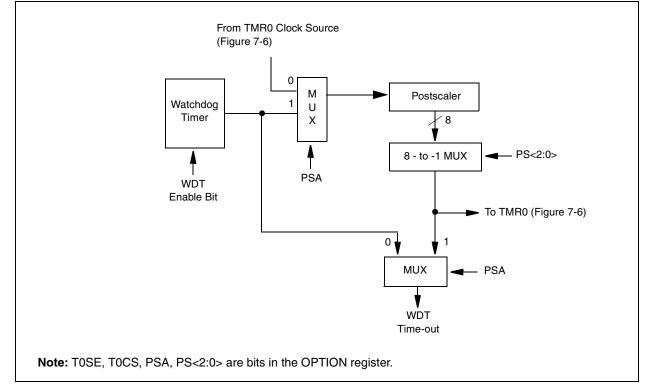

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

## REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1    | R/W-1                                                                                                                                                             | R/W-1                                                       | R/W-1        | R/W-1     | R/W-1 | R/W-1 | R/W-1 |                                                                                                                   |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------|-----------|-------|-------|-------|-------------------------------------------------------------------------------------------------------------------|--|--|

| RBPU     | INTEDG                                                                                                                                                            | TOCS                                                        | TOSE         | PSA       | PS2   | PS1   | PS0   | R = Readable bit                                                                                                  |  |  |

| bit7     |                                                                                                                                                                   |                                                             |              |           |       |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |  |  |

| bit 7:   | <b>RBPU</b> : PORTB Pull-up Enable bit<br>1 = PORTB pull-ups are disabled<br>0 = PORTB pull-ups are enabled by individual port latch values                       |                                                             |              |           |       |       |       |                                                                                                                   |  |  |

| bit 6:   | INTEDG: In<br>1 = Interrup<br>0 = Interrup                                                                                                                        | ot on rising                                                | g edge o     | f RB0/INT |       |       |       |                                                                                                                   |  |  |

| bit 5:   | <b>TOCS</b> : TMF<br>1 = Transiti<br>0 = Interna                                                                                                                  | ion on RA                                                   | 4/T0CKI      | pin       | (OUT) |       |       |                                                                                                                   |  |  |

| bit 4:   | <b>T0SE</b> : TMR0 Source Edge Select bit<br>1 = Increment on high-to-low transition on RA4/T0CKI pin<br>0 = Increment on low-to-high transition on RA4/T0CKI pin |                                                             |              |           |       |       |       |                                                                                                                   |  |  |

| bit 3:   | <b>PSA</b> : Prescaler Assignment bit<br>1 = Prescaler is assigned to the WDT<br>0 = Prescaler is assigned to the Timer0 module                                   |                                                             |              |           |       |       |       |                                                                                                                   |  |  |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : F                                                                                                                                          | Prescaler I                                                 | Rate Sele    | ect bits  |       |       |       |                                                                                                                   |  |  |

|          | Bit Value                                                                                                                                                         | TMR0 Ra                                                     | te WD1       | Γ Rate    |       |       |       |                                                                                                                   |  |  |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                              | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 :<br>3 1 : | 2<br>4    |       |       |       |                                                                                                                   |  |  |

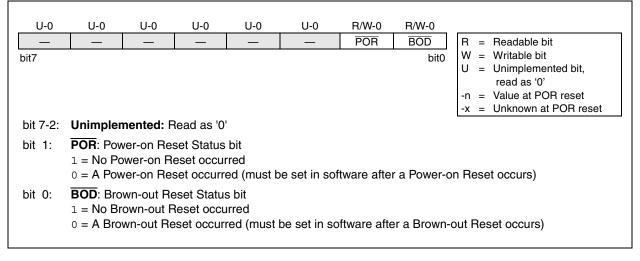

#### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset, an external  $\overline{\text{MCLR}}$  reset, WDT reset or a Brown-out Reset.

| Note: | BOD is unknown on Power-on Reset. It        |

|-------|---------------------------------------------|

|       | must then be set by the user and checked    |

|       | on subsequent resets to see if BOD is       |

|       | cleared, indicating a brown-out has         |

|       | occurred. The BOD status bit is a "don't    |

|       | care" and is not necessarily predictable if |

|       | the brown-out circuit is disabled (by       |

|       | programming BODEN bit in the                |

|       | configuration word).                        |

#### REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16CE62X. A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

| EXAMPLE 4-1: |       | INDIRECT ADDRESSING |                      |  |  |

|--------------|-------|---------------------|----------------------|--|--|

|              | movlw |                     | ;initialize pointer  |  |  |

|              | movwf | FSR                 | ;to RAM              |  |  |

| NEXT         | clrf  | INDF                | clear INDF register; |  |  |

|              | incf  | FSR                 | ;inc pointer         |  |  |

|              | btfss | FSR,4               | ;all done?           |  |  |

|              | goto  | NEXT                | ;no clear next       |  |  |

|              |       |                     | ;yes continue        |  |  |

| CONTINUE:    |       |                     |                      |  |  |

#### FIGURE 4-7: DIRECT/INDIRECT ADDRESSING PIC16CE62X

#### 6.3 Write Operations

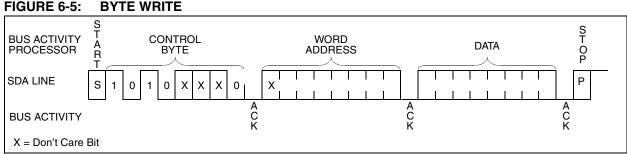

#### BYTE WRITE 6.3.1

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the R/W bit, which is a logic low, is placed onto the bus by the processor. This indicates to the EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer of the EEPROM. After receiving another acknowledge signal from the EEPROM, the processor will transmit the data word to be written into the addressed memory location. The EEPROM acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time, the EEPROM will not generate acknowledge signals (Figure 6-5).

#### 6.3.2 PAGE WRITE

The write control byte, word address and the first data byte are transmitted to the EEPROM in the same way as in a byte write. But instead of generating a stop condition, the processor transmits up to eight data bytes to the EEPROM, which are temporarily stored in the onchip page buffer and will be written into the memory after the processor has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the processor should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin (Figure 6-6).

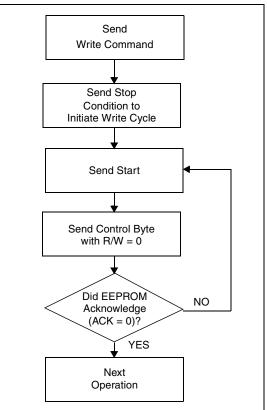

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the EEPROM initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. See Figure 6-4 for flow diagram.

#### FIGURE 6-4: ACKNOWLEDGE POLLING FLOW

#### FIGURE 6-5:

#### 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

## 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

#### 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

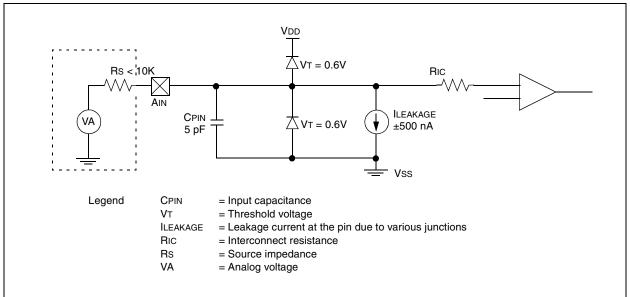

#### 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 8-4: ANALOG INPUT MODEL

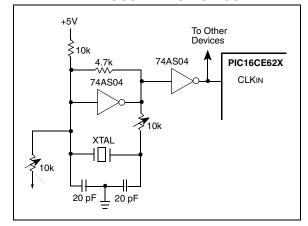

#### 10.2.3 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used; one with series resonance or one with parallel resonance.

Figure 10-3 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180° phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometers bias the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 10-3: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

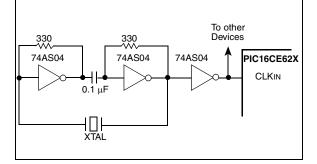

Figure 10-4 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180° phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 10-4: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

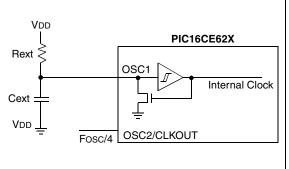

#### 10.2.4 RC OSCILLATOR

For timing insensitive applications the "RC" device option offers additional cost savings. The RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, the oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect the oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 10-5 shows how the R/C combination is connected to the PIC16CE62X. For Rext values below 2.2 k $\Omega$ , the oscillator operation may become unstable, or stop completely. For very high Rext values (i.e., 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3 k $\Omega$  and 100 k $\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With no or small external capacitance, the oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 14.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 14.0 for variation of oscillator frequency due to VDD for given Rext/Cext values, as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin and can be used for test purposes or to synchronize other logic (Figure 3-2 for waveform).

# FIGURE 10-5: RC OSCILLATOR MODE

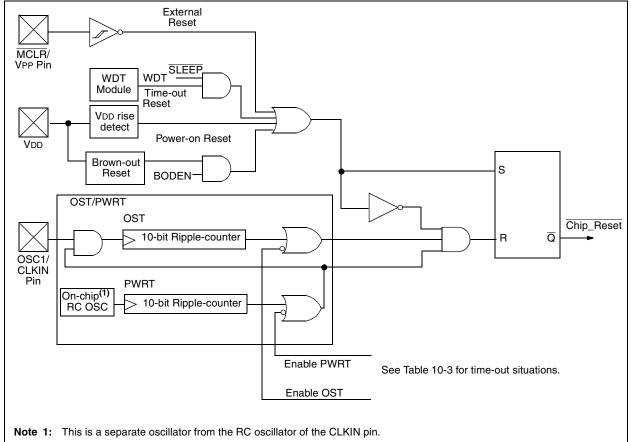

#### 10.3 <u>Reset</u>

The PIC16CE62X differentiates between various kinds of reset:

- a) Power-on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOD)

Some registers are not affected in any reset condition. Their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on reset, MCLR reset, WDT reset and MCLR reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different reset situations as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-6.

The  $\overline{\text{MCLR}}$  reset path has a noise filter to detect and ignore small pulses. See Table 13-5 for pulse width specification.

#### FIGURE 10-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

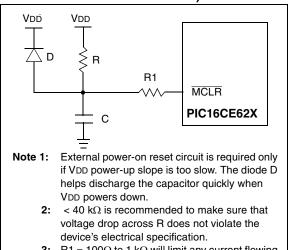

#### FIGURE 10-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

**3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

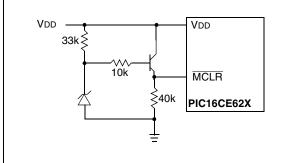

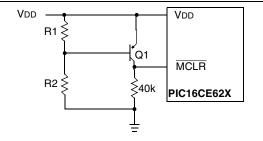

#### FIGURE 10-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal Brown-out Reset circuitry should be disabled when using this circuit.

#### FIGURE 10-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \times \frac{R1}{R1 + R2} = 0.7 V$$

- **2:** Internal brown-out detection should be disabled when using this circuit.

- **3:** Resistors should be adjusted for the characteristics of the transistor.

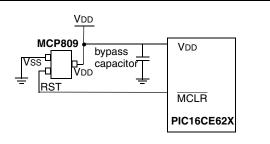

#### FIGURE 10-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

### FIGURE 10-17: WATCHDOG TIMER BLOCK DIAGRAM

#### FIGURE 10-18: SUMMARY OF WATCHDOG TIMER REGISTERS

| Address | Name         | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------------|-------|--------|-------|-------|-------|-------|-------|-------|

| 2007h   | Config. bits |       | BOREN  | CP1   | CP0   | PWRTE | WDTE  | FOSC1 | FOSC0 |

| 81h     | OPTION       | RBPU  | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

Legend: - = Unimplemented location, read as "0", + = Reserved for future use

Note: Shaded cells are not used by the Watchdog Timer.

# PIC16CE62X

| BTFSS            | Bit Test f, Skip if Set                                                  |                                                                                                             |                                           |                           |  |

|------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------|--|

| Syntax:          | [ <i>label</i> ] B                                                       | TFSS f,b                                                                                                    | )                                         |                           |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b < 7 \end{array}$          | 7                                                                                                           |                                           |                           |  |

| Operation:       | skip if (f<                                                              | b>) = 1                                                                                                     |                                           |                           |  |

| Status Affected: | None                                                                     |                                                                                                             |                                           |                           |  |

| Encoding:        | 01                                                                       | 11bb                                                                                                        | bfff                                      | ffff                      |  |

| Description:     | instruction<br>If bit 'b' is '<br>fetched du<br>execution,<br>executed i | register 'f' is<br>is skipped.<br>1', then the<br>ring the cur<br>is discarde<br>nstead, ma<br>instruction. | next instru<br>rrent instru<br>d and a No | uction<br>Iction<br>DP is |  |

| Words:           | 1                                                                        |                                                                                                             |                                           |                           |  |

| Cycles:          | 1(2)                                                                     |                                                                                                             |                                           |                           |  |

| Example          | HERE<br>FALSE<br>TRUE                                                    |                                                                                                             | FLAG, 1<br>PROCESS_                       | _CODE                     |  |

|                  | Before In                                                                | struction                                                                                                   |                                           |                           |  |

|                  | After Inst                                                               | ruction<br>if FLAG<1><br>PC = a<br>if FLAG<1>                                                               | = 0,<br>address F                         |                           |  |

| CLRF             | Clear f                                                               |                    |             |           |  |

|------------------|-----------------------------------------------------------------------|--------------------|-------------|-----------|--|

| Syntax:          | [label] (                                                             | CLRF f             |             |           |  |

| Operands:        | $0 \le f \le 12$                                                      | 27                 |             |           |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |                    |             |           |  |

| Status Affected: | Z                                                                     |                    |             |           |  |

| Encoding:        | 0 0                                                                   | 0001               | lfff        | ffff      |  |

| Description:     | The conte and the Z                                                   | 0                  | ster 'f' ar | e cleared |  |

| Words:           | 1                                                                     |                    |             |           |  |

| Cycles:          | 1                                                                     |                    |             |           |  |

| Example          | CLRF                                                                  | FLAC               | G_REG       |           |  |

|                  | Before In                                                             | struction          |             |           |  |

|                  |                                                                       | FLAG_RE            | EG =        | 0x5A      |  |

|                  | After Inst                                                            | ruction<br>Flag Re | EG =        | 0x00      |  |

|                  |                                                                       | Z                  | =           | 1         |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |  |  |  |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<4:3>) → PC<12:11>                                                                                                                                                                                   |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                          |  |  |  |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                             |  |  |  |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle instruc-<br>tion. |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                             |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                                             |  |  |  |

| Example          | HERE CALL THERE                                                                                                                                                                                                                               |  |  |  |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                    |  |  |  |

| Clear W                                                               |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| [ label ]                                                             | CLRW                                                                                                          |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| None                                                                  |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| Z                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| 00                                                                    | 0001                                                                                                          | 0000                                                                                                                                                             | 0011                                                                                                                                                                                          |  |

| W register set.                                                       | is cleare                                                                                                     | d. Zero bit                                                                                                                                                      | (Z) is                                                                                                                                                                                        |  |

| 1                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| 1                                                                     |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| CLRW                                                                  |                                                                                                               |                                                                                                                                                                  |                                                                                                                                                                                               |  |

| Before In                                                             | structior                                                                                                     | l                                                                                                                                                                |                                                                                                                                                                                               |  |

| After Inst                                                            | ruction<br>W =                                                                                                | 0x5A<br>0x00<br>1                                                                                                                                                |                                                                                                                                                                                               |  |

|                                                                       | $[label]$ None $00h \rightarrow (V \\ 1 \rightarrow Z$ $Z$ $00$ W register set. 1 $CLRW$ Before In After Inst | $[label] CLRW$ None $00h \rightarrow (W)$ $1 \rightarrow Z$ $Z$ $00 0001$ W register is cleared set. $1$ $CLRW$ Before Instruction $W =$ After Instruction $W =$ | $[label] CLRW$ None $00h \rightarrow (W)$ $1 \rightarrow Z$ Z $00  0001  0000$ W register is cleared. Zero bit set. $1$ $1$ $CLRW$ Before Instruction $W = 0x5A$ After Instruction $W = 0x00$ |  |

$\odot$  1998-2013 Microchip Technology Inc.

| GOTO                                    | Unconditional Branch                                                                                                                                                                               | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                                 | [ <i>label</i> ] GOTO k                                                                                                                                                                            | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:                               | $0 \le k \le 2047$                                                                                                                                                                                 | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                              |

| Operation:                              | $k \rightarrow PC < 10:0 >$                                                                                                                                                                        |                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                      |

|                                         | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected:                        | None                                                                                                                                                                                               | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |

| Encoding:                               | 10 1kkk kkkk kkkk                                                                                                                                                                                  | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                              |

| Description:<br>Words:<br>Cycles:       | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.<br>1 | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. |

| Example                                 | GOTO THERE                                                                                                                                                                                         | Words:           | 1                                                                                                                                                                                                                                                                                                                              |

| After Instruction<br>PC = Address THERE |                                                                                                                                                                                                    | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |

|                                         | FC = Addless There                                                                                                                                                                                 | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                |

|                                         |                                                                                                                                                                                                    |                  | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                |

|                                         |                                                                                                                                                                                                    |                  | •                                                                                                                                                                                                                                                                                                                              |

$\begin{array}{rcl} Before \ Instruction \\ PC &= & address \ HERE \\ After \ Instruction \\ CNT &= & CNT + 1 \\ if \ CNT = & 0, \\ PC &= & address \ CONTINUE \\ if \ CNT \neq & 0, \\ PC &= & address \ HERE \ +1 \\ \end{array}$

| INCF             | Increment f                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                   |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                   |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |

| Words:           | 1                                                                                                                                                                   |

| Cycles:          | 1                                                                                                                                                                   |

| Example          | INCF CNT, 1                                                                                                                                                         |

|                  | Before Instruction $CNT = 0xFF$ $Z = 0$ After Instruction $CNT = 0x00$ $Z = 1$                                                                                      |

| IORLW            | Inclusive OR Literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                           |

| Status Affected: | Z                                                                                                                      |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                      |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:           | 1                                                                                                                      |

| Cycles:          | 1                                                                                                                      |

| Example          | IORLW 0x35                                                                                                             |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                               |

| SUBLW        | Subtract W from Literal                                                                    | SUBWF        | Subtract W from f                                                                  |  |  |

|--------------|--------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------|--|--|

| Syntax:      | [label] SUBLW k                                                                            | Syntax:      | [label] SUBWF f,d                                                                  |  |  |

| Operands:    | $0 \le k \le 255$                                                                          | Operands:    | $0 \leq f \leq 127$                                                                |  |  |

| Operation:   | $k - (W) \rightarrow (W) \qquad \qquad d \in [0,1]$                                        |              |                                                                                    |  |  |

| Status       | C, DC, Z                                                                                   | Operation:   | (f) - (W) $\rightarrow$ (dest)                                                     |  |  |

| Affected:    |                                                                                            | Status       | C, DC, Z                                                                           |  |  |

| Encoding:    | 11 110x kkkk kkkk                                                                          | Affected:    |                                                                                    |  |  |

| Description: | The W register is subtracted (2's com-                                                     | Encoding:    | 00 0010 dfff ffff                                                                  |  |  |

|              | plement method) from the eight bit literal<br>'k'. The result is placed in the W register. | Description: | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0, the |  |  |

| Words:       | 1                                                                                          |              | result is stored in the W register. If 'd' is 1,                                   |  |  |

| Cycles:      | 1                                                                                          |              | the result is stored back in register 'f'.                                         |  |  |

| Example 1:   | SUBLW 0x02                                                                                 | Words:       | 1                                                                                  |  |  |

|              | Before Instruction                                                                         | Cycles:      | 1                                                                                  |  |  |

|              |                                                                                            | Example 1:   | SUBWF REG1,1                                                                       |  |  |

|              | W = 1 $C = ?$                                                                              |              | Before Instruction                                                                 |  |  |

|              | After Instruction                                                                          |              | REG1 = 3                                                                           |  |  |

|              | W = 1                                                                                      |              | W = 2 $C = ?$                                                                      |  |  |

|              | C = 1; result is positive                                                                  |              | After Instruction                                                                  |  |  |

| Example 2:   | Before Instruction                                                                         |              | REG1 = 1                                                                           |  |  |

|              | W = 2                                                                                      |              | W = 2                                                                              |  |  |

|              | C = ?                                                                                      | Example 2:   | C = 1; result is positive                                                          |  |  |

|              | After Instruction                                                                          |              | Before Instruction                                                                 |  |  |

|              | W = 0<br>C = 1; result is zero                                                             |              | REG1 = 2<br>W = 2                                                                  |  |  |

| Example 3:   | Before Instruction                                                                         |              | C = ?                                                                              |  |  |

|              | W = 3                                                                                      |              | After Instruction                                                                  |  |  |

|              | C = ?                                                                                      |              | REG1 = 0                                                                           |  |  |

|              | After Instruction                                                                          |              | W = 2                                                                              |  |  |

|              | W = 0xFF                                                                                   | Evenuela Or  | C = 1; result is zero                                                              |  |  |

|              | C = 0; result is nega-<br>tive                                                             | Example 3:   | Before Instruction                                                                 |  |  |

|              |                                                                                            |              | REG1 = 1<br>W = 2                                                                  |  |  |

|              |                                                                                            |              | C = ?                                                                              |  |  |

|              |                                                                                            |              | After Instruction                                                                  |  |  |

|              |                                                                                            |              | REG1 = 0xFF                                                                        |  |  |

|              |                                                                                            |              | W = 2<br>C = 0; result is negative                                                 |  |  |

|              |                                                                                            |              |                                                                                    |  |  |

## 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

#### 12.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

#### 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

#### 12.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

# PIC16CE62X

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

#### 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

## **13.0 ELECTRICAL SPECIFICATIONS**

#### Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                                     | 40° to +125°C                                      |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Storage Temperature                                                                                                                | 65° to +150°C                                      |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                       |                                                    |

| Voltage on VDD with respect to VSS                                                                                                 | 0 to +7.0V                                         |

| Voltage on RA4 with respect to Vss                                                                                                 | 8.5V                                               |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                       | 0 to +14V                                          |

| Voltage on RA4 with respect to Vss                                                                                                 |                                                    |

| Total power Dissipation (Note 1)                                                                                                   | 1.0W                                               |

| Maximum Current out of Vss pin                                                                                                     |                                                    |

| Maximum Current into VDD pin                                                                                                       | 250 mA                                             |

| Input Clamp Current, Iк (VI <0 or VI> VDD)                                                                                         | ±20 mA                                             |

| Output Clamp Current, IOK (Vo <0 or Vo>VDD)                                                                                        | ±20 mA                                             |

| Maximum Output Current sunk by any I/O pin                                                                                         | 25 mA                                              |

| Maximum Output Current sourced by any I/O pin                                                                                      | 25 mA                                              |

| Maximum Current sunk by PORTA and PORTB                                                                                            | 200 mA                                             |

| Maximum Current sourced by PORTA and PORTB                                                                                         | 200 mA                                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 100 + $\sum$ IOH} | $x \text{ IOH} + \sum (\text{VOI } x \text{ IOL})$ |

2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100<sup>3</sup>/<sub>4</sub> should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 13.3 DC CHARACTERISTICS:

#### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended) PIC16LCE62X (Commercial, Industrial)

|               |                                                                |                                                                 | Standard Opera   | ting (                                               | Conditions (u | Inles | s otherwise stated)                             |  |  |  |  |

|---------------|----------------------------------------------------------------|-----------------------------------------------------------------|------------------|------------------------------------------------------|---------------|-------|-------------------------------------------------|--|--|--|--|

|               |                                                                |                                                                 |                  |                                                      |               |       | +85°C for industrial and                        |  |  |  |  |

| DC CH         | IARAC                                                          | TERISTICS                                                       |                  |                                                      | 0°C ≤         | TA≤   | +70°C for commercial and                        |  |  |  |  |

|               |                                                                |                                                                 |                  | $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended |               |       |                                                 |  |  |  |  |

|               | Operating voltage VDD range as described in DC spec Table 13-1 |                                                                 |                  |                                                      |               |       |                                                 |  |  |  |  |

| Parm          | Sym                                                            | Characteristic                                                  | Min              | Typ†                                                 | Max           | Unit  | Conditions                                      |  |  |  |  |

| No.           |                                                                |                                                                 |                  |                                                      |               |       |                                                 |  |  |  |  |

|               | Vi∟                                                            | Input Low Voltage                                               |                  |                                                      |               |       |                                                 |  |  |  |  |

|               |                                                                | I/O ports                                                       |                  |                                                      |               |       |                                                 |  |  |  |  |

| D030          |                                                                | with TTL buffer                                                 | Vss              | _                                                    | 0.8V          | V     | VDD = 4.5V to 5.5V, Otherwise                   |  |  |  |  |

|               |                                                                |                                                                 |                  |                                                      | 0.15VDD       |       |                                                 |  |  |  |  |

| D031          |                                                                | with Schmitt Trigger input                                      | Vss              |                                                      | 0.2VDD        | V     |                                                 |  |  |  |  |

| D032          |                                                                | MCLR, RA4/T0CKI,OSC1 (in RC                                     | Vss              | -                                                    | 0.2VDD        | V     | Note1                                           |  |  |  |  |

|               |                                                                | mode)                                                           |                  |                                                      |               |       |                                                 |  |  |  |  |

| D033          |                                                                | OSC1 (in XT and HS)                                             | Vss              | -                                                    | 0.3Vdd        | V     |                                                 |  |  |  |  |

|               |                                                                | OSC1 (in LP)                                                    | Vss              | -                                                    | 0.6VDD - 1.0  | V     |                                                 |  |  |  |  |

|               | VIH                                                            | Input High Voltage                                              |                  |                                                      |               |       |                                                 |  |  |  |  |

|               |                                                                | I/O ports                                                       |                  |                                                      |               |       |                                                 |  |  |  |  |

| D040          |                                                                | with TTL buffer                                                 | 2.0V             | -                                                    | VDD           | V     | VDD = 4.5V to 5.5V, Otherwise                   |  |  |  |  |

| <b>D</b> 044  |                                                                |                                                                 | .25VDD + 0.8V    |                                                      | VDD           |       |                                                 |  |  |  |  |

| D041          |                                                                | with Schmitt Trigger input                                      | 0.8VDD           |                                                      | VDD           | .,    |                                                 |  |  |  |  |

| D042          |                                                                | MCLR RA4/T0CKI                                                  | 0.8VDD           | -                                                    | VDD           | V     |                                                 |  |  |  |  |

| D043<br>D043A |                                                                | OSC1 (XT, HS and LP)                                            | 0.7Vdd<br>0.9Vdd | -                                                    | Vdd           | V     | Note1                                           |  |  |  |  |

| D043A         | IPURB                                                          | OSC1 (in RC mode)<br>PORTB weak pull-up current                 | 50               | 200                                                  | 400           | μA    | VDD = 5.0V, VPIN = VSS                          |  |  |  |  |

| 0070          | IPUND                                                          | Input Leakage Current                                           | 50               | 200                                                  | 400           | μΑ    | VDD = 5.0V, VPIN = V35                          |  |  |  |  |