Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                              |

| Supplier Device Package    | 18-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce623-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 PIC16CE62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in the PIC16CE62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

## 2.1 UV Erasable Devices

The UV erasable version, offered in the CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16CE62X.

## 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

## 2.3 <u>Quick-Turn-Programming (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

### 2.4 <u>Serialized Quick-Turn-Programming</u> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The special registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7                  | Bit 6              | Bit 5       | Bit 4         | Bit 3        | Bit 2        | Bit 1        | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>resets <sup>(1)</sup> |

|---------|---------------|------------------------|--------------------|-------------|---------------|--------------|--------------|--------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 00h     | INDF          | Addressin<br>register) | ig this locat      | a physical  | xxxx xxxx     | xxxx xxxx    |              |              |            |                       |                                                |

| 01h     | TMR0          | Timer0 M               | odule's Reg        | jister      |               |              |              |              |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          |              |              |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>     | RP1 <sup>(2)</sup> | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | I            |              | I          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         |                        |                    |             | RA4           | RA3          | RA2          | RA1          | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                    | RB6                | RB5         | RB4           | RB3          | RB2          | RB1          | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h     | Unimplemented |                        | 1                  |             | 1             |              | 1            |              | 1          | -                     | -                                              |

| 08h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 09h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 0Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | —                      | CMIF               | —           | —             | —            | —            | —            | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                        |                    |             |               |              |              |              |            | —                     | _                                              |

| 1Fh     | CMCON         | C2OUT                  | C10UT              | _           |               | CIS          | CM2          | CM1          | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 80h     | INDF          | Addressin<br>register) | ig this locat      | ion uses co | ontents of F  | SR to addre  | ess data me  | emory (not a | a physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                   | INTEDG             | TOCS        | T0SE          | PSA          | PS2          | PS1          | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          | 1            |              | 1          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP                    | RP1                | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | 1            |              | 1          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                      |                    |             | TRISA4        | TRISA3       | TRISA2       | TRISA1       | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7                 | TRISB6             | TRISB5      | TRISB4        | TRISB3       | TRISB2       | TRISB1       | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 88h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 89h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                      | CMIE               | _           | —             | _            | —            | _            | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Eh     | PCON          | —                      | —                  | —           | _             | —            | —            | POR          | BOD        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 90h     | EEINTF        | —                      | —                  | —           | _             | —            | EESCL        | EESDA        | EEVDD      | 111                   | 111                                            |

| 9Fh     | VRCON         | VREN                   | VROE               | VRR         | _             | VR3          | VR2          | VR1          | VR0        | 000- 0000             | 000- 0000                                      |

#### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16CE62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non power-up) resets include MCLR reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

Note 2: IRP & RPI bits are reserved; always maintain these bits clear.

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

| R/W-0       | R/W-0 | R/W-0        | R/W-0                                     | R/W-0        | R/W-0       | R/W-0       | R/W-x        |                                                                                                                                       |

|-------------|-------|--------------|-------------------------------------------|--------------|-------------|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| GIE<br>bit7 | PEIE  | TOIE         | INTE                                      | RBIE         | TOIF        | INTF        | RBIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |

| bit 7:      |       |              | masked in                                 |              |             |             |              |                                                                                                                                       |

| bit 6:      |       | es all un-r  | terrupt En<br>masked pe<br>ipheral int    | eripheral ir | nterrupts   |             |              |                                                                                                                                       |

| bit 5:      |       | es the TN    | ow Interrup<br>IR0 interru<br>IR0 interru | ıpt          | bit         |             |              |                                                                                                                                       |

| bit 4:      |       | es the RB    | ernal Inter<br>0/INT exte<br>30/INT ext   | ernal interi | rupt        |             |              |                                                                                                                                       |

| bit 3:      |       | es the RB    | nge Interr<br>port char<br>3 port cha     | ige interru  | pt          |             |              |                                                                                                                                       |

| bit 2:      |       | ) register l |                                           | wed (mus     | t be cleare | d in softwa | ure)         |                                                                                                                                       |

| bit 1:      |       | RB0/INT e    |                                           | errupt occ   | urred (must | t be cleare | d in softwar | re)                                                                                                                                   |

| bit 0:      |       | at least c   | one of the                                | RB<7:4> p    |             | •           | ust be clea  | red in software)                                                                                                                      |

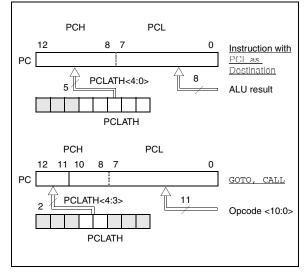

## 4.3 PCL and PCLATH

The program counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any reset, the PC is cleared. Figure 4-6 shows the two situations for the loading of the PC. The upper example in the figure shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in the figure shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

#### FIGURE 4-6: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.3.1 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When doing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256 byte block). Refer to the application note, *"Implementing a Table Read"* (AN556).

#### 4.3.2 STACK

The PIC16CE62X family has an 8 level deep x 13-bit wide hardware stack (Figure 4-2 and Figure 4-3). The stack space is not part of either program or data space and the stack pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no STATUS bits to indicate stack overflow or stack underflow conditions.

- Note 2: There are no instruction/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

## TABLE 5-1:PORTA FUNCTIONS

| Name         | e Bit # Buffer<br>Type |    | Function                                                                                          |

|--------------|------------------------|----|---------------------------------------------------------------------------------------------------|

| RA0/AN0      | bit0                   | ST | Input/output or comparator input                                                                  |

| RA1/AN1      | bit1                   | ST | Input/output or comparator input                                                                  |

| RA2/AN2/VREF | bit2                   | ST | Input/output or comparator input or VREF output                                                   |

| RA3/AN3      | bit3                   | ST | Input/output or comparator input/output                                                           |

| RA4/T0CKI    | bit4                   | ST | Input/output or external clock input for TMR0 or comparator output.<br>Output is open drain type. |

Legend: ST = Schmitt Trigger input

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|------------------|---------------------------------|

| 05h     | PORTA | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | x 0000           | u 0000                          |

| 85h     | TRISA | _     | _     | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111           | 1 1111                          |

| 1Fh     | CMCON | C2OUT | C10UT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000          | 00 0000                         |

| 9Fh     | VRCON | VREN  | VROE  | VRR   |        | VR3    | VR2    | VR1    | VR0    | 000- 0000        | 000- 0000                       |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged

Note: Shaded bits are not used by PORTA.

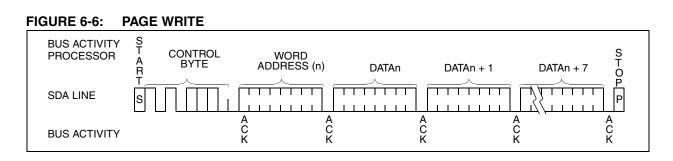

## 6.0 EEPROM PERIPHERAL OPERATION

The PIC16CE623/624/625 each have 128 bytes of EEPROM data memory. The EEPROM data memory supports a bi-directional, 2-wire bus and data transmission protocol. These two-wires are serial data (SDA) and serial clock (SCL), and are mapped to bit1 and bit2, respectively, of the EEINTF register (SFR 90h). In addition, the power to the EEPROM can be controlled using bit0 (EEVDD) of the EEINTF register. For most applications, all that is required is calls to the following functions:

| ;<br>;<br>; | Inputs: EEPROM Address EEADDR             |  |  |  |  |  |  |  |  |  |  |  |

|-------------|-------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| ;           | Outputs: Return 01 in W if OK, else       |  |  |  |  |  |  |  |  |  |  |  |

| ΄.          | return 00 in W                            |  |  |  |  |  |  |  |  |  |  |  |

| '           |                                           |  |  |  |  |  |  |  |  |  |  |  |

| i           | - · · · · · · · · · · · · · · · · · · ·   |  |  |  |  |  |  |  |  |  |  |  |

| ;           | Read_Current: Read EEPROM at address      |  |  |  |  |  |  |  |  |  |  |  |

| C١          | urrently held by EE device.               |  |  |  |  |  |  |  |  |  |  |  |

| ;           | Inputs: NONE                              |  |  |  |  |  |  |  |  |  |  |  |

| ;           | Outputs: EEPROM Data EEDATA               |  |  |  |  |  |  |  |  |  |  |  |

| ;           | Return 01 in W if OK, else                |  |  |  |  |  |  |  |  |  |  |  |

| ;           | return 00 in W                            |  |  |  |  |  |  |  |  |  |  |  |

| ;           |                                           |  |  |  |  |  |  |  |  |  |  |  |

| ;           | Read Random: Read EEPROM byte at supplied |  |  |  |  |  |  |  |  |  |  |  |

| ;           | address                                   |  |  |  |  |  |  |  |  |  |  |  |

| ;           | Inputs: EEPROM Address EEADDR             |  |  |  |  |  |  |  |  |  |  |  |

| ;           | Outputs: EEPROM Data EEDATA               |  |  |  |  |  |  |  |  |  |  |  |

| ;           | Return 01 in W if OK,                     |  |  |  |  |  |  |  |  |  |  |  |

|             | else return 00 in W                       |  |  |  |  |  |  |  |  |  |  |  |

| '           |                                           |  |  |  |  |  |  |  |  |  |  |  |

The code for these functions is available on our web site (www.microchip.com). The code will be accessed by either including the source code FL62XINC.ASM or by linking FLASH62X.ASM. FLASH62.IMC provides external definition to the calling program.

#### 6.0.1 SERIAL DATA

SDA is a bi-directional pin used to transfer addresses and data into and data out of the memory.

For normal data transfer, SDA is allowed to change only during SCL low. Changes during SCL high are reserved for indicating the START and STOP conditions.

#### 6.0.2 SERIAL CLOCK

This SCL input is used to synchronize the data transfer to and from the memory.

#### 6.0.3 EEINTF REGISTER

The EEINTF register (SFR 90h) controls the access to the EEPROM. Register 6-1 details the function of each bit. User code must generate the clock and data signals.

### REGISTER 6-1: EEINTF REGISTER (ADDRESS 90h)

| U-0              | U-0                                                                                                                                                                     | U-0         | U-0         | U-0          | R/W-1        | R/W-1       | R/W-1        |                                                                                       |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|--------------|--------------|-------------|--------------|---------------------------------------------------------------------------------------|--|--|

|                  | _                                                                                                                                                                       | _           | _           | _            | EESCL        | EESDA       | EEVDD        | R = Readable bit                                                                      |  |  |

| bit7<br>bit 7-3: | Unimpler                                                                                                                                                                | nented: F   | lead as '0' |              |              |             | bit0         | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |

| bit 2:           | <b>EESCL</b> : 0<br>1 = Clock<br>0 = Clock                                                                                                                              | high        | o the EEF   | PROM         |              |             |              |                                                                                       |  |  |

| bit 1:           | <b>EESDA</b> : [<br>1 = Data  <br>0 = Data                                                                                                                              | ine is high |             |              | ne is pulled | high by a p | oull-up resi | stor)                                                                                 |  |  |

| bit 0:           | <b>EEVDD</b> : VDD control bit for EEPROM<br>1 = VDD is turned on to EEPROM<br>0 = VDD is turned off to EEPROM (all pins are tri-stated and the EEPROM is powered down) |             |             |              |              |             |              |                                                                                       |  |  |

| Note:            | EESDA, E                                                                                                                                                                | ESCL an     | d EEVDD     | will read '( | 0' if EEVDD  | is turned c | off.         |                                                                                       |  |  |

## 6.5 <u>Read Operation</u>

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the EEPROM address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

## 6.6 Current Address Read

The EEPROM contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the EEPROM address with R/W bit set to one, the EEPROM issues an acknowledge and transmits the eight bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-7).

### 6.7 Random Read

Random read operations allow the processor to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the EEPROM as part of a write operation. After the word address is sent, the processor generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the processor issues the control byte again, but with the R/W bit set to a one. The EEPROM will then issue an acknowledge and transmits the eight bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-8).

## 6.8 Sequential Read

Sequential reads are initiated in the same way as a random read except that after the EEPROM transmits the first data byte, the processor issues an acknowledge as opposed to a stop condition in a random read. This directs the EEPROM to transmit the next sequentially addressed 8-bit word (Figure 6-9).

To provide sequential reads, the EEPROM contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation.

### 6.9 Noise Protection

The EEPROM employs a Vcc threshold detector circuit, which disables the internal erase/write logic if the Vcc is below 1.5 volts at nominal conditions.

The SCL and SDA inputs have Schmitt trigger and filter circuits, which suppress noise spikes to assure proper device operation even on a noisy bus.

#### 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs, otherwise the maximum delay of the comparators should be used (Table 13-1).

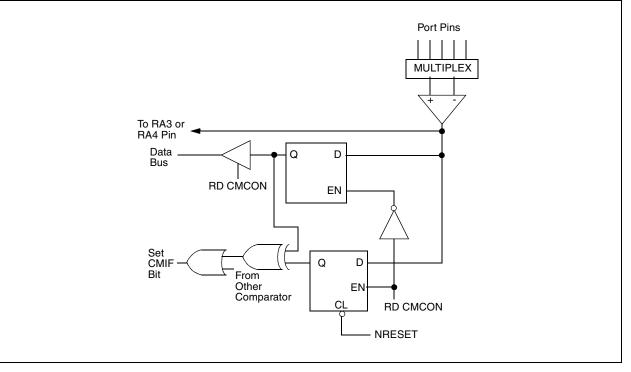

#### 8.5 <u>Comparator Outputs</u>

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 8-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

### FIGURE 8-3: COMPARATOR OUTPUT BLOCK DIAGRAM

### 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

**REGISTER 10-1: CONFIGURATION WORD**

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1 CP    | 0 <sup>(2)</sup> CP1 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <sub>CP0</sub> (2) | CP1      | CP0 <sup>(2)</sup> | _       | BODEN <sup>(1)</sup> | CP1    | CP0 <sup>(2)</sup> | PWRTE(    | 1) WDTE | F0SC1       | F0SC0       | CONFIG       | Addres  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--------------------|---------|----------------------|--------|--------------------|-----------|---------|-------------|-------------|--------------|---------|

| bit13     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |          |                    |         |                      |        |                    |           |         |             | bit0        | REGISTER     | 8: 2007 |

| bit 13-8, | CP1:CP0 Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | irs: Cod           | le prote | ection bit         | pairs   | (2)                  |        |                    |           |         |             |             |              |         |

| 5-4:      | · · · · •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          | •                  |         | n off                |        |                    |           |         |             |             |              |         |

|           | 10 = 0400h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = 0200h-<br>00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | Code prote                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         | morv                 |        |                    |           |         |             |             |              |         |

|           | 11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 10 =Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = 0200h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | Code prote<br>11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |          |                    |         | -                    |        |                    |           |         |             |             |              |         |

|           | 11 = Progra<br>10 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          | •                  |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          | •                  |         |                      |        |                    |           |         |             |             |              |         |

|           | 00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -01FFh             | code     | ,<br>protecte      | d       |                      |        |                    |           |         |             |             |              |         |

| bit 7:    | Unimpleme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ented: F           | Read a   | s '1'              |         |                      |        |                    |           |         |             |             |              |         |

| bit 6:    | BODEN: Bro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | own-ou             | t Rese   | t Enable           | e bit ( | 1)                   |        |                    |           |         |             |             |              |         |

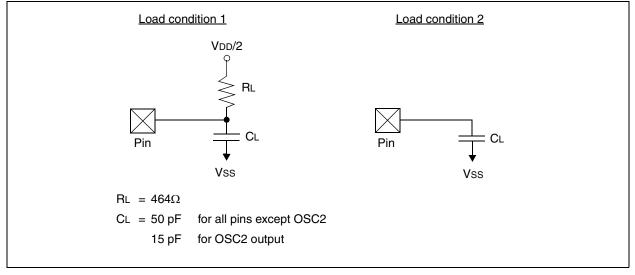

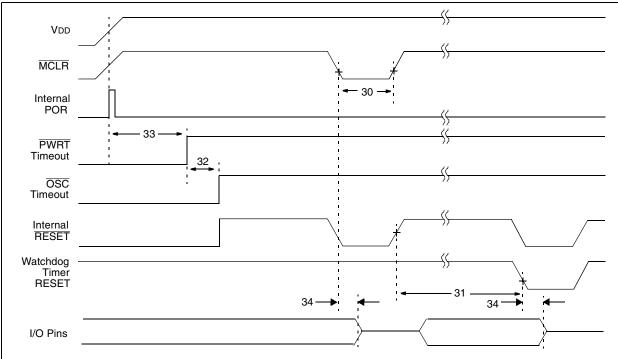

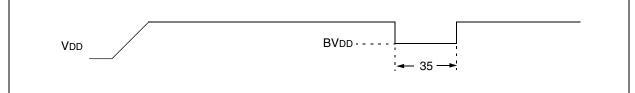

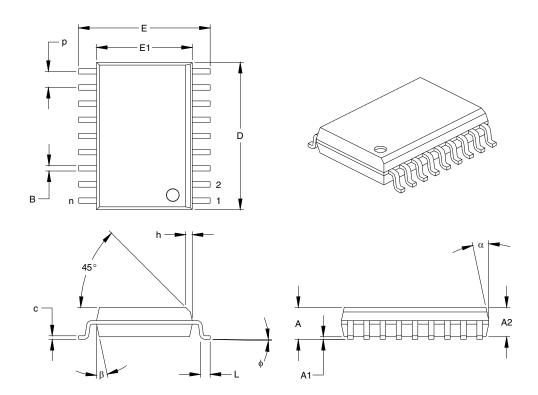

|           | 1 = BOD en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |