Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014.10                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

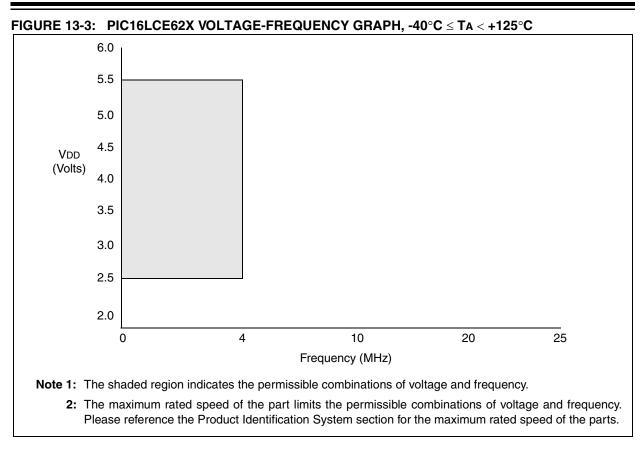

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 896B (512 x 14)                                                             |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 20-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce623-04-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

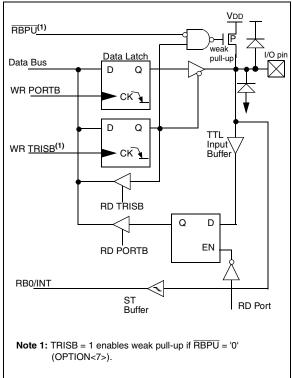

#### 3.1 Clocking Scheme/Instruction Cycle

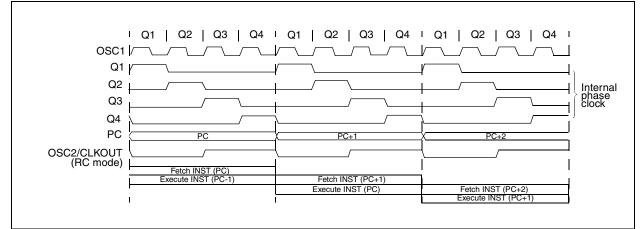

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

#### 3.2 Instruction Flow/Pipelining

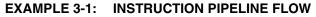

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

### 4.0 MEMORY ORGANIZATION

#### 4.1 <u>Program Memory Organization</u>

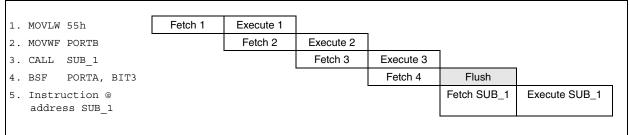

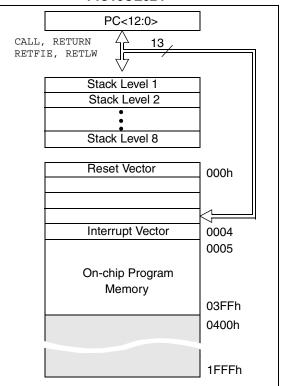

The PIC16CE62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16CE623, 1K x 14 (0000h - 03FFh) for the PIC16CE624 and 2K x 14 (0000h - 07FFh) for the PIC16CE625 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16CE623) or 1K x 14 space (PIC16CE624) or 2K x 14 space (PIC16CE625). The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE623

#### FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE624

#### FIGURE 4-3: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE625

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

#### REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

| R/W-0       | R/W-0 | R/W-0        | R/W-0                                     | R/W-0        | R/W-0       | R/W-0       | R/W-x        |                                                                                                                                       |

|-------------|-------|--------------|-------------------------------------------|--------------|-------------|-------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| GIE<br>bit7 | PEIE  | TOIE         | INTE                                      | RBIE         | TOIF        | INTF        | RBIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |

| bit 7:      |       |              | masked in                                 |              |             |             |              |                                                                                                                                       |

| bit 6:      |       | es all un-r  | terrupt En<br>masked pe<br>ipheral int    | eripheral ir | nterrupts   |             |              |                                                                                                                                       |

| bit 5:      |       | es the TN    | ow Interrup<br>IR0 interru<br>IR0 interru | ıpt          | bit         |             |              |                                                                                                                                       |

| bit 4:      |       | es the RB    | ernal Inter<br>0/INT exte<br>30/INT ext   | ernal interi | rupt        |             |              |                                                                                                                                       |

| bit 3:      |       | es the RB    | nge Interr<br>port char<br>3 port cha     | ige interru  | pt          |             |              |                                                                                                                                       |

| bit 2:      |       | ) register l |                                           | wed (mus     | t be cleare | d in softwa | ure)         |                                                                                                                                       |

| bit 1:      |       | RB0/INT e    |                                           | errupt occ   | urred (must | t be cleare | d in softwar | re)                                                                                                                                   |

| bit 0:      |       | at least c   | one of the                                | RB<7:4> p    |             | •           | ust be clea  | red in software)                                                                                                                      |

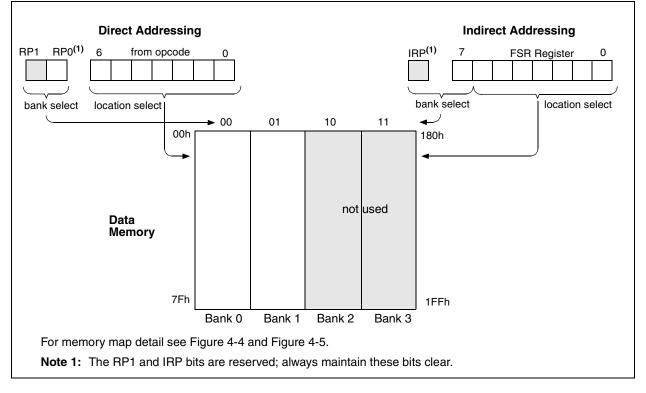

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16CE62X. A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

| EXAMPL    | E 4-1: | INDIRE | ECT ADDRESSING       |

|-----------|--------|--------|----------------------|

|           | movlw  | 0x20   | ;initialize pointer  |

|           | movwf  | FSR    | ;to RAM              |

| NEXT      | clrf   | INDF   | clear INDF register; |

|           | incf   | FSR    | ;inc pointer         |

|           | btfss  | FSR,4  | ;all done?           |

|           | goto   | NEXT   | ;no clear next       |

|           |        |        | ;yes continue        |

| CONTINUE: |        |        |                      |

#### FIGURE 4-7: DIRECT/INDIRECT ADDRESSING PIC16CE62X

## 5.0 I/O PORTS

The PIC16CE62X parts have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

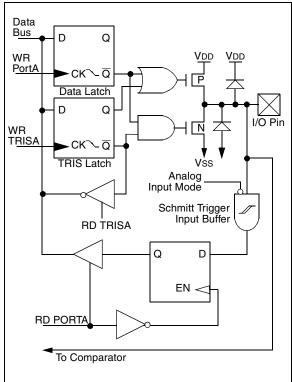

#### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the TOCKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a hi- impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (Comparator Control Register) register and the VRCON (Voltage Reference Control Register) register. When selected as a comparator input, these pins will read as '0's.

#### FIGURE 5-1: BLOCK DIAGRAM OF RA<1:0> PINS

| Note: | On reset, the TRISA register is set to all  |

|-------|---------------------------------------------|

|       | inputs. The digital inputs are disabled and |

|       | the comparator inputs are forced to ground  |

|       | to reduce excess current consumption.       |

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

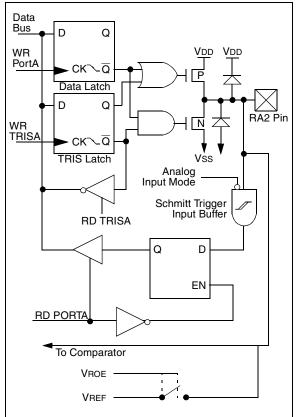

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### **EXAMPLE 5-1: INITIALIZING PORTA**

| CLRF  | PORTA   |     | ;Initialize PORTA by setting ;output data latches |

|-------|---------|-----|---------------------------------------------------|

| MOVLW | 0X07    |     | ;Turn comparators off and                         |

| MOVWF | CMCON   |     | ;enable pins for I/O                              |

|       |         |     | ;functions                                        |

| BSF   | STATUS, | RP0 | ;Select Bank1                                     |

| MOVLW | 0x1F    |     | ;Value used to initialize                         |

|       |         |     | ;data direction                                   |

| MOVWF | TRISA   |     | ;Set RA<4:0> as inputs                            |

|       |         |     | ;TRISA<7:5> are always                            |

|       |         |     | ;read as '0'.                                     |

#### FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

<sup>© 1998-2013</sup> Microchip Technology Inc.

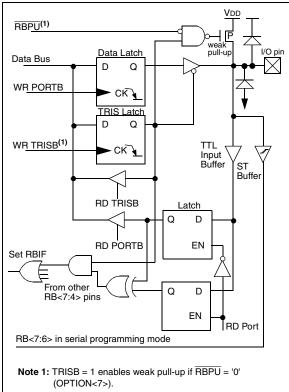

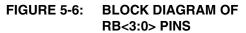

#### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a high impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{RBPU}$  (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins of RB<7:4> are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes".)

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

#### 6.1 Bus Characteristics

In this section, the term "processor" refers to the portion of the PIC16CE62X that interfaces to the EEPROM through software manipulating the EEINTF register. The following **bus protocol** is to be used with the EEPROM data memory.

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted by the EEPROM as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 6-1).

#### 6.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

#### 6.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### 6.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### 6.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the processor and is theoretically unlimited, although only the last sixteen will be stored when doing a write operation. When an overwrite does occur, it will replace data in a first-in, first-out fashion.

#### 6.1.5 ACKNOWLEDGE

The EEPROM will generate an acknowledge after the reception of each byte. The processor must generate an extra clock pulse which is associated with this acknowledge bit.

| Note: | Acknowledge bits are not generated if an   |

|-------|--------------------------------------------|

|       | internal programming cycle is in progress. |

When the EEPROM acknowledges, it pulls down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. The processor must signal an end of data to the EEPROM by not generating an acknowledge bit on the last byte that has been clocked out of the EEPROM. In this case, the EEPROM must leave the data line HIGH to enable the processor to generate the STOP condition (Figure 6-2).

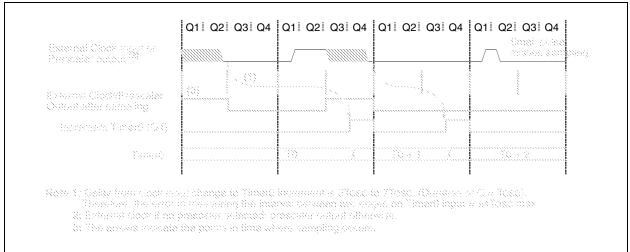

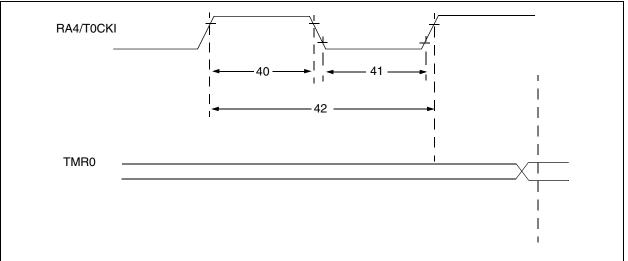

#### 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

#### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

### 10.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16CE62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-Up Timer (OST) Brown-out Reset (BOD)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

The PIC16CE62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, and is designed to keep the part in reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

| GOTO                              | Unconditional Branch                                                                                                                                                                               | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [ <i>label</i> ] GOTO k                                                                                                                                                                            | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:                         | $0 \le k \le 2047$                                                                                                                                                                                 | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                              |

| Operation:                        | $k \rightarrow PC < 10:0 >$                                                                                                                                                                        |                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                      |

|                                   | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected:                  | None                                                                                                                                                                                               | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |

| Encoding:                         | 10 1kkk kkkk kkkk                                                                                                                                                                                  | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                              |

| Description:<br>Words:<br>Cycles: | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.<br>1 | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. |

| Example                           | GOTO THERE                                                                                                                                                                                         | Words:           | 1                                                                                                                                                                                                                                                                                                                              |

|                                   | After Instruction<br>PC = Address THERE                                                                                                                                                            | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |

|                                   | FC = Addless There                                                                                                                                                                                 | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                    |                  | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                    |                  | •                                                                                                                                                                                                                                                                                                                              |

$\begin{array}{rcl} Before \ Instruction \\ PC & = & address \ HERE \\ After \ Instruction \\ CNT & = & CNT + 1 \\ if \ CNT = & 0, \\ PC & = & address \ CONTINUE \\ if \ CNT \neq & 0, \\ PC & = & address \ HERE \ +1 \\ \end{array}$

| INCF             | Increment f                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                         |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                   |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                   |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |

| Words:           | 1                                                                                                                                                                   |

| Cycles:          | 1                                                                                                                                                                   |

| Example          | INCF CNT, 1                                                                                                                                                         |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                               |

| IORLW            | Inclusive OR Literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                           |

| Status Affected: | Z                                                                                                                      |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                      |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:           | 1                                                                                                                      |

| Cycles:          | 1                                                                                                                      |

| Example          | IORLW 0x35                                                                                                             |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                               |

| RETURN             | Return from Subroutine                                                                                          | RRF              | Rotate Right f through Carry                                                                                                                                                   |

|--------------------|-----------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:            | [label] RETURN                                                                                                  | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                       |

| Operands:          | None                                                                                                            | Operands:        | $0 \le f \le 127$                                                                                                                                                              |

| Operation:         | $TOS \rightarrow PC$                                                                                            |                  | $d \in [0,1]$                                                                                                                                                                  |

| Status Affected:   | None                                                                                                            | Operation:       | See description below                                                                                                                                                          |

| Encoding:          | 00 0000 0000 1000                                                                                               | Status Affected: | С                                                                                                                                                                              |

| Description:       | Return from subroutine. The stack is                                                                            | Encoding:        | 00 1100 dfff ffff                                                                                                                                                              |

|                    | POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a two cycle instruction. | Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>Flag. If 'd' is 0, the result is placed in<br>the W register. If 'd' is 1, the result is |

| Words:             | 1                                                                                                               |                  | placed back in register 'f'.                                                                                                                                                   |

| Cycles:<br>Example | 2<br>RETURN                                                                                                     |                  | C Register f                                                                                                                                                                   |

|                    | After Interrupt                                                                                                 | Words:           | 1                                                                                                                                                                              |

|                    | PC = TOS                                                                                                        | Cycles:          | 1                                                                                                                                                                              |

|                    |                                                                                                                 | Example          | RRF REG1,0                                                                                                                                                                     |

|                    |                                                                                                                 |                  | Before Instruction REG1 = 1110 0110   C = 0 0   After Instruction REG1 = 1110 0110   W = 0111 0011   C = 0 0                                                                   |

| RLF              | Rotate Left f t                                                   | hrough Carry                                                                                                                |         |  |  |

|------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|--|--|

| Syntax:          | [label] RLF                                                       | f,d                                                                                                                         |         |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$ |                                                                                                                             |         |  |  |

| Operation:       | See description below                                             |                                                                                                                             |         |  |  |

| Status Affected: | С                                                                 |                                                                                                                             |         |  |  |

| Encoding:        | 00 110                                                            | 1 dfff ff                                                                                                                   | ff      |  |  |

| Description:     | one bit to the left<br>Flag. If 'd' is 0, th                      | register 'f' are rota<br>t through the Carry<br>ne result is placed<br>f 'd' is 1, the result<br>egister 'f'.<br>Register f | /<br>in |  |  |

| Words:           | 1                                                                 |                                                                                                                             |         |  |  |

| Cycles:          | 1                                                                 |                                                                                                                             |         |  |  |

|                  |                                                                   |                                                                                                                             |         |  |  |

| Example          | RLF                                                               | REG1,0                                                                                                                      |         |  |  |

# SLEEP

| 02221            |                                                                                                                                                                                                                                                                          |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                                                                                          |

| Operands:        | None                                                                                                                                                                                                                                                                     |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \ \text{prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                                                                                              |

| Status Affected: | TO, PD                                                                                                                                                                                                                                                                   |

| Encoding:        | 00 0000 0110 0011                                                                                                                                                                                                                                                        |

| Description:     | The power-down status bit, $\overline{PD}$ is<br>cleared. Time-out status bit, $\overline{TO}$ is<br>set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped.<br>See Section 10.8 for more details. |

| Words:           | 1                                                                                                                                                                                                                                                                        |

| Cycles:          | 1                                                                                                                                                                                                                                                                        |

| Example:         | SLEEP                                                                                                                                                                                                                                                                    |

MPLIB is a librarian for pre-compiled code to be used with MPLINK. When a routine from a library is called from another source file, only the modules that contains that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications. MPLIB manages the creation and modification of library files.

MPLINK features include:

- MPLINK works with MPASM and MPLAB-C17 and MPLAB-C18.

- MPLINK allows all memory areas to be defined as sections to provide link-time flexibility.

MPLIB features include:

- MPLIB makes linking easier because single libraries can be included instead of many smaller files.

- MPLIB helps keep code maintainable by grouping related modules together.

- MPLIB commands allow libraries to be created and modules to be added, listed, replaced, deleted, or extracted.

#### 12.5 MPLAB-SIM Software Simulator

The MPLAB-SIM Software Simulator allows code development in a PC host environment by simulating the PIC series microcontrollers on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a file or user-defined key press to any of the pins. The execution can be performed in single step, execute until break, or trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C17 and MPLAB-C18 and MPASM. The Software Simulator offers the flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

#### 12.6 <u>MPLAB-ICE High Performance</u> <u>Universal In-Circuit Emulator with</u> <u>MPLAB IDE</u>

The MPLAB-ICE Universal In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers (MCUs). Software control of MPLAB-ICE is provided by the MPLAB Integrated Development Environment (IDE), which allows editing, "make" and download, and source debugging from a single environment.

Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The universal architecture of the MPLAB-ICE allows expansion to support new PIC microcontrollers.

The MPLAB-ICE Emulator System has been designed as a real-time emulation system with advanced features that are generally found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows 3.x/95/98 environment were chosen to best make these features available to you, the end user.

MPLAB-ICE 2000 is a full-featured emulator system with enhanced trace, trigger, and data monitoring features. Both systems use the same processor modules and will operate across the full operating speed range of the PIC MCU.

#### 12.7 PICMASTER/PICMASTER CE

The PICMASTER system from Microchip Technology is a full-featured, professional quality emulator system. This flexible in-circuit emulator provides a high-quality, universal platform for emulating Microchip 8-bit PIC microcontrollers (MCUs). PICMASTER systems are sold worldwide, with a CE compliant model available for European Union (EU) countries.

### 12.8 <u>ICEPIC</u>

ICEPIC is a low-cost in-circuit emulation solution for the Microchip Technology PIC16C5X, PIC16C6X, PIC16C7X, and PIC16CXXX families of 8-bit one-timeprogrammable (OTP) microcontrollers. The modular system can support different subsets of PIC16C5X or PIC16CXXX products through the use of interchangeable personality modules or daughter boards. The emulator is capable of emulating without target application circuitry being present.

#### 12.9 MPLAB-ICD In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB-ICD, is a powerful, low-cost run-time development tool. This tool is based on the flash PIC16F877 and can be used to develop for this and other PIC microcontrollers from the PIC16CXXX family. MPLAB-ICD utilizes the In-Circuit Debugging capability built into the PIC16F87X. This feature, along with Microchip's In-Circuit Serial Programming protocol, offers cost-effective in-circuit flash programming and debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by watching variables, single-stepping and setting break points. Running at full speed enables testing hardware in real-time. The MPLAB-ICD is also a programmer for the flash PIC16F87X family.

#### 12.10 PRO MATE II Universal Programmer

The PRO MATE II Universal Programmer is a full-featured programmer capable of operating in stand-alone mode as well as PC-hosted mode. PRO MATE II is CE compliant.

The PRO MATE II has programmable VDD and VPP supplies which allows it to verify programmed memory at VDD min and VDD max for maximum reliability. It has an LCD display for instructions and error messages, keys to enter commands and a modular detachable socket assembly to support various package types. In

TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                          | PIC120 | PIC14 | PIC160 | 91019 | PIC160 | PIC16F | PIC16          | PICIEC | PIC160 | PIC16F | PIC16C | DTFOIG | 22121919 | PIC18C | 83CX<br>52CX<br>54CX | кхээн | мсвгх | MCP25 |

|----------------------------------------------------------|--------|-------|--------|-------|--------|--------|----------------|--------|--------|--------|--------|--------|----------|--------|----------------------|-------|-------|-------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment | >      | >     | >      | >     | >      | >      | >              | >      | >      | >      | >      | >      | >        | >      |                      |       |       |       |

|                                                          |        |       |        |       |        |        |                |        |        |        |        | >      | >        |        |                      |       |       |       |

| MPLAB <sup>®</sup> C18 Compiler                          |        |       |        |       |        |        |                |        |        |        |        |        |          | >      |                      |       |       |       |

| B MPASM/MPLINK                                           | >      | >     | >      | >     | >      | >      | >              | >      | >      | >      | >      | >      | >        | >      | >                    | >     |       |       |

| 2 MPLAB <sup>®</sup> -ICE                                | >      | >     | >      | >     | >      | **`    | >              | >      | >      | >      | >      | >      | >        | >      |                      |       |       |       |

| PICMASTER/PICMASTER-CE                                   | >      | >     | ~      | >     | >      |        | >              | >      | ~      |        | >      | ~      | ~        |        |                      |       |       |       |

| E ICEPIC™ Low-Cost<br>III In-Circuit Emulator            | `      |       | >      | >     | >      |        | >              | >      | >      |        | ~      |        |          |        |                      |       |       |       |

| MPLAB <sup>®</sup> -ICD In-Circuit<br>Debugger<br>De     |        |       |        | *>    |        |        | *              |        |        | >      |        |        |          |        |                      |       |       |       |

| 20 PICSTART®Plus<br>E Low-Cost Universal Dev. Kit        | ~      | >     | >      | `     | `      | ×**    | ~              | `      | `      | >      | >      | ~      | `        | `      |                      |       |       |       |

| ଅଟେ PRO MATE® I<br>Universal Programmer<br>ଦ             | >      | >     | >      | >     | >      | **/    | >              | >      | >      | >      | >      | ~      | ~        | ~      | >                    | >     |       |       |

| SIMICE                                                   | >      |       | >      |       |        |        |                |        |        |        |        |        |          |        |                      |       |       |       |

| PICDEM-1                                                 |        |       | >      |       | >      |        | ۲ <sup>+</sup> |        | >      |        |        | >      |          |        |                      |       |       |       |

| PICDEM-2                                                 |        |       |        | ∕†    |        |        | <↓<br>↓        |        |        |        |        |        |          | ~      |                      |       |       |       |

| 2 PICDEM-3                                               |        |       |        |       |        |        |                |        |        |        | ~      |        |          |        |                      |       |       |       |

| PICDEM-14A                                               |        | >     |        |       |        |        |                |        |        |        |        |        |          |        |                      |       |       |       |

| PICDEM-17                                                |        |       |        |       |        |        |                |        |        |        |        |        | ~        |        |                      |       |       |       |

| KEELOQ® Evaluation Kit                                   |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      | ~     |       |       |

| KEELOQ Transponder Kit                                   |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      | ~     |       |       |

| microlD™ Programmer's Kit                                |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       | ~     |       |

| 125 kHz microID Developer's Kit                          |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       | >     |       |

| 25 kHz Anticollision microlD<br>Developer's Kit          |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       | >     |       |

| 13.56 MHz Anticollision microID<br>Developer's Kit       |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       | >     |       |

| MCP2510 CAN Developer's Kit                              |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       |       | >     |

ğ Contact Microcrip reciniology inc. for availability <sup>†</sup> Development tool is available on select devices.

#### TABLE 13-1: COMPARATOR SPECIFICATIONS

| Param No. | Characteristics                           | Sym    | Min  | Тур   | Max       | Units | Comments   |

|-----------|-------------------------------------------|--------|------|-------|-----------|-------|------------|

| D300      | Input offset voltage                      | VIOFF  |      | ± 5.0 | ± 10      | mV    |            |

| D301      | Input common mode voltage                 | VICM   | 0    |       | Vdd - 1.5 | V     |            |

| D302      | CMRR                                      | CMRR   | +55* |       |           | db    |            |

| 300       | Response Time <sup>(1)</sup>              | TRESP  |      | 150*  | 400*      | ns    | PIC16CE62X |

| 301       | Comparator Mode Change to<br>Output Valid | Тмс2ov |      |       | 10*       | μS    |            |

Operating Conditions: VDD range as described in Table 12-1, -40°C<TA<+125°C. .

\* These parameters are characterized but not tested.

Note 1: Response time measured with one comparator input at (VDD - 1.5)/2 while the other input transitions from Vss to VDD.

#### TABLE 13-2: VOLTAGE REFERENCE SPECIFICATIONS

Operating Conditions: VDD range as described in Table 12-1, -40°C<TA<+125°C.

| Param<br>No. | Characteristics              | Sym  | Min    | Тур | Мах                          | Units      | Comments                                |

|--------------|------------------------------|------|--------|-----|------------------------------|------------|-----------------------------------------|

| D310         | Resolution                   | VRES | VDD/24 |     | Vdd/32                       | LSB        |                                         |

| D311         | Absolute Accuracy            | Vraa |        |     | <u>+</u> 1/4<br><u>+</u> 1/2 | LSB<br>LSB | Low Range (VRR=1)<br>High Range (VRR=0) |

| D312         | Unit Resistor Value (R)      | VRur |        | 2K* |                              | Ω          | Figure 9-1                              |

| 310          | Settling Time <sup>(1)</sup> | TSET |        |     | 10*                          | μS         |                                         |

\* These parameters are characterized but not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from 0000 to 1111.

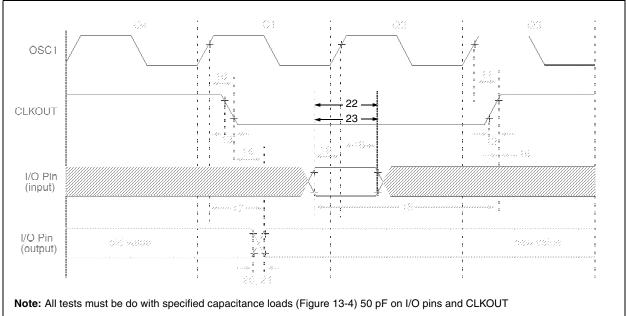

#### FIGURE 13-6: CLKOUT AND I/O TIMING

| Parameter # | Sym      | Characteristic                                                        | Min          | Тур† | Мах | Units |

|-------------|----------|-----------------------------------------------------------------------|--------------|------|-----|-------|

| 10*         | TosH2ckL | OSC1↑ to CLKOUT↓ <sup>(1)</sup>                                       | —            | 75   | 200 | ns    |

| 11*         | TosH2ckH | OSC1 <sup>↑</sup> to CLKOUT <sup>↑</sup> <sup>(1)</sup>               | _            | 75   | 200 | ns    |

| 12*         | TckR     | CLKOUT rise time <sup>(1)</sup>                                       | _            | 35   | 100 | ns    |

| 13*         | TckF     | CLKOUT fall time <sup>(1)</sup>                                       | _            | 35   | 100 | ns    |

| 14*         | TckL2ioV | CLKOUT ↓ to Port out valid <sup>(1)</sup>                             | _            | —    | 20  | ns    |

| 15*         | TioV2ckH | Port in valid before CLKOUT $\uparrow$ <sup>(1)</sup>                 | Tosc +200 ns | —    |     | ns    |

| 16*         | TckH2iol | Port in hold after CLKOUT ↑ <sup>(1)</sup>                            | 0            | —    |     | ns    |

| 17*         | TosH2ioV | OSC1↑ (Q1 cycle) to Port out valid                                    | —            | 50   | 150 | ns    |

| 18*         | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | 100          | —    | _   | ns    |

| 19*         | TioV2osH | Port input valid to OSC1 <sup>↑</sup> (I/O in setup time)             | 0            | —    | _   | ns    |

| 20*         | TioR     | Port output rise time                                                 | —            | 10   | 40  | ns    |

| 21*         | TioF     | Port output fall time                                                 | —            | 10   | 40  | ns    |

| 22*         | Tinp     | RB0/INT pin high or low time                                          | 25           | —    | _   | ns    |

| 23          | Trbp     | RB<7:4> change interrupt high or low time                             | Тсү          | —    | _   | ns    |

|  | TABLE 13-4: | <b>CLKOUT AND I/O TIMING REQUIREMENTS</b> |

|--|-------------|-------------------------------------------|

|--|-------------|-------------------------------------------|

\* These parameters are characterized but not tested

+ Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Measurements are taken in RC Mode where CLKOUT output is 4 x Tosc.

#### FIGURE 13-9: TIMER0 CLOCK TIMING

#### **TABLE 13-6:** TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic         |                | Min                    | Тур† | Max | Units | Conditions                            |

|------------------|------|------------------------|----------------|------------------------|------|-----|-------|---------------------------------------|

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5 TCY + 20*          | _    | _   | ns    |                                       |

|                  |      |                        | With Prescaler | 10*                    | _    | —   | ns    |                                       |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5 TCY + 20*          | _    | _   | ns    |                                       |

|                  |      |                        | With Prescaler | 10*                    | _    | _   | ns    |                                       |

| 42               | Tt0P | T0CKI Period           |                | <u>Tcy + 40</u> *<br>N |      | _   | ns    | N = prescale value<br>(1, 2, 4,, 256) |

t

These parameters are characterized but not tested. Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: