Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 4MHz                                                                          |

| Connectivity               | -                                                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                              |

| Number of I/O              | 13                                                                            |

| Program Memory Size        | 896B (512 x 14)                                                               |

| Program Memory Type        | OTP                                                                           |

| EEPROM Size                | 128 x 8                                                                       |

| RAM Size                   | 96 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | -                                                                             |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 18-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce623t-04e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16CE62X

NOTES:

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC16CE62X family can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC16CE62X uses a Harvard architecture in which program and data are accessed from separate memories using separate buses. This improves bandwidth over traditional von Neumann architecture where program and data are fetched from the same memory. Separating program and data memory further allows instructions to be sized differently than 8-bit wide data word. Instruction opcodes are 14-bits wide making it possible to have all single word instructions. A 14-bit wide program memory access bus fetches a 14-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (35) execute in a single-cycle (200 ns @ 20 MHz) except for program branches.

The table below lists program memory (EPROM), data memory (RAM) and non-volatile memory (EEPROM) for each PIC16CE62X device.

| Device     | Program<br>Memory | RAM<br>Data<br>Memory | EEPROM<br>Data<br>Memory |

|------------|-------------------|-----------------------|--------------------------|

| PIC16CE623 | 512x14            | 96x8                  | 128x8                    |

| PIC16CE624 | 1Kx14             | 96x8                  | 128x8                    |

| PIC16CE625 | 2Kx14             | 128x8                 | 128x8                    |

The PIC16CE62X can directly or indirectly address its register files or data memory. All special function registers including the program counter are mapped in the data memory. The PIC16CE62X family has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC16CE62X simple yet efficient. In addition, the learning curve is reduced significantly.

The PIC16CE62X devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8 bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, typically one operand is the working register (W register). The other operand is a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a Borrow and Digit Borrow out bit respectively, bit in subtraction. See the SUBLWand SUBWFinstructions for examples.

A simplified block diagram is shown in Figure 3-1, with a description of the device pins in Table 3-1.

| TABLE 3-1: | PIC16CE62X PINOUT DESCRIPTION |

|------------|-------------------------------|

|            |                               |

| Name         | DIP/<br>SOIC<br>Pin # | SSOP<br>Pin #     | I/O/P<br>Type | Buffer<br>Type          | Description                                                                                                                                                                                                       |

|--------------|-----------------------|-------------------|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                    | 18                | I             | ST/CMOS                 | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT  | 15                    | 17                | 0             | _                       | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/VPP     | 4                     | 4                 | I/P           | ST                      | Master clear (reset) input/programming voltage input.<br>This pin is an active low reset to the device.                                                                                                           |

|              |                       |                   |               |                         | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0      | 17                    | 19                | I/O           | ST                      | Analog comparator input                                                                                                                                                                                           |

| RA1/AN1      | 18                    | 20                | I/O           | ST                      | Analog comparator input                                                                                                                                                                                           |

| RA2/AN2/VREF | 1                     | 1                 | I/O           | ST                      | Analog comparator input or VREF output                                                                                                                                                                            |

| RA3/AN3      | 2                     | 2                 | I/O           | ST                      | Analog comparator input /output                                                                                                                                                                                   |

| RA4/T0CKI    | 3                     | 3                 | I/O           | ST                      | Can be selected to be the clock input to the Timer0 timer/counter or a comparator output. Output is open drain type.                                                                                              |

|              |                       |                   |               |                         | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                               |

| RB0/INT      | 6                     | 7                 | I/O           | TTL/ST <sup>(1)</sup>   | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                                        |

| RB1          | 7                     | 8                 | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB2          | 8                     | 9                 | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB3          | 9                     | 10                | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB4          | 10                    | 11                | I/O           | TTL                     | Interrupt on change pin.                                                                                                                                                                                          |

| RB5          | 11                    | 12                | I/O           | TTL                     | Interrupt on change pin.                                                                                                                                                                                          |

| RB6          | 12                    | 13                | I/O           | TTL/ST <sup>(2)</sup>   | Interrupt on change pin. Serial programming clock.                                                                                                                                                                |

| RB7          | 13                    | 14                | I/O           | TTL/ST <sup>(2)</sup>   | Interrupt on change pin. Serial programming data.                                                                                                                                                                 |

| Vss          | 5                     | 5,6               | Р             | _                       | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| Vdd          | 14                    | 15,16             | Р             | —                       | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Legend:      |                       | utput<br>Not used | 1:            | O = input/or<br>= Input | utput P = power<br>ST = Schmitt Trigger input                                                                                                                                                                     |

TTL = TTL input

Note 1: This buffer is a Schmitt Trigger input when configured as the external interrupt. Note 2: This buffer is a Schmitt Trigger input when used in serial programming mode.

#### 4.2.2.1 STATUS REGISTER

The STATUS register, shown in Register 4-1, contains the arithmetic status of the ALU, the RESET status and the bank select bits for data memory.

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper-three bits and set the Z bit. This leaves the status register as 000uu1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPFand MOVWFinstructions are used to alter the STATUS register, because these instructions do not affect any status bit. For other instructions, not affecting any status bits, see the "Instruction Set Summary".

| Note 1: | The IRP and RP1 bits (STATUS<7:6>) are not used by the PIC16CE62X and should be programmed as '0'. Use of these bits as general purpose R/W bits is NOT recommended, since this may affect upward compatibility with future products. |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note 2: | The <u>C</u> and <u>DC</u> bits operate as a Borrow<br>and <u>Digit</u> Borrow out bit, respectively, in<br>subtraction. See the SUBLWand SUBWF<br>instructions for examples                                                          |

| Reserved | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0       | R-1       | R-1        | R/W-x     | R/W-x     | R/W-x          |             |                                                                                                                                        |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|------------|-----------|-----------|----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------|

| IRP      | RP1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | RP0         | TO        | PD         | Z         | DC        | С              |             | Readable bit                                                                                                                           |

| bit7     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |           |            |           |           | bitO           | U =<br>-n = | <ul> <li>Writable bit</li> <li>Unimplemented bit,<br/>read as '0'</li> <li>Value at POR reset</li> <li>Unknown at POR reset</li> </ul> |

| bit 7:   | IRP: The I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RP bit is r | eserved o | n the PIC1 | 6CE62X, a | ways main | ntain this bit | clear.      |                                                                                                                                        |

| bit 6:5  | RP<1:O>: Register Bank Select bits (used for direct addressing)<br>11 = Bank 3 (180h - 1FFh)<br>10 = Bank 2 (100h - 17Fh)<br>01 = Bank 1 (80h - FFh)<br>00 = Bank 0 (00h - 7Fh)<br>Each bank is 128 bytes. The RP1 bit is reserved, always maintain this bit clear.                                                                                                                                                                                                                                                             |             |           |            |           |           |                |             |                                                                                                                                        |

| bit 4:   | TO: Time-out bit<br>1 = After power-up, CLRWDTnstruction, or SLEEPinstruction<br>0 = A WDT time-out occurred                                                                                                                                                                                                                                                                                                                                                                                                                    |             |           |            |           |           |                |             |                                                                                                                                        |

| bit 3:   | <ul> <li>PD: Power-down bit</li> <li>1 = After power-up or by the CLRWDTnstruction</li> <li>0 = By execution of the SLEEPinstruction</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                 |             |           |            |           |           |                |             |                                                                                                                                        |

| bit 2:   | <ul> <li>Z: Zero bit</li> <li>1 = The result of an arithmetic or logic operation is zero</li> <li>0 = The result of an arithmetic or logic operation is not zero</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |             |           |            |           |           |                |             |                                                                                                                                        |

| bit 1:   | DC: Digit carry/ $\overline{borrow}$ bit (ADDW,FADDLW,SUBLW,SUBWFFstructions) (for $\overline{borrow}$ the polarity is reversed)<br>1 = A carry-out from the 4th low order bit of the result occurred                                                                                                                                                                                                                                                                                                                           |             |           |            |           |           |                |             |                                                                                                                                        |

| bit 0:   | 0 = No carry-out from the 4th low order bit of the result<br>C: Carry/borrow bit (ADDW,FADDLW,SUBLW,SUBWFnstructions)<br>1 = A carry-out from the most significant bit of the result occurred<br>0 = No carry-out from the most significant bit of the result occurred<br>Note: For borrow the polarity is reversed. A subtraction is executed by adding the two's complement of the<br>second operand. For rotate (RRF, RLF) instructions, this bit is loaded with either the high or low order bit of<br>the source register. |             |           |            |           |           |                |             |                                                                                                                                        |

#### REGISTER 4-1: STATUS REGISTER (ADDRESS 03H OR 83H)

### 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

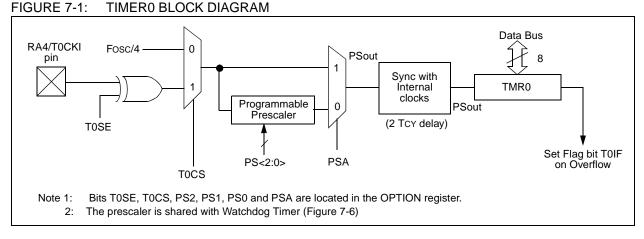

Figure 7-1 is a simplified block diagram of the Timer0 module.

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 <u>Timer0 Interrupt</u>

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

#### FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

| PC<br>(Program<br>Counter) | ( PC-1 |         | PC+1                   | Q1 Q2 Q3 Q4            | PC+3                   | ( PC+4                 | PC+5                       | PC+6                     |

|----------------------------|--------|---------|------------------------|------------------------|------------------------|------------------------|----------------------------|--------------------------|

| Instruction<br>Fetch       |        | î       | 1                      | i                      |                        | 1                      | MOVF TMR0,W                |                          |

| TMR0                       | то)(   | T0+1 )( | T0+2                   | NT                     | p                      |                        | NT0+1 /                    | NT0+2 X                  |

| Instruction<br>Executed    |        |         | <b>≜</b>               | <b>≜</b>               | <b>↑</b>               | <b>≜</b>               | <b>↑</b>                   | <b>↑</b>                 |

| • • • • • •                |        |         | Write TMR0<br>executed | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 | Read TMR0<br>reads NT0 + 1 | Read TMR0<br>reads NT0 - |

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

#### EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 o WDT)

|         | · · ·       | ,                        |

|---------|-------------|--------------------------|

| 1.BCF   | STATUS, RP0 | ;Skip if already in      |

|         |             | ; Bank 0                 |

| 2.CLRWD | Т           | ;Clear WDT               |

| 3.CLRF  | TMR0        | ;Clear TMR0 & Prescaler  |

| 4.BSF   | STATUS, RP0 | ;Bank 1                  |

| 5.MOVLW | '00101111'b | ;These 3 lines (5, 6, 7) |

| 6.MOVWF | OPTION      | ; are required only if   |

|         |             | ; desired PS<2:0> are    |

| 7.CLRWD | Т           | ; 000 or 001             |

| 8.MOVLW | '00101xxx'b | ;Set Postscaler to       |

| 9.MOVWF | OPTION      | ; desired WDT rate       |

| 10.BCF  | STATUS, RP0 | ;Return to Bank 0        |

|         |             |                          |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

#### EXAMPLE 7-2: CHANGING PRESCALER (WDT o TIMER0)

| CLRWDT |                 | ;Clear WDT and      |

|--------|-----------------|---------------------|

|        |                 | ;prescaler          |

| BSF    | STATUS, RP0     |                     |

| MOVLW  | b'xxxx0xxx' ;Se | elect TMR0, new     |

|        |                 | ;prescale value and |

|        |                 | clock source;       |

| MOVWF  | OPTION_REG      |                     |

| BCF    | STATUS, RP0     |                     |

#### TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name   | Bit 7    | Bit 6                                      | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 E | Bit O    | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|--------|----------|--------------------------------------------|-------|--------|--------|--------|---------|----------|------------------|---------------------------------|

| 01h     | TMR0   | Timer0 ı | Fimer0 module register xxxx xxxx uµuu uuuu |       |        |        |        |         | uuu uuuu |                  |                                 |

| 0Bh/8Bh | INTCON | GIE      | PEIE                                       | T0IE  | INTE   | RBIE   | T0IF   | INTF    | RBIF     | 0000 000x (      | 000 000u                        |

| 81h     | OPTION | RBPU     | INTEDG                                     | TOCS  | T0SE   | PSA    | PS2    | PS1     | PS0      | 1111 1111        | 1111 1111                       |

| 85h     | TRISA  | —        |                                            | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0   | 1 1111           | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged.

Note: Shaded bits are not used by TMR0 module.

The code example in Example 8-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 8-1: INITIALIZING COMPARATOR MODULE

| FLAG RE | G EQU       | 0X20                            |

|---------|-------------|---------------------------------|

| CLRF    | FLAG_REG    | ;Init flag register             |

| CLRF    | PORTA       | ;Init PORTA                     |

| MOVF    | CMCON,W     | ;Move comparator contents to W  |

| ANDLW   | 0xC0        | ;Mask comparator bits           |

| IORWF   | FLAG_REG,F  | ;Store bits in flag register    |

| MOVLW   | 0x03        | ;Init comparator mode           |

| MOVWF   | CMCON       | ;CM<2:0> = 011                  |

| BSF     | STATUS, RP0 | ;Select Bank1                   |

| MOVLW   | 0x07        | ;Initialize data direction      |

| MOVWF   | TRISA       | ;Set RA<2:0> as inputs          |

|         |             | ;RA<4:3> as outputs             |

|         |             | ;TRISA<7:5> always read '0'     |

| BCF     | STATUS, RP0 | ;Select Bank 0                  |

| CALL    | DELAY 10    | ;10 B delay                     |

| MOVF    | CMCON,F     | ;ReadCMCON end change condition |

| BCF     | PIR1,CMIF   | ;Clear pending interrupts       |

| BSF     | STATUS, RP0 | ;Select Bank 1                  |

| BSF     | PIE1,CMIE   | ;Enable comparator interrupts   |

| BCF     | STATUS, RP0 | ;Select Bank 0                  |

| BSF     | INTCON,PEIE | ;Enable peripheral interrupts   |

| BSF     | INTCON,GIE  | ;Global interrupt enable        |

|         |             |                                 |

#### 8.2 <u>Comparator Operation</u>

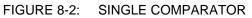

A single comparator is shown in Figure 8-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN–, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN–, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 8-2 represent the uncertainty due to input offsets and response time.

#### 8.3 <u>Comparator Reference</u>

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal that is present at VIN– is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 8-2).

#### 8.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 8.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 8-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

PIC16CE62X

#### 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs, otherwise the maximum delay of the comparators should be used (Table 13-1).

#### 8.5 Comparator Outputs

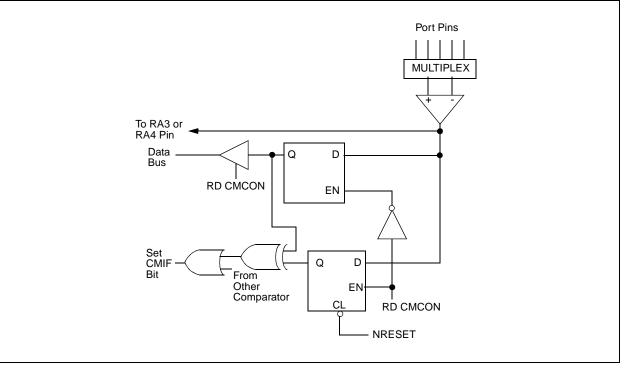

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 8-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 8-3: COMPARATOR OUTPUT BLOCK DIAGRAM

#### EXAMPLE 9-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02       | ; 4 Inputs Muxed |

|-------|------------|------------------|

| MOVWF | CMCON      | ; to 2 comps.    |

| BSF   | STATUS,RP0 | ; go to Bank 1   |

| MOVLW | 0x07       | ; RA3-RA0 are    |

| MOVWF | TRISA      | ; outputs        |

| MOVLW | 0xA6       | ; enable V REF   |

| MOVWF | VRCON      | ; low range      |

|       |            | ; set V R<3:0>=6 |

| BCF   | STATUS,RP0 | ; go to Bank 0   |

| CALL  | DELAY10    | ;10 Bs delay     |

#### 9.2 Voltage Reference Accuracy/Error

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 9-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 13-2.

#### 9.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

#### 9.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

#### 9.5 Connection Considerations

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 9-2 shows an example buffering technique.

# VREF Module Voltage Reference Output Impedance

### FIGURE 9-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

Note 1: R is dependent upon the Voltage Reference Configuration VRCON<3:0> and VRCON<5>.

#### TABLE 9-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 I | Bit O  | Value On<br>POR / BOD | Value On<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|---------|--------|-----------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   |        | VR3    | VR2    | VR1     | VR0    | 000-0000 0            | 00- 0000                        |

| 1Fh     | CMCON | C2OUT | C10UT |       | —      | CIS    | CM2    | CM1     | CM0    | 00 0000 0             | 0 0000                          |

| 85h     | TRISA |       | _     | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1  | TRISA0 | 1 1111                | 1 1111                          |

Legend: - = Unimplemented, read as "0"

## 10.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16CE62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-Up Timer (OST) Brown-out Reset (BOD)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

The PIC16CE62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, and is designed to keep the part in reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

<sup>&</sup>quot; 1998-2013 Microchip Technology Inc.

| 11.1 | Instruction Descriptions |

|------|--------------------------|

|      |                          |

| ADDLW            | Add Litera                                 | al and W   | ,              |         |  |  |

|------------------|--------------------------------------------|------------|----------------|---------|--|--|

| Syntax:          | [label] A                                  | DDLW       | k              |         |  |  |

| Operands:        | 0 dk d25                                   | 5          |                |         |  |  |

| Operation:       | (W) + k o (W)                              |            |                |         |  |  |

| Status Affected: | C, DC, Z                                   |            |                |         |  |  |

| Encoding:        | 11                                         | 111x       | kkkk           | kkkk    |  |  |

| Description:     | The conter<br>added to th<br>result is pla | ne eight b | it literal 'k' | and the |  |  |

| Words:           | 1                                          |            |                |         |  |  |

| Cycles:          | 1                                          |            |                |         |  |  |

| Example          | ADDLW                                      | 0x15       |                |         |  |  |

|                  | After Instr                                | N =        | 0x10<br>0x25   |         |  |  |

| ANDLW            | AND Literal with W                                                                                                  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |  |  |  |  |  |  |

| Operands:        | 0 dk d255                                                                                                           |  |  |  |  |  |  |

| Operation:       | (W) .AND. (k) o (W)                                                                                                 |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                   |  |  |  |  |  |  |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                   |  |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |  |  |

| Words:           | 1                                                                                                                   |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                   |  |  |  |  |  |  |

| Example          | ANDLW 0x5F                                                                                                          |  |  |  |  |  |  |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                     |  |  |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                 |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                           |  |  |  |  |

| Operands:        | 0 df d127<br>d • > @                                                                                                                                                        |  |  |  |  |

| Operation:       | (W) + (f) o (dest)                                                                                                                                                          |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                    |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                           |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                                           |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                           |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                                |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                 |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] ANDWF f,d                                                                                                                                           |  |  |  |  |

| Operands:        | 0 df d127<br>d • > @                                                                                                                                        |  |  |  |  |

| Operation:       | (W) .AND. (f) o (dest)                                                                                                                                      |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                                |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |

# Worldwide Sales and Service

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755 China - Beijing Tel: 86-10-8569-7000

Fax: 86-10-8528-2104 China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123 India - New Delhi Tel: 91-11-4160-8631

Fax: 91-11-4160-8632 India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857

Fax: 60-3-6201-9859 Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

UK - Wokingham Tel: 44-118-921-5869 Fax: 44-118-921-5820