# E·XFL

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 4MHz                                                                          |

| Connectivity               | -                                                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                              |

| Number of I/O              | 13                                                                            |

| Program Memory Size        | 896B (512 x 14)                                                               |

| Program Memory Type        | OTP                                                                           |

| EEPROM Size                | 128 x 8                                                                       |

| RAM Size                   | 96 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | -                                                                             |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce623t-04i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | General Description                           | 3     |

|-------|-----------------------------------------------|-------|

| 2.0   | PIC16CE62X Device Varieties                   | 5     |

| 3.0   | Architectural Overview                        |       |

| 4.0   | Memory Organization                           | 11    |

| 5.0   | I/O Ports                                     |       |

| 6.0   | EEPROM Peripheral Operation                   | 29    |

| 7.0   | Timer0 Module                                 |       |

| 8.0   | Comparator Module                             | 41    |

| 9.0   | Voltage Reference Module                      | 47    |

| 10.0  | Special Features of the CPU                   | 49    |

| 11.0  | Instruction Set Summary                       | 65    |

|       | Development Support                           |       |

|       | Electrical Specifications                     |       |

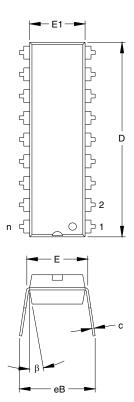

| 14.0  | Packaging Information                         | 97    |

| Appe  | ndix A: Code for Accessing EEPROM Data Memory | 103   |

| Index |                                               | 105   |

| On Li | ne Support                                    | . 107 |

| Read  | ne Support<br>er Response                     | 108   |

| PIC1  | 6CE62X Product Identification System          | . 109 |

### To Our Valued Customers

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

#### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

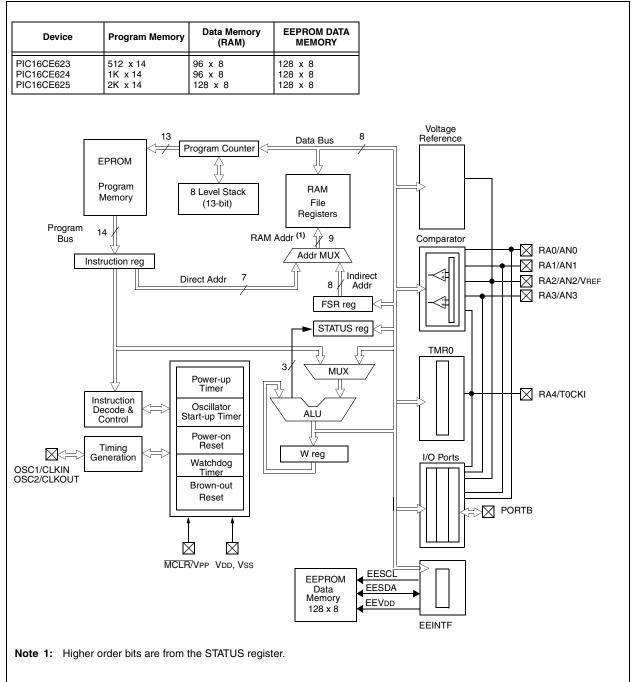

# FIGURE 3-1: BLOCK DIAGRAM

### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

# REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1    | R/W-1                                                                                                                          | R/W-1                                                       | R/W-1        | R/W-1      | R/W-1                  | R/W-1 | R/W-1 |                                                                                                                   |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------|------------|------------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| RBPU     | INTEDG                                                                                                                         | TOCS                                                        | TOSE         | PSA        | PS2                    | PS1   | PS0   | R = Readable bit                                                                                                  |  |  |  |

| bit7     |                                                                                                                                |                                                             |              |            |                        |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |  |  |  |

| bit 7:   |                                                                                                                                |                                                             |              |            |                        |       |       |                                                                                                                   |  |  |  |

| bit 6:   |                                                                                                                                |                                                             |              |            |                        |       |       |                                                                                                                   |  |  |  |

| bit 5:   | <b>TOCS</b> : TMR0 Clock Source Select bit<br>1 = Transition on RA4/T0CKI pin<br>0 = Internal instruction cycle clock (CLKOUT) |                                                             |              |            |                        |       |       |                                                                                                                   |  |  |  |

| bit 4:   |                                                                                                                                | ent on hig                                                  | h-to-low     | transition | on RA4/T0<br>on RA4/T0 |       |       |                                                                                                                   |  |  |  |

| bit 3:   | PSA: Prese<br>1 = Presca<br>0 = Presca                                                                                         | ler is assi                                                 | gned to t    | he WDT     | ) module               |       |       |                                                                                                                   |  |  |  |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : F                                                                                                       | Prescaler I                                                 | Rate Sele    | ect bits   |                        |       |       |                                                                                                                   |  |  |  |

|          | Bit Value                                                                                                                      | TMR0 Ra                                                     | te WD1       | Γ Rate     |                        |       |       |                                                                                                                   |  |  |  |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                           | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 :<br>3 1 : | 2<br>4     |                        |       |       |                                                                                                                   |  |  |  |

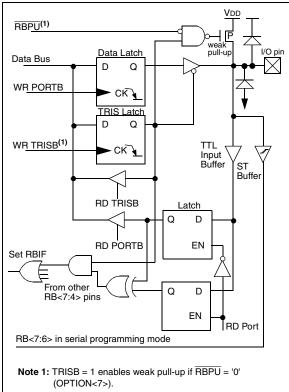

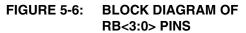

### 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a high impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{RBPU}$  (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins of RB<7:4> are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes".)

| Note: | If a change on the I/O pin should occur       |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|

|       | when the read operation is being executed     |  |  |  |  |  |  |

|       | (start of the Q2 cycle), then the RBIF inter- |  |  |  |  |  |  |

|       | rupt flag may not get set.                    |  |  |  |  |  |  |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

### 5.3 <u>I/O Programming Considerations</u>

### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read modify write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (i.e.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ; ; PORTB<7:6> have external pull-up and are not ; connected to other circuitry ; PORT latch PORT pins ; ; BCF PORTB. 7 ; 01pp pppp 11pp pppp BCF PORTB, 6 ; 10pp pppp 11pp pppp BSF STATUS, RPO ; BCF TRISB, 7 ; 10pp pppp 11pp pppp BCF TRISB, 6 ; 10pp pppp 10pp pppp ; ; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused ; RB7 to be latched as the pin value (High).

### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

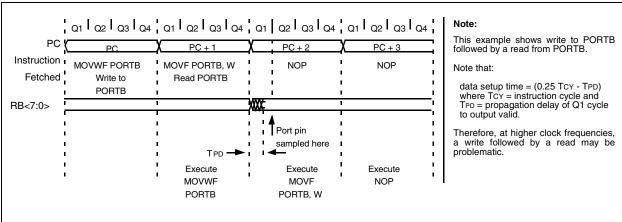

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with an NOP or another instruction not accessing this I/O port.

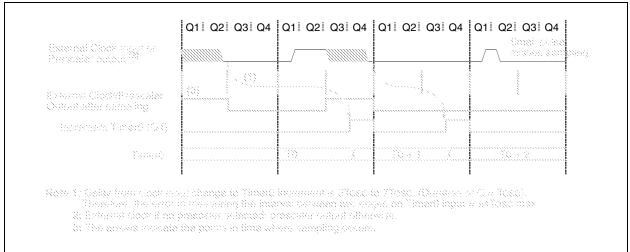

### FIGURE 5-7: SUCCESSIVE I/O OPERATION

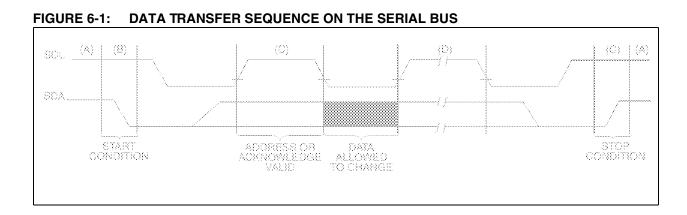

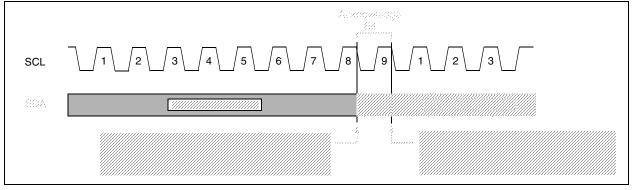

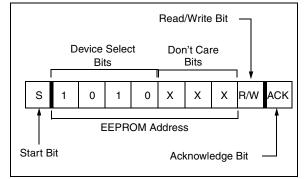

### 6.2 Device Addressing

After generating a START condition, the processor transmits a control byte consisting of a EEPROM address and a Read/Write bit that indicates what type of operation is to be performed. The EEPROM address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one, a read operation is selected, and when set to a zero, a write operation is selected. (Figure 6-3). The bus is monitored for its corresponding EEPROM address all the time. It generates an acknowledge bit if the EEPROM address was true and it is not in a programming mode.

### FIGURE 6-3: CONTROL BYTE FORMAT

### 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

### FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

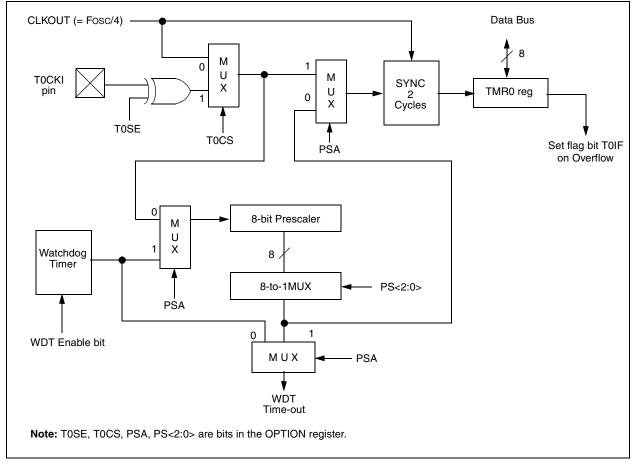

### 7.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

NOTES:

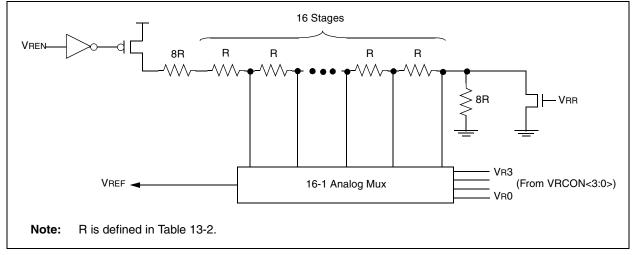

# 9.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 9-1. The block diagram is given in Figure 9-1.

### 9.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1: VREF = (VR<3:0>/24) x VDD

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 13-1). Example 9-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

| R/W-0                                                                                                                                                              | R/W-0                                                                                                 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |                                                                                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|-------|-------|---------------------------------------------------------------------------------------|--|--|--|

| VREN                                                                                                                                                               | VROE                                                                                                  | Vrr   | _   | Vr3   | VR2   | VR1   | VR0   | R = Readable bit                                                                      |  |  |  |

| bit7                                                                                                                                                               | •                                                                                                     |       | •   |       |       |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |  |  |  |

| bit 7: VREF Enable<br>1 = VREF circuit powered on<br>0 = VREF circuit powered down, no IDD drain                                                                   |                                                                                                       |       |     |       |       |       |       |                                                                                       |  |  |  |

| bit 6:                                                                                                                                                             | 6: VROE: VREF Output Enable<br>1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |       |     |       |       |       |       |                                                                                       |  |  |  |

| bit 5:                                                                                                                                                             | VRR: VREF Range selection<br>1 = Low Range<br>0 = High Range                                          |       |     |       |       |       |       |                                                                                       |  |  |  |

| bit 4: Unimplemented: Read as '0'                                                                                                                                  |                                                                                                       |       |     |       |       |       |       |                                                                                       |  |  |  |

| bit 3-0: VR<3:0>: VREF value selection $0 \le VR [3:0] \le 15$<br>when VRR = 1: VREF = (VR<3:0>/ 24) * VDD<br>when VRR = 0: VREF = 1/4 * VDD + (VR<3:0>/ 32) * VDD |                                                                                                       |       |     |       |       |       |       |                                                                                       |  |  |  |

# REGISTER 9-1: VRCON REGISTER (ADDRESS 9Fh)

FIGURE 9-1: VOLTAGE REFERENCE BLOCK DIAGRAM

### EXAMPLE 9-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x07        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | outputs        |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank 0   |

| CALL  | DELAY10     | ; | 10µs delay     |

### 9.2 <u>Voltage Reference Accuracy/Error</u>

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 9-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 13-2.

### 9.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

### 9.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

### 9.5 <u>Connection Considerations</u>

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 9-2 shows an example buffering technique.

# VREF Nodule Voltage Reference Output Impedance

# FIGURE 9-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

Note 1: R is dependent upon the Voltage Reference Configuration VRCON<3:0> and VRCON<5>.

### TABLE 9-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR / BOD | Value On<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000             | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000               | 00 0000                         |

| 85h     | TRISA | _     | _     |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                | 1 1111                          |

Legend: - = Unimplemented, read as "0"

### 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

**REGISTER 10-1: CONFIGURATION WORD**

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1 CP    | 0 <sup>(2)</sup> CP1 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <sub>CP0</sub> (2) | CP1      | CP0 <sup>(2)</sup> | _       | BODEN <sup>(1)</sup> | CP1    | CP0 <sup>(2)</sup> | PWRTE(    | 1) WDTE | F0SC1       | F0SC0       | CONFIG       | Addres  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--------------------|---------|----------------------|--------|--------------------|-----------|---------|-------------|-------------|--------------|---------|

| bit13     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |          |                    |         |                      |        |                    |           |         |             | bit0        | REGISTER     | 8: 2007 |

| bit 13-8, | CP1:CP0 Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | irs: Cod           | le prote | ection bit         | pairs   | (2)                  |        |                    |           |         |             |             |              |         |

| 5-4:      | · · · · •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          | •                  |         | n off                |        |                    |           |         |             |             |              |         |

|           | 10 = 0400h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = 0200h-<br>00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | Code prote                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         | morv                 |        |                    |           |         |             |             |              |         |

|           | 11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 10 =Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = 0200h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | Code prote<br>11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |          |                    |         | -                    |        |                    |           |         |             |             |              |         |

|           | 11 = Progra<br>10 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          | •                  |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          | •                  |         |                      |        |                    |           |         |             |             |              |         |

|           | 00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -01FFh             | code     | ,<br>protecte      | d       |                      |        |                    |           |         |             |             |              |         |

| bit 7:    | Unimpleme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ented: F           | Read a   | s '1'              |         |                      |        |                    |           |         |             |             |              |         |

| bit 6:    | BODEN: Bro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | own-ou             | t Rese   | t Enable           | e bit ( | 1)                   |        |                    |           |         |             |             |              |         |

|           | 1 = BOD en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 0 = BOD dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | sabled             |          |                    |         |                      |        |                    |           |         |             |             |              |         |

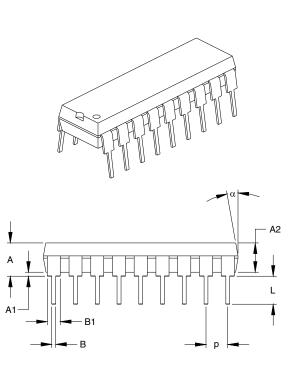

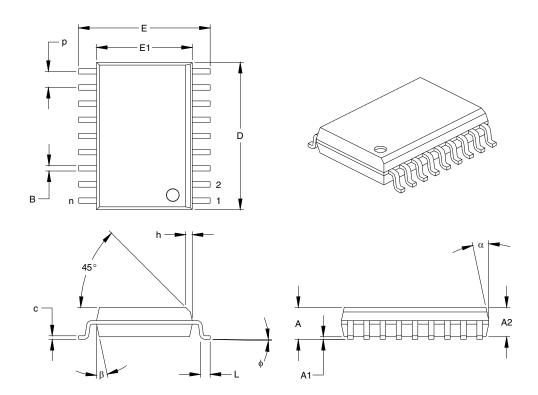

| bit 3:    | PWRTE: Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | wer-up             | Timer    | Enable             | bit (1  | )                    |        |                    |           |         |             |             |              |         |