Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 4MHz                                                                       |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 13                                                                         |

| Program Memory Size        | 1.75KB (1K x 14)                                                           |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | 128 x 8                                                                    |

| RAM Size                   | 96 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                    |

| Supplier Device Package    | 18-PDIP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce624-04-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 GENERAL DESCRIPTION

The PIC16CE62X are 18 and 20-Pin EPROM-based members of the versatile PIC<sup>®</sup> family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with EEPROM data memory.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16CE62X family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CE62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16CE623 and PIC16CE624 have 96 bytes of RAM. The PIC16CE625 has 128 bytes of RAM. Each microcontroller contains a 128x8 EEPROM memory array for storing non-volatile information, such as calibration data or security codes. This memory has an endurance of 1,000,000 erase/write cycles and a retention of 40 plus years.

Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16CE62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low-cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16CE62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and reset. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development, while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16CE62X mid-range microcontroller families.

A simplified block diagram of the PIC16CE62X is shown in Figure 3-1.

The PIC16CE62X series fits perfectly in applications ranging from multi-pocket battery chargers to low-power remote sensors. The EPROM technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high-performance, ease of use and I/O flexibility make the PIC16CE62X very versatile.

# 1.1 <u>Development Support</u>

The PIC16CE62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler is also available.

| Name         | DIP/<br>SOIC<br>Pin # | SSOP<br>Pin #                   | l/O/P<br>Type | Buffer<br>Type          | Description                                                                                                                                                                                                       |

|--------------|-----------------------|---------------------------------|---------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1/CLKIN   | 16                    | 18                              | I             | ST/CMOS                 | Oscillator crystal input/external clock source input.                                                                                                                                                             |

| OSC2/CLKOUT  | 15                    | 17                              | 0             | -                       | Oscillator crystal output. Connects to crystal or resonator<br>in crystal oscillator mode. In RC mode, OSC2 pin outputs<br>CLKOUT which has 1/4 the frequency of OSC1, and<br>denotes the instruction cycle rate. |

| MCLR/Vpp     | 4                     | 4                               | I/P           | ST                      | Master clear (reset) input/programming voltage input.<br>This pin is an active low reset to the device.                                                                                                           |

|              |                       |                                 |               |                         | PORTA is a bi-directional I/O port.                                                                                                                                                                               |

| RA0/AN0      | 17                    | 19                              | I/O           | ST                      | Analog comparator input                                                                                                                                                                                           |

| RA1/AN1      | 18                    | 20                              | I/O           | ST                      | Analog comparator input                                                                                                                                                                                           |

| RA2/AN2/VREF | 1                     | 1                               | I/O           | ST                      | Analog comparator input or VREF output                                                                                                                                                                            |

| RA3/AN3      | 2                     | 2                               | I/O           | ST                      | Analog comparator input /output                                                                                                                                                                                   |

| RA4/T0CKI    | 3                     | 3                               | I/O           | ST                      | Can be selected to be the clock input to the Timer0<br>timer/counter or a comparator output. Output is open<br>drain type.                                                                                        |

|              |                       |                                 |               |                         | PORTB is a bi-directional I/O port. PORTB can be<br>software programmed for internal weak pull-up on all<br>inputs.                                                                                               |

| RB0/INT      | 6                     | 7                               | I/O           | TTL/ST(1)               | RB0/INT can also be selected as an external interrupt pin.                                                                                                                                                        |

| RB1          | 7                     | 8                               | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB2          | 8                     | 9                               | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB3          | 9                     | 10                              | I/O           | TTL                     |                                                                                                                                                                                                                   |

| RB4          | 10                    | 11                              | I/O           | TTL                     | Interrupt on change pin.                                                                                                                                                                                          |

| RB5          | 11                    | 12                              | I/O           | TTL                     | Interrupt on change pin.                                                                                                                                                                                          |

| RB6          | 12                    | 13                              | I/O           | TTL/ST <sup>(2)</sup>   | Interrupt on change pin. Serial programming clock.                                                                                                                                                                |

| RB7          | 13                    | 14                              | I/O           | TTL/ST <sup>(2)</sup>   | Interrupt on change pin. Serial programming data.                                                                                                                                                                 |

| Vss          | 5                     | 5,6                             | Р             | l –                     | Ground reference for logic and I/O pins.                                                                                                                                                                          |

| Vdd          | 14                    | 15,16                           | Р             | —                       | Positive supply for logic and I/O pins.                                                                                                                                                                           |

| Legend:      |                       | utput<br>Not used<br>: TTL inpu | 1 :           | O = input/or<br>= Input | utput P = power<br>ST = Schmitt Trigger input                                                                                                                                                                     |

**TABLE 3-1: PIC16CE62X PINOUT DESCRIPTION**

**Note 1:** This buffer is a Schmitt Trigger input when configured as the external interrupt. **Note 2:** This buffer is a Schmitt Trigger input when used in serial programming mode.

PIC16CE62X

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The special registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7                  | Bit 6              | Bit 5       | Bit 4         | Bit 3        | Bit 2        | Bit 1        | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>resets <sup>(1)</sup> |

|---------|---------------|------------------------|--------------------|-------------|---------------|--------------|--------------|--------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 00h     | INDF          | Addressin<br>register) | ig this locat      | a physical  | xxxx xxxx     | xxxx xxxx    |              |              |            |                       |                                                |

| 01h     | TMR0          | Timer0 M               | odule's Reg        | jister      |               |              |              |              |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          |              |              |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>     | RP1 <sup>(2)</sup> | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | I            |              | I          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         |                        |                    |             | RA4           | RA3          | RA2          | RA1          | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                    | RB6                | RB5         | RB4           | RB3          | RB2          | RB1          | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h     | Unimplemented |                        | 1                  |             | 1             |              | 1            |              | 1          | -                     | -                                              |

| 08h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 09h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 0Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | —                      | CMIF               | —           | —             | —            | —            | —            | —          | - 0                   | -0                                             |

| 0Dh-1Eh | Unimplemented |                        |                    |             |               |              |              |              |            |                       | _                                              |

| 1Fh     | CMCON         | C2OUT                  | C10UT              | _           | _             | CIS          | CM2          | CM1          | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 80h     | INDF          | Addressin<br>register) | ig this locat      | ion uses co | ontents of F  | SR to addre  | ess data me  | emory (not a | a physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                   | INTEDG             | TOCS        | TOSE          | PSA          | PS2          | PS1          | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          | 1            |              | 1          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP                    | RP1                | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | 1            |              | 1          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                      |                    |             | TRISA4        | TRISA3       | TRISA2       | TRISA1       | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7                 | TRISB6             | TRISB5      | TRISB4        | TRISB3       | TRISB2       | TRISB1       | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 88h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 89h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | T0IF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                      | CMIE               | _           | —             | _            | —            | _            | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Eh     | PCON          | —                      | —                  | —           | —             | —            | —            | POR          | BOD        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 90h     | EEINTF        | —                      | —                  | —           | —             | —            | EESCL        | EESDA        | EEVDD      | 111                   | 111                                            |

| 9Fh     | VRCON         | VREN                   | VROE               | VRR         | —             | VR3          | VR2          | VR1          | VR0        | 000- 0000             | 000- 0000                                      |

# TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16CE62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non power-up) resets include MCLR reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

Note 2: IRP & RPI bits are reserved; always maintain these bits clear.

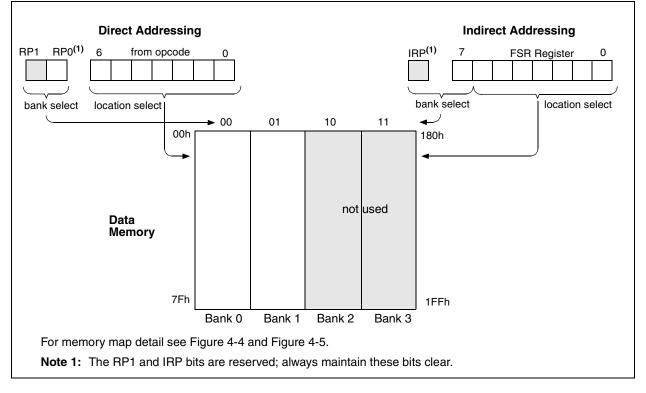

#### 4.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no-operation (although status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>), as shown in Figure 4-7. However, IRP is not used in the PIC16CE62X. A simple program to clear RAM location 20h-2Fh using indirect addressing is shown in Example 4-1.

| EXAMPL    | E 4-1: | INDIRE | ECT ADDRESSING       |

|-----------|--------|--------|----------------------|

|           | movlw  | 0x20   | ;initialize pointer  |

|           | movwf  | FSR    | ;to RAM              |

| NEXT      | clrf   | INDF   | clear INDF register; |

|           | incf   | FSR    | ;inc pointer         |

|           | btfss  | FSR,4  | ;all done?           |

|           | goto   | NEXT   | ;no clear next       |

|           |        |        | ;yes continue        |

| CONTINUE: |        |        |                      |

# FIGURE 4-7: DIRECT/INDIRECT ADDRESSING PIC16CE62X

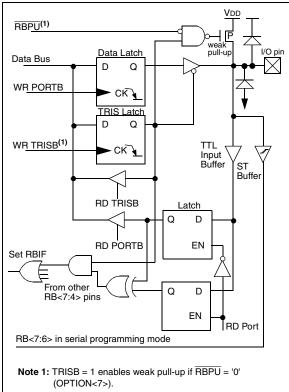

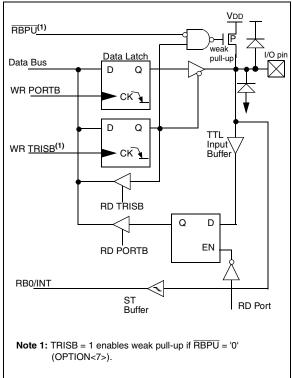

# 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a high impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{RBPU}$  (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins of RB<7:4> are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes".)

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

# 5.3 <u>I/O Programming Considerations</u>

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read modify write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (i.e.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ; ; PORTB<7:6> have external pull-up and are not ; connected to other circuitry ; PORT latch PORT pins ; ; BCF PORTB. 7 ; 01pp pppp 11pp pppp BCF PORTB, 6 ; 10pp pppp 11pp pppp BSF STATUS, RPO ; BCF TRISB, 7 ; 10pp pppp 11pp pppp BCF TRISB, 6 ; 10pp pppp 10pp pppp ; ; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused ; RB7 to be latched as the pin value (High).

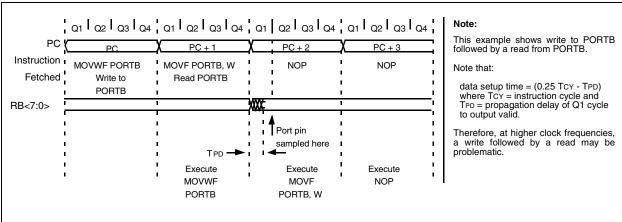

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with an NOP or another instruction not accessing this I/O port.

#### FIGURE 5-7: SUCCESSIVE I/O OPERATION

# 6.5 <u>Read Operation</u>

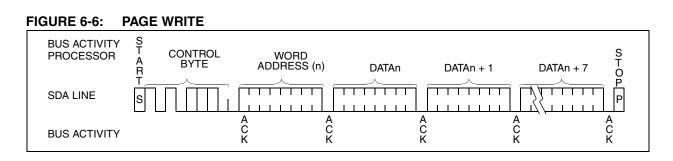

Read operations are initiated in the same way as write operations with the exception that the  $R/\overline{W}$  bit of the EEPROM address is set to one. There are three basic types of read operations: current address read, random read, and sequential read.

# 6.6 Current Address Read

The EEPROM contains an address counter that maintains the address of the last word accessed, internally incremented by one. Therefore, if the previous access (either a read or write operation) was to address n, the next current address read operation would access data from address n + 1. Upon receipt of the EEPROM address with R/W bit set to one, the EEPROM issues an acknowledge and transmits the eight bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-7).

# 6.7 Random Read

Random read operations allow the processor to access any memory location in a random manner. To perform this type of read operation, first the word address must be set. This is done by sending the word address to the EEPROM as part of a write operation. After the word address is sent, the processor generates a start condition following the acknowledge. This terminates the write operation, but not before the internal address pointer is set. Then the processor issues the control byte again, but with the R/W bit set to a one. The EEPROM will then issue an acknowledge and transmits the eight bit data word. The processor will not acknowledge the transfer, but does generate a stop condition and the EEPROM discontinues transmission (Figure 6-8).

# 6.8 Sequential Read

Sequential reads are initiated in the same way as a random read except that after the EEPROM transmits the first data byte, the processor issues an acknowledge as opposed to a stop condition in a random read. This directs the EEPROM to transmit the next sequentially addressed 8-bit word (Figure 6-9).

To provide sequential reads, the EEPROM contains an internal address pointer which is incremented by one at the completion of each operation. This address pointer allows the entire memory contents to be serially read during one operation.

# 6.9 Noise Protection

The EEPROM employs a Vcc threshold detector circuit, which disables the internal erase/write logic if the Vcc is below 1.5 volts at nominal conditions.

The SCL and SDA inputs have Schmitt trigger and filter circuits, which suppress noise spikes to assure proper device operation even on a noisy bus.

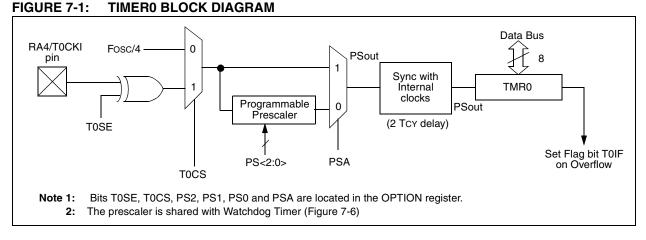

# 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

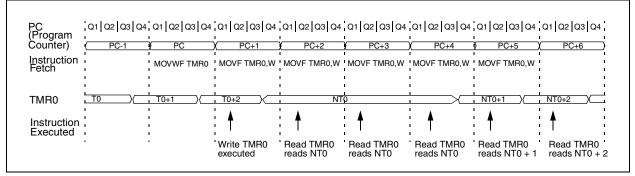

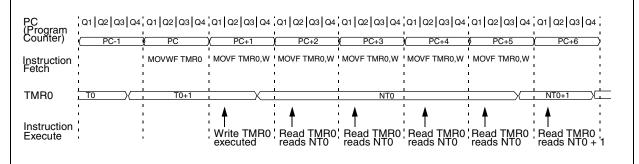

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

# 7.1 <u>Timer0 Interrupt</u>

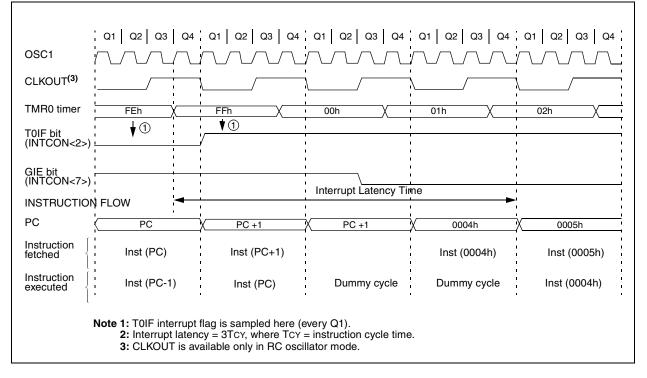

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

# FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

# PIC16CE62X

## FIGURE 7-4: TIMER0 INTERRUPT TIMING

# 7.2 Using Timer0 with External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

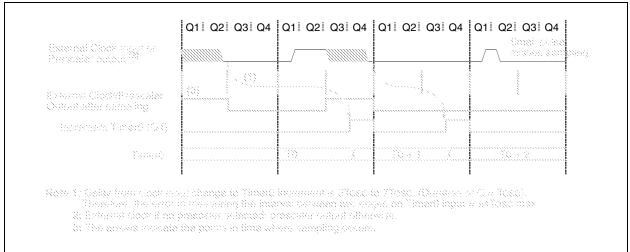

#### 7.2.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 7-5). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 20 ns) and low for at least 2Tosc (and a small RC delay of 20 ns). Refer to the electrical specification of the desired device. When a prescaler is used, the external clock input is divided by the asynchronous ripple-counter type prescaler so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple-counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4TOSC (and a small RC delay of 40 ns) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of 10 ns. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 7.2.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the TMR0 is actually incremented. Figure 7-5 shows the delay from the external clock edge to the timer incrementing.

## FIGURE 7-5: TIMER0 TIMING WITH EXTERNAL CLOCK

The code example in Example 8-1 depicts the steps required to configure the comparator module. RA3 and RA4 are configured as digital output. RA0 and RA1 are configured as the V- inputs and RA2 as the V+ input to both comparators.

#### EXAMPLE 8-1: INITIALIZING COMPARATOR MODULE

| FLAG_REG | f EQU        | 0X20                              |

|----------|--------------|-----------------------------------|

| CLRF     | FLAG_REG     | ;Init flag register               |

| CLRF     | PORTA        | ;Init PORTA                       |

| MOVF     | CMCON,W      | ;Move comparator contents to W    |

| ANDLW    | 0xC0         | ;Mask comparator bits             |

| IORWF    | FLAG_REG,F   | ;Store bits in flag register      |

| MOVLW    | 0x03         | ;Init comparator mode             |

| MOVWF    | CMCON        | ;CM<2:0> = 011                    |

| BSF      | STATUS, RPO  | ;Select Bank1                     |

| MOVLW    | 0x07         | ;Initialize data direction        |

| MOVWF    | TRISA        | ;Set RA<2:0> as inputs            |

|          |              | ;RA<4:3> as outputs               |

|          |              | ;TRISA<7:5> always read `0'       |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| CALL     | DELAY 10     | ;10µs delay                       |

| MOVF     | CMCON, F     | ;Read CMCONtoend change condition |

| BCF      | PIR1,CMIF    | ;Clear pending interrupts         |

| BSF      | STATUS, RPO  | ;Select Bank 1                    |

| BSF      | PIE1,CMIE    | ;Enable comparator interrupts     |

| BCF      | STATUS, RPO  | ;Select Bank 0                    |

| BSF      | INTCON, PEIE | ;Enable peripheral interrupts     |

| BSF      | INTCON, GIE  | ;Global interrupt enable          |

|          |              |                                   |

## 8.2 Comparator Operation

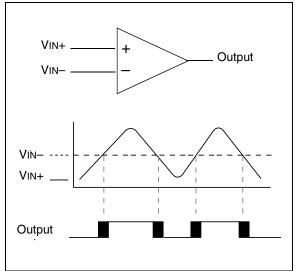

A single comparator is shown in Figure 8-2 along with the relationship between the analog input levels and the digital output. When the analog input at VIN+ is less than the analog input VIN–, the output of the comparator is a digital low level. When the analog input at VIN+ is greater than the analog input VIN–, the output of the comparator is a digital high level. The shaded areas of the output of the comparator in Figure 8-2 represent the uncertainty due to input offsets and response time.

# 8.3 <u>Comparator Reference</u>

An external or internal reference signal may be used depending on the comparator operating mode. The analog signal that is present at VIN– is compared to the signal at VIN+, and the digital output of the comparator is adjusted accordingly (Figure 8-2).

FIGURE 8-2: SINGLE COMPARATOR

## 8.3.1 EXTERNAL REFERENCE SIGNAL

When external voltage references are used, the comparator module can be configured to have the comparators operate from the same or different reference sources. However, threshold detector applications may require the same reference. The reference signal must be between VSS and VDD and can be applied to either pin of the comparator(s).

#### 8.3.2 INTERNAL REFERENCE SIGNAL

The comparator module also allows the selection of an internally generated voltage reference for the comparators. Section 13, Instruction Sets, contains a detailed description of the Voltage Reference Module that provides this signal. The internal reference signal is used when the comparators are in mode CM<2:0>=010 (Figure 8-1). In this mode, the internal voltage reference is applied to the VIN+ pin of both comparators.

#### EXAMPLE 9-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x07        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | outputs        |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank 0   |

| CALL  | DELAY10     | ; | 10µs delay     |

#### 9.2 <u>Voltage Reference Accuracy/Error</u>

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 9-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 13-2.

## 9.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

# 9.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

## 9.5 <u>Connection Considerations</u>

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 9-2 shows an example buffering technique.

# VREF Nodule Voltage Reference Output Impedance

# FIGURE 9-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

Note 1: R is dependent upon the Voltage Reference Configuration VRCON<3:0> and VRCON<5>.

# TABLE 9-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR / BOD | Value On<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000             | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000               | 00 0000                         |

| 85h     | TRISA | _     | _     |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                | 1 1111                          |

Legend: - = Unimplemented, read as "0"

# 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

**REGISTER 10-1: CONFIGURATION WORD**

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

|           |                         |                    |          | 1                  |         |                      |       |                    | I         |         |           |                   |              |        |    |

|-----------|-------------------------|--------------------|----------|--------------------|---------|----------------------|-------|--------------------|-----------|---------|-----------|-------------------|--------------|--------|----|

| CP1 CF    | 0 <sup>(2)</sup> CP1    | CP0 <sup>(2)</sup> | CP1      | CP0 <sup>(2)</sup> | _       | BODEN <sup>(1)</sup> | CP1   | CP0 <sup>(2)</sup> | PWRTE(    | 1) WDTE | F0SC1     | F0SC0             | CONFIG       | Addre  |    |

| bit13     |                         |                    |          |                    |         |                      |       |                    |           |         |           | bit0              | REGISTER     | R: 200 | 7h |

| bit 13-8, | CP1:CP0 P               | Pairs: Co          | de prote | ection bit         | pairs   | (2)                  |       |                    |           |         |           |                   |              |        |    |

| 5-4:      |                         |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 11 = Prog               |                    |          | •                  |         | n off                |       |                    |           |         |           |                   |              |        |    |

|           | 10 = 0400               |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 01 = 0200<br>00 = 0000  |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | Code prot               |                    |          |                    |         | morv                 |       |                    |           |         |           |                   |              |        |    |

|           | 11 = Prog               |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 10 =Progra              |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 01 = 0200               |                    |          | •                  |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 00 = 0000               |                    |          | •                  |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | Code prot               |                    |          | •••                |         | •                    |       |                    |           |         |           |                   |              |        |    |

|           | 10 = Prog               |                    |          | •                  |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 01 = Prog               |                    |          | •                  |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 00 = 0000               | h-01FFh            | n code   | protecte           | d       |                      |       |                    |           |         |           |                   |              |        |    |

| bit 7:    | Unimplem                | nented:            | Read a   | as '1'             |         |                      |       |                    |           |         |           |                   |              |        |    |

| bit 6:    | BODEN: E                | Brown-ou           | ut Rese  | et Enable          | e bit ( | 1)                   |       |                    |           |         |           |                   |              |        |    |

|           | 1 = BOD e               |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 0 = BOD d               | lisabled           |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

| bit 3:    | PWRTE: F                | ower-up            | o Timer  | r Enable           | bit (1  | )                    |       |                    |           |         |           |                   |              |        |    |

|           | 1 = PWRT                |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 0 = PWRT                | enableo            | b        |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

| bit 2:    | WDTE: Wa                | -                  | Timer    | Enable I           | oit     |                      |       |                    |           |         |           |                   |              |        |    |

|           | 1 = WDT e               |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 0 = WDT c               | disabled           |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

| bit 1-0:  |                         |                    |          | or Select          | tion b  | oits                 |       |                    |           |         |           |                   |              |        |    |

|           | 11 = RC o               |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 10 = HS o<br>01 = XT o  |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           | 01 = XT 03 $00 = LP 03$ |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

|           |                         |                    |          |                    |         |                      |       |                    |           |         |           |                   |              |        |    |

| Note 1:   |                         |                    |          |                    |         |                      |       |                    |           |         | ardless o | of the valu       | e of bit PWR | TE.    |    |

| <b>c</b>  | Ensure the              |                    | •        |                    |         |                      |       |                    |           |         |           | a a la a sa a - P | : at a d     |        |    |

| 2:        | All of the C            | JP<1:0>            | pairs r  | iave to t          | be giv  | ien the sa           | me va | iue to er          | iable the | coae pr | olection  | scheme I          | istea.       |        |    |

# 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

#### 12.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

#### 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

#### 12.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

#### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script. stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

# 12.11 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PIC devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

## 12.12 <u>SIMICE Entry-Level</u> <u>Hardware Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB-SIM. Both SIMICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PIC 8-bit microcontrollers. SIM-ICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entry-level system development.

# 12.13 <u>PICDEM-1 Low-Cost PIC MCU</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

# 12.14 <u>PICDEM-2 Low-Cost PIC16CXX</u> <u>Demonstration Board</u>

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

# 12.15 <u>PICDEM-3 Low-Cost PIC16CXXX</u> <u>Demonstration Board</u>

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

# 12.16 PICDEM-17

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756, PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug

# PIC16CE62X

and test the sample code. In addition, PICDEM-17 supports down-loading of programs to and executing out of external FLASH memory on board. The PICDEM-17 is also usable with the MPLAB-ICE or PICMASTER emulator, and all of the sample programs can be run and modified using either emulator. Additionally, a generous prototype area is available for user hardware.

# 12.17 <u>SEEVAL Evaluation and Programming</u> <u>System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

# 12.18 <u>KEELOQ Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

# 13.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| 2. ippo |                                         |     |              |

|---------|-----------------------------------------|-----|--------------|

| т       |                                         |     |              |

| F       | Frequency                               | Т   | Time         |

| Lowerc  | ase subscripts (pp) and their meanings: |     |              |

| рр      |                                         |     |              |

| ck      | CLKOUT                                  | OSC | OSC1         |

| io      | I/O port                                | tO  | TOCKI        |

| mc      | MCLR                                    |     |              |

| Upperc  | ase letters and their meanings:         |     |              |

| S       |                                         |     |              |

| F       | Fall                                    | Р   | Period       |

| Н       | High                                    | R   | Rise         |

| I       | Invalid (Hi-impedance)                  | V   | Valid        |

| L       | Low                                     | Z   | Hi-Impedance |

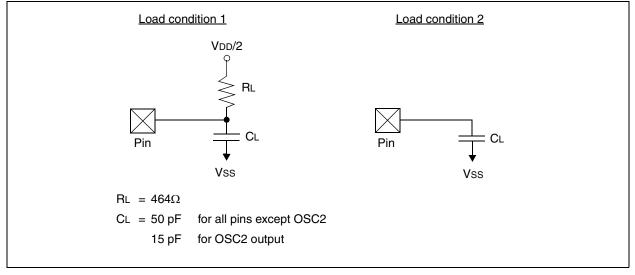

# FIGURE 13-4: LOAD CONDITIONS

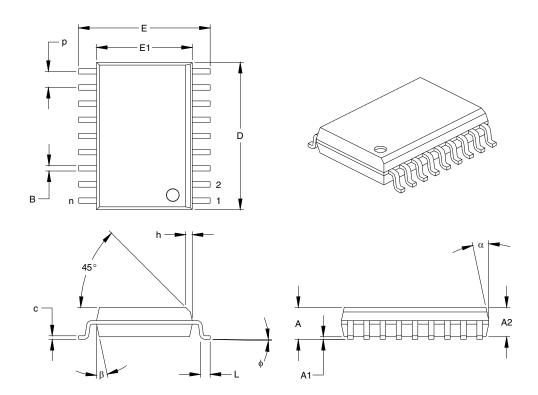

# 18-Lead Plastic Small Outline (SO) - Wide, 300 mil (SOIC)

Note: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Limits<br>n | MIN                                         | NOM                                                                                              |                                                                                                                                                           |                                                                                                                                                                                                   |                                                                                                                                                                                            |                                                                                                                                                                                                                                     |

|-------------|---------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| n           |                                             | 110101                                                                                           | MAX                                                                                                                                                       | MIN                                                                                                                                                                                               | NOM                                                                                                                                                                                        | MAX                                                                                                                                                                                                                                 |

|             |                                             | 18                                                                                               |                                                                                                                                                           |                                                                                                                                                                                                   | 18                                                                                                                                                                                         |                                                                                                                                                                                                                                     |

| р           |                                             | .050                                                                                             |                                                                                                                                                           |                                                                                                                                                                                                   | 1.27                                                                                                                                                                                       |                                                                                                                                                                                                                                     |

| А           | .093                                        | .099                                                                                             | .104                                                                                                                                                      | 2.36                                                                                                                                                                                              | 2.50                                                                                                                                                                                       | 2.64                                                                                                                                                                                                                                |

| A2          | .088                                        | .091                                                                                             | .094                                                                                                                                                      | 2.24                                                                                                                                                                                              | 2.31                                                                                                                                                                                       | 2.39                                                                                                                                                                                                                                |

| A1          | .004                                        | .008                                                                                             | .012                                                                                                                                                      | 0.10                                                                                                                                                                                              | 0.20                                                                                                                                                                                       | 0.30                                                                                                                                                                                                                                |

| Е           | .394                                        | .407                                                                                             | .420                                                                                                                                                      | 10.01                                                                                                                                                                                             | 10.34                                                                                                                                                                                      | 10.67                                                                                                                                                                                                                               |

| E1          | .291                                        | .295                                                                                             | .299                                                                                                                                                      | 7.39                                                                                                                                                                                              | 7.49                                                                                                                                                                                       | 7.59                                                                                                                                                                                                                                |

| D           | .446                                        | .454                                                                                             | .462                                                                                                                                                      | 11.33                                                                                                                                                                                             | 11.53                                                                                                                                                                                      | 11.73                                                                                                                                                                                                                               |

| h           | .010                                        | .020                                                                                             | .029                                                                                                                                                      | 0.25                                                                                                                                                                                              | 0.50                                                                                                                                                                                       | 0.74                                                                                                                                                                                                                                |

| L           | .016                                        | .033                                                                                             | .050                                                                                                                                                      | 0.41                                                                                                                                                                                              | 0.84                                                                                                                                                                                       | 1.27                                                                                                                                                                                                                                |

| ø           | 0                                           | 4                                                                                                | 8                                                                                                                                                         | 0                                                                                                                                                                                                 | 4                                                                                                                                                                                          | 8                                                                                                                                                                                                                                   |