Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 4MHz                                                                        |

| Connectivity               | -                                                                           |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                            |

| Number of I/O              | 13                                                                          |

| Program Memory Size        | 1.75KB (1K x 14)                                                            |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | 128 x 8                                                                     |

| RAM Size                   | 96 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                 |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 18-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce624-04e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 GENERAL DESCRIPTION

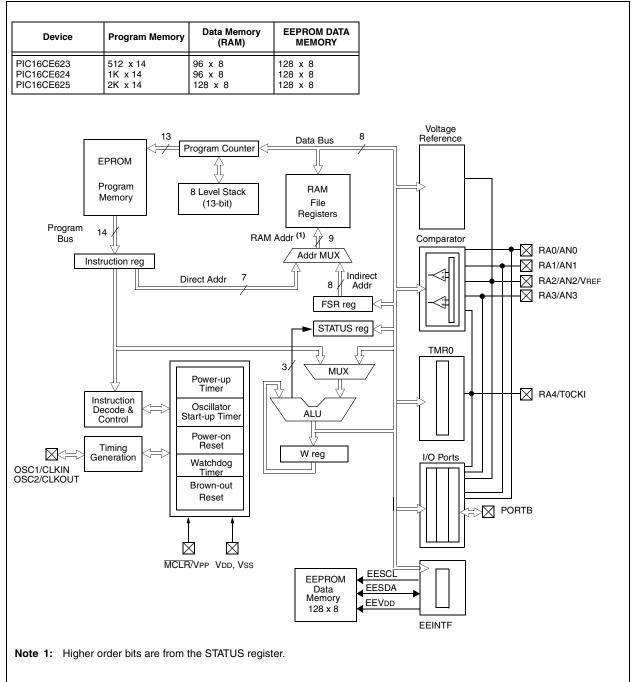

The PIC16CE62X are 18 and 20-Pin EPROM-based members of the versatile PIC<sup>®</sup> family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers with EEPROM data memory.

All PIC<sup>®</sup> microcontrollers employ an advanced RISC architecture. The PIC16CE62X family has enhanced core features, eight-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 14-bit wide instruction word with separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single-cycle, except for program branches (which require two cycles). A total of 35 instructions (reduced instruction set) are available. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance.

PIC16CE62X microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

The PIC16CE623 and PIC16CE624 have 96 bytes of RAM. The PIC16CE625 has 128 bytes of RAM. Each microcontroller contains a 128x8 EEPROM memory array for storing non-volatile information, such as calibration data or security codes. This memory has an endurance of 1,000,000 erase/write cycles and a retention of 40 plus years.

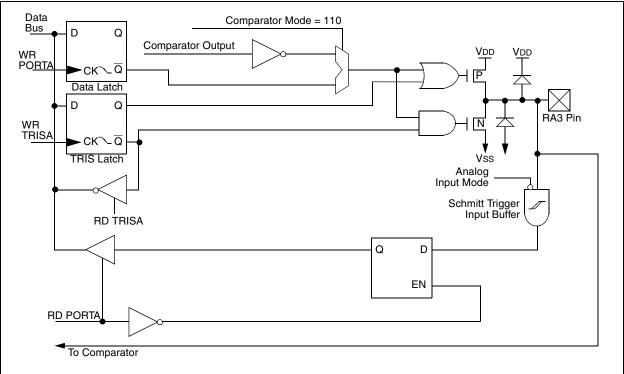

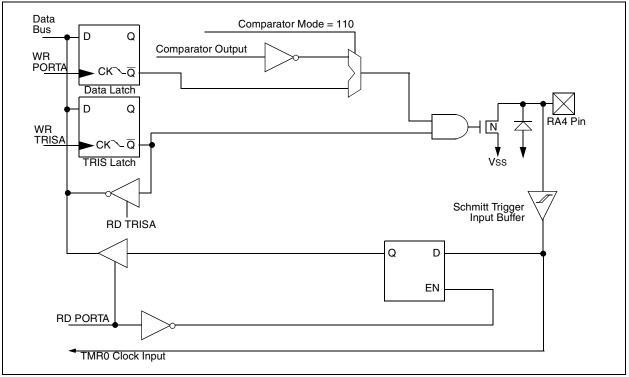

Each device has 13 I/O pins and an 8-bit timer/counter with an 8-bit programmable prescaler. In addition, the PIC16CE62X adds two analog comparators with a programmable on-chip voltage reference module. The comparator module is ideally suited for applications requiring a low-cost analog interface (e.g., battery chargers, threshold detectors, white goods controllers, etc).

PIC16CE62X devices have special features to reduce external components, thus reducing system cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LP oscillator minimizes power consumption, XT is a standard crystal, and the HS is for High Speed crystals. The SLEEP (power-down) mode offers power savings. The user can wake-up the chip from SLEEP through several external and internal interrupts and reset. A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software lock- up.

A UV-erasable CERDIP-packaged version is ideal for code development, while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

Table 1-1 shows the features of the PIC16CE62X mid-range microcontroller families.

A simplified block diagram of the PIC16CE62X is shown in Figure 3-1.

The PIC16CE62X series fits perfectly in applications ranging from multi-pocket battery chargers to low-power remote sensors. The EPROM technology makes customization of application programs (detection levels, pulse generation, timers, etc.) extremely fast and convenient. The small footprint packages make this microcontroller series perfect for all applications with space limitations. Low-cost, low-power, high-performance, ease of use and I/O flexibility make the PIC16CE62X very versatile.

## 1.1 <u>Development Support</u>

The PIC16CE62X family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a low-cost development programmer and a full-featured programmer. A "C" compiler is also available.

### TABLE 1-1: PIC16CE62X FAMILY OF DEVICES

|             |                                      | PIC16CE623                          | PIC16CE624                          | PIC16CE625                          |

|-------------|--------------------------------------|-------------------------------------|-------------------------------------|-------------------------------------|

| Clock       | Maximum Frequency of Operation (MHz) | 20                                  | 20                                  | 20                                  |

| Momoriy     | EPROM Program Memory (x14 words)     | 512                                 | 1K                                  | 2K                                  |

| Memory      | Data Memory (bytes)                  | 96                                  | 96                                  | 128                                 |

|             | EEPROM Data Memory (bytes)           | 128                                 | 128                                 | 128                                 |

| Peripherals | Timer Module(s)                      | TMR0                                | TMR0                                | TMR0                                |

| Peripherais | Comparators(s)                       | 2                                   | 2                                   | 2                                   |

|             | Internal Reference Voltage           | Yes                                 | Yes                                 | Yes                                 |

|             | Interrupt Sources                    | 4                                   | 4                                   | 4                                   |

|             | I/O Pins                             | 13                                  | 13                                  | 13                                  |

|             | Voltage Range (Volts)                | 2.5-5.5                             | 2.5-5.5                             | 2.5-5.5                             |

| Features    | Brown-out Reset                      | Yes                                 | Yes                                 | Yes                                 |

|             | Packages                             | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP | 18-pin DIP,<br>SOIC;<br>20-pin SSOP |

All PIC<sup>®</sup> Family devices have Power-on Reset, selectable Watchdog Timer, selectable code protect and high I/O current capability. All PIC16CE62X Family devices use serial programming with clock pin RB6 and data pin RB7.

## FIGURE 3-1: BLOCK DIAGRAM

#### 4.2.2 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and peripheral functions for controlling the desired operation of the device (Table 4-1). These registers are static RAM. The special registers can be classified into two sets (core and peripheral). The Special Function Registers associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name          | Bit 7                  | Bit 6              | Bit 5       | Bit 4         | Bit 3        | Bit 2        | Bit 1        | Bit 0      | Value on<br>POR Reset | Value on all<br>other<br>resets <sup>(1)</sup> |

|---------|---------------|------------------------|--------------------|-------------|---------------|--------------|--------------|--------------|------------|-----------------------|------------------------------------------------|

| Bank 0  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 00h     | INDF          | Addressin<br>register) | ig this locat      | a physical  | xxxx xxxx     | xxxx xxxx    |              |              |            |                       |                                                |

| 01h     | TMR0          | Timer0 M               | odule's Reg        | jister      |               |              |              |              |            | xxxx xxxx             | uuuu uuuu                                      |

| 02h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          |              |              |            | 0000 0000             | 0000 0000                                      |

| 03h     | STATUS        | IRP <sup>(2)</sup>     | RP1 <sup>(2)</sup> | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 04h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | I            |              | I          | xxxx xxxx             | uuuu uuuu                                      |

| 05h     | PORTA         |                        |                    |             | RA4           | RA3          | RA2          | RA1          | RA0        | x 0000                | u 0000                                         |

| 06h     | PORTB         | RB7                    | RB6                | RB5         | RB4           | RB3          | RB2          | RB1          | RB0        | xxxx xxxx             | uuuu uuuu                                      |

| 07h     | Unimplemented |                        | 1                  |             | 1             |              | 1            |              | 1          | -                     | -                                              |

| 08h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 09h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | _                                              |

| 0Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 0Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 0Ch     | PIR1          | —                      | CMIF               | —           | —             | —            | —            | —            | —          | -0                    | -0                                             |

| 0Dh-1Eh | Unimplemented |                        |                    |             |               |              |              |              |            | —                     | _                                              |

| 1Fh     | CMCON         | C2OUT                  | C10UT              | _           |               | CIS          | CM2          | CM1          | CM0        | 00 0000               | 00 0000                                        |

| Bank 1  |               |                        |                    |             |               |              |              |              |            |                       |                                                |

| 80h     | INDF          | Addressin<br>register) | ig this locat      | ion uses co | ontents of F  | SR to addre  | ess data me  | emory (not a | a physical | xxxx xxxx             | xxxx xxxx                                      |

| 81h     | OPTION        | RBPU                   | INTEDG             | TOCS        | T0SE          | PSA          | PS2          | PS1          | PS0        | 1111 1111             | 1111 1111                                      |

| 82h     | PCL           | Program (              | Counter's (F       | PC) Least S | Significant B | yte          | 1            |              | 1          | 0000 0000             | 0000 0000                                      |

| 83h     | STATUS        | IRP                    | RP1                | RP0         | TO            | PD           | Z            | DC           | С          | 0001 1xxx             | 000q quuu                                      |

| 84h     | FSR           | Indirect da            | ata memory         | address p   | ointer        |              | 1            |              | 1          | xxxx xxxx             | uuuu uuuu                                      |

| 85h     | TRISA         | _                      |                    |             | TRISA4        | TRISA3       | TRISA2       | TRISA1       | TRISA0     | 1 1111                | 1 1111                                         |

| 86h     | TRISB         | TRISB7                 | TRISB6             | TRISB5      | TRISB4        | TRISB3       | TRISB2       | TRISB1       | TRISB0     | 1111 1111             | 1111 1111                                      |

| 87h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 88h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 89h     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Ah     | PCLATH        | _                      |                    | _           | Write buff    | er for upper | 5 bits of pr | ogram cou    | nter       | 0 0000                | 0 0000                                         |

| 8Bh     | INTCON        | GIE                    | PEIE               | TOIE        | INTE          | RBIE         | TOIF         | INTF         | RBIF       | 0000 000x             | 0000 000u                                      |

| 8Ch     | PIE1          | _                      | CMIE               | _           | —             | _            | —            | _            | —          | -0                    | -0                                             |

| 8Dh     | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 8Eh     | PCON          | —                      | —                  | —           | _             | —            | —            | POR          | BOD        | 0x                    | uq                                             |

| 8Fh-9Eh | Unimplemented |                        |                    |             |               |              |              |              |            | -                     | -                                              |

| 90h     | EEINTF        | —                      | —                  | —           | _             | —            | EESCL        | EESDA        | EEVDD      | 111                   | 111                                            |

| 9Fh     | VRCON         | VREN                   | VROE               | VRR         | _             | VR3          | VR2          | VR1          | VR0        | 000- 0000             | 000- 0000                                      |

#### TABLE 4-1: SPECIAL REGISTERS FOR THE PIC16CE62X

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

Note 1: Other (non power-up) resets include MCLR reset, Brown-out Reset and Watchdog Timer Reset during normal operation.

Note 2: IRP & RPI bits are reserved; always maintain these bits clear.

NOTES:

#### 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

## 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

### 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

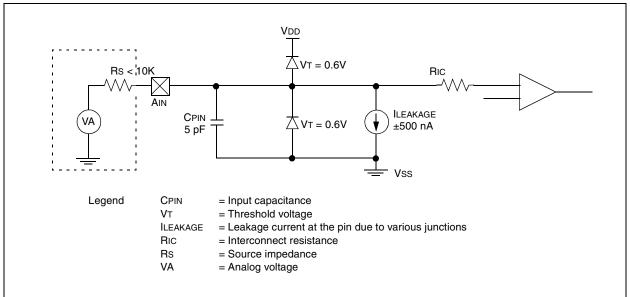

### 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

#### FIGURE 8-4: ANALOG INPUT MODEL

#### EXAMPLE 9-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x07        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | outputs        |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank 0   |

| CALL  | DELAY10     | ; | 10µs delay     |

#### 9.2 <u>Voltage Reference Accuracy/Error</u>

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 9-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 13-2.

#### 9.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

### 9.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

#### 9.5 <u>Connection Considerations</u>

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 9-2 shows an example buffering technique.

## VREF Nodule Voltage Reference Output Impedance

## FIGURE 9-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

Note 1: R is dependent upon the Voltage Reference Configuration VRCON<3:0> and VRCON<5>.

#### TABLE 9-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR / BOD | Value On<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000             | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000               | 00 0000                         |

| 85h     | TRISA | _     | _     |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                | 1 1111                          |

Legend: - = Unimplemented, read as "0"

## 10.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16CE62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-Up Timer (OST) Brown-out Reset (BOD)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

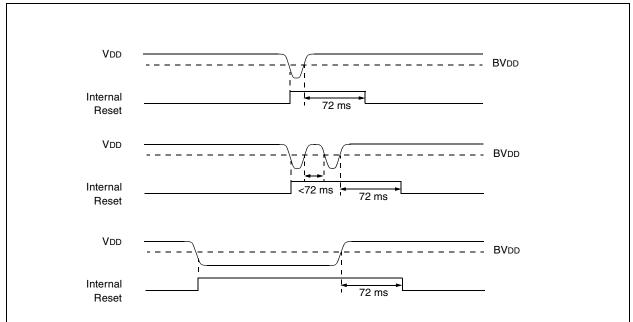

The PIC16CE62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, and is designed to keep the part in reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 10.4 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT), Oscillator Start-up</u> <u>Timer (OST) and Brown-out Reset</u> (BOD)

#### 10.4.1 POWER-ON RESET (POR)

The on-chip POR circuit holds the chip in reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, just tie the  $\overline{\text{MCLR}}$  pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See electrical specifications for details.

The POR circuit does not produce an internal reset when VDD declines.

When the device starts normal operation (exits the reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in reset until the operating conditions are met.

For additional information, refer to Application Note AN607, "Power-up Trouble Shooting".

#### 10.4.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 72 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates on an internal RC oscillator. The chip is kept in reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should always be enabled when Brown-out Reset is enabled.

The Power-Up Time delay will vary from chip-to-chip and due to VDD, temperature and process variation. See DC parameters for details.

#### 10.4.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-Up Timer (OST) provides a 1024 oscillator cycle (from OSC1 input) delay after the PWRT delay is over. This ensures that the crystal oscillator or resonator has started and stabilized.

The OST time-out is invoked only for XT, LP and HS modes and only on power-on reset or wake-up from SLEEP.

#### 10.4.4 BROWN-OUT RESET (BOD)

The PIC16CE62X members have on-chip Brown-out Reset circuitry. A configuration bit, BOREN, can disable (if clear/programmed) or enable (if set) the Brown-out Reset circuitry. If VDD falls below 4.0V (refer to BVDD parameter D005) for greater than parameter (TBOR) in Table 13-5, the brown-out situation will reset the chip. A reset won't occur if VDD falls below 4.0V for less than parameter (TBOR).

On any reset (Power-on, Brown-out, Watch-dog, etc.) the chip will remain in reset until VDD rises above BVDD. The Power-up Timer will then be invoked and will keep the chip in reset an additional 72 ms.

If VDD drops below BVDD while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above BVDD, the Power-Up Timer will execute a 72 ms reset. The Power-up Timer should always be enabled when Brown-out Reset is enabled. Figure 10-7 shows typical Brown-out situations.

#### FIGURE 10-7: BROWN-OUT SITUATIONS

#### 10.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit in the STATUS register is cleared, the  $\overline{TO}$  bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSS, with no external circuitry drawing current from the I/O pin, and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |

|-------|-------------------------------------------|

|       | by a WDT time-out does not drive MCLR     |

|       | pin low.                                  |

#### 10.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register can be used to determine the cause of device reset.  $\overline{PD}$ bit, which is set on power-up is cleared when SLEEP is invoked.  $\overline{TO}$  bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

| Note: | If the global interrupts are disabled (GIE is |

|-------|-----------------------------------------------|

|       | cleared), but any interrupt source has both   |

|       | its interrupt enable bit and the correspond-  |

|       | ing interrupt flag bits set, the device will  |

|       | immediately wake-up from sleep. The           |

|       | sleep instruction is completely executed.     |

The WDT is cleared when the device wakes-up from sleep, regardless of the source of wake-up.

|                                             |              |              | Q1   Q2   Q3   Q4                      | Q1 Q2 Q3 Q4                           | Q1 Q2 Q3 Q4 |

|---------------------------------------------|--------------|--------------|----------------------------------------|---------------------------------------|-------------|

|                                             |              |              | $\mathcal{A} \cup \cup \cup \cup \cup$ | $, \cup \cup \cup \cup$               |             |

| CLKOUT(4)                                   | -\           | /            | <u>\</u> /                             | \/                                    |             |

| INT pin                                     |              |              | ,<br>,<br>,                            | ı<br>I                                |             |

| INTF flag<br>(INTCON<1>)                    |              |              | Interrupt Latency                      | · · · · · · · · · · · · · · · · · · · |             |

|                                             |              |              | 1                                      | 1 · · · ·                             |             |

| GIE bit<br>(INTCON<7>)                      | Processor in | <br>         |                                        | I                                     |             |

|                                             | SLEEP        |              |                                        |                                       |             |

| INSTRUCTION FLOW                            |              |              |                                        |                                       |             |

| PC X PC X PC+1                              | PC+2         | PC+2         | X PC + 2                               | X 0004h                               | X 0005h     |

| Instruction { Inst(PC) = SLEEP Inst(PC + 1) | 1            | Inst(PC + 2) | 1<br>1<br>1                            | Inst(0004h)                           | Inst(0005h) |

| Instruction Inst(PC - 1) SLEEP              | 1            | Inst(PC + 1) | Dummy cycle                            | Dummy cycle                           | Inst(0004h) |

|                                             |              |              |                                        |                                       |             |

#### FIGURE 10-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**Note 1:** XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay does not occur for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

| BCF              | Bit Clear                                                                                        | f             |            |      |  |  |

|------------------|--------------------------------------------------------------------------------------------------|---------------|------------|------|--|--|

| Syntax:          | [ <i>label</i> ] BCF f,b                                                                         |               |            |      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                              |               |            |      |  |  |

| Operation:       | $0 \rightarrow (f < b;$                                                                          | >)            |            |      |  |  |

| Status Affected: | None                                                                                             |               |            |      |  |  |

| Encoding:        | 01                                                                                               | 00bb          | bfff       | ffff |  |  |

| Description:     | Bit 'b' in re                                                                                    | gister 'f' is | s cleared. |      |  |  |

| Words:           | 1                                                                                                |               |            |      |  |  |

| Cycles:          | 1                                                                                                |               |            |      |  |  |

| Example          | BCF                                                                                              | FLAG_         | REG, 7     |      |  |  |

|                  | BCF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |               |            |      |  |  |

| BTFSC            | Bit Test, Skip if Clear                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                                        |  |  |  |  |  |

| Operation:       | skip if $(f < b >) = 0$                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Encoding:        | 01 10bb bfff ffff                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', then the next<br>instruction is skipped.<br>If bit 'b' is '0', then the next instruction<br>fetched during the current instruction<br>execution is discarded, and a NOP is<br>executed instead, making this a<br>two-cycle instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| Cycles:          | 1(2)                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Example          | HERE BTFSC FLAG,1<br>FALSE GOTO PROCESS_CODE<br>TRUE •<br>•                                                                                                                                                                                                                |  |  |  |  |  |

|                  | Before Instruction<br>PC = address HERE                                                                                                                                                                                                                                    |  |  |  |  |  |

|                  | PC = address HERE<br>After Instruction<br>if FLAG<1> = 0,<br>PC = address TRUE<br>if FLAG<1>=1,<br>PC = address FALSE                                                                                                                                                      |  |  |  |  |  |

| BSF              | Bit Set f                                                                     |               |        |      |  |  |

|------------------|-------------------------------------------------------------------------------|---------------|--------|------|--|--|

| Syntax:          | [ <i>label</i> ] BSF f,b                                                      |               |        |      |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$           |               |        |      |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                                     |               |        |      |  |  |

| Status Affected: | None                                                                          |               |        |      |  |  |

| Encoding:        | 01                                                                            | 01bb          | bfff   | ffff |  |  |

| Description:     | Bit 'b' in re                                                                 | gister 'f' is | s set. |      |  |  |

| Words:           | 1                                                                             |               |        |      |  |  |

| Cycles:          | 1                                                                             |               |        |      |  |  |

| Example          | BSF                                                                           | FLAG_F        | REG, 7 |      |  |  |

|                  | Before Instruction<br>FLAG_REG = 0x0A<br>After Instruction<br>FLAG_REG = 0x8A |               |        |      |  |  |

## **13.0 ELECTRICAL SPECIFICATIONS**

#### Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40° to +125°C                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65° to +150°C                                      |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

| Voltage on VDD with respect to VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 to +7.0V                                         |

| Voltage on RA4 with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.5V                                               |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 to +14V                                          |

| Voltage on RA4 with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

| Total power Dissipation (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0W                                               |

| Maximum Current out of Vss pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| Maximum Current into VDD pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 250 mA                                             |

| Input Clamp Current, Iк (Vi <0 or Vi> VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ±20 mA                                             |

| Output Clamp Current, IOK (Vo <0 or Vo>VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ±20 mA                                             |

| Maximum Output Current sunk by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 mA                                              |

| Maximum Output Current sourced by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 mA                                              |

| Maximum Current sunk by PORTA and PORTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 200 mA                                             |

| Maximum Current sourced by PORTA and PORTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 200 mA                                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - } \sum | $x \text{ IOH} + \sum (\text{VOI } x \text{ IOL})$ |

2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100<sup>3</sup>/<sub>4</sub> should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 13.1 DC CHARACTERISTICS:

#### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended)

| DC CHARACTERISTICS |                           |                                                                        |       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |           |            |                                                                   |  |  |

|--------------------|---------------------------|------------------------------------------------------------------------|-------|------------------------------------------------------|-----------|------------|-------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym                       | Characteristic                                                         | Min   | Тур†                                                 | Max       | Units      | Conditions                                                        |  |  |

| D001               | Vdd                       | Supply Voltage                                                         | 3.0   | -                                                    | 5.5       | V          | See Figure 13-1 through Figure 13-3                               |  |  |

| D002               | Vdr                       | RAM Data Retention<br>Voltage (Note 1)                                 | -     | 1.5*                                                 | -         | V          | Device in SLEEP mode                                              |  |  |

| D003               | VPOR                      | VDD start voltage to<br>ensure Power-on Reset                          | -     | Vss                                                  | -         | V          | See section on power-on reset for details                         |  |  |

| D004               | SVDD                      | VDD rise rate to ensure<br>Power-on Reset                              | 0.05* | -                                                    | -         | V/ms       | See section on power-on reset for details                         |  |  |

| D005               | VBOR                      | Brown-out Detect Voltage                                               | 3.7   | 4.0                                                  | 4.35      | V          | BOREN configuration bit is cleared                                |  |  |

| D010               | IDD                       | Supply Current (Note 2, 4)                                             | -     | 1.2                                                  | 2.0       | mA         | Fosc = 4 MHz, VDD = 5.5V, WDT disabled,<br>XT osc mode, (Note 4)* |  |  |

|                    |                           |                                                                        | -     | 0.4                                                  | 1.2       | mA         | Fosc = 4 MHz, VDD = 3.0V, WDT disabled,<br>XT osc mode, (Note 4)  |  |  |

|                    |                           |                                                                        | -     | 1.0                                                  | 2.0       | mA         | Fosc = 10 MHz, VDD = 3.0V, WDT disabled,<br>HS osc mode, (Note 6) |  |  |

|                    |                           |                                                                        | -     | 4.0                                                  | 6.0       | mA         | Fosc = 20 MHz, VDD = 4.5V, WDT disabled,<br>HS osc mode           |  |  |

|                    |                           |                                                                        | -     | 4.0                                                  | 7.0       | mA         | Fosc = 20 MHz, VDD = 5.5V, WDT disabled*,<br>HS osc mode          |  |  |

|                    |                           |                                                                        | -     | 35                                                   | 70        | μA         | Fosc = 32 kHz, VDD = 3.0V, WDT disabled,<br>LP osc mode           |  |  |

| D020               | IPD                       | Power Down Current (Note 3)                                            | -     | -                                                    | 2.2       | μA         | VDD = 3.0V                                                        |  |  |

|                    |                           |                                                                        | -     | -                                                    | 5.0       | μA         | VDD = 4.5V*                                                       |  |  |

|                    |                           |                                                                        | _     | _                                                    | 9.0<br>15 | μΑ<br>μΑ   | VDD = 5.5V<br>VDD = 5.5V Extended                                 |  |  |

| D022               | ΔIWDT                     | WDT Current (Note 5)                                                   | _     | 6.0                                                  | 10        | μΑ         | VDD = 4.0V                                                        |  |  |

| 2022               |                           |                                                                        |       | 0.0                                                  | 12        | μA         | (125°C)                                                           |  |  |

| D022A              | $\Delta$ IBOR             | Brown-out Reset Current (Note 5)                                       | -     | 75                                                   | 125       | μA         | $\overline{\text{BOD}}$ enabled, VDD = 5.0V                       |  |  |

| D023               | ∆ICOMP                    | Comparator Current for each<br>Comparator (Note 5)                     | -     | 30                                                   | 60        | μA         | VDD = 4.0V                                                        |  |  |

| D023A              | $\Delta$ IVREF            | VREF Current (Note 5)                                                  | -     | 80                                                   | 135       | μA         | VDD = 4.0V                                                        |  |  |

|                    | $\Delta \text{IEE Write}$ | Operating Current                                                      | -     |                                                      | 3         | mA         | Vcc = 5.5V, SCL = 400 kHz                                         |  |  |

|                    | $\Delta$ IEE Read         | Operating Current                                                      | -     |                                                      | 1         | mA         |                                                                   |  |  |

|                    | ΔIEE                      | Standby Current                                                        | -     |                                                      | 30        | μA         | $V_{CC} = 3.0V, EE V_{DD} = V_{CC}$                               |  |  |

|                    | ΔIEE                      | Standby Current                                                        | -     |                                                      | 100       | μ <b>Α</b> | Vcc = 3.0V, EE VDD = Vcc                                          |  |  |

| 1A                 | Fosc                      | LP Oscillator Operating Frequency                                      | 0     | -                                                    | 200       | kHz        | All temperatures                                                  |  |  |

|                    |                           | RC Oscillator Operating Frequency                                      | 0     | -                                                    | 4         | MHz<br>MHz | All temperatures                                                  |  |  |

|                    |                           | XT Oscillator Operating Frequency<br>HS Oscillator Operating Frequency | 0     | _                                                    | 4<br>20   | MHZ        | All temperatures<br>All temperatures                              |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C, unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tri-stated, pulled to VDD,

$\overline{MCLR} = VDD$ ; WDT enabled/disabled as specified.

3: The power down current in SLEEP mode does not depend on the oscillator type. Power down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in k $\Omega$ .

5: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

**6:** Commercial temperature range only.

#### 13.3 DC CHARACTERISTICS:

#### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended) PIC16LCE62X (Commercial, Industrial)

|                         |       |                                | Standard Opera                                            | ating (                                                        | Conditions (u   | Inles | s otherwise stated)                                                                                                |  |  |  |  |  |

|-------------------------|-------|--------------------------------|-----------------------------------------------------------|----------------------------------------------------------------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                         |       |                                |                                                           |                                                                |                 |       | +85°C for industrial and                                                                                           |  |  |  |  |  |

| DC CHARACTERISTICS      |       |                                | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial and |                                                                |                 |       |                                                                                                                    |  |  |  |  |  |

|                         |       |                                |                                                           |                                                                | -40°C ≤         | TA≤   | +125°C for extended                                                                                                |  |  |  |  |  |

|                         |       |                                | Operating voltag                                          | Operating voltage VDD range as described in DC spec Table 13-1 |                 |       |                                                                                                                    |  |  |  |  |  |

| Parm Sym Characteristic |       |                                | Min                                                       | Typ†                                                           | Max             | Unit  | Conditions                                                                                                         |  |  |  |  |  |

| No.                     |       |                                |                                                           |                                                                |                 |       |                                                                                                                    |  |  |  |  |  |

|                         | Vi∟   | Input Low Voltage              |                                                           |                                                                |                 |       |                                                                                                                    |  |  |  |  |  |

|                         |       | I/O ports                      |                                                           |                                                                |                 |       |                                                                                                                    |  |  |  |  |  |

| D030                    |       | with TTL buffer                | Vss                                                       | -                                                              | 0.8V<br>0.15Vdd | v     | VDD = 4.5V to 5.5V, Otherwise                                                                                      |  |  |  |  |  |

| D031                    |       | with Schmitt Trigger input     | Vss                                                       |                                                                | 0.2VDD          | v     |                                                                                                                    |  |  |  |  |  |

| D032                    |       | MCLR, RA4/T0CKI,OSC1 (in RC    | Vss                                                       | _                                                              | 0.2VDD          | V     | Note1                                                                                                              |  |  |  |  |  |

|                         |       | mode)                          |                                                           |                                                                |                 | -     |                                                                                                                    |  |  |  |  |  |

| D033                    |       | OSC1 (in XT and HS)            | Vss                                                       | _                                                              | 0.3VDD          | v     |                                                                                                                    |  |  |  |  |  |

|                         |       | OSC1 (in LP)                   | Vss                                                       | -                                                              | 0.6Vdd - 1.0    | V     |                                                                                                                    |  |  |  |  |  |

|                         | Vih   | Input High Voltage             |                                                           |                                                                |                 |       |                                                                                                                    |  |  |  |  |  |

|                         |       | I/O ports                      |                                                           |                                                                |                 |       |                                                                                                                    |  |  |  |  |  |

| D040                    |       | with TTL buffer                | 2.0V                                                      | -                                                              | Vdd             | V     | VDD = 4.5V to 5.5V, Otherwise                                                                                      |  |  |  |  |  |