Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                             |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 96 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            |                                                                              |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce624-04i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

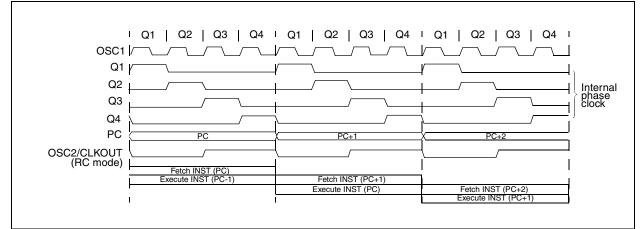

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

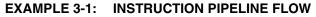

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

#### 4.0 MEMORY ORGANIZATION

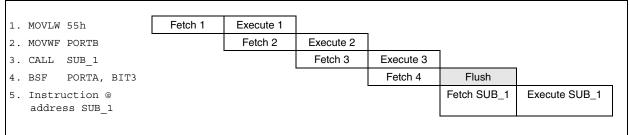

#### 4.1 <u>Program Memory Organization</u>

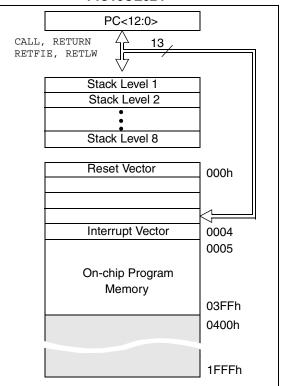

The PIC16CE62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16CE623, 1K x 14 (0000h - 03FFh) for the PIC16CE624 and 2K x 14 (0000h - 07FFh) for the PIC16CE625 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16CE623) or 1K x 14 space (PIC16CE624) or 2K x 14 space (PIC16CE625). The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE623

#### FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE624

#### FIGURE 4-3: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE625

#### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

#### REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1    | R/W-1                                                                                                                                                                             | R/W-1                                                       | R/W-1        | R/W-1      | R/W-1                  | R/W-1 | R/W-1 |                                                                                                                   |  |  |  |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------|------------|------------------------|-------|-------|-------------------------------------------------------------------------------------------------------------------|--|--|--|

| RBPU     | INTEDG                                                                                                                                                                            | TOCS                                                        | TOSE         | PSA        | PS2                    | PS1   | PS0   | R = Readable bit                                                                                                  |  |  |  |

| bit7     |                                                                                                                                                                                   |                                                             |              |            |                        |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |  |  |  |

| bit 7:   | <ul> <li>bit 7: <b>RBPU</b>: PORTB Pull-up Enable bit</li> <li>1 = PORTB pull-ups are disabled</li> <li>0 = PORTB pull-ups are enabled by individual port latch values</li> </ul> |                                                             |              |            |                        |       |       |                                                                                                                   |  |  |  |

| bit 6:   | INTEDG: In<br>1 = Interrup<br>0 = Interrup                                                                                                                                        | ot on rising                                                | g edge o     | f RB0/INT  |                        |       |       |                                                                                                                   |  |  |  |

| bit 5:   | <b>TOCS</b> : TMF<br>1 = Transiti<br>0 = Interna                                                                                                                                  | ion on RA                                                   | 4/T0CKI      | pin        | (OUT)                  |       |       |                                                                                                                   |  |  |  |

| bit 4:   |                                                                                                                                                                                   | ent on hig                                                  | h-to-low     | transition | on RA4/T0<br>on RA4/T0 |       |       |                                                                                                                   |  |  |  |

| bit 3:   | <b>PSA</b> : Prese<br>1 = Presca<br>0 = Presca                                                                                                                                    | ler is assi                                                 | gned to t    | he WDT     | ) module               |       |       |                                                                                                                   |  |  |  |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : F                                                                                                                                                          | Prescaler I                                                 | Rate Sele    | ect bits   |                        |       |       |                                                                                                                   |  |  |  |

|          | Bit Value                                                                                                                                                                         | TMR0 Ra                                                     | te WD1       | Γ Rate     |                        |       |       |                                                                                                                   |  |  |  |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111                                                                                                                              | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 :<br>3 1 : | 2<br>4     |                        |       |       |                                                                                                                   |  |  |  |

NOTES:

#### 5.0 I/O PORTS

The PIC16CE62X parts have two ports, PORTA and PORTB. Some pins for these I/O ports are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general purpose I/O pin.

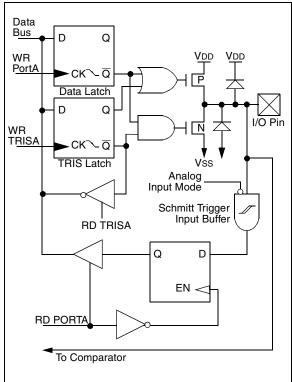

#### 5.1 PORTA and TRISA Registers

PORTA is a 5-bit wide latch. RA4 is a Schmitt Trigger input and an open drain output. Port RA4 is multiplexed with the TOCKI clock input. All other RA port pins have Schmitt Trigger input levels and full CMOS output drivers. All pins have data direction bits (TRIS registers), which can configure these pins as input or output.

A '1' in the TRISA register puts the corresponding output driver in a hi- impedance mode. A '0' in the TRISA register puts the contents of the output latch on the selected pin(s).

Reading the PORTA register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

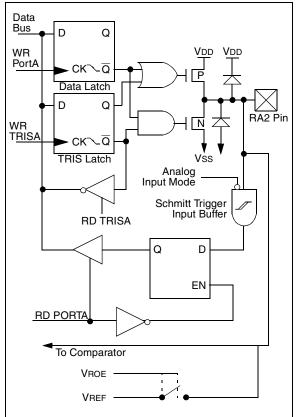

The PORTA pins are multiplexed with comparator and voltage reference functions. The operation of these pins are selected by control bits in the CMCON (Comparator Control Register) register and the VRCON (Voltage Reference Control Register) register. When selected as a comparator input, these pins will read as '0's.

#### FIGURE 5-1: BLOCK DIAGRAM OF RA<1:0> PINS

| Note: | On reset, the TRISA register is set to all  |

|-------|---------------------------------------------|

|       | inputs. The digital inputs are disabled and |

|       | the comparator inputs are forced to ground  |

|       | to reduce excess current consumption.       |

TRISA controls the direction of the RA pins, even when they are being used as comparator inputs. The user must make sure to keep the pins configured as inputs when using them as comparator inputs.

The RA2 pin will also function as the output for the voltage reference. When in this mode, the VREF pin is a very high impedance output. The user must configure TRISA<2> bit as an input and use high impedance loads.

In one of the comparator modes defined by the CMCON register, pins RA3 and RA4 become outputs of the comparators. The TRISA<4:3> bits must be cleared to enable outputs to use this function.

#### **EXAMPLE 5-1: INITIALIZING PORTA**

| CLRF  | PORTA   |     | ;Initialize PORTA by setting ;output data latches |

|-------|---------|-----|---------------------------------------------------|

| MOVLW | 0X07    |     | ;Turn comparators off and                         |

| MOVWF | CMCON   |     | ;enable pins for I/O                              |

|       |         |     | ;functions                                        |

| BSF   | STATUS, | RP0 | ;Select Bank1                                     |

| MOVLW | 0x1F    |     | ;Value used to initialize                         |

|       |         |     | ;data direction                                   |

| MOVWF | TRISA   |     | ;Set RA<4:0> as inputs                            |

|       |         |     | ;TRISA<7:5> are always                            |

|       |         |     | ;read as '0'.                                     |

#### FIGURE 5-2: BLOCK DIAGRAM OF RA2 PIN

<sup>© 1998-2013</sup> Microchip Technology Inc.

#### EXAMPLE 9-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x07        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | outputs        |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank 0   |

| CALL  | DELAY10     | ; | 10µs delay     |

#### 9.2 <u>Voltage Reference Accuracy/Error</u>

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 9-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 13-2.

#### 9.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

#### 9.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

#### 9.5 <u>Connection Considerations</u>

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 9-2 shows an example buffering technique.

### VREF Nodule Voltage Reference Output Impedance

#### FIGURE 9-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

Note 1: R is dependent upon the Voltage Reference Configuration VRCON<3:0> and VRCON<5>.

#### TABLE 9-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR / BOD | Value On<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000             | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000               | 00 0000                         |

| 85h     | TRISA | _     | _     |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                | 1 1111                          |

Legend: - = Unimplemented, read as "0"

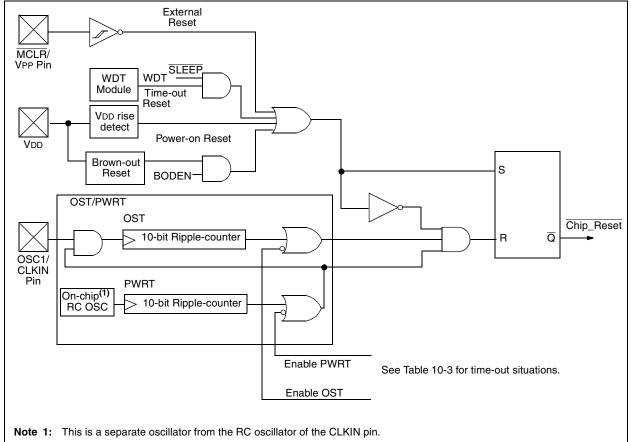

#### 10.3 <u>Reset</u>

The PIC16CE62X differentiates between various kinds of reset:

- a) Power-on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOD)

Some registers are not affected in any reset condition. Their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on reset, MCLR reset, WDT reset and MCLR reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different reset situations as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-6.

The  $\overline{\text{MCLR}}$  reset path has a noise filter to detect and ignore small pulses. See Table 13-5 for pulse width specification.

#### FIGURE 10-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

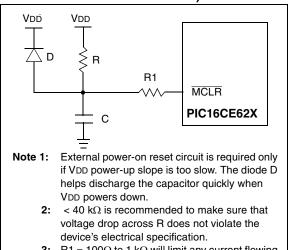

#### FIGURE 10-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

**3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

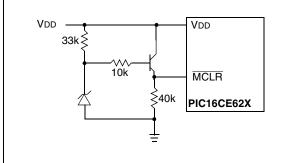

#### FIGURE 10-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal Brown-out Reset circuitry should be disabled when using this circuit.

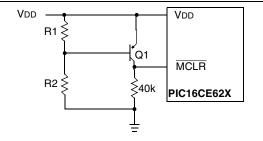

#### FIGURE 10-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \times \frac{R1}{R1 + R2} = 0.7 V$$

- **2:** Internal brown-out detection should be disabled when using this circuit.

- **3:** Resistors should be adjusted for the characteristics of the transistor.

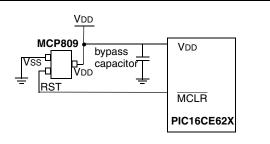

#### FIGURE 10-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

#### TABLE 11-2: PIC16CE62X INSTRUCTION SET

| Mnemonic,  |         | Description                  |       |     | 14-Bit | e    | Status | Notes    |      |

|------------|---------|------------------------------|-------|-----|--------|------|--------|----------|------|

| Operands   |         |                              |       | MSb |        |      | LSb    | Affected |      |

| BYTE-ORIE  | NTED    | FILE REGISTER OPERATIONS     |       |     |        |      |        |          |      |

| ADDWF      | f, d    | Add W and f                  | 1     | 00  | 0111   | dfff | ffff   | C,DC,Z   | 1,2  |

| ANDWF      | f, d    | AND W with f                 | 1     | 00  | 0101   | dfff | ffff   | Z        | 1,2  |

| CLRF       | f       | Clear f                      | 1     | 00  | 0001   | lfff | ffff   | Z        | 2    |

| CLRW       | -       | Clear W                      | 1     | 00  | 0001   | 0000 | 0011   | Z        |      |

| COMF       | f, d    | Complement f                 | 1     | 00  | 1001   | dfff | ffff   | Z        | 1,2  |

| DECF       | f, d    | Decrement f                  | 1     | 00  | 0011   | dfff | ffff   | Z        | 1,2  |

| DECFSZ     | f, d    | Decrement f, Skip if 0       | 1(2)  | 00  | 1011   | dfff | ffff   |          | 1,2, |

| INCF       | f, d    | Increment f                  | 1     | 00  | 1010   | dfff | ffff   | Z        | 1,2  |

| INCFSZ     | f, d    | Increment f, Skip if 0       | 1(2)  | 00  | 1111   | dfff | ffff   |          | 1,2, |

| IORWF      | f, d    | Inclusive OR W with f        | 1     | 00  | 0100   | dfff | ffff   | Z        | 1,2  |

| MOVF       | f, d    | Move f                       | 1     | 00  | 1000   | dfff | ffff   | Z        | 1,2  |

| MOVWF      | f       | Move W to f                  | 1     | 00  | 0000   | lfff | ffff   |          |      |

| NOP        | -       | No Operation                 | 1     | 00  | 0000   | 0xx0 | 0000   |          |      |

| RLF        | f, d    | Rotate Left f through Carry  | 1     | 00  | 1101   | dfff | ffff   | С        | 1,2  |

| RRF        | f, d    | Rotate Right f through Carry | 1     | 00  | 1100   | dfff | ffff   | С        | 1,2  |

| SUBWF      | f, d    | Subtract W from f            | 1     | 00  | 0010   | dfff | ffff   | C,DC,Z   | 1,2  |

| SWAPF      | f, d    | Swap nibbles in f            | 1     | 00  | 1110   | dfff | ffff   |          | 1,2  |

| XORWF      | f, d    | Exclusive OR W with f        | 1     | 00  | 0110   | dfff | ffff   | Z        | 1,2  |

| BIT-ORIENT | FED FIL | E REGISTER OPERATIONS        |       |     |        |      |        | •        |      |

| BCF        | f, b    | Bit Clear f                  | 1     | 01  | 00bb   | bfff | ffff   |          | 1,2  |

| BSF        | f, b    | Bit Set f                    | 1     | 01  | 01bb   | bfff | ffff   |          | 1,2  |

| BTFSC      | f, b    | Bit Test f, Skip if Clear    | 1 (2) | 01  | 10bb   | bfff | ffff   |          | 3    |

| BTFSS      | f, b    | Bit Test f, Skip if Set      | 1 (2) | 01  | 11bb   | bfff | ffff   |          | 3    |

| LITERAL A  | ND CO   | NTROL OPERATIONS             |       |     |        |      |        |          |      |

| ADDLW      | k       | Add literal and W            | 1     | 11  | 111x   | kkkk | kkkk   | C,DC,Z   |      |

| ANDLW      | k       | AND literal with W           | 1     | 11  | 1001   | kkkk | kkkk   | Z        |      |

| CALL       | k       | Call subroutine              | 2     | 10  | 0kkk   | kkkk | kkkk   |          |      |

| CLRWDT     | -       | Clear Watchdog Timer         | 1     | 00  | 0000   | 0110 | 0100   | TO,PD    |      |

| GOTO       | k       | Go to address                | 2     | 10  | 1kkk   | kkkk | kkkk   |          |      |

| IORLW      | k       | Inclusive OR literal with W  | 1     | 11  | 1000   | kkkk | kkkk   | Z        |      |

| MOVLW      | k       | Move literal to W            | 1     | 11  | 00xx   | kkkk | kkkk   |          |      |

| RETFIE     | -       | Return from interrupt        | 2     | 00  | 0000   | 0000 | 1001   |          |      |

| RETLW      | k       | Return with literal in W     | 2     | 11  | 01xx   | kkkk | kkkk   |          |      |

| RETURN     | -       | Return from Subroutine       | 2     | 00  | 0000   | 0000 | 1000   |          |      |

|            | -       | Go into standby mode         | 1     | 00  | 0000   | 0110 | 0011   | TO,PD    |      |

| SLEEP      |         |                              |       | 1   |        |      |        |          | 1    |

| SUBLW      | k       | Subtract W from literal      | 1     | 11  | 110x   | kkkk | kkkk   | C,DC,Z   |      |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| GOTO                              | Unconditional Branch                                                                                                                                                                               | INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                         |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                           | [ <i>label</i> ] GOTO k                                                                                                                                                                            | Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                    |

| Operands:                         | $0 \le k \le 2047$                                                                                                                                                                                 | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                              |

| Operation:                        | $k \rightarrow PC < 10:0 >$                                                                                                                                                                        |                  | d ∈ [0,1]                                                                                                                                                                                                                                                                                                                      |

|                                   | $PCLATH<4:3> \rightarrow PC<12:11>$                                                                                                                                                                | Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected:                  | None                                                                                                                                                                                               | Status Affected: | None                                                                                                                                                                                                                                                                                                                           |

| Encoding:                         | 10 1kkk kkkk kkkk                                                                                                                                                                                  | Encoding:        | 00 1111 dfff ffff                                                                                                                                                                                                                                                                                                              |

| Description:<br>Words:<br>Cycles: | GOTO is an unconditional branch. The<br>eleven bit immediate value is loaded<br>into PC bits <10:0>. The upper bits of<br>PC are loaded from PCLATH<4:3>.<br>GOTO is a two-cycle instruction.<br>1 | Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'.<br>If the result is 0, the next instruction,<br>which is already fetched, is discarded.<br>A NOP is executed instead making it a<br>two-cycle instruction. |

| Example                           | GOTO THERE                                                                                                                                                                                         | Words:           | 1                                                                                                                                                                                                                                                                                                                              |

|                                   | After Instruction<br>PC = Address THERE                                                                                                                                                            | Cycles:          | 1(2)                                                                                                                                                                                                                                                                                                                           |

|                                   | FC = Addless There                                                                                                                                                                                 | Example          | HERE INCFSZ CNT, 1<br>GOTO LOOP                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                    |                  | CONTINUE •<br>•                                                                                                                                                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                    |                  | •                                                                                                                                                                                                                                                                                                                              |

$\begin{array}{rcl} Before \ Instruction \\ PC & = & address \ {\tt HERE} \\ After \ Instruction \\ CNT & = & CNT + 1 \\ if \ CNT = & 0, \\ PC & = & address \ CONTINUE \\ if \ CNT \neq & 0, \\ PC & = & address \ {\tt HERE} \ +1 \end{array}$

| INCF             | Increment f                                                                                                                                                         |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                    |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                         |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                   |  |  |  |  |  |

| Encoding:        | 00 1010 dfff ffff                                                                                                                                                   |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is 0, the result is<br>placed in the W register. If 'd' is 1, the<br>result is placed back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                   |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                   |  |  |  |  |  |

| Example          | INCF CNT, 1                                                                                                                                                         |  |  |  |  |  |

|                  | Before Instruction<br>CNT = 0xFF<br>Z = 0<br>After Instruction<br>CNT = 0x00<br>Z = 1                                                                               |  |  |  |  |  |

| IORLW            | Inclusive OR Literal with W                                                                                            |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                               |

| Operands:        | $0 \le k \le 255$                                                                                                      |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                           |

| Status Affected: | Z                                                                                                                      |

| Encoding:        | 11 1000 kkkk kkkk                                                                                                      |

| Description:     | The contents of the W register are<br>OR'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:           | 1                                                                                                                      |

| Cycles:          | 1                                                                                                                      |

| Example          | IORLW 0x35                                                                                                             |

|                  | Before Instruction<br>W = 0x9A<br>After Instruction<br>W = 0xBF<br>Z = 1                                               |

| SWAPF            | Swap Nibbles in f                                                                                                                                                       | XORLW                          | Exclusive OR Literal with W                                                               |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                       | Syntax:                        | [ <i>label</i> ] XORLW k                                                                  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                       | Operands:                      | 0 ≤ k ≤ 255                                                                               |  |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>),$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                               | Operation:<br>Status Affected: | (W) .XOR. $k \rightarrow (W)$                                                             |  |  |  |  |

| Status Affected: | None                                                                                                                                                                    | Encoding:                      | 11 1010 kkkk kkkk                                                                         |  |  |  |  |

| Encoding:        | 00 1110 dfff ffff                                                                                                                                                       | Description:                   | The contents of the W register are                                                        |  |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0,<br>the result is placed in W register. If 'd'<br>is 1, the result is placed in register 'f'. | Words:                         | XOR'ed with the eight bit literal 'k'.<br>The result is placed in the<br>W register.<br>1 |  |  |  |  |

| Words:           | 1                                                                                                                                                                       | Cycles:                        | 1                                                                                         |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                       | Example:                       | XORLW 0xAF                                                                                |  |  |  |  |

| Example          | SWAPF REG, 0                                                                                                                                                            |                                | Before Instruction                                                                        |  |  |  |  |

| ·                | Before Instruction                                                                                                                                                      |                                | W = 0xB5                                                                                  |  |  |  |  |

|                  | REG1 = 0xA5                                                                                                                                                             |                                | After Instruction                                                                         |  |  |  |  |

|                  | After Instruction                                                                                                                                                       |                                | W = 0x1A                                                                                  |  |  |  |  |

|                  | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$                                                                                                             |                                |                                                                                           |  |  |  |  |

| TRIS                              | Load TR                                                                                                                                                                              | Load TRIS Register |          |      |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|------|--|--|--|--|

| Syntax:                           | [ label ]                                                                                                                                                                            | TRIS               | f        |      |  |  |  |  |

| Operands:                         | $5 \leq f \leq 7$                                                                                                                                                                    |                    |          |      |  |  |  |  |

| Operation:                        | $(W) \rightarrow TF$                                                                                                                                                                 | RIS regis          | ster f;  |      |  |  |  |  |

| Status Affected:                  | None                                                                                                                                                                                 |                    |          |      |  |  |  |  |

| Encoding:                         | 0 0                                                                                                                                                                                  | 0000               | 0110     | Offf |  |  |  |  |

| Description:<br>Words:<br>Cycles: | The instruction is supported for code<br>compatibility with the PIC16C5X<br>products. Since TRIS registers are<br>readable and writable, the user can<br>directly address them.<br>1 |                    |          |      |  |  |  |  |

| Example                           |                                                                                                                                                                                      |                    |          |      |  |  |  |  |

|                                   |                                                                                                                                                                                      | -                  | rd compa | -    |  |  |  |  |

|                                   | with future PIC <sup>®</sup> MCU products, do not use this instruction.                                                                                                              |                    |          |      |  |  |  |  |

|                                   |                                                                                                                                                                                      |                    |          |      |  |  |  |  |

|                                   |                                                                                                                                                                                      |                    |          |      |  |  |  |  |

| XORWF            | Exclusiv                                                        | e OR W                    | with 1               | f            |  |  |  |

|------------------|-----------------------------------------------------------------|---------------------------|----------------------|--------------|--|--|--|

| Syntax:          | [ label ]                                                       | XORWF                     | f,d                  |              |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$ |                           |                      |              |  |  |  |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                              |                           |                      |              |  |  |  |

| Status Affected: | Z                                                               |                           |                      |              |  |  |  |

| Encoding:        | 0 0                                                             | 0110                      | dfff                 | f fff        |  |  |  |

| Description:     |                                                                 | with regis<br>s stored ir | ster 'f'.<br>n the V |              |  |  |  |

| Words:           | 1                                                               |                           |                      |              |  |  |  |

| Cycles:          | 1                                                               |                           |                      |              |  |  |  |

| Example          | XORWF                                                           | REG                       | 1                    |              |  |  |  |

|                  | Before In                                                       | struction                 |                      |              |  |  |  |

|                  |                                                                 | REG<br>W                  | =<br>=               | 0xAF<br>0xB5 |  |  |  |

|                  | After Inst                                                      | ruction                   |                      |              |  |  |  |

|                  |                                                                 | REG<br>W                  | =<br>=               | 0x1A<br>0xB5 |  |  |  |

stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

#### 12.11 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PIC devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

#### 12.12 <u>SIMICE Entry-Level</u> <u>Hardware Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB-SIM. Both SIMICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PIC 8-bit microcontrollers. SIM-ICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entry-level system development.

#### 12.13 <u>PICDEM-1 Low-Cost PIC MCU</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

#### 12.14 PICDEM-2 Low-Cost PIC16CXX Demonstration Board

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

#### 12.15 <u>PICDEM-3 Low-Cost PIC16CXXX</u> <u>Demonstration Board</u>

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

#### 12.16 PICDEM-17

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756, PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug

#### 13.3 DC CHARACTERISTICS:

#### PIC16CE62X-04 (Commercial, Industrial, Extended) PIC16CE62X-20 (Commercial, Industrial, Extended) PIC16LCE62X (Commercial, Industrial)

|                                                                |       |                                                                 | Standard Opera                                       | ating ( | Conditions (u | unles | s otherwise stated)                             |  |  |

|----------------------------------------------------------------|-------|-----------------------------------------------------------------|------------------------------------------------------|---------|---------------|-------|-------------------------------------------------|--|--|

|                                                                |       |                                                                 |                                                      |         |               |       | +85°C for industrial and                        |  |  |

| DC CH                                                          | IARAC | TERISTICS                                                       |                                                      |         | 0°C ≤         | TA≤   | +70°C for commercial and                        |  |  |

|                                                                |       |                                                                 | $-40^{\circ}$ C $\leq$ TA $\leq$ +125°C for extended |         |               |       |                                                 |  |  |

| Operating voltage VDD range as described in DC spec Table 13-1 |       |                                                                 |                                                      |         |               |       |                                                 |  |  |

| Parm                                                           | Sym   | Characteristic                                                  | Min Typ† Max Unit                                    |         | Conditions    |       |                                                 |  |  |

| No.                                                            |       |                                                                 |                                                      |         |               |       |                                                 |  |  |

|                                                                | Vi∟   | Input Low Voltage                                               |                                                      |         |               |       |                                                 |  |  |

|                                                                |       | I/O ports                                                       |                                                      |         |               |       |                                                 |  |  |

| D030                                                           |       | with TTL buffer                                                 | Vss                                                  | _       | 0.8V          | v     | VDD = 4.5V to 5.5V, Otherwise                   |  |  |

|                                                                |       |                                                                 |                                                      |         | 0.15VDD       |       |                                                 |  |  |

| D031                                                           |       | with Schmitt Trigger input                                      | Vss                                                  |         | 0.2VDD        | V     |                                                 |  |  |

| D032                                                           |       | MCLR, RA4/T0CKI,OSC1 (in RC                                     | Vss                                                  | -       | 0.2VDD        | V     | Note1                                           |  |  |

|                                                                |       | mode)                                                           |                                                      |         |               |       |                                                 |  |  |

| D033                                                           |       | OSC1 (in XT and HS)                                             | Vss                                                  | -       | 0.3Vdd        | V     |                                                 |  |  |

|                                                                |       | OSC1 (in LP)                                                    | Vss                                                  | -       | 0.6VDD - 1.0  | V     |                                                 |  |  |

|                                                                | VIH   | Input High Voltage                                              |                                                      |         |               |       |                                                 |  |  |

|                                                                |       | I/O ports                                                       |                                                      |         |               |       |                                                 |  |  |

| D040                                                           |       | with TTL buffer                                                 | 2.0V                                                 | -       | VDD           | V     | VDD = 4.5V to 5.5V, Otherwise                   |  |  |

| <b>D</b> 044                                                   |       |                                                                 | .25VDD + 0.8V                                        |         | VDD           |       |                                                 |  |  |

| D041                                                           |       | with Schmitt Trigger input                                      | 0.8VDD                                               |         | VDD           |       |                                                 |  |  |

| D042                                                           |       | MCLR RA4/T0CKI                                                  | 0.8VDD                                               | -       | VDD           | V     |                                                 |  |  |

| D043<br>D043A                                                  |       | OSC1 (XT, HS and LP)                                            | 0.7Vdd<br>0.9Vdd                                     | -       | Vdd           | V     | Note1                                           |  |  |

| D043A                                                          | IPURB | OSC1 (in RC mode)<br>PORTB weak pull-up current                 | 50                                                   | 200     | 400           | μA    | VDD = 5.0V, VPIN = VSS                          |  |  |

| 0070                                                           | IPUND | Input Leakage Current                                           | 50                                                   | 200     | 400           | μΑ    | VDD = 5.0V, VPIN = V35                          |  |  |

|                                                                | lı∟   | (Notes 2, 3)                                                    |                                                      |         |               |       |                                                 |  |  |

|                                                                |       | I/O ports (Except PORTA)                                        |                                                      |         | ±1.0          | μА    | VSS $\leq$ VPIN $\leq$ VDD, pin at hi-impedance |  |  |

| D060                                                           |       | PORTA                                                           | _                                                    | _       | ±0.5          | μA    |                                                 |  |  |

| D061                                                           |       | RA4/T0CKI                                                       | _                                                    | _       | ±1.0          | μA    |                                                 |  |  |

| D063                                                           |       | OSC1, MCLR                                                      | _                                                    | _       | ±5.0          | μA    |                                                 |  |  |

|                                                                |       |                                                                 |                                                      |         |               | · ·   | configuration                                   |  |  |

|                                                                | Vol   | Output Low Voltage                                              |                                                      |         |               |       |                                                 |  |  |

| D080                                                           |       | I/O ports                                                       | _                                                    | _       | 0.6           | v     | IOL=8.5 mA, VDD=4.5V, -40° to +85°C             |  |  |

|                                                                |       | -                                                               | _                                                    | _       | 0.6           | v     | IOL=7.0 mA, VDD=4.5V, +125°C                    |  |  |

| D083                                                           |       | OSC2/CLKOUT (RC only)                                           | _                                                    | _       | 0.6           | v     | IOL=1.6 mA, VDD=4.5V, -40° to +85°C             |  |  |

|                                                                |       |                                                                 | -                                                    | -       | 0.6           | V     | IOL=1.2 mA, VDD=4.5V, +125°C                    |  |  |

|                                                                | Voh   | Output High Voltage (Note 3)                                    |                                                      | 1       |               | 1     |                                                 |  |  |

| D090                                                           |       | I/O ports (Except RA4)                                          | VDD-0.7                                              | -       | _             | v     | IOH=-3.0 mA, VDD=4.5V, -40° to +85°C            |  |  |

|                                                                |       |                                                                 | VDD-0.7                                              | -       | -             | v     | IOH=-2.5 mA, VDD=4.5V, +125°С                   |  |  |

| D092                                                           |       | OSC2/CLKOUT (RC only)                                           | VDD-0.7                                              | -       | -             | v     | IOH=-1.3 mA, VDD=4.5V, -40° to +85°C            |  |  |

|                                                                |       |                                                                 | VDD-0.7                                              | -       | -             | v     | IOH=-1.0 mA, VDD=4.5V, +125°С                   |  |  |

| *D150                                                          | Vod   | Open-Drain High Voltage                                         |                                                      |         | 8.5           | V     | RA4 pin                                         |  |  |

|                                                                |       | Capacitive Loading Specs on                                     |                                                      |         |               |       |                                                 |  |  |

|                                                                |       | Output Pins                                                     |                                                      |         |               |       |                                                 |  |  |

| D100                                                           |       | OSC2 pin                                                        |                                                      |         | 15            | pF    | In XT, HS and LP modes when external            |  |  |

|                                                                | 2     |                                                                 |                                                      |         |               |       | clock used to drive OSC1.                       |  |  |

| D101                                                           | Cio   | All I/O pins/OSC2 (in RC mode)<br>These parameters are characte |                                                      |         | 50            | pF    |                                                 |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC16CE62X be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

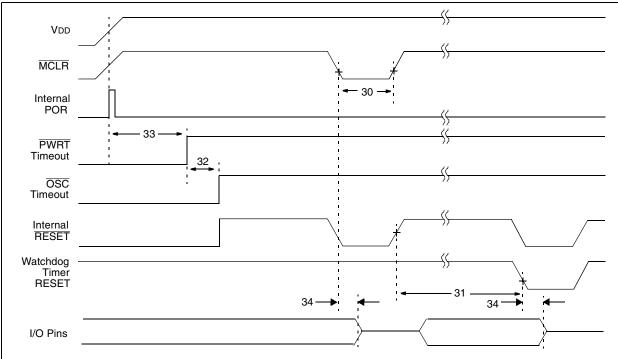

#### FIGURE 13-7: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

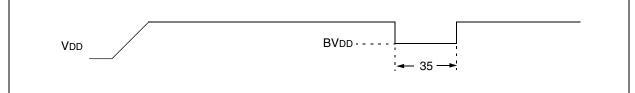

#### FIGURE 13-8: BROWN-OUT RESET TIMING

#### **TABLE 13-5:** RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                                   | Min  | Тур†      | Max  | Units | Conditions                                         |

|------------------|-------|--------------------------------------------------|------|-----------|------|-------|----------------------------------------------------|

| 30               | TmcL  | MCLR Pulse Width (low)                           | 2000 | _         | _    | ns    | -40° to +85°C                                      |

| 31               | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7*   | 18        | 33*  | ms    | $VDD = 5.0V, -40^{\circ} \text{ to } +85^{\circ}C$ |

| 32               | Tost  | Oscillation Start-up Timer Period                | _    | 1024 Tosc | _    | _     | Tosc = OSC1 period                                 |

| 33               | Tpwrt | Power-up Timer Period                            | 28*  | 72        | 132* | ms    | $VDD = 5.0V, -40^{\circ} \text{ to } +85^{\circ}C$ |

| 34               | Tioz  | I/O hi-impedance from MCLR low                   |      | —         | 2.0  | μS    |                                                    |

| 35               | TBOR  | Brown-out Reset Pulse Width                      | 100* | —         |      | μs    | $3.7V \leq V\text{DD} \leq 4.3V$                   |

These parameters are characterized but not tested. Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are t not tested.

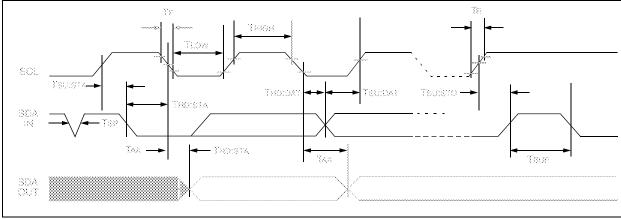

#### 13.6 EEPROM Timing

| Parameter                                           | Symbol  |           | NDARD Vcc = 4.5 - 5.5V<br>ODE FAST MODE |                | Units | Remarks |                                                                     |  |

|-----------------------------------------------------|---------|-----------|-----------------------------------------|----------------|-------|---------|---------------------------------------------------------------------|--|

|                                                     |         | Min.      | Max.                                    | Min.           | Max.  |         |                                                                     |  |

| Clock frequency                                     | FCLK    | _         | 100                                     |                | 400   | kHz     |                                                                     |  |

| Clock high time                                     | THIGH   | 4000      | _                                       | 600            | _     | ns      |                                                                     |  |

| Clock low time                                      | TLOW    | 4700      | _                                       | 1300           | —     | ns      |                                                                     |  |

| SDA and SCL rise time                               | TR      | —         | 1000                                    | _              | 300   | ns      | (Note 1)                                                            |  |

| SDA and SCL fall time                               | TF      | _         | 300                                     | _              | 300   | ns      | (Note 1)                                                            |  |

| START condition hold time                           | THD:STA | 4000      | —                                       | 600            | —     | ns      | After this period the first clock pulse is generated                |  |

| START condition setup time                          | TSU:STA | 4700      | —                                       | 600            | —     | ns      | Only relevant for repeated START condition                          |  |

| Data input hold time                                | THD:DAT | 0         |                                         | 0              |       | ns      | (Note 2)                                                            |  |

| Data input setup time                               | TSU:DAT | 250       | _                                       | 100            | _     | ns      |                                                                     |  |

| STOP condition setup time                           | Tsu:sto | 4000      | _                                       | 600            | _     | ns      |                                                                     |  |

| Output valid from clock                             | TAA     | —         | 3500                                    | —              | 900   | ns      | (Note 2)                                                            |  |

| Bus free time                                       | TBUF    | 4700      | _                                       | 1300           | _     | ns      | Time the bus must be free<br>before a new transmission<br>can start |  |

| Output fall time from VIH<br>minimum to VIL maximum | TOF     | —         | 250                                     | 20 + 0.1<br>CB | 250   | ns      | (Note 1), $CB \le 100 \text{ pF}$                                   |  |

| Input filter spike suppression (SDA and SCL pins)   | TSP     | _         | 50                                      | _              | 50    | ns      | (Note 3)                                                            |  |

| Write cycle time                                    | Twr     | _         | 10                                      |                | 10    | ms      | Byte or Page mode                                                   |  |

| Endurance                                           |         | 10M<br>1M | —                                       | 10M<br>1M      | _     | cycles  | 25°C, Vcc = 5.0V, Block<br>Mode (Note 4)                            |  |

#### TABLE 13-7: AC CHARACTERISTICS

**Note 1:** Not 100% tested. CB = total capacitance of one bus line in pF.

2: As a transmitter, the device must provide an internal minimum delay time to bridge the undefined region (minimum 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

3: The combined TSP and VHYS specifications are due to new Schmitt trigger inputs which provide improved noise spike suppression. This eliminates the need for a TI specification for standard operation.

4: This parameter is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which can be obtained on our website.

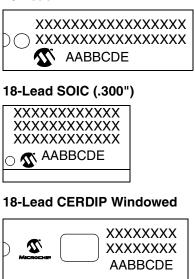

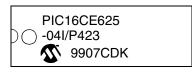

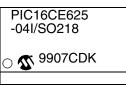

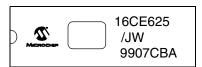

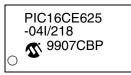

#### 14.1 Package Marking Information

#### **18-Lead PDIP**

#### 20-Lead SSOP

#### Example

#### Example

#### Example

#### Example

| Legend | I: XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|--------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Note:  | be carrie                                 | nt the full Microchip part number cannot be marked on one line, it will d over to the next line, thus limiting the number of available s for customer-specific information.                                                                                                                                                                                                  |

#### INDEX

| Α                      |    |

|------------------------|----|

| ADDLW Instruction      |    |

| ADDWF Instruction      |    |

| ANDLW Instruction      |    |

| ANDWF Instruction      |    |

| Architectural Overview | 7  |

| Assembler              |    |

| MPASM Assembler        | 77 |

| в                      |    |

#### В

| BCF Instruction        |    |

|------------------------|----|

| Block Diagram          |    |

| TIMER0                 | 35 |

| TMR0/WDT PRESCALER     |    |

| Brown-Out Detect (BOD) |    |

| BSF Instruction        | 68 |

| BTFSC Instruction      |    |

| BTFSS Instruction      |    |

| С                      |    |