Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 1.75KB (1K x 14)                                                             |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 96 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce624t-04-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

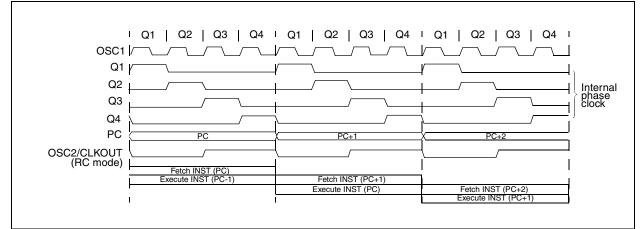

## 3.1 Clocking Scheme/Instruction Cycle

The clock input (OSC1/CLKIN pin) is internally divided by four to generate four non-overlapping quadrature clocks namely Q1, Q2, Q3 and Q4. Internally, the program counter (PC) is incremented every Q1, the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow is shown in Figure 3-2.

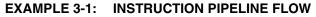

### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3 and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle, while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (i.e., GOTO) then two cycles are required to complete the instruction (Example 3-1).

A fetch cycle begins with the program counter (PC) incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-2: CLOCK/INSTRUCTION CYCLE

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline, while the new instruction is being fetched and then executed.

# 4.0 MEMORY ORGANIZATION

# 4.1 <u>Program Memory Organization</u>

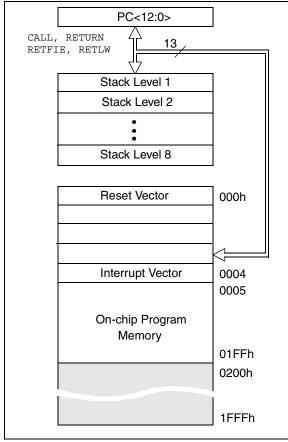

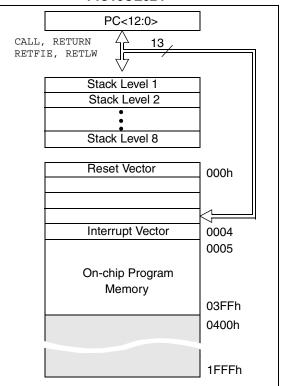

The PIC16CE62X has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 512 x 14 (0000h - 01FFh) for the PIC16CE623, 1K x 14 (0000h - 03FFh) for the PIC16CE624 and 2K x 14 (0000h - 07FFh) for the PIC16CE625 are physically implemented. Accessing a location above these boundaries will cause a wrap-around within the first 512 x 14 space (PIC16CE623) or 1K x 14 space (PIC16CE624) or 2K x 14 space (PIC16CE625). The reset vector is at 0000h and the interrupt vector is at 0004h (Figure 4-1, Figure 4-2, Figure 4-3).

## FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE623

# FIGURE 4-2: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE624

#### FIGURE 4-3: PROGRAM MEMORY MAP AND STACK FOR THE PIC16CE625

## FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16CE623/624

| File<br>Address | 3                                         | -                   | File<br>Address |

|-----------------|-------------------------------------------|---------------------|-----------------|

| 00h             | INDF <sup>(1)</sup>                       | INDF <sup>(1)</sup> | 80h             |

| 01h             | TMR0                                      | OPTION              | 81h             |

| 02h             | PCL                                       | PCL                 | 82h             |

| 03h             | STATUS                                    | STATUS              | 83h             |

| 04h             | FSR                                       | FSR                 | 84h             |

| 05h             | PORTA                                     | TRISA               | 85h             |

| 06h             | PORTB                                     | TRISB               | 86h             |

| 07h             |                                           |                     | 87h             |

| 08h             |                                           |                     | 88h             |

| 09h             |                                           |                     | 89h             |

| 0Ah             | PCLATH                                    | PCLATH              | 8Ah             |

| 0Bh             | INTCON                                    | INTCON              | 8Bh             |

| 0Ch             | PIR1                                      | PIE1                | 8Ch             |

| 0Dh             |                                           |                     | 8Dh             |

| 0Eh             |                                           | PCON                | 8Eh             |

| 0Fh             |                                           |                     | 8Fh             |

| 10h             |                                           | EEINTF              | 90h             |

| 11h             |                                           |                     | 91h             |

| 12h             |                                           |                     | 92h             |

| 13h             |                                           |                     | 93h             |

| 14h             |                                           |                     | 94h             |

| 15h             |                                           |                     | 95h             |

| 16h             |                                           |                     | 96h             |

| 17h             |                                           |                     | 97h             |

| 18h             |                                           |                     | 98h             |

| 19h             |                                           |                     | 99h             |

| 1Ah             |                                           |                     | 9Ah             |

| 1Bh             |                                           |                     | 9Bh             |

| 1Ch             |                                           |                     | 9Ch             |

| 1Dh             |                                           |                     | 9Dh             |

| 1Eh             |                                           |                     | 9Eh             |

| 1Fh             | CMCON                                     | VRCON               | 9Fh             |

| 20h             |                                           |                     | A0h             |

|                 | General<br>Purpose<br>Register            |                     |                 |

|                 |                                           |                     |                 |

|                 |                                           |                     | EFh             |

|                 |                                           | Accesses            | F0h             |

| 7Fh             |                                           | 70h-7Fh             | FFh             |

| / [1]           | Bank 0                                    | Bank 1              |                 |

|                 | blemented data me<br>Not a physical regis | •                   | ead as '0'.     |

#### FIGURE 4-5: DATA MEMORY MAP FOR THE PIC16CE625

| File     |                      |                     | File       |

|----------|----------------------|---------------------|------------|

| Address  | ;                    |                     | Address    |

| 00h      | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h        |

| 01h      | TMR0                 | OPTION              | 81h        |

| 02h      | PCL                  | PCL                 | 82h        |

| 03h      | STATUS               | STATUS              | 83h        |

| 04h      | FSR                  | FSR                 | 84h        |

| 05h      | PORTA                | TRISA               | 85h        |

| 06h      | PORTB                | TRISB               | 86h        |

| 07h      |                      |                     | 87h        |

| 08h      |                      |                     | 88h        |

| 09h      |                      |                     | 89h        |

| 0Ah      | PCLATH               | PCLATH              | 8Ah        |

| 0Bh      | INTCON               | INTCON              | 8Bh        |

| 0Ch      | PIR1                 | PIE1                | 8Ch        |

| 0Dh      |                      |                     | 8Dh        |

| 0Eh      |                      | PCON                | 8Eh        |

| 0Fh      |                      |                     | 8Fh        |

| 10h      |                      | EEINTF              | 90h        |

| 11h      |                      |                     | 91h        |

| 12h      |                      |                     | 92h        |

| 13h      |                      |                     | 93h        |

| 14h      |                      |                     | 94h        |

| 15h      |                      |                     | 95h        |

| 16h      |                      |                     | 96h        |

| 17h      |                      |                     | 97h        |

| 18h      |                      |                     | 98h        |

| 19h      |                      |                     | 99h        |

| 1Ah      |                      |                     | 9Ah        |

| 1Bh      |                      |                     | 9Bh        |

| 1Ch      |                      |                     | 9Ch        |

| 1Dh      |                      |                     | 9Dh        |

| 1Eh      |                      |                     | 9Eh        |

| 1Fh      | CMCON                | VRCON               | 9Fh        |

| 20h      |                      |                     | A0h        |

|          | General              | General             | AUII       |

|          | Purpose<br>Register  | Purpose<br>Register |            |

|          | negistei             | negister            | BFh        |

|          |                      |                     | C0h        |

|          |                      |                     |            |

|          |                      | _                   | F0h        |

|          |                      | Accesses            |            |

| 751      |                      | 70h-7Fh             | FFh        |

| 7Fh I    | Bank 0               | Bank 1              | J FFN      |

| <b>—</b> |                      |                     |            |

|          | plemented data me    |                     | ad as '0'. |

| Note 1:  | Not a physical regis | ster.               |            |

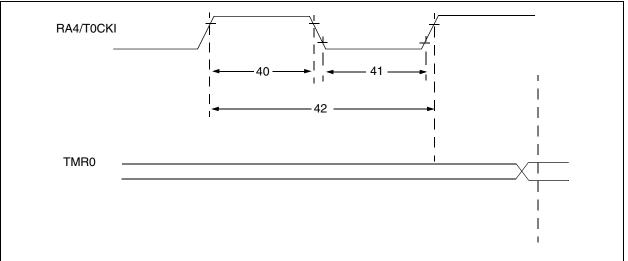

#### 4.2.2.2 OPTION REGISTER

The OPTION register is a readable and writable register which contains various control bits to configure the TMR0/WDT prescaler, the external RB0/INT interrupt, TMR0 and the weak pull-ups on PORTB.

Note: To achieve a 1:1 prescaler assignment for TMR0, assign the prescaler to the WDT (PSA = 1).

# REGISTER 4-2: OPTION REGISTER (ADDRESS 81H)

| R/W-1    | R/W-1                                                | R/W-1                                                       | R/W-1        | R/W-1      | R/W-1                  | R/W-1      | R/W-1 |                                                                                                                   |

|----------|------------------------------------------------------|-------------------------------------------------------------|--------------|------------|------------------------|------------|-------|-------------------------------------------------------------------------------------------------------------------|

| RBPU     | INTEDG                                               | TOCS                                                        | TOSE         | PSA        | PS2                    | PS1        | PS0   | R = Readable bit                                                                                                  |

| bit7     |                                                      |                                                             |              |            |                        |            | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |

| bit 7:   | <b>RBPU</b> : PO<br>1 = PORTE<br>0 = PORTE           | 3 pull-ups                                                  | are disal    | oled       | lividual port          | latch valu | es    |                                                                                                                   |

| bit 6:   | INTEDG: In<br>1 = Interrup<br>0 = Interrup           | ot on rising                                                | g edge o     | f RB0/INT  |                        |            |       |                                                                                                                   |

| bit 5:   | <b>TOCS</b> : TMF<br>1 = Transiti<br>0 = Interna     | ion on RA                                                   | 4/T0CKI      | pin        | (OUT)                  |            |       |                                                                                                                   |

| bit 4:   |                                                      | ent on hig                                                  | h-to-low     | transition | on RA4/T0<br>on RA4/T0 |            |       |                                                                                                                   |

| bit 3:   | PSA: Prese<br>1 = Presca<br>0 = Presca               | ler is assi                                                 | gned to t    | he WDT     | ) module               |            |       |                                                                                                                   |

| bit 2-0: | <b>PS&lt;2:0&gt;</b> : F                             | Prescaler I                                                 | Rate Sele    | ect bits   |                        |            |       |                                                                                                                   |

|          | Bit Value                                            | TMR0 Ra                                                     | te WD1       | Γ Rate     |                        |            |       |                                                                                                                   |

|          | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1 :<br>3 1 : | 2<br>4     |                        |            |       |                                                                                                                   |

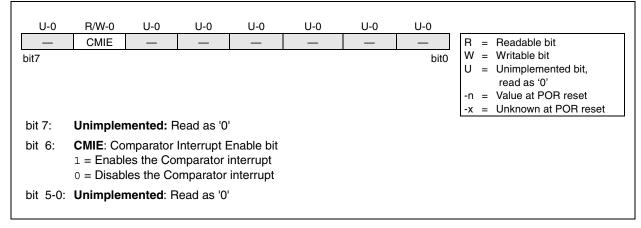

#### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bit for the comparator interrupt.

# REGISTER 4-4: PIE1 REGISTER (ADDRESS 8CH)

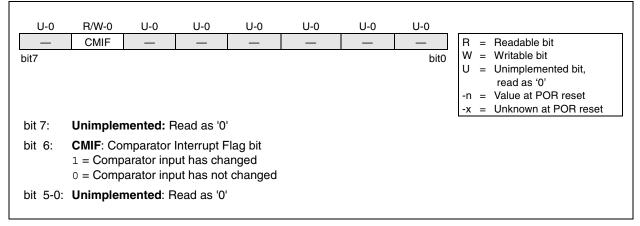

#### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt   |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------------|--|--|--|--|--|--|--|--|

|       | condition occurs, regardless of the state of    |  |  |  |  |  |  |  |  |

|       | its corresponding enable bit or the global      |  |  |  |  |  |  |  |  |

|       | enable bit, GIE (INTCON<7>). User               |  |  |  |  |  |  |  |  |

|       | software should ensure the appropriate          |  |  |  |  |  |  |  |  |

|       | interrupt flag bits are clear prior to enabling |  |  |  |  |  |  |  |  |

|       | an interrupt.                                   |  |  |  |  |  |  |  |  |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

## 6.1 Bus Characteristics

In this section, the term "processor" refers to the portion of the PIC16CE62X that interfaces to the EEPROM through software manipulating the EEINTF register. The following **bus protocol** is to be used with the EEPROM data memory.

- Data transfer may be initiated only when the bus is not busy.

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH will be interpreted by the EEPROM as a START or STOP condition.

Accordingly, the following bus conditions have been defined (Figure 6-1).

#### 6.1.1 BUS NOT BUSY (A)

Both data and clock lines remain HIGH.

#### 6.1.2 START DATA TRANSFER (B)

A HIGH to LOW transition of the SDA line while the clock (SCL) is HIGH determines a START condition. All commands must be preceded by a START condition.

#### 6.1.3 STOP DATA TRANSFER (C)

A LOW to HIGH transition of the SDA line while the clock (SCL) is HIGH determines a STOP condition. All operations must be ended with a STOP condition.

#### 6.1.4 DATA VALID (D)

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal.

The data on the line must be changed during the LOW period of the clock signal. There is one bit of data per clock pulse.

Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of the data bytes transferred between the START and STOP conditions is determined by the processor and is theoretically unlimited, although only the last sixteen will be stored when doing a write operation. When an overwrite does occur, it will replace data in a first-in, first-out fashion.

#### 6.1.5 ACKNOWLEDGE

The EEPROM will generate an acknowledge after the reception of each byte. The processor must generate an extra clock pulse which is associated with this acknowledge bit.

| Note: | Acknowledge bits are not generated if an   |

|-------|--------------------------------------------|

|       | internal programming cycle is in progress. |

When the EEPROM acknowledges, it pulls down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse. Of course, setup and hold times must be taken into account. The processor must signal an end of data to the EEPROM by not generating an acknowledge bit on the last byte that has been clocked out of the EEPROM. In this case, the EEPROM must leave the data line HIGH to enable the processor to generate the STOP condition (Figure 6-2).

#### 6.3 Write Operations

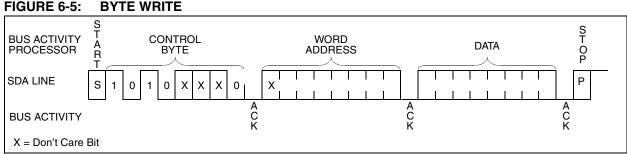

#### BYTE WRITE 6.3.1

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the R/W bit, which is a logic low, is placed onto the bus by the processor. This indicates to the EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer of the EEPROM. After receiving another acknowledge signal from the EEPROM, the processor will transmit the data word to be written into the addressed memory location. The EEPROM acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time, the EEPROM will not generate acknowledge signals (Figure 6-5).

#### 6.3.2 PAGE WRITE

The write control byte, word address and the first data byte are transmitted to the EEPROM in the same way as in a byte write. But instead of generating a stop condition, the processor transmits up to eight data bytes to the EEPROM, which are temporarily stored in the onchip page buffer and will be written into the memory after the processor has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the processor should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin (Figure 6-6).

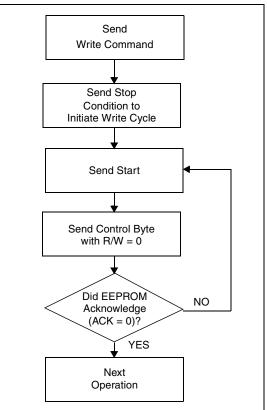

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the EEPROM initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. See Figure 6-4 for flow diagram.

#### FIGURE 6-4: ACKNOWLEDGE POLLING FLOW

# FIGURE 6-5:

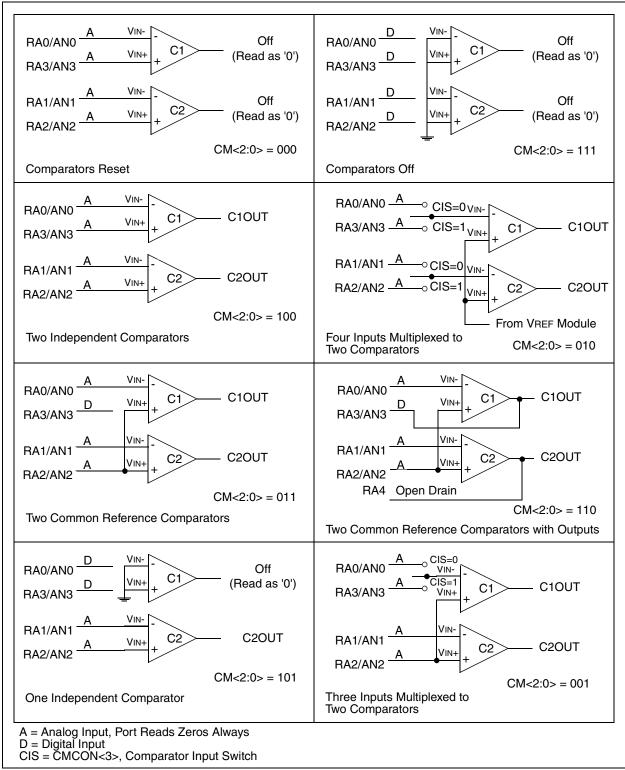

# 8.1 <u>Comparator Configuration</u>

There are eight modes of operation for the comparators. The CMCON register is used to select the mode. Figure 8-1 shows the eight possible modes. The TRISA register controls the data direction of the comparator pins for each mode. If the comparator

mode is changed, the comparator output level may not be valid for the specified mode change delay shown in Table 13-1.

Note: Comparator interrupts should be disabled during a comparator mode change, otherwise a false interrupt may occur.

FIGURE 8-1: COMPARATOR I/O OPERATING MODES

#### 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs, otherwise the maximum delay of the comparators should be used (Table 13-1).

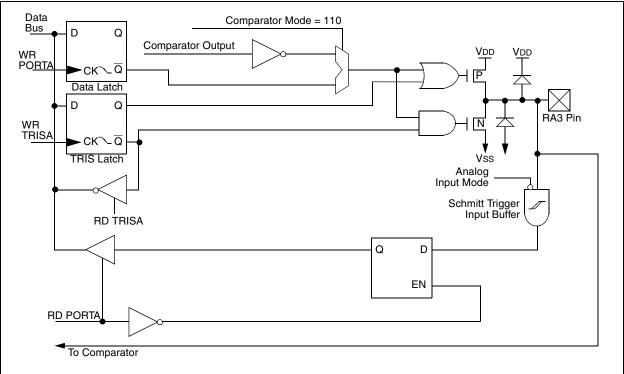

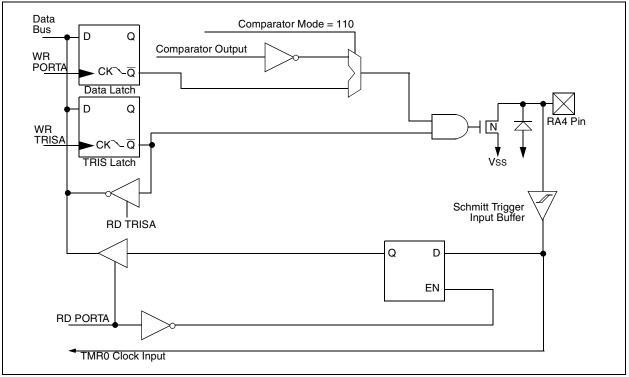

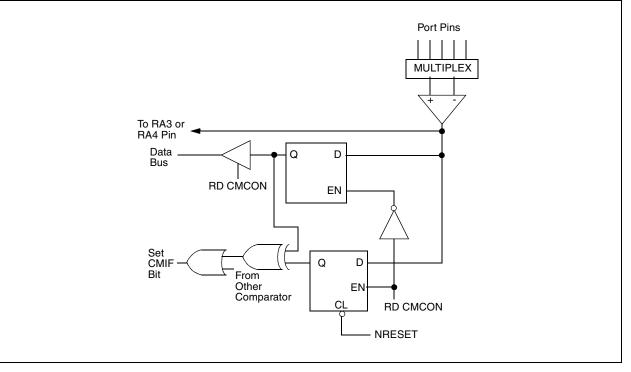

## 8.5 <u>Comparator Outputs</u>

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 8-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

# FIGURE 8-3: COMPARATOR OUTPUT BLOCK DIAGRAM

# 10.1 Configuration Bits

The configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations. These bits are mapped in program memory location 2007h.

**REGISTER 10-1: CONFIGURATION WORD**

The user will note that address 2007h is beyond the user program memory space. In fact, it belongs to the special test/configuration memory space (2000h - 3FFFh), which can be accessed only during programming.

| CP1 CP    | 0 <sup>(2)</sup> CP1 C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <sub>CP0</sub> (2) | CP1      | CP0 <sup>(2)</sup> | _       | BODEN <sup>(1)</sup> | CP1    | CP0 <sup>(2)</sup> | PWRTE(    | 1) WDTE | F0SC1       | F0SC0       | CONFIG       | Addres  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------|--------------------|---------|----------------------|--------|--------------------|-----------|---------|-------------|-------------|--------------|---------|

| bit13     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                    |          |                    |         |                      |        |                    |           |         |             | bit0        | REGISTER     | 8: 2007 |

| bit 13-8, | CP1:CP0 Pa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | irs: Cod           | le prote | ection bit         | pairs   | (2)                  |        |                    |           |         |             |             |              |         |

| 5-4:      | · · · · •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          | •                  |         | n off                |        |                    |           |         |             |             |              |         |

|           | 10 = 0400h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = 0200h-<br>00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | Code prote                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         | morv                 |        |                    |           |         |             |             |              |         |

|           | 11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 10 =Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = 0200h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | Code prote<br>11 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                    |          |                    |         | -                    |        |                    |           |         |             |             |              |         |

|           | 11 = Progra<br>10 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          | •                  |         |                      |        |                    |           |         |             |             |              |         |

|           | 01 = Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                    |          | •                  |         |                      |        |                    |           |         |             |             |              |         |

|           | 00 = 0000h-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -01FFh             | code     | ,<br>protecte      | d       |                      |        |                    |           |         |             |             |              |         |

| bit 7:    | Unimpleme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ented: F           | Read a   | s '1'              |         |                      |        |                    |           |         |             |             |              |         |

| bit 6:    | BODEN: Bro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | own-ou             | t Rese   | t Enable           | e bit ( | 1)                   |        |                    |           |         |             |             |              |         |

|           | 1 = BOD en                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    |          |                    |         |                      |        |                    |           |         |             |             |              |         |

|           | 0 = BOD dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | sabled             |          |                    |         |                      |        |                    |           |         |             |             |              |         |

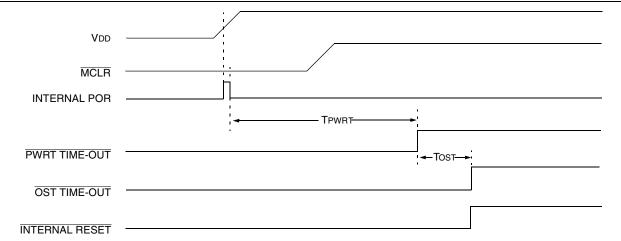

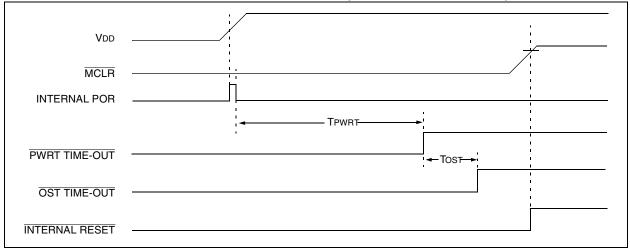

| bit 3:    | PWRTE: Po                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | wer-up             | Timer    | Enable             | bit (1  | )                    |        |                    |           |         |             |             |              |         |

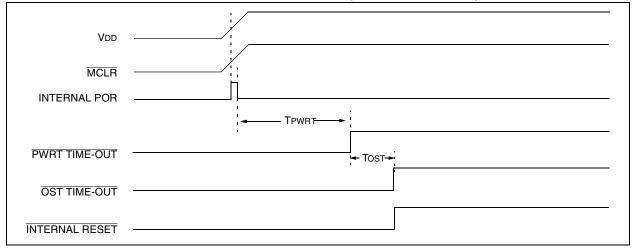

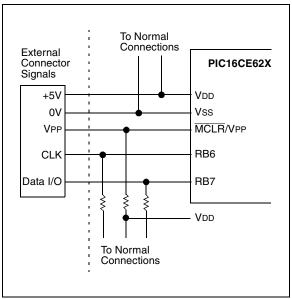

|           | 1 = PWRT c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                    | -        |                    |         |                      |        |                    |           |         |             |             |              |         |