Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 4MHz                                                                          |

| Connectivity               | -                                                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                              |

| Number of I/O              | 13                                                                            |

| Program Memory Size        | 1.75KB (1K x 14)                                                              |

| Program Memory Type        | OTP                                                                           |

| EEPROM Size                | 128 x 8                                                                       |

| RAM Size                   | 96 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | <u>.</u>                                                                      |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                |

| Supplier Device Package    | 18-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce624t-04e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| 1.0   | General Description                           | 3     |

|-------|-----------------------------------------------|-------|

| 2.0   | PIC16CE62X Device Varieties                   | 5     |

| 3.0   | Architectural Overview                        |       |

| 4.0   | Memory Organization                           | 11    |

| 5.0   | I/O Ports                                     |       |

| 6.0   | EEPROM Peripheral Operation                   | 29    |

| 7.0   | Timer0 Module                                 |       |

| 8.0   | Comparator Module                             | 41    |

| 9.0   | Voltage Reference Module                      | 47    |

| 10.0  | Special Features of the CPU                   | 49    |

| 11.0  | Instruction Set Summary                       | 65    |

|       | Development Support                           |       |

|       | Electrical Specifications                     |       |

| 14.0  | Packaging Information                         | 97    |

| Appe  | ndix A: Code for Accessing EEPROM Data Memory | 103   |

| Index |                                               | 105   |

| On Li | ne Support                                    | . 107 |

| Read  | ne Support<br>er Response                     | 108   |

| PIC1  | 6CE62X Product Identification System          | . 109 |

# To Our Valued Customers

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

### New Customer Notification System

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

#### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

# 2.0 PIC16CE62X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements the proper device option can be selected using the information in the PIC16CE62X Product Identification System section at the end of this data sheet. When placing orders, please use this page of the data sheet to specify the correct part number.

# 2.1 UV Erasable Devices

The UV erasable version, offered in the CERDIP package is optimal for prototype development and pilot programs. This version can be erased and reprogrammed to any of the oscillator modes.

Microchip's PICSTART<sup>®</sup> and PRO MATE<sup>®</sup> programmers both support programming of the PIC16CE62X.

# 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers who need the flexibility for frequent code updates and small volume applications. In addition to the program memory, the configuration bits must also be programmed.

# 2.3 <u>Quick-Turn-Programming (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who chose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your Microchip Technology sales office for more details.

# 2.4 <u>Serialized Quick-Turn-Programming</u> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

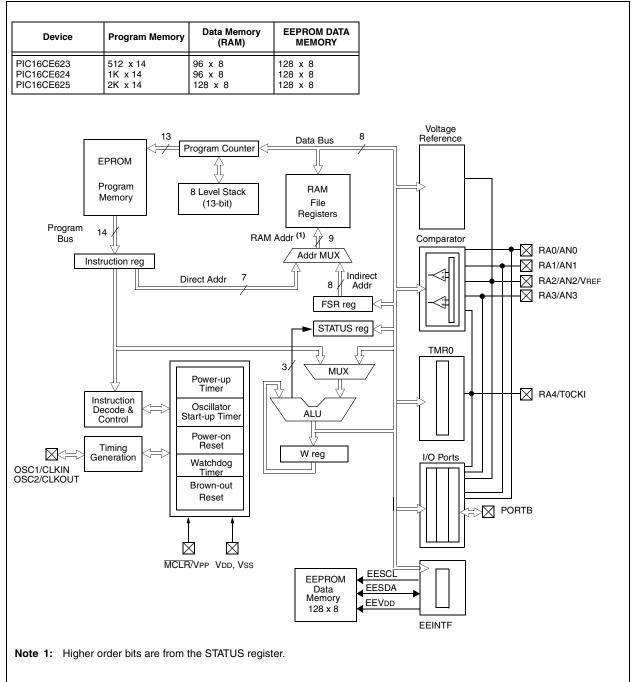

# FIGURE 3-1: BLOCK DIAGRAM

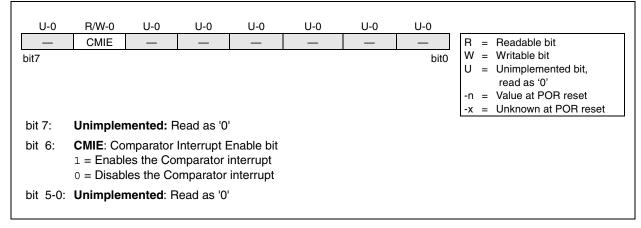

### 4.2.2.4 PIE1 REGISTER

This register contains the individual enable bit for the comparator interrupt.

# REGISTER 4-4: PIE1 REGISTER (ADDRESS 8CH)

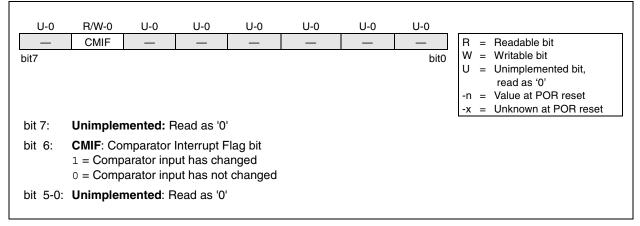

### 4.2.2.5 PIR1 REGISTER

This register contains the individual flag bit for the comparator interrupt.

| Note: | Interrupt flag bits get set when an interrupt   |

|-------|-------------------------------------------------|

|       | condition occurs, regardless of the state of    |

|       | its corresponding enable bit or the global      |

|       | enable bit, GIE (INTCON<7>). User               |

|       | software should ensure the appropriate          |

|       | interrupt flag bits are clear prior to enabling |

|       | an interrupt.                                   |

# REGISTER 4-5: PIR1 REGISTER (ADDRESS 0CH)

NOTES:

# 7.3 <u>Prescaler</u>

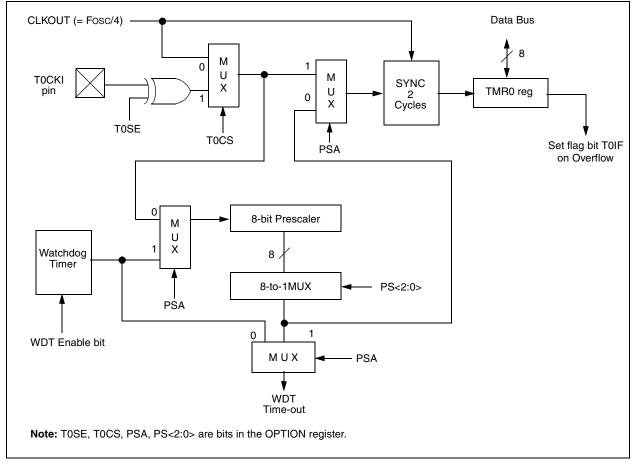

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

# 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

# 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

# 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

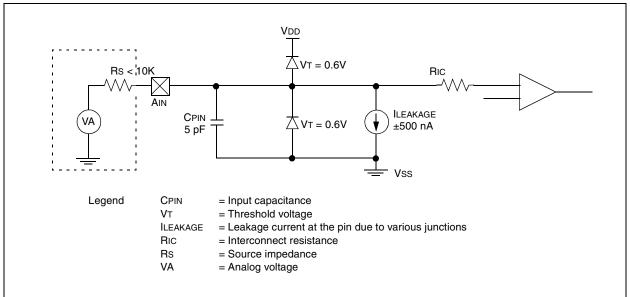

# 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

# FIGURE 8-4: ANALOG INPUT MODEL

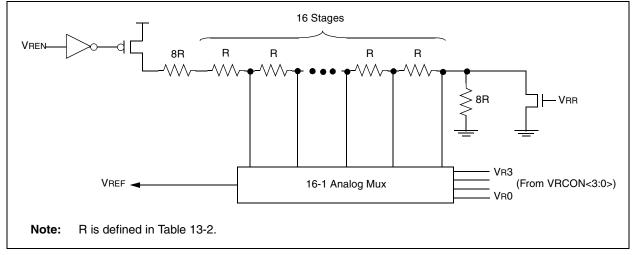

# 9.0 VOLTAGE REFERENCE MODULE

The Voltage Reference is a 16-tap resistor ladder network that provides a selectable voltage reference. The resistor ladder is segmented to provide two ranges of VREF values and has a power-down function to conserve power when the reference is not being used. The VRCON register controls the operation of the reference as shown in Register 9-1. The block diagram is given in Figure 9-1.

# 9.1 Configuring the Voltage Reference

The Voltage Reference can output 16 distinct voltage levels for each range.

The equations used to calculate the output of the Voltage Reference are as follows:

if VRR = 1: VREF = (VR<3:0>/24) x VDD

if VRR = 0: VREF = (VDD x 1/4) + (VR<3:0>/32) x VDD

The setting time of the Voltage Reference must be considered when changing the VREF output (Table 13-1). Example 9-1 shows an example of how to configure the Voltage Reference for an output voltage of 1.25V with VDD = 5.0V.

| R/W-0    | R/W-0                                                                                              | R/W-0                                                                                                                                                                             | U-0      | R/W-0         | R/W-0     | R/W-0 | R/W-0 |                                                                                       |

|----------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------|-----------|-------|-------|---------------------------------------------------------------------------------------|

| VREN     | VROE                                                                                               | Vrr                                                                                                                                                                               | _        | Vr3           | VR2       | VR1   | VR0   | R = Readable bit                                                                      |

| bit7     | •                                                                                                  |                                                                                                                                                                                   | •        |               |           |       | bitO  | W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>- n = Value at POR reset |

| bit 7:   |                                                                                                    | Enable<br>EF circuit p<br>EF circuit p                                                                                                                                            |          |               | IDD drain |       |       |                                                                                       |

| bit 6:   | VROE: VREF Output Enable<br>1 = VREF is output on RA2 pin<br>0 = VREF is disconnected from RA2 pin |                                                                                                                                                                                   |          |               |           |       |       |                                                                                       |

| bit 5:   | VRR: VREF Range selection<br>1 = Low Range<br>0 = High Range                                       |                                                                                                                                                                                   |          |               |           |       |       |                                                                                       |

| bit 4:   | Unimplem                                                                                           | ented: Re                                                                                                                                                                         | ad as '0 | <sup>ji</sup> |           |       |       |                                                                                       |

| bit 3-0: | when V                                                                                             | Inimplemented: Read as '0'<br>(R<3:0>: VREF value selection 0 ≤ VR [3:0] ≤ 15<br>when VRR = 1: VREF = (VR<3:0>/ 24) * VDD<br>when VRR = 0: VREF = 1/4 * VDD + (VR<3:0>/ 32) * VDD |          |               |           |       |       |                                                                                       |

# REGISTER 9-1: VRCON REGISTER (ADDRESS 9Fh)

FIGURE 9-1: VOLTAGE REFERENCE BLOCK DIAGRAM

### EXAMPLE 9-1: VOLTAGE REFERENCE CONFIGURATION

| MOVLW | 0x02        | ; | 4 Inputs Muxed |

|-------|-------------|---|----------------|

| MOVWF | CMCON       | ; | to 2 comps.    |

| BSF   | STATUS, RPO | ; | go to Bank 1   |

| MOVLW | 0x07        | ; | RA3-RA0 are    |

| MOVWF | TRISA       | ; | outputs        |

| MOVLW | 0xA6        | ; | enable VREF    |

| MOVWF | VRCON       | ; | low range      |

|       |             | ; | set VR<3:0>=6  |

| BCF   | STATUS, RPO | ; | go to Bank 0   |

| CALL  | DELAY10     | ; | 10µs delay     |

### 9.2 <u>Voltage Reference Accuracy/Error</u>

The full range of VSS to VDD cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 9-1) keep VREF from approaching VSS or VDD. The Voltage Reference is VDD derived and therefore, the VREF output changes with fluctuations in VDD. The absolute accuracy of the Voltage Reference can be found in Table 13-2.

# 9.3 Operation During Sleep

When the device wakes up from sleep through an interrupt or a Watchdog Timer time-out, the contents of the VRCON register are not affected. To minimize current consumption in SLEEP mode, the Voltage Reference should be disabled.

# 9.4 Effects of a Reset

A device reset disables the Voltage Reference by clearing bit VREN (VRCON<7>). This reset also disconnects the reference from the RA2 pin by clearing bit VROE (VRCON<6>) and selects the high voltage range by clearing bit VRR (VRCON<5>). The VREF value select bits, VRCON<3:0>, are also cleared.

# 9.5 <u>Connection Considerations</u>

The Voltage Reference Module operates independently of the comparator module. The output of the reference generator may be connected to the RA2 pin if the TRISA<2> bit is set and the VROE bit, VRCON<6>, is set. Enabling the Voltage Reference output onto the RA2 pin with an input signal present will increase current consumption. Connecting RA2 as a digital output with VREF enabled will also increase current consumption.

The RA2 pin can be used as a simple D/A output with limited drive capability. Due to the limited drive capability, a buffer must be used in conjunction with the Voltage Reference output for external connections to VREF. Figure 9-2 shows an example buffering technique.

# VREF Nodule Voltage Reference Output Impedance

# FIGURE 9-2: VOLTAGE REFERENCE OUTPUT BUFFER EXAMPLE

Note 1: R is dependent upon the Voltage Reference Configuration VRCON<3:0> and VRCON<5>.

# TABLE 9-1: REGISTERS ASSOCIATED WITH VOLTAGE REFERENCE

| Address | Name  | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value On<br>POR / BOD | Value On<br>All Other<br>Resets |

|---------|-------|-------|-------|-------|--------|--------|--------|--------|--------|-----------------------|---------------------------------|

| 9Fh     | VRCON | VREN  | VROE  | VRR   | _      | VR3    | VR2    | VR1    | VR0    | 000- 0000             | 000- 0000                       |

| 1Fh     | CMCON | C2OUT | C10UT | _     | _      | CIS    | CM2    | CM1    | CM0    | 00 0000               | 00 0000                         |

| 85h     | TRISA | _     | _     |       | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 1 1111                | 1 1111                          |

Legend: - = Unimplemented, read as "0"

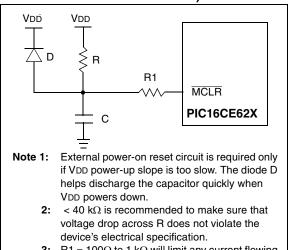

### 10.4.5 TIME-OUT SEQUENCE

On power-up, the time-out sequence is as follows: First PWRT time-out is invoked after POR has expired, then OST is activated. The total time-out will vary based on oscillator configuration and <u>PWRTE</u> bit status. For example, in RC mode with <u>PWRTE</u> bit erased (PWRT disabled), there will be no time-out at all. Figure 10-8, Figure 10-9 and Figure 10-10 depict time-out sequences.

Since the time-outs occur from the POR pulse, if  $\overline{\text{MCLR}}$  is kept low long enough, the time-outs will expire. Then bringing  $\overline{\text{MCLR}}$  high will begin execution immediately (see Figure 10-9). This is useful for testing purposes or to synchronize more than one  $\text{PIC}^{\textcircled{B}}$  device operating in parallel.

Table 10-5 shows the reset conditions for some special registers, while Table 10-6 shows the reset conditions for all the registers.

### 10.4.6 POWER CONTROL (PCON)/STATUS REGISTER

The power control/status register, PCON (address 8Eh) has two bits.

Bit0 is  $\overline{\text{BOR}}$  (Brown-out).  $\overline{\text{BOR}}$  is unknown on power-on-reset. It must then be set by the user and checked on subsequent resets to see if  $\overline{\text{BOR}} = 0$  indicating that a brown-out has occurred. The  $\overline{\text{BOR}}$  status bit is a don't care and is not necessarily predictable if the brown-out circuit is disabled (by setting BODEN bit = 0 in the Configuration word).

Bit1 is POR (Power-on-reset). It is a '0' on power-on-reset and unaffected otherwise. The user must write a '1' to this bit following a power-on-reset. On a subsequent reset, if POR is '0', it will indicate that a power-on-reset must have occurred (VDD may have gone too low).

| Oscillator Configuration | Powe              | er-up     | Brown-out Reset   | Wake-up<br>from SLEEP |  |

|--------------------------|-------------------|-----------|-------------------|-----------------------|--|

| Oscillator Configuration | <b>PWRTE</b> = 0  | PWRTE = 1 | brown-out neset   |                       |  |

| XT, HS, LP               | 72 ms + 1024 Tosc | 1024 Tosc | 72 ms + 1024 Tosc | 1024 Tosc             |  |

| RC                       | 72 ms             | _         | 72 ms             | —                     |  |

# TABLE 10-3: TIME-OUT IN VARIOUS SITUATIONS

| POR | BOR | TO | PD |                           |

|-----|-----|----|----|---------------------------|

| 0   | Х   | 1  | 1  | Power-on-reset            |

| 0   | Х   | 0  | Х  | Illegal, TO is set on POR |

| 0   | Х   | Х  | 0  | Illegal, PD is set on POR |

**Brown-out Reset**

WDT Reset

WDT Wake-up

MCLR reset during normal operation

MCLR reset during SLEEP

# TABLE 10-4: STATUS/PCON BITS AND THEIR SIGNIFICANCE

Х

u

0

u

Ο

Legend: x = unknown, u = unchanged

0

1

1

1

1

Х

0

0

u

1

1

1

1

1

1

# TABLE 10-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set and the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

# TABLE 10-6: INITIALIZATION CONDITION FOR REGISTERS

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | -       | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| INDF     | 00h     | -              | -                                                                                                                                                          | -                                                                                                                 |

| TMR0     | 01h     | XXXX XXXX      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | x000 0000      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | นนนน นนนน                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| EEINTF   | 90h     | 111            | 111                                                                                                                                                        | 111                                                                                                               |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 10-5 for reset value for specific condition.

5: If wake-up was due to comparator input changing , then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

6: If reset was due to brown-out, then PCON bit 0 = 0. All other resets will cause bit 0 = u.

### FIGURE 10-11: EXTERNAL POWER-ON RESET CIRCUIT (FOR SLOW VDD POWER-UP)

**3:**  $R1 = 100\Omega$  to 1 k $\Omega$  will limit any current flowing into MCLR from external capacitor C in the event of MCLR/VPP pin breakdown due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS).

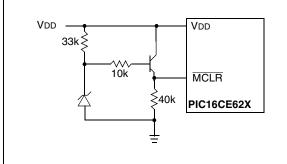

# FIGURE 10-12: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 1

- Note 1: This circuit will activate reset when VDD goes below (Vz + 0.7V) where Vz = Zener voltage.

- 2: Internal Brown-out Reset circuitry should be disabled when using this circuit.

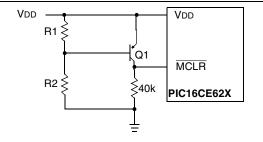

## FIGURE 10-13: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 2

Note 1: This brown-out circuit is less expensive, albeit less accurate. Transistor Q1 turns off when VDD is below a certain level such that:

$$V_{DD} \times \frac{R1}{R1 + R2} = 0.7 V$$

- **2:** Internal brown-out detection should be disabled when using this circuit.

- **3:** Resistors should be adjusted for the characteristics of the transistor.

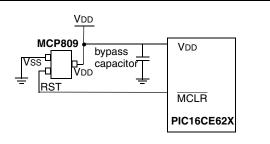

# FIGURE 10-14: EXTERNAL BROWN-OUT PROTECTION CIRCUIT 3

This brown-out protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. The MCP8XX and MCP1XX families of supervisors provide push-pull and open collector outputs with both high and low active reset pins. There are 7 different trip point selections to accommodate 5V and 3V systems.

### 10.8 Power-Down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{PD}$  bit in the STATUS register is cleared, the  $\overline{TO}$  bit is set and the oscillator driver is turned off. The I/O ports maintain the status they had before SLEEP was executed (driving high, low, or hi-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSS, with no external circuitry drawing current from the I/O pin, and the comparators and VREF should be disabled. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on chip pull-ups on PORTB should be considered.

The MCLR pin must be at a logic high level (VIHMC).

| Note: | It should be noted that a RESET generated |

|-------|-------------------------------------------|

|       | by a WDT time-out does not drive MCLR     |

|       | pin low.                                  |

### 10.8.1 WAKE-UP FROM SLEEP

The device can wake-up from SLEEP through one of the following events:

- 1. External reset input on MCLR pin

- 2. Watchdog Timer Wake-up (if WDT was enabled)

- 3. Interrupt from RB0/INT pin, RB Port change, or the Peripheral Interrupt (Comparator).

The first event will cause a device reset. The two latter events are considered a continuation of program execution. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register can be used to determine the cause of device reset.  $\overline{PD}$ bit, which is set on power-up is cleared when SLEEP is invoked.  $\overline{TO}$  bit is cleared if WDT wake-up occurred.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction after the SLEEP instruction after the instruction and then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have an NOP after the SLEEP instruction.

| If the global interrupts are disabled (GIE is |

|-----------------------------------------------|

| cleared), but any interrupt source has both   |

| its interrupt enable bit and the correspond-  |

| ing interrupt flag bits set, the device will  |

| immediately wake-up from sleep. The           |

| sleep instruction is completely executed.     |

|                                               |

The WDT is cleared when the device wakes-up from sleep, regardless of the source of wake-up.

| Q1 Q2 Q3 Q4 Q1 Q                     | Q2 Q3 Q4 Q1           | Q1 Q2 Q3 Q4  | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4      | Q1 Q2 Q3 Q4 |

|--------------------------------------|-----------------------|--------------|-------------------|------------------|-------------|

|                                      |                       |              |                   |                  |             |

| CLKOUT(4) \                          |                       | /            |                   |                  |             |

| INT pin                              |                       |              |                   |                  | i           |

| INTF flag<br>(INTCON<1>)             |                       | + + +<br>    | Interrupt Latency |                  |             |

| GIE bit<br>(INTCON<7>)               | Processor in<br>SLEEP |              |                   | י<br>ו<br>ו<br>ו |             |

| INSTRUCTION FLOW                     |                       | · ·          | 1<br>1            | 1<br>1           | 1<br>1      |

| PC X PC X F                          | PC+1 X PC+2           | X PC+2       | PC + 2            | (0004h)          | 0005h       |

| Instruction { Inst(PC) = SLEEP Ins   | st(PC + 1)            | Inst(PC + 2) | . I               | Inst(0004h)      | Inst(0005h) |

| Instruction<br>executed Inst(PC - 1) | EEP                   | Inst(PC + 1) | Dummy cycle       | Dummy cycle      | Inst(0004h) |

### FIGURE 10-19: WAKE-UP FROM SLEEP THROUGH INTERRUPT

**Note 1:** XT, HS or LP oscillator mode assumed.

2: TOST = 1024TOSC (drawing not to scale) This delay does not occur for RC osc mode.

3: GIE = '1' assumed. In this case after wake- up, the processor jumps to the interrupt routine. If GIE = '0', execution will continue in-line.

4: CLKOUT is not available in these osc modes, but shown here for timing reference.

| BTFSS            | Bit Test                                                                 | i, Skip if S                                                                                                | Set                                       |                  |

|------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------|

| Syntax:          | [ <i>label</i> ] B                                                       | TFSS f,b                                                                                                    | )                                         |                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 12 \\ 0 \leq b < 7 \end{array}$          | 7                                                                                                           |                                           |                  |

| Operation:       | skip if (f<                                                              | b>) = 1                                                                                                     |                                           |                  |

| Status Affected: | None                                                                     |                                                                                                             |                                           |                  |

| Encoding:        | 01                                                                       | 11bb                                                                                                        | bfff                                      | ffff             |

| Description:     | instruction<br>If bit 'b' is '<br>fetched du<br>execution,<br>executed i | register 'f' is<br>is skipped.<br>1', then the<br>ring the cur<br>is discarde<br>nstead, ma<br>instruction. | next instru<br>rrent instru<br>d and a No | uction<br>Iction |

| Words:           | 1                                                                        |                                                                                                             |                                           |                  |

| Cycles:          | 1(2)                                                                     |                                                                                                             |                                           |                  |

| Example          | HERE<br>FALSE<br>TRUE                                                    |                                                                                                             | FLAG,1<br>PROCESS_                        | _CODE            |

|                  | Before In                                                                | struction                                                                                                   |                                           |                  |

|                  | After Inst                                                               | ruction<br>if FLAG<1><br>PC = a<br>if FLAG<1>                                                               | = 0,<br>address F                         |                  |

| CLRF             | Clear f                                                               |   |

|------------------|-----------------------------------------------------------------------|---|

| Syntax:          | [label] CLRF f                                                        | _ |

| Operands:        | $0 \leq f \leq 127$                                                   |   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (f) \\ 1 \rightarrow Z \end{array}$ |   |

| Status Affected: | Z                                                                     |   |

| Encoding:        | 00 0001 1fff fff                                                      |   |

| Description:     | The contents of register 'f' are cleared and the Z bit is set.        |   |

| Words:           | 1                                                                     |   |

| Cycles:          | 1                                                                     |   |

| Example          | CLRF FLAG_REG                                                         |   |

|                  | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction            |   |

|                  | $FLAG\_REG = 0x00$ $Z = 1$                                            |   |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                                          |

| Operation:       | $\begin{array}{l} (PC)+1 \rightarrow TOS, \\ k \rightarrow PC < 10:0>, \\ (PCLATH < 4:3>) \rightarrow PC < 12:11> \end{array}$                                                                                                                |

| Status Affected: | None                                                                                                                                                                                                                                          |

| Encoding:        | 10 0kkk kkkk kkkk                                                                                                                                                                                                                             |

| Description:     | Call Subroutine. First, return address<br>(PC+1) is pushed onto the stack. The<br>eleven bit immediate address is<br>loaded into PC bits <10:0>. The upper<br>bits of the PC are loaded from<br>PCLATH. CALL is a two-cycle instruc-<br>tion. |

| Words:           | 1                                                                                                                                                                                                                                             |

| Cycles:          | 2                                                                                                                                                                                                                                             |

| Example          | HERE CALL THERE                                                                                                                                                                                                                               |

|                  | Before Instruction<br>PC = Address HERE<br>After Instruction<br>PC = Address THERE<br>TOS = Address HERE+1                                                                                                                                    |

| CLRW             | Clear W                                                               |   |

|------------------|-----------------------------------------------------------------------|---|

| Syntax:          | [label] CLRW                                                          | - |

| Operands:        | None                                                                  |   |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |   |

| Status Affected: | Z                                                                     |   |

| Encoding:        | 00 0001 0000 0011                                                     | 1 |

| Description:     | W register is cleared. Zero bit (Z) is set.                           | - |

| Words:           | 1                                                                     |   |

| Cycles:          | 1                                                                     |   |

| Example          | CLRW                                                                  |   |

|                  | Before Instruction<br>W = 0x5A                                        |   |

|                  | After Instruction<br>W = 0x00<br>Z = 1                                |   |

$\odot$  1998-2013 Microchip Technology Inc.

| SUBLW        | Subtract W from Literal                                                                    | SUBWF        | Subtract W from f                                                                  |

|--------------|--------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------|

| Syntax:      | [label] SUBLW k                                                                            | Syntax:      | [label] SUBWF f,d                                                                  |

| Operands:    | $0 \le k \le 255$                                                                          | Operands:    | $0 \leq f \leq 127$                                                                |

| Operation:   | $k - (W) \rightarrow (W)$                                                                  |              | d ∈ [0,1]                                                                          |

| Status       | C, DC, Z                                                                                   | Operation:   | (f) - (W) $\rightarrow$ (dest)                                                     |

| Affected:    |                                                                                            | Status       | C, DC, Z                                                                           |

| Encoding:    | 11 110x kkkk kkkk                                                                          | Affected:    |                                                                                    |

| Description: | The W register is subtracted (2's com-                                                     | Encoding:    | 00 0010 dfff ffff                                                                  |

|              | plement method) from the eight bit literal<br>'k'. The result is placed in the W register. | Description: | Subtract (2's complement method)<br>W register from register 'f'. If 'd' is 0, the |

| Words:       | 1                                                                                          |              | result is stored in the W register. If 'd' is 1,                                   |

| Cycles:      | 1                                                                                          |              | the result is stored back in register 'f'.                                         |

| Example 1:   | SUBLW 0x02                                                                                 | Words:       | 1                                                                                  |

|              | Before Instruction                                                                         | Cycles:      | 1                                                                                  |

|              |                                                                                            | Example 1:   | SUBWF REG1,1                                                                       |

|              | W = 1 $C = ?$                                                                              |              | Before Instruction                                                                 |

|              | After Instruction                                                                          |              | REG1 = 3                                                                           |

|              | W = 1                                                                                      |              | W = 2 $C = ?$                                                                      |

|              | C = 1; result is positive                                                                  |              | After Instruction                                                                  |

| Example 2:   | Before Instruction                                                                         |              | REG1 = 1                                                                           |

|              | W = 2                                                                                      |              | W = 2                                                                              |

|              | C = ?                                                                                      |              | C = 1; result is positive                                                          |

|              | After Instruction                                                                          | Example 2:   | Before Instruction                                                                 |

|              | W = 0<br>C = 1; result is zero                                                             |              | REG1 = 2<br>W = 2                                                                  |

| Example 3:   | Before Instruction                                                                         |              | C = ?                                                                              |

|              | W = 3                                                                                      |              | After Instruction                                                                  |

|              | C = ?                                                                                      |              | REG1 = 0                                                                           |

|              | After Instruction                                                                          |              | W = 2                                                                              |

|              | W = 0xFF                                                                                   | Evenuela Or  | C = 1; result is zero                                                              |

|              | C = 0; result is nega-<br>tive                                                             | Example 3:   | Before Instruction                                                                 |

|              |                                                                                            |              | REG1 = 1<br>W = 2                                                                  |

|              |                                                                                            |              | C = ?                                                                              |

|              |                                                                                            |              | After Instruction                                                                  |

|              |                                                                                            |              | REG1 = 0xFF                                                                        |

|              |                                                                                            |              | W = 2<br>C = 0; result is negative                                                 |

|              |                                                                                            |              |                                                                                    |

# 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM Assembler

- MPLAB-C17 and MPLAB-C18 C Compilers

- MPLINK/MPLIB Linker/Librarian

- Simulators

- MPLAB-SIM Software Simulator

- Emulators

- MPLAB-ICE Real-Time In-Circuit Emulator

- PICMASTER<sup>®</sup>/PICMASTER-CE In-Circuit Emulator

- ICEPIC™

- In-Circuit Debugger

- MPLAB-ICD for PIC16F877

- Device Programmers

- PRO MATE<sup>®</sup> II Universal Programmer

- PICSTART<sup>®</sup> Plus Entry-Level Prototype Programmer

- Low-Cost Demonstration Boards

- SIMICE

- PICDEM-1

- PICDEM-2

- PICDEM-3

- PICDEM-17

- SEEVAL®

- KEELOQ<sup>®</sup>

### 12.1 <u>MPLAB Integrated Development</u> <u>Environment Software</u>

The MPLAB IDE software brings an ease of software development previously unseen in the 8-bit microcontroller market. MPLAB is a Windows<sup>®</sup>-based application which contains:

- · Multiple functionality

- editor

- simulator

- programmer (sold separately)

- emulator (sold separately)

- A full featured editor

- A project manager

- Customizable tool bar and key mapping

- · A status bar

- On-line help

MPLAB allows you to:

- Edit your source files (either assembly or 'C')

- One touch assemble (or compile) and download to PIC MCU tools (automatically updates all project information)

- Debug using:

- source files

- absolute listing file

- object code

The ability to use MPLAB with Microchip's simulator, MPLAB-SIM, allows a consistent platform and the ability to easily switch from the cost-effective simulator to the full featured emulator with minimal retraining.

### 12.2 MPASM Assembler

MPASM is a full featured universal macro assembler for all PIC MCUs. It can produce absolute code directly in the form of HEX files for device programmers, or it can generate relocatable objects for MPLINK.

MPASM has a command line interface and a Windows shell and can be used as a standalone application on a Windows 3.x or greater system. MPASM generates relocatable object files, Intel standard HEX files, MAP files to detail memory usage and symbol reference, an absolute LST file which contains source lines and generated machine code, and a COD file for MPLAB debugging.

MPASM features include:

- MPASM and MPLINK are integrated into MPLAB projects.

- MPASM allows user defined macros to be created for streamlined assembly.

- MPASM allows conditional assembly for multi purpose source files.

- MPASM directives allow complete control over the assembly process.

### 12.3 <u>MPLAB-C17 and MPLAB-C18</u> <u>C Compilers</u>

The MPLAB-C17 and MPLAB-C18 Code Development Systems are complete ANSI 'C' compilers and integrated development environments for Microchip's PIC17CXXX and PIC18CXXX family of microcontrollers, respectively. These compilers provide powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compilers provide symbol information that is compatible with the MPLAB IDE memory display.

### 12.4 MPLINK/MPLIB Linker/Librarian

MPLINK is a relocatable linker for MPASM and MPLAB-C17 and MPLAB-C18. It can link relocatable objects from assembly or C source files along with precompiled libraries using directives from a linker script.

TABLE 12-1: DEVELOPMENT TOOLS FROM MICROCHIP

|                                                          | PIC120 | PIC14 | PIC160 | 91019 | PIC160 | PIC16F | PIC160         | PIC16C | PIC160 | PIC16F | PIC16C | DTFOIG | 22121919 | PIC18C | 83CX<br>52CX<br>54CX | кхээн | мсвгх | MCP25 |

|----------------------------------------------------------|--------|-------|--------|-------|--------|--------|----------------|--------|--------|--------|--------|--------|----------|--------|----------------------|-------|-------|-------|

| MPLAB <sup>®</sup> Integrated<br>Development Environment | >      | >     | >      | >     | >      | >      | >              | >      | >      | >      | >      | >      | >        | >      |                      |       |       |       |

|                                                          |        |       |        |       |        |        |                |        |        |        |        | >      | >        |        |                      |       |       |       |

| MPLAB <sup>®</sup> C18 Compiler                          |        |       |        |       |        |        |                |        |        |        |        |        |          | >      |                      |       |       |       |

| B MPASM/MPLINK                                           | >      | >     | >      | >     | >      | >      | >              | >      | >      | >      | >      | >      | >        | >      | >                    | >     |       |       |

| 2 MPLAB <sup>®</sup> -ICE                                | >      | >     | >      | >     | >      | **`    | >              | >      | >      | >      | >      | >      | >        | >      |                      |       |       |       |

| PICMASTER/PICMASTER-CE                                   | >      | >     | ~      | >     | >      |        | >              | >      | ~      |        | >      | ~      | ~        |        |                      |       |       |       |

| E ICEPIC™ Low-Cost<br>III In-Circuit Emulator            | `      |       | >      | >     | >      |        | >              | >      | >      |        | ~      |        |          |        |                      |       |       |       |

| MPLAB <sup>®</sup> -ICD In-Circuit<br>Debugger<br>De     |        |       |        | *>    |        |        | *              |        |        | >      |        |        |          |        |                      |       |       |       |

| 20 PICSTART®Plus<br>E Low-Cost Universal Dev. Kit        | ~      | >     | >      | `     | `      | ×**    | ~              | `      | `      | >      | >      | ~      | `        | `      |                      |       |       |       |

| ଅଟେ PRO MATE® I<br>Universal Programmer<br>ଦ             | >      | >     | >      | >     | >      | **/    | >              | >      | >      | >      | >      | ~      | ~        | ~      | >                    | >     |       |       |

| SIMICE                                                   | >      |       | >      |       |        |        |                |        |        |        |        |        |          |        |                      |       |       |       |

| PICDEM-1                                                 |        |       | >      |       | >      |        | ۲ <sup>+</sup> |        | >      |        |        | >      |          |        |                      |       |       |       |

| PICDEM-2                                                 |        |       |        | ∕†    |        |        | <↓<br>↓        |        |        |        |        |        |          | ~      |                      |       |       |       |

| 2 PICDEM-3                                               |        |       |        |       |        |        |                |        |        |        | ~      |        |          |        |                      |       |       |       |

| PICDEM-14A                                               |        | >     |        |       |        |        |                |        |        |        |        |        |          |        |                      |       |       |       |

| PICDEM-17                                                |        |       |        |       |        |        |                |        |        |        |        |        | ~        |        |                      |       |       |       |

| KEELOQ® Evaluation Kit                                   |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      | ~     |       |       |

| KEELOQ Transponder Kit                                   |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      | ~     |       |       |

| microlD™ Programmer's Kit                                |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       | ~     |       |

| 125 kHz microID Developer's Kit                          |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       | >     |       |

| 25 kHz Anticollision microlD<br>Developer's Kit          |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       | >     |       |

| 13.56 MHz Anticollision microID<br>Developer's Kit       |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       | >     |       |

| MCP2510 CAN Developer's Kit                              |        |       |        |       |        |        |                |        |        |        |        |        |          |        |                      |       |       | >     |

ğ Contact Microcrip reciniology inc. for availability <sup>†</sup> Development tool is available on select devices.

NOTES:

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

### Trademarks

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 1998-2013, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620769768

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEEL0Q® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and mulfacture of development systems is ISO 9001:2000 certified.

# Worldwide Sales and Service

### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431 Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

**India - New Delhi** Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

## EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820