# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betalls                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                      |

| Core Processor             | PIC                                                                           |

| Core Size                  | 8-Bit                                                                         |

| Speed                      | 4MHz                                                                          |

| Connectivity               | -                                                                             |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                              |

| Number of I/O              | 13                                                                            |

| Program Memory Size        | 1.75KB (1K x 14)                                                              |

| Program Memory Type        | OTP                                                                           |

| EEPROM Size                | 128 x 8                                                                       |

| RAM Size                   | 96 x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                   |

| Data Converters            | -                                                                             |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce624t-04i-ss |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### FIGURE 4-4: DATA MEMORY MAP FOR THE PIC16CE623/624

| File<br>Address | 3                                                                                         | -                   | File<br>Address |  |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------|---------------------|-----------------|--|--|--|--|--|

| 00h             | INDF <sup>(1)</sup>                                                                       | INDF <sup>(1)</sup> | 80h             |  |  |  |  |  |

| 01h             | TMR0                                                                                      | OPTION              | 81h             |  |  |  |  |  |

| 02h             | PCL                                                                                       | PCL                 | 82h             |  |  |  |  |  |

| 03h             | STATUS                                                                                    | STATUS              | 83h             |  |  |  |  |  |

| 04h             | FSR                                                                                       | FSR                 | 84h             |  |  |  |  |  |

| 05h             | PORTA                                                                                     | TRISA               | 85h             |  |  |  |  |  |

| 06h             | PORTB                                                                                     | TRISB               | 86h             |  |  |  |  |  |

| 07h             |                                                                                           |                     | 87h             |  |  |  |  |  |

| 08h             |                                                                                           |                     | 88h             |  |  |  |  |  |

| 09h             |                                                                                           |                     | 89h             |  |  |  |  |  |

| 0Ah             | PCLATH                                                                                    | PCLATH              | 8Ah             |  |  |  |  |  |

| 0Bh             | INTCON                                                                                    | INTCON              | 8Bh             |  |  |  |  |  |

| 0Ch             | PIR1                                                                                      | PIE1                | 8Ch             |  |  |  |  |  |

| 0Dh             |                                                                                           |                     | 8Dh             |  |  |  |  |  |

| 0Eh             |                                                                                           | PCON                | 8Eh             |  |  |  |  |  |

| 0Fh             |                                                                                           |                     | 8Fh             |  |  |  |  |  |

| 10h             |                                                                                           | EEINTF              | 90h             |  |  |  |  |  |

| 11h             |                                                                                           |                     | 91h             |  |  |  |  |  |

| 12h             |                                                                                           |                     | 92h             |  |  |  |  |  |

| 13h             |                                                                                           |                     | 93h             |  |  |  |  |  |

| 14h             |                                                                                           |                     | 94h             |  |  |  |  |  |

| 15h             |                                                                                           |                     | 95h             |  |  |  |  |  |

| 16h             |                                                                                           |                     | 96h             |  |  |  |  |  |

| 17h             |                                                                                           |                     | 97h             |  |  |  |  |  |

| 18h             |                                                                                           |                     | 98h             |  |  |  |  |  |

| 19h             |                                                                                           |                     | 99h             |  |  |  |  |  |

| 1Ah             |                                                                                           |                     | 9Ah             |  |  |  |  |  |

| 1Bh             |                                                                                           |                     | 9Bh             |  |  |  |  |  |

| 1Ch             |                                                                                           |                     | 9Ch             |  |  |  |  |  |

| 1Dh             |                                                                                           |                     | 9Dh             |  |  |  |  |  |

| 1Eh             |                                                                                           |                     | 9Eh             |  |  |  |  |  |

| 1Fh             | CMCON                                                                                     | VRCON               | 9Fh             |  |  |  |  |  |

| 20h             |                                                                                           |                     | A0h             |  |  |  |  |  |

|                 | General<br>Purpose<br>Register                                                            |                     |                 |  |  |  |  |  |

|                 |                                                                                           |                     |                 |  |  |  |  |  |

|                 |                                                                                           |                     | EFh             |  |  |  |  |  |

|                 |                                                                                           | Accesses            | F0h             |  |  |  |  |  |

| 7Fh             |                                                                                           | 70h-7Fh             | FFh             |  |  |  |  |  |

| / [1]           | Bank 0                                                                                    | Bank 1              |                 |  |  |  |  |  |

|                 | Unimplemented data memory locations, read as '0'. <b>Note 1:</b> Not a physical register. |                     |                 |  |  |  |  |  |

#### FIGURE 4-5: DATA MEMORY MAP FOR THE PIC16CE625

| File     |                      |                     | File       |

|----------|----------------------|---------------------|------------|

| Address  | ;                    |                     | Address    |

| 00h      | INDF <sup>(1)</sup>  | INDF <sup>(1)</sup> | 80h        |

| 01h      | TMR0                 | OPTION              | 81h        |

| 02h      | PCL                  | PCL                 | 82h        |

| 03h      | STATUS               | STATUS              | 83h        |

| 04h      | FSR                  | FSR                 | 84h        |

| 05h      | PORTA                | TRISA               | 85h        |

| 06h      | PORTB                | TRISB               | 86h        |

| 07h      |                      |                     | 87h        |

| 08h      |                      |                     | 88h        |

| 09h      |                      |                     | 89h        |

| 0Ah      | PCLATH               | PCLATH              | 8Ah        |

| 0Bh      | INTCON               | INTCON              | 8Bh        |

| 0Ch      | PIR1                 | PIE1                | 8Ch        |

| 0Dh      |                      |                     | 8Dh        |

| 0Eh      |                      | PCON                | 8Eh        |

| 0Fh      |                      |                     | 8Fh        |

| 10h      |                      | EEINTF              | 90h        |

| 11h      |                      |                     | 91h        |

| 12h      |                      |                     | 92h        |

| 13h      |                      |                     | 93h        |

| 14h      |                      |                     | 94h        |

| 15h      |                      |                     | 95h        |

| 16h      |                      |                     | 96h        |

| 17h      |                      |                     | 97h        |

| 18h      |                      |                     | 98h        |

| 19h      |                      |                     | 99h        |

| 1Ah      |                      |                     | 9Ah        |

| 1Bh      |                      |                     | 9Bh        |

| 1Ch      |                      |                     | 9Ch        |

| 1Dh      |                      |                     | 9Dh        |

| 1Eh      |                      |                     | 9Eh        |

| 1Fh      | CMCON                | VRCON               | 9Fh        |

| 20h      |                      |                     | A0h        |

|          | General              | General             | AUII       |

|          | Purpose<br>Register  | Purpose<br>Register |            |

|          | negistei             | negister            | BFh        |

|          |                      |                     | C0h        |

|          |                      |                     |            |

|          |                      | _                   | F0h        |

|          |                      | Accesses            |            |

| 751      |                      | 70h-7Fh             | FFh        |

| 7Fh I    | Bank 0               | Bank 1              | J FFN      |

| <b>—</b> |                      |                     |            |

|          | plemented data me    |                     | ad as '0'. |

| Note 1:  | Not a physical regis | ster.               |            |

#### 4.2.2.3 INTCON REGISTER

The INTCON register is a readable and writable register which contains the various enable and flag bits for all interrupt sources except the comparator module. See Section 4.2.2.4 and Section 4.2.2.5 for a description of the comparator enable and flag bits.

**Note:** Interrupt flag bits get set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE (INTCON<7>).

### REGISTER 4-3: INTCON REGISTER (ADDRESS 0BH OR 8BH)

| R/W-0       | R/W-0                                                                                                                                                                                                                                                                                          | R/W-0       | R/W-0                                   | R/W-0        | R/W-0     | R/W-0 | R/W-x        |                                                                                                                                       |  |  |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------|--------------|-----------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GIE<br>bit7 | PEIE                                                                                                                                                                                                                                                                                           | TOIE        | INTE                                    | RBIE         | TOIF      | INTF  | RBIF<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented bit,<br>read as '0'<br>-n = Value at POR reset<br>-x = Unknown at POR reset |  |  |

| bit 7:      |                                                                                                                                                                                                                                                                                                |             |                                         |              |           |       |              |                                                                                                                                       |  |  |

| bit 6:      |                                                                                                                                                                                                                                                                                                | es all un-r | terrupt En<br>masked pe<br>ipheral int  | eripheral ir | nterrupts |       |              |                                                                                                                                       |  |  |

| bit 5:      | <b>TOIE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enables the TMR0 interrupt<br>0 = Disables the TMR0 interrupt                                                                                                                                                                          |             |                                         |              |           |       |              |                                                                                                                                       |  |  |

| bit 4:      |                                                                                                                                                                                                                                                                                                | es the RB   | ernal Inter<br>0/INT exte<br>30/INT ext | ernal interi | rupt      |       |              |                                                                                                                                       |  |  |

| bit 3:      | <b>RBIE</b> : RB Port Change Interrupt Enable bit<br>1 = Enables the RB port change interrupt<br>0 = Disables the RB port change interrupt                                                                                                                                                     |             |                                         |              |           |       |              |                                                                                                                                       |  |  |

| bit 2:      | <ul> <li>T0IF: TMR0 Overflow Interrupt Flag bit</li> <li>1 = TMR0 register has overflowed (must be cleared in software)</li> <li>0 = TMR0 register did not overflow</li> </ul>                                                                                                                 |             |                                         |              |           |       |              |                                                                                                                                       |  |  |

| bit 1:      | INTF: RB0/INT External Interrupt Flag bit<br>1 = The RB0/INT external interrupt occurred (must be cleared in software)<br>0 = The RB0/INT external interrupt did not occur                                                                                                                     |             |                                         |              |           |       |              |                                                                                                                                       |  |  |

| bit 0:      | <ul> <li>a The RB0/INT external interrupt did not occur</li> <li><b>RBIF</b>: RB Port Change Interrupt Flag bit</li> <li>1 = When at least one of the RB&lt;7:4&gt; pins changed state (must be cleared in software)</li> <li>0 = None of the RB&lt;7:4&gt; pins have changed state</li> </ul> |             |                                         |              |           |       |              |                                                                                                                                       |  |  |

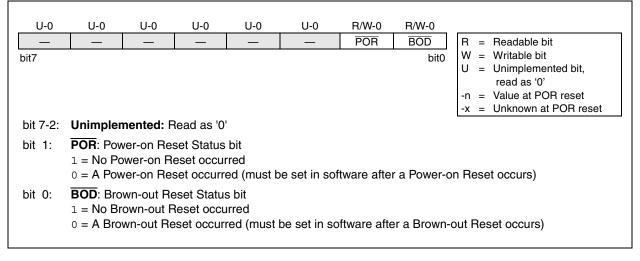

#### 4.2.2.6 PCON REGISTER

The PCON register contains flag bits to differentiate between a Power-on Reset, an external  $\overline{\text{MCLR}}$  reset, WDT reset or a Brown-out Reset.

| Note: | BOD is unknown on Power-on Reset. It        |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | must then be set by the user and checked    |  |  |  |  |  |  |  |

|       | on subsequent resets to see if BOD is       |  |  |  |  |  |  |  |

|       | cleared, indicating a brown-out has         |  |  |  |  |  |  |  |

|       | occurred. The BOD status bit is a "don't    |  |  |  |  |  |  |  |

|       | care" and is not necessarily predictable if |  |  |  |  |  |  |  |

|       | the brown-out circuit is disabled (by       |  |  |  |  |  |  |  |

|       | programming BODEN bit in the                |  |  |  |  |  |  |  |

|       | configuration word).                        |  |  |  |  |  |  |  |

# REGISTER 4-6: PCON REGISTER (ADDRESS 8Eh)

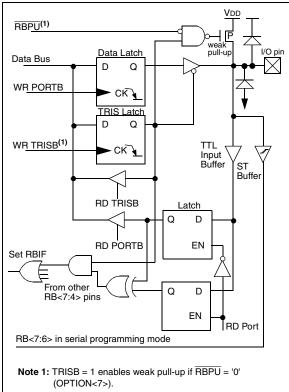

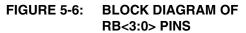

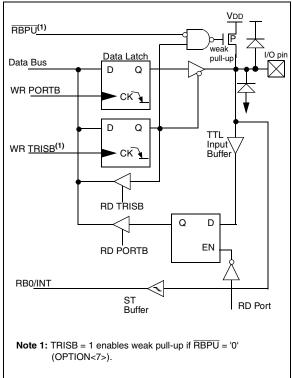

# 5.2 PORTB and TRISB Registers

PORTB is an 8-bit wide, bi-directional port. The corresponding data direction register is TRISB. A '1' in the TRISB register puts the corresponding output driver in a high impedance mode. A '0' in the TRISB register puts the contents of the output latch on the selected pin(s).

Reading PORTB register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. So a write to a port implies that the port pins are first read, then this value is modified and written to the port data latch.

Each of the PORTB pins has a weak internal pull-up ( $\approx 200 \ \mu A$  typical). A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{RBPU}$  (OPTION<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on Power-on Reset.

Four of PORTB's pins, RB<7:4>, have an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt on change comparison). The input pins of RB<7:4> are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are OR'ed together to generate the RBIF interrupt (flag latched in INTCON<0>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB. This will end the mismatch condition.

- b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will end the mismatch condition and allow flag bit RBIF to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on these four pins allow easy interface to a key pad and make it possible for wake-up on key-depression. (See AN552, "Implementing Wake-Up on Key Strokes".)

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

The interrupt on change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt on change feature. Polling of PORTB is not recommended while using the interrupt on change feature.

## 5.3 <u>I/O Programming Considerations</u>

#### 5.3.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. The BCF and BSF instructions, for example, read the register into the CPU, execute the bit operation and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bidirectional I/O pin (i.e., bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading the port register, reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read modify write instructions (i.e., BCF, BSF, etc.) on a port, the value of the port pins is read, the desired operation is done to this value, and this value is then written to the port latch.

Example 5-2 shows the effect of two sequential read-modify-write instructions (i.e.,  ${\tt BCF}\,,\ {\tt BSF},$  etc.) on an I/O port

A pin actively outputting a Low or High should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

#### EXAMPLE 5-2: READ-MODIFY-WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs ; PORTB<3:0> Outputs ; ; PORTB<7:6> have external pull-up and are not ; connected to other circuitry ; PORT latch PORT pins ; ; BCF PORTB. 7 ; 01pp pppp 11pp pppp BCF PORTB, 6 ; 10pp pppp 11pp pppp BSF STATUS, RPO ; BCF TRISB, 7 ; 10pp pppp 11pp pppp BCF TRISB, 6 ;10pp pppp 10pp pppp ; ; Note that the user may have expected the pin

; values to be 00pp pppp. The 2nd BCF caused ; RB7 to be latched as the pin value (High).

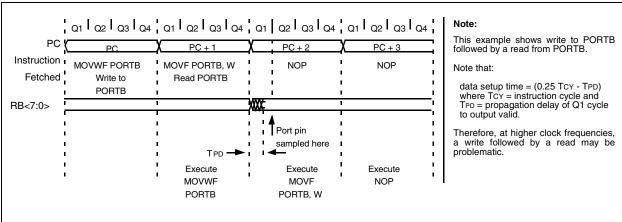

#### 5.3.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-7). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with an NOP or another instruction not accessing this I/O port.

#### FIGURE 5-7: SUCCESSIVE I/O OPERATION

#### 6.3 Write Operations

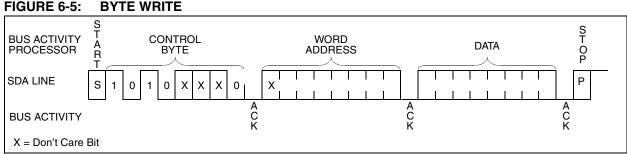

#### BYTE WRITE 6.3.1

Following the start signal from the processor, the device code (4 bits), the don't care bits (3 bits), and the R/W bit, which is a logic low, is placed onto the bus by the processor. This indicates to the EEPROM that a byte with a word address will follow after it has generated an acknowledge bit during the ninth clock cycle. Therefore, the next byte transmitted by the processor is the word address and will be written into the address pointer of the EEPROM. After receiving another acknowledge signal from the EEPROM, the processor will transmit the data word to be written into the addressed memory location. The EEPROM acknowledges again and the processor generates a stop condition. This initiates the internal write cycle, and during this time, the EEPROM will not generate acknowledge signals (Figure 6-5).

#### 6.3.2 PAGE WRITE

The write control byte, word address and the first data byte are transmitted to the EEPROM in the same way as in a byte write. But instead of generating a stop condition, the processor transmits up to eight data bytes to the EEPROM, which are temporarily stored in the onchip page buffer and will be written into the memory after the processor has transmitted a stop condition. After the receipt of each word, the three lower order address pointer bits are internally incremented by one. The higher order five bits of the word address remains constant. If the processor should transmit more than eight words prior to generating the stop condition, the address counter will roll over and the previously received data will be overwritten. As with the byte write operation, once the stop condition is received, an internal write cycle will begin (Figure 6-6).

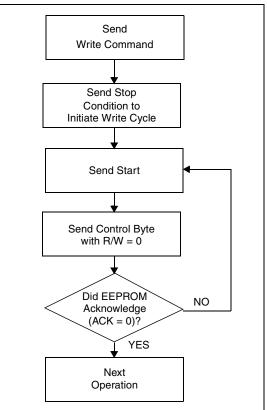

#### 6.4 Acknowledge Polling

Since the EEPROM will not acknowledge during a write cycle, this can be used to determine when the cycle is complete (this feature can be used to maximize bus throughput). Once the stop condition for a write command has been issued from the processor, the EEPROM initiates the internally timed write cycle. ACK polling can be initiated immediately. This involves the processor sending a start condition followed by the control byte for a write command (R/W = 0). If the device is still busy with the write cycle, then no ACK will be returned. If no ACK is returned, then the start bit and control byte must be re-sent. If the cycle is complete, then the device will return the ACK and the processor can then proceed with the next read or write command. See Figure 6-4 for flow diagram.

#### FIGURE 6-4: ACKNOWLEDGE POLLING FLOW

## FIGURE 6-5:

#### 7.3.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device RESET, the following instruction sequence (Example 7-1) must be executed when changing the prescaler assignment from Timer0 to WDT.

# EXAMPLE 7-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| 1.BCF    | STATUS, RPO | ;Skip if already in      |

|----------|-------------|--------------------------|

|          |             | ; Bank 0                 |

| 2.CLRWDT |             | ;Clear WDT               |

| 3.CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| 4.BSF    | STATUS, RPO | ;Bank 1                  |

| 5.MOVLW  | '00101111'b | ;These 3 lines (5, 6, 7) |

| 6.MOVWF  | OPTION      | ; are required only if   |

|          |             | ; desired PS<2:0> are    |

| 7.CLRWDT |             | ; 000 or 001             |

| 8.MOVLW  | '00101xxx'b | ;Set Postscaler to       |

| 9.MOVWF  | OPTION      | ; desired WDT rate       |

| 10.BCF   | STATUS, RPO | ;Return to Bank 0        |

|          |             |                          |

To change prescaler from the WDT to the TMR0 module, use the sequence shown in Example 7-2. This precaution must be taken even if the WDT is disabled.

# EXAMPLE 7-2: CHANGING PRESCALER (WDT $\rightarrow$ TIMER0)

| CLRWDT |             | ;Clear WDT and<br>;prescaler |

|--------|-------------|------------------------------|

|        |             | /prebearer                   |

| BSF    | STATUS, RPO |                              |

| MOVLW  | b'xxxx0xxx' | ;Select TMR0, new            |

|        |             | ;prescale value and          |

|        |             | ;clock source                |

| MOVWF  | OPTION_REG  |                              |

| BCF    | STATUS, RPO |                              |

## TABLE 7-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name                        | Bit 7 | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0     | Value on:<br>POR | Value on<br>All Other<br>Resets |

|---------|-----------------------------|-------|--------|-------|--------|--------|--------|--------|-----------|------------------|---------------------------------|

| 01h     | TMR0 Timer0 module register |       |        |       |        |        |        |        | xxxx xxxx | uuuu uuuu        |                                 |

| 0Bh/8Bh | INTCON                      | GIE   | PEIE   | T0IE  | INTE   | RBIE   | T0IF   | INTF   | RBIF      | 0000 000x        | 0000 000u                       |

| 81h     | OPTION                      | RBPU  | INTEDG | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0       | 1111 1111        | 1111 1111                       |

| 85h     | TRISA                       |       |        | _     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0    | 1 1111           | 1 1111                          |

Legend: — = Unimplemented locations, read as '0', x = unknown, u = unchanged.

Note: Shaded bits are not used by TMR0 module.

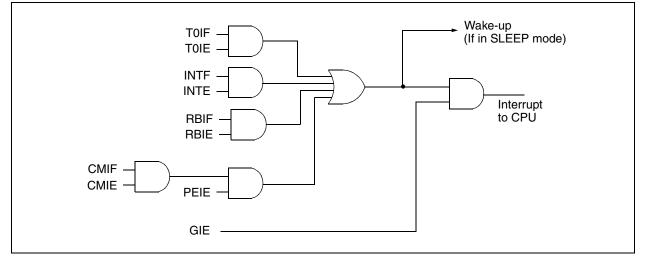

### 8.6 Comparator Interrupts

The comparator interrupt flag is set whenever there is a change in the output value of either comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<7:6>, to determine the actual change that has occurred. The CMIF bit, PIR1<6>, is the comparator interrupt flag. The CMIF bit must be reset by clearing '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

The CMIE bit (PIE1<6>) and the PEIE bit (INTCON<6>) must be set to enable the interrupt. In addition, the GIE bit must also be set. If any of these bits are clear, the interrupt is not enabled, though the CMIF bit will still be set if an interrupt condition occurs.

Note: If a change in the CMCON register (C1OUT or C2OUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CMIF (PIR1<6>) interrupt flag may not get set.

The user, in the interrupt service routine, can clear the interrupt in the following manner:

- a) Any read or write of CMCON. This will end the mismatch condition.

- b) Clear flag bit CMIF.

A mismatch condition will continue to set flag bit CMIF. Reading CMCON will end the mismatch condition, and allow flag bit CMIF to be cleared.

# 8.7 <u>Comparator Operation During SLEEP</u>

When a comparator is active and the device is placed in SLEEP mode, the comparator remains active and the interrupt is functional if enabled. This interrupt will wake-up the device from SLEEP mode when enabled. While the comparator is powered-up, higher sleep currents than shown in the power down current specification will occur. Each comparator that is operational will consume additional current as shown in the comparator specifications. To minimize power consumption while in SLEEP mode, turn off the comparators, CM<2:0> = 111, before entering sleep. If the device wakes-up from sleep, the contents of the CMCON register are not affected.

# 8.8 Effects of a RESET

A device reset forces the CMCON register to its reset state. This forces the comparator module to be in the comparator reset mode, CM<2:0> = 000. This ensures that all potential inputs are analog inputs. Device current is minimized when analog inputs are present at reset time. The comparators will be powered-down during the reset interval.

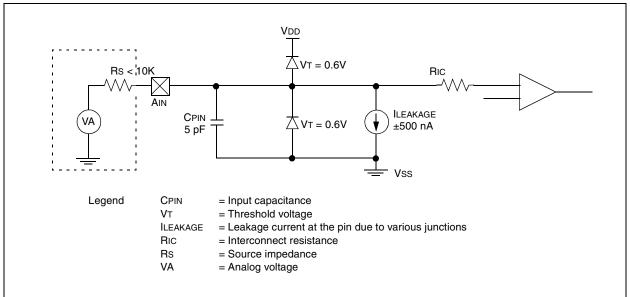

# 8.9 <u>Analog Input Connection</u> <u>Considerations</u>

A simplified circuit for an analog input is shown in Figure 8-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur. A maximum source impedance of 10 k $\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

## FIGURE 8-4: ANALOG INPUT MODEL

| Name   | Bit 7                                    | Bit 6                                                   | Bit 5                                                       | Bit 4                                                            | Bit 3                                                                        | Bit 2                                                                                     | Bit 1                                                                                                 | Bit 0                                                                                                             | Value on:<br>POR                                                                                                              | Value on<br>All Other<br>Resets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMCON  | C2OUT                                    | C1OUT                                                   |                                                             | _                                                                | CIS                                                                          | CM2                                                                                       | CM1                                                                                                   | CM0                                                                                                               | 00 0000                                                                                                                       | 00 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| VRCON  | VREN                                     | VROE                                                    | VRR                                                         | —                                                                | VR3                                                                          | VR2                                                                                       | VR1                                                                                                   | VR0                                                                                                               | 000- 0000                                                                                                                     | 000- 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTCON | GIE                                      | PEIE                                                    | TOIE                                                        | INTE                                                             | RBIE                                                                         | T0IF                                                                                      | INTF                                                                                                  | RBIF                                                                                                              | 0000 000x                                                                                                                     | 0000 000u                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PIR1   | _                                        | CMIF                                                    |                                                             | _                                                                | _                                                                            |                                                                                           | _                                                                                                     | _                                                                                                                 | -0                                                                                                                            | -0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PIE1   | —                                        | CMIE                                                    | —                                                           | —                                                                | —                                                                            | —                                                                                         | —                                                                                                     | —                                                                                                                 | -0                                                                                                                            | -0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TRISA  | —                                        | —                                                       | _                                                           | TRISA4                                                           | TRISA3                                                                       | TRISA2                                                                                    | TRISA1                                                                                                | TRISA0                                                                                                            | 1 1111                                                                                                                        | 1 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        | CMCON<br>VRCON<br>INTCON<br>PIR1<br>PIE1 | CMCON C2OUT<br>VRCON VREN<br>INTCON GIE<br>PIR1<br>PIE1 | CMCONC2OUTC1OUTVRCONVRENVROEINTCONGIEPEIEPIR1—CMIFPIE1—CMIE | CMCONC2OUTC1OUTVRCONVRENVROEVRRINTCONGIEPEIETOIEPIR1CMIFPIE1CMIE | CMCONC2OUTC1OUT—VRCONVRENVROEVRR—INTCONGIEPEIETOIEINTEPIR1—CMIF——PIE1I—CMIEI | CMCONC2OUTC1OUT——CISVRCONVRENVROEVRR—VR3INTCONGIEPEIET0IEINTERBIEPIR1—CMIF———PIE1—CMIE——— | CMCONC2OUTC1OUT——CISCM2VRCONVRENVROEVRR—VR3VR2INTCONGIEPEIETOIEINTERBIETOIFPIR1—CMIF————PIE1—CMIE———— | CMCONC2OUTC1OUT——CISCM2CM1VRCONVRENVROEVRR—VR3VR2VR1INTCONGIEPEIET0IEINTERBIET0IFINTFPIR1—CMIF—————PIE1—CMIE————— | CMCONC2OUTC1OUT——CISCM2CM1CM0VRCONVRENVROEVRR—VR3VR2VR1VR0INTCONGIEPEIETOIEINTERBIETOIFINTFRBIFPIR1—CMIF——————PIE1—CMIE—————— | Name         Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0         POR           CMCON         C2OUT         C1OUT         —         —         CIS         CM2         CM1         CM0         00 0000           VRCON         VREN         VROE         VRR         —         VR3         VR2         VR1         VR0         000- 0000           INTCON         GIE         PEIE         TOIE         INTE         RBIE         TOIF         INTF         RBIF         0000 000x           PIR1         —         CMIE         —         —         —         —         —         -         -0         -0           PIE1         —         CMIE         —         —         —         —         —         -         -0         - |

TABLE 8-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

Legend: - = Unimplemented, read as "0", x = Unknown, u = unchanged

# TABLE 10-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set and the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

### TABLE 10-6: INITIALIZATION CONDITION FOR REGISTERS

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | -       | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| INDF     | 00h     | -              | -                                                                                                                                                          | -                                                                                                                 |

| TMR0     | 01h     | XXXX XXXX      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | x000 0000      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | นนนน นนนน                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| EEINTF   | 90h     | 111            | 111                                                                                                                                                        | 111                                                                                                               |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 10-5 for reset value for specific condition.

5: If wake-up was due to comparator input changing , then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

6: If reset was due to brown-out, then PCON bit 0 = 0. All other resets will cause bit 0 = u.

### 10.5 Interrupts

The PIC16CE62X has 4 sources of interrupt:

- External interrupt RB0/INT

- TMR0 overflow interrupt

- PortB change interrupts (pins RB<7:4>)

- · Comparator interrupt

The interrupt control register (INTCON) records individual interrupt requests in flag bits. It also has individual and global interrupt enable bits.

A global interrupt enable bit, GIE (INTCON<7>) enables (if set) all un-masked interrupts or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in INTCON register. GIE is cleared on reset.

The "return from interrupt" instruction, RETFIE, exits interrupt routine, as well as sets the GIE bit, which re-enable RB0/INT interrupts.

The INT pin interrupt, the RB port change interrupt and the TMR0 overflow interrupt flags are contained in the INTCON register.

The peripheral interrupt flag is contained in the special register PIR1. The corresponding interrupt enable bit is contained in special registers PIE1.

When an interrupt is responded to, the GIE is cleared to disable any further interrupt, the return address is pushed into the stack and the PC is loaded with 0004h. Once in the interrupt service routine, the source(s) of

the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid RB0/INT recursive interrupts.

For external interrupt events, such as the INT pin or PORTB change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends on when the interrupt event occurs (Figure 10-16). The latency is the same for one or two cycle instructions. Once in the interrupt service routine the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The CPU will execute a NOP in the cycle immediately following the instruction which clears the GIE bit. The interrupts which were ignored are still pending to be serviced when the GIE bit is set again.

## FIGURE 10-15: INTERRUPT LOGIC

# TABLE 11-2: PIC16CE62X INSTRUCTION SET

| Mnemonic, |         | Description                                     | Cycles | 14-Bit Opcode |              |      |              | Status          | Notes |

|-----------|---------|-------------------------------------------------|--------|---------------|--------------|------|--------------|-----------------|-------|

| Operands  |         |                                                 |        | MSb           |              | LSb  |              | Affected        |       |

| BYTE-ORIE | INTED   | FILE REGISTER OPERATIONS                        |        |               |              |      |              |                 |       |

| ADDWF     | f, d    | Add W and f                                     | 1      | 00            | 0111         | dfff | ffff         | C,DC,Z          | 1,2   |

| ANDWF     | f, d    | AND W with f                                    | 1      | 00            | 0101         | dfff | ffff         | Z               | 1,2   |

| CLRF      | f       | Clear f                                         | 1      | 00            | 0001         | lfff | ffff         | Z               | 2     |

| CLRW      | -       | Clear W                                         | 1      | 00            | 0001         | 0000 | 0011         | Z               |       |

| COMF      | f, d    | Complement f                                    | 1      | 00            | 1001         | dfff | ffff         | Z               | 1,2   |

| DECF      | f, d    | Decrement f                                     | 1      | 00            | 0011         | dfff | ffff         | Z               | 1,2   |

| DECFSZ    | f, d    | Decrement f, Skip if 0                          | 1(2)   | 00            | 1011         | dfff | ffff         |                 | 1,2,  |

| INCF      | f, d    | Increment f                                     | 1      | 00            | 1010         | dfff | ffff         | Z               | 1,2   |

| INCFSZ    | f, d    | Increment f, Skip if 0                          | 1(2)   | 00            | 1111         | dfff | ffff         |                 | 1,2,  |

| IORWF     | f, d    | Inclusive OR W with f                           | 1      | 00            | 0100         | dfff | ffff         | Z               | 1,2   |

| MOVF      | f, d    | Move f                                          | 1      | 00            | 1000         | dfff | ffff         | Z               | 1,2   |

| MOVWF     | f       | Move W to f                                     | 1      | 00            | 0000         | lfff | ffff         |                 |       |

| NOP       | -       | No Operation                                    | 1      | 00            | 0000         | 0xx0 | 0000         |                 |       |

| RLF       | f, d    | Rotate Left f through Carry                     | 1      | 00            | 1101         | dfff | ffff         | С               | 1,2   |

| RRF       | f, d    | Rotate Right f through Carry                    | 1      | 00            | 1100         | dfff | ffff         | С               | 1,2   |

| SUBWF     | f, d    | Subtract W from f                               | 1      | 00            | 0010         | dfff | ffff         | C,DC,Z          | 1,2   |

| SWAPF     | f, d    | Swap nibbles in f                               | 1      | 00            | 1110         | dfff | ffff         |                 | 1,2   |

| XORWF     | f, d    | Exclusive OR W with f                           | 1      | 00            | 0110         | dfff | ffff         | Z               | 1,2   |

| BIT-ORIEN | TED FIL | E REGISTER OPERATIONS                           |        | •             |              |      |              |                 |       |

| BCF       | f, b    | Bit Clear f                                     | 1      | 01            | 00bb         | bfff | ffff         |                 | 1,2   |

| BSF       | f, b    | Bit Set f                                       | 1      | 01            | 01bb         | bfff | ffff         |                 | 1,2   |

| BTFSC     | f, b    | Bit Test f, Skip if Clear                       | 1 (2)  | 01            | 10bb         | bfff | ffff         |                 | 3     |

| BTFSS     | f, b    | Bit Test f, Skip if Set                         | 1 (2)  | 01            | 11bb         | bfff | ffff         |                 | 3     |

| LITERAL A | ND CO   | NTROL OPERATIONS                                |        |               |              |      |              |                 |       |

| ADDLW     | k       | Add literal and W                               | 1      | 11            | 111x         | kkkk | kkkk         | C,DC,Z          |       |

| ANDLW     | k       | AND literal with W                              | 1      | 11            | 1001         | kkkk | kkkk         | Z               |       |

| CALL      | k       | Call subroutine                                 | 2      | 10            | 0kkk         | kkkk | kkkk         |                 |       |

| CLRWDT    | -       | Clear Watchdog Timer                            | 1      | 00            | 0000         | 0110 | 0100         | TO,PD           |       |

| GOTO      | k       | Go to address                                   | 2      | 10            | 1kkk         | kkkk | kkkk         |                 |       |

| IORLW     | k       | Inclusive OR literal with W                     | 1      | 11            | 1000         | kkkk | kkkk         | Z               |       |

| MOVLW     | k       | Move literal to W                               | 1      | 11            | 00xx         | kkkk | kkkk         |                 |       |

| RETFIE    | -       | Return from interrupt                           | 2      | 00            | 0000         | 0000 | 1001         |                 |       |

| RETLW     | k       | Return with literal in W                        | 2      | 11            | 01xx         | kkkk | kkkk         |                 |       |

|           | -       | Return from Subroutine                          | 2      | 00            | 0000         | 0000 | 1000         |                 |       |

| RETURN    |         |                                                 | 1      | 1             |              |      |              | I               | 1     |

|           | -       | Go into standby mode                            | 1      | 00            | 0000         | 0110 | 0011         | TO,PD           |       |

| RETURN    | -<br>k  | Go into standby mode<br>Subtract W from literal | 1      | 00<br>11      | 0000<br>110x |      | 0011<br>kkkk | TO,PD<br>C,DC,Z |       |

Note 1: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 Module.

**3:** If Program Counter (PC) is modified or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

# 11.1 Instruction Descriptions

| ADDLW            | Add Literal and W                          |                   |                |         |  |  |  |

|------------------|--------------------------------------------|-------------------|----------------|---------|--|--|--|

| Syntax:          | [label] A                                  | ADDLW             | k              |         |  |  |  |

| Operands:        | $0 \le k \le 25$                           | $0 \le k \le 255$ |                |         |  |  |  |

| Operation:       | (W) + k –                                  | → (W)             |                |         |  |  |  |

| Status Affected: | C, DC, Z                                   |                   |                |         |  |  |  |

| Encoding:        | 11                                         | 111x              | kkkk           | kkkk    |  |  |  |

| Description:     | The conter<br>added to th<br>result is pla | ne eight b        | it literal 'k' | and the |  |  |  |

| Words:           | 1                                          |                   |                |         |  |  |  |

| Cycles:          | 1                                          |                   |                |         |  |  |  |

| Example          | ADDLW                                      | 0x15              |                |         |  |  |  |

|                  | After Inst                                 | W =               | 0x10<br>0x25   |         |  |  |  |

| ANDLW            | AND Literal with W                                                                                                  |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                     |

| Status Affected: | Z                                                                                                                   |

| Encoding:        | 11 1001 kkkk kkkk                                                                                                   |

| Description:     | The contents of W register are<br>AND'ed with the eight bit literal 'k'. The<br>result is placed in the W register. |

| Words:           | 1                                                                                                                   |

| Cycles:          | 1                                                                                                                   |

| Example          | ANDLW 0x5F                                                                                                          |

|                  | Before Instruction<br>W = 0xA3<br>After Instruction<br>W = 0x03                                                     |

| ADDWF            | Add W and f                                                                                                                                                                 |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                           |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | $(W) + (f) \to (dest)$                                                                                                                                                      |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                    |  |  |  |  |  |

| Encoding:        | 00 0111 dfff ffff                                                                                                                                                           |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is 0, the result is<br>stored in the W register. If 'd' is 1, the<br>result is stored back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                           |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                           |  |  |  |  |  |

| Example          | ADDWF FSR, 0                                                                                                                                                                |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0xD9<br>FSR = 0xC2                                                                                 |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                             |  |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (dest)                                                                                                                          |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                           |  |  |  |  |  |

| Encoding:        | 00 0101 dfff ffff                                                                                                                                           |  |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is 0, the result is stored in the W<br>register. If 'd' is 1, the result is stored<br>back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                           |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                           |  |  |  |  |  |

| Example          | ANDWF FSR, 1                                                                                                                                                |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x17<br>FSR = 0xC2<br>After Instruction<br>W = 0x17<br>FSR = 0x02                                                                 |  |  |  |  |  |

# PIC16CE62X

| RETURN             | Return from Subroutine                                                                                          | RRF              | Rotate Right f through Carry                                                                                                                                                                                                                                                                                 |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:            | [label] RETURN                                                                                                  | Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                                                                                                     |  |  |  |

| Operands:          | None                                                                                                            | Operands:        | $0 \le f \le 127$                                                                                                                                                                                                                                                                                            |  |  |  |