Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | -                                                                            |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                             |

| Number of I/O              | 13                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | OTP                                                                          |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 128 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                  |

| Data Converters            | -                                                                            |

| Oscillator Type            | External                                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                               |

| Supplier Device Package    | 18-SOIC                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lce625-04e-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

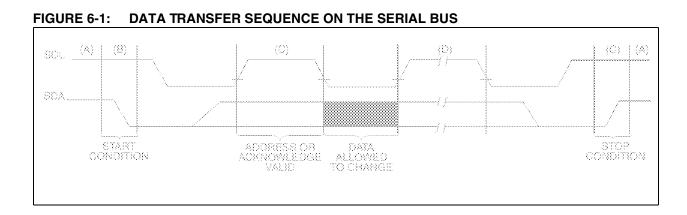

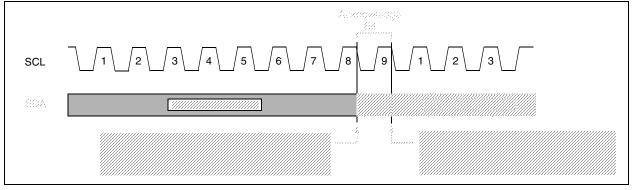

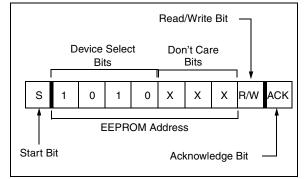

#### 6.2 Device Addressing

After generating a START condition, the processor transmits a control byte consisting of a EEPROM address and a Read/Write bit that indicates what type of operation is to be performed. The EEPROM address consists of a 4-bit device code (1010) followed by three don't care bits.

The last bit of the control byte determines the operation to be performed. When set to a one, a read operation is selected, and when set to a zero, a write operation is selected. (Figure 6-3). The bus is monitored for its corresponding EEPROM address all the time. It generates an acknowledge bit if the EEPROM address was true and it is not in a programming mode.

#### FIGURE 6-3: CONTROL BYTE FORMAT

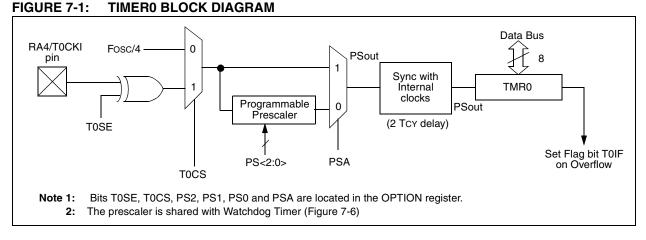

# 7.0 TIMER0 MODULE

The Timer0 module timer/counter has the following features:

- 8-bit timer/counter

- Readable and writable

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Figure 7-1 is a simplified block diagram of the Timer0 module.

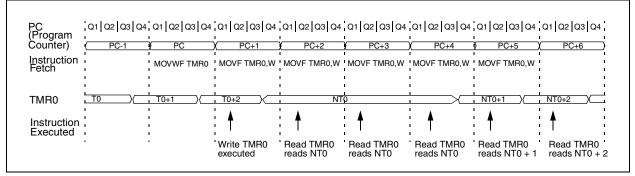

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In timer mode, the TMR0 will increment every instruction cycle (without prescaler). If Timer0 is written, the increment is inhibited for the following two cycles (Figure 7-2 and Figure 7-3). The user can work around this by writing an adjusted value to TMR0.

Counter mode is selected by setting the T0CS bit. In this mode Timer0 will increment either on every rising or falling edge of pin RA4/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION<4>). Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 7.2.

The prescaler is shared between the Timer0 module and the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale value of 1:2, 1:4, ..., 1:256 are selectable. Section 7.3 details the operation of the prescaler.

#### 7.1 <u>Timer0 Interrupt</u>

Timer0 interrupt is generated when the TMR0 register timer/counter overflows from FFh to 00h. This overflow sets the T0IF bit. The interrupt can be masked by clearing the T0IE bit (INTCON<5>). The T0IF bit (INTCON<2>) must be cleared in software by the Timer0 module interrupt service routine before re-enabling this interrupt. The Timer0 interrupt cannot wake the processor from SLEEP since the timer is shut off during SLEEP. See Figure 7-4 for Timer0 interrupt timing.

#### FIGURE 7-2: TIMER0 (TMR0) TIMING: INTERNAL CLOCK/NO PRESCALER

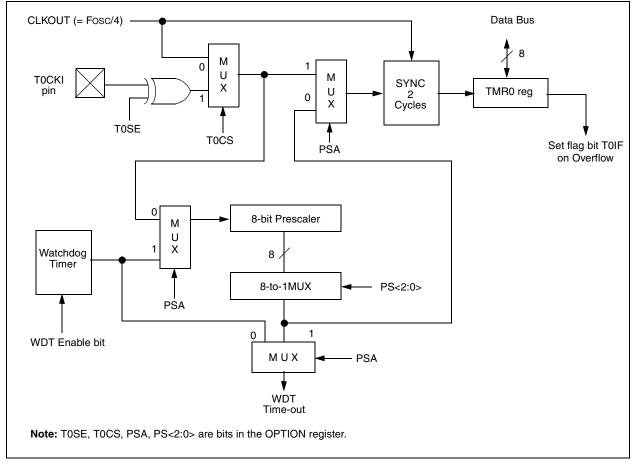

#### 7.3 <u>Prescaler</u>

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer, respectively (Figure 7-6). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet. Note that there is only one prescaler available which is mutually exclusive between the Timer0 module and the Watchdog Timer. Thus, a prescaler assignment for the Timer0 module means that there is no prescaler for the Watchdog Timer and vice-versa.

The PSA and PS<2:0> bits (OPTION<3:0>) determine the prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (i.e., CLRF 1, MOVWF 1, BSF 1, x....etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler is not readable or writable.

#### FIGURE 7-6: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

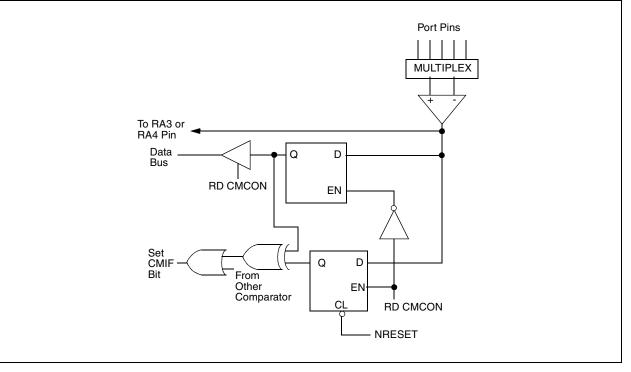

# 8.0 COMPARATOR MODULE

The comparator module contains two analog comparators. The inputs to the comparators are multiplexed with the RA0 through RA3 pins. The on-chip voltage reference (Section 9.0) can also be an input to the comparators.

The CMCON register, shown in Register 8-1, controls the comparator input and output multiplexers. A block diagram of the comparator is shown in Figure 8-1.

| R-0           | R-0                                                                                                                    | U-0                                                           | U-0                                                                          | R/W-0                      | R/W-0 | R/W-0 | R/W-0       |                                                                                                                                                |

|---------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------|-------|-------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| C2OUT<br>bit7 | C1OUT                                                                                                                  |                                                               | _                                                                            | CIS                        | CM2   | CM1   | CM0<br>bit0 | <ul> <li>R = Readable bit</li> <li>W = Writable bit</li> <li>U = Unimplemented bit,<br/>read as '0'</li> <li>n = Value at POR reset</li> </ul> |

| bit 7:        | <b>C2OUT</b> : Con<br>1 = C2 VIN+<br>0 = C2 VIN+                                                                       | > C2 V                                                        | 'IN—                                                                         | out                        |       |       |             |                                                                                                                                                |

| bit 6:        | <b>C1OUT</b> : Con<br>1 = C1 VIN+<br>0 = C1 VIN+                                                                       | > C1 V                                                        | 'IN—                                                                         | out                        |       |       |             |                                                                                                                                                |

| bit 5-4:      | Unimpleme                                                                                                              | nted: F                                                       | Read as                                                                      | '0'                        |       |       |             |                                                                                                                                                |

| bit 3:        | CIS: Compa<br>When CM<2<br>1 = C1 VIN-<br>0 = C1 VIN-<br>When CM<2<br>1 = C1 VIN-<br>C2 VIN-<br>0 = C1 VIN-<br>C2 VIN- | 2:0>: = 0<br>connec<br>connec<br>2:0> = 0<br>connec<br>connec | 001:<br>tts to RA<br>tts to RA<br>10:<br>tts to RA<br>tts to RA<br>tts to RA | 43<br>40<br>43<br>42<br>40 |       |       |             |                                                                                                                                                |

| bit 2-0:      | <b>CM&lt;2:0&gt;</b> : C<br>Figure 8-1.                                                                                | ompara                                                        | ator mod                                                                     | le                         |       |       |             |                                                                                                                                                |

### REGISTER 8-1: CMCON REGISTER (ADDRESS 1Fh)

#### 8.4 Comparator Response Time

Response time is the minimum time, after selecting a new reference voltage or input source, before the comparator output has a valid level. If the internal reference is changed, the maximum delay of the internal voltage reference must be considered when using the comparator outputs, otherwise the maximum delay of the comparators should be used (Table 13-1).

#### 8.5 <u>Comparator Outputs</u>

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 8-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/disable for the RA3 and RA4 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 8-3: COMPARATOR OUTPUT BLOCK DIAGRAM

# 10.0 SPECIAL FEATURES OF THE CPU

Special circuits to deal with the needs of real time applications are what sets a microcontroller apart from other processors. The PIC16CE62X family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection.

These are:

- 1. OSC selection

- 2. Reset

Power-on Reset (POR) Power-up Timer (PWRT) Oscillator Start-Up Timer (OST) Brown-out Reset (BOD)

- 3. Interrupts

- 4. Watchdog Timer (WDT)

- 5. SLEEP

- 6. Code protection

- 7. ID Locations

- 8. In-circuit serial programming

The PIC16CE62X has a Watchdog Timer which is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, and is designed to keep the part in reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which provides at least a 72 ms reset. With these three functions on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake-up from SLEEP through external reset, Watchdog Timer wake-up or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost, while the LP crystal option saves power. A set of configuration bits are used to select various options.

#### 10.3 <u>Reset</u>

The PIC16CE62X differentiates between various kinds of reset:

- a) Power-on reset (POR)

- b) MCLR reset during normal operation

- c) MCLR reset during SLEEP

- d) WDT reset (normal operation)

- e) WDT wake-up (SLEEP)

- f) Brown-out Reset (BOD)

Some registers are not affected in any reset condition. Their status is unknown on POR and unchanged in any other reset. Most other registers are reset to a "reset state" on Power-on reset, MCLR reset, WDT reset and MCLR reset during SLEEP. They are not affected by a WDT wake-up, since this is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different reset situations as indicated in Table 10-4. These bits are used in software to determine the nature of the reset. See Table 10-6 for a full description of reset states of all registers.

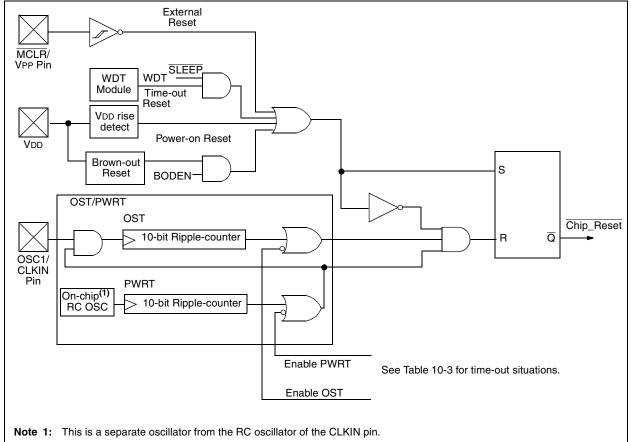

A simplified block diagram of the on-chip reset circuit is shown in Figure 10-6.

The  $\overline{\text{MCLR}}$  reset path has a noise filter to detect and ignore small pulses. See Table 13-5 for pulse width specification.

#### FIGURE 10-6: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### TABLE 10-5: INITIALIZATION CONDITION FOR SPECIAL REGISTERS

| Condition                          | Program<br>Counter    | STATUS<br>Register | PCON<br>Register |

|------------------------------------|-----------------------|--------------------|------------------|

| Power-on Reset                     | 000h                  | 0001 1xxx          | 0x               |

| MCLR reset during normal operation | 000h                  | 000u uuuu          | uu               |

| MCLR reset during SLEEP            | 000h                  | 0001 0uuu          | uu               |

| WDT reset                          | 000h                  | 0000 uuuu          | uu               |

| WDT Wake-up                        | PC + 1                | uuu0 0uuu          | uu               |

| Brown-out Reset                    | 000h                  | 000x xuuu          | u0               |

| Interrupt Wake-up from SLEEP       | PC + 1 <sup>(1)</sup> | uuu1 0uuu          | uu               |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0'.

**Note 1:** When the wake-up is due to an interrupt and global enable bit, GIE is set and the PC is loaded with the interrupt vector (0004h) after execution of PC+1.

#### TABLE 10-6: INITIALIZATION CONDITION FOR REGISTERS

| Register | Address | Power-on Reset | <ul> <li>MCLR Reset during<br/>normal operation</li> <li>MCLR Reset during<br/>SLEEP</li> <li>WDT Reset</li> <li>Brown-out Reset <sup>(1)</sup></li> </ul> | <ul> <li>Wake-up from SLEEP<br/>through interrupt</li> <li>Wake-up from SLEEP<br/>through WDT time-out</li> </ul> |

|----------|---------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| W        | -       | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| INDF     | 00h     | -              | -                                                                                                                                                          | -                                                                                                                 |

| TMR0     | 01h     | XXXX XXXX      | uuuu uuuu                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PCL      | 02h     | 0000 0000      | 0000 0000                                                                                                                                                  | PC + 1 <sup>(3)</sup>                                                                                             |

| STATUS   | 03h     | 0001 1xxx      | 000q quuu <sup>(4)</sup>                                                                                                                                   | uuuq quuu <sup>(4)</sup>                                                                                          |

| FSR      | 04h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| PORTA    | 05h     | x xxxx         | u uuuu                                                                                                                                                     | u uuuu                                                                                                            |

| PORTB    | 06h     | xxxx xxxx      | uuuu uuuu                                                                                                                                                  | นนนน นนนน                                                                                                         |

| CMCON    | 1Fh     | 00 0000        | 00 0000                                                                                                                                                    | uu uuuu                                                                                                           |

| PCLATH   | 0Ah     | 0 0000         | 0 0000                                                                                                                                                     | u uuuu                                                                                                            |

| INTCON   | 0Bh     | x000 0000      | 0000 000u                                                                                                                                                  | uuuu uqqq <sup>(2)</sup>                                                                                          |

| PIR1     | 0Ch     | -0             | -0                                                                                                                                                         | -q (2,5)                                                                                                          |

| OPTION   | 81h     | 1111 1111      | 1111 1111                                                                                                                                                  | นนนน นนนน                                                                                                         |

| TRISA    | 85h     | 1 1111         | 1 1111                                                                                                                                                     | u uuuu                                                                                                            |

| TRISB    | 86h     | 1111 1111      | 1111 1111                                                                                                                                                  | uuuu uuuu                                                                                                         |

| PIE1     | 8Ch     | -0             | -0                                                                                                                                                         | -u                                                                                                                |

| PCON     | 8Eh     | 0x             | uq <sup>(1,6)</sup>                                                                                                                                        | uu                                                                                                                |

| EEINTF   | 90h     | 111            | 111                                                                                                                                                        | 111                                                                                                               |

| VRCON    | 9Fh     | 000- 0000      | 000- 0000                                                                                                                                                  | uuu- uuuu                                                                                                         |

Legend: u = unchanged, x = unknown, - = unimplemented bit, reads as '0', q = value depends on condition.

Note 1: If VDD goes too low, Power-on Reset will be activated and registers will be affected differently.

2: One or more bits in INTCON, PIR1 and/or PIR2 will be affected (to cause wake-up).

3: When the wake-up is due to an interrupt and the GIE bit is set, the PC is loaded with the interrupt vector (0004h).

4: See Table 10-5 for reset value for specific condition.

5: If wake-up was due to comparator input changing , then bit 6 = 1. All other interrupts generating a wake-up will cause bit 6 = u.

6: If reset was due to brown-out, then PCON bit 0 = 0. All other resets will cause bit 0 = u.

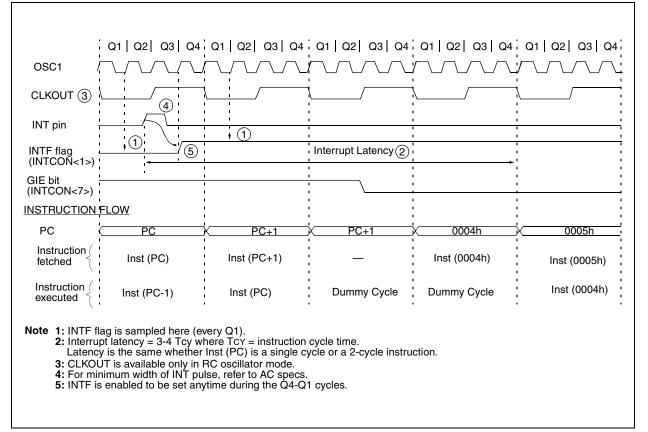

#### 10.5.1 RB0/INT INTERRUPT

External interrupt on RB0/INT pin is edge triggered; either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before re-enabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 10.8 for details on SLEEP and Figure 10-19 for timing of wake-up from SLEEP through RB0/INT interrupt.

#### 10.5.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can be enabled/disabled by setting/clearing T0IE (INTCON<5>) bit. For operation of the Timer0 module, see Section 7.0.

#### 10.5.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

Note: If a change on the I/O pin should occur when the read operation is being executed (start of the Q2 cycle), then the RBIF interrupt flag may not get set.

#### 10.5.4 COMPARATOR INTERRUPT

See Section 8.6 for complete description of comparator interrupts.

#### FIGURE 10-16: INT PIN INTERRUPT TIMING

| SWAPF            | Swap Nibbles in f                                                                                                                                                       | XORLW                          | Exclusive OR Literal with W                                                               |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] SWAPF f,d                                                                                                                                                       | Syntax:                        | [ <i>label</i> ] XORLW k                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                       | Operands:                      | 0 ≤ k ≤ 255                                                                               |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>),$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                               | Operation:<br>Status Affected: | (W) .XOR. $k \rightarrow (W)$                                                             |  |  |  |

| Status Affected: | None                                                                                                                                                                    | Encoding:                      | 11 1010 kkkk kkkk                                                                         |  |  |  |

| Encoding:        | 00 1110 dfff ffff                                                                                                                                                       | Description:                   | The contents of the W register are                                                        |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is 0,<br>the result is placed in W register. If 'd'<br>is 1, the result is placed in register 'f'. | Words:                         | XOR'ed with the eight bit literal 'k'.<br>The result is placed in the<br>W register.<br>1 |  |  |  |

| Words:           | 1                                                                                                                                                                       | Cycles:                        | 1                                                                                         |  |  |  |

| Cycles:          | 1                                                                                                                                                                       | Example:                       | XORLW 0xAF                                                                                |  |  |  |

| Example          | SWAPF REG, 0                                                                                                                                                            |                                | Before Instruction                                                                        |  |  |  |

| ·                | Before Instruction                                                                                                                                                      |                                | W = 0xB5                                                                                  |  |  |  |

|                  | REG1 = 0xA5                                                                                                                                                             |                                | After Instruction                                                                         |  |  |  |

|                  | After Instruction                                                                                                                                                       |                                | W = 0x1A                                                                                  |  |  |  |

|                  | $\begin{array}{rcl} REG1 &=& 0xA5\\ W &=& 0x5A \end{array}$                                                                                                             |                                |                                                                                           |  |  |  |

| TRIS                              | Load TR                                                                  | Load TRIS Register                    |                                        |              |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------|---------------------------------------|----------------------------------------|--------------|--|--|--|

| Syntax:                           | [ label ]                                                                | TRIS                                  | f                                      |              |  |  |  |

| Operands:                         | $5 \leq f \leq 7$                                                        |                                       |                                        |              |  |  |  |

| Operation:                        | $(W) \rightarrow TF$                                                     | RIS regis                             | ster f;                                |              |  |  |  |

| Status Affected:                  | None                                                                     |                                       |                                        |              |  |  |  |

| Encoding:                         | 0 0                                                                      | 0000                                  | 0110                                   | Offf         |  |  |  |

| Description:<br>Words:<br>Cycles: | The instru-<br>compatibil<br>products.<br>readable a<br>directly ad<br>1 | ity with th<br>Since TR<br>and writab | e PIC16C<br>IS register<br>le, the use | 5X<br>rs are |  |  |  |

| Example                           |                                                                          |                                       |                                        |              |  |  |  |

|                                   |                                                                          | -                                     | rd compa                               | -            |  |  |  |

|                                   | with future PIC <sup>®</sup> MCU products, do not use this instruction.  |                                       |                                        |              |  |  |  |

|                                   |                                                                          |                                       |                                        |              |  |  |  |

|                                   |                                                                          |                                       |                                        |              |  |  |  |

| XORWF            | Exclusive OR W with f                                                                                                                                                                     |                          |        |              |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------|--------------|--|--|--|--|--|

| Syntax:          | [label] XORWF f,d                                                                                                                                                                         |                          |        |              |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                           |                          |        |              |  |  |  |  |  |

| Operation:       | (W) .XOF                                                                                                                                                                                  | R. (f) $\rightarrow$ (6) | dest)  |              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                         |                          |        |              |  |  |  |  |  |

| Encoding:        | 0 0                                                                                                                                                                                       | 0110                     | dfff   | f fff        |  |  |  |  |  |

| Description:     | Exclusive OR the contents of the<br>W register with register 'f'. If 'd' is 0,<br>the result is stored in the W register. If<br>'d' is 1, the result is stored back in reg-<br>ister 'f'. |                          |        |              |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                         |                          |        |              |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                         |                          |        |              |  |  |  |  |  |

| Example          | XORWF                                                                                                                                                                                     | REG                      | 1      |              |  |  |  |  |  |

|                  | Before In                                                                                                                                                                                 | struction                |        |              |  |  |  |  |  |

|                  |                                                                                                                                                                                           | REG<br>W                 | =<br>= | 0xAF<br>0xB5 |  |  |  |  |  |

|                  | After Inst                                                                                                                                                                                | ruction                  |        |              |  |  |  |  |  |

|                  |                                                                                                                                                                                           | REG<br>W                 | =<br>= | 0x1A<br>0xB5 |  |  |  |  |  |

stand-alone mode the PRO MATE II can read, verify or program PIC devices. It can also set code-protect bits in this mode.

#### 12.11 <u>PICSTART Plus Entry Level</u> <u>Development System</u>

The PICSTART programmer is an easy-to-use, lowcost prototype programmer. It connects to the PC via one of the COM (RS-232) ports. MPLAB Integrated Development Environment software makes using the programmer simple and efficient.

PICSTART Plus supports all PIC devices with up to 40 pins. Larger pin count devices such as the PIC16C92X, and PIC17C76X may be supported with an adapter socket. PICSTART Plus is CE compliant.

#### 12.12 <u>SIMICE Entry-Level</u> <u>Hardware Simulator</u>

SIMICE is an entry-level hardware development system designed to operate in a PC-based environment with Microchip's simulator MPLAB-SIM. Both SIMICE and MPLAB-SIM run under Microchip Technology's MPLAB Integrated Development Environment (IDE) software. Specifically, SIMICE provides hardware simulation for Microchip's PIC12C5XX, PIC12CE5XX, and PIC16C5X families of PIC 8-bit microcontrollers. SIM-ICE works in conjunction with MPLAB-SIM to provide non-real-time I/O port emulation. SIMICE enables a developer to run simulator code for driving the target system. In addition, the target system can provide input to the simulator code. This capability allows for simple and interactive debugging without having to manually generate MPLAB-SIM stimulus files. SIMICE is a valuable debugging tool for entry-level system development.

#### 12.13 <u>PICDEM-1 Low-Cost PIC MCU</u> <u>Demonstration Board</u>

The PICDEM-1 is a simple board which demonstrates the capabilities of several of Microchip's microcontrollers. The microcontrollers supported are: PIC16C5X (PIC16C54 to PIC16C58A), PIC16C61, PIC16C62X, PIC16C71, PIC16C8X, PIC17C42, PIC17C43 and PIC17C44. All necessary hardware and software is included to run basic demo programs. The users can program the sample microcontrollers provided with the PICDEM-1 board, on a PRO MATE II or PICSTART-Plus programmer, and easily test firmware. The user can also connect the PICDEM-1 board to the MPLAB-ICE emulator and download the firmware to the emulator for testing. Additional prototype area is available for the user to build some additional hardware and connect it to the microcontroller socket(s). Some of the features include an RS-232 interface, a potentiometer for simulated analog input, push-button switches and eight LEDs connected to PORTB.

#### 12.14 <u>PICDEM-2 Low-Cost PIC16CXX</u> <u>Demonstration Board</u>

The PICDEM-2 is a simple demonstration board that supports the PIC16C62, PIC16C64, PIC16C65, PIC16C73 and PIC16C74 microcontrollers. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-2 board, on a PRO MATE II programmer or PICSTART-Plus, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-2 board to test firmware. Additional prototype area has been provided to the user for adding additional hardware and connecting it to the microcontroller socket(s). Some of the features include a RS-232 interface, push-button switches, a potentiometer for simulated analog input, a Serial EEPROM to demonstrate usage of the I<sup>2</sup>C bus and separate headers for connection to an LCD module and a keypad.

#### 12.15 <u>PICDEM-3 Low-Cost PIC16CXXX</u> <u>Demonstration Board</u>

The PICDEM-3 is a simple demonstration board that supports the PIC16C923 and PIC16C924 in the PLCC package. It will also support future 44-pin PLCC microcontrollers with a LCD Module. All the necessary hardware and software is included to run the basic demonstration programs. The user can program the sample microcontrollers provided with the PICDEM-3 board, on a PRO MATE II programmer or PICSTART Plus with an adapter socket, and easily test firmware. The MPLAB-ICE emulator may also be used with the PICDEM-3 board to test firmware. Additional prototype area has been provided to the user for adding hardware and connecting it to the microcontroller socket(s). Some of the features include an RS-232 interface, push-button switches, a potentiometer for simulated analog input, a thermistor and separate headers for connection to an external LCD module and a keypad. Also provided on the PICDEM-3 board is an LCD panel, with 4 commons and 12 segments, that is capable of displaying time, temperature and day of the week. The PICDEM-3 provides an additional RS-232 interface and Windows 3.1 software for showing the demultiplexed LCD signals on a PC. A simple serial interface allows the user to construct a hardware demultiplexer for the LCD signals.

### 12.16 PICDEM-17

The PICDEM-17 is an evaluation board that demonstrates the capabilities of several Microchip microcontrollers, including PIC17C752, PIC17C756, PIC17C762, and PIC17C766. All necessary hardware is included to run basic demo programs, which are supplied on a 3.5-inch disk. A programmed sample is included, and the user may erase it and program it with the other sample programs using the PRO MATE II or PICSTART Plus device programmers and easily debug

# **13.0 ELECTRICAL SPECIFICATIONS**

#### Absolute Maximum Ratings †

| Ambient Temperature under bias                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 40° to +125°C                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 65° to +150°C                                      |

| Voltage on any pin with respect to Vss (except VDD and MCLR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                    |

| Voltage on VDD with respect to VSS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 to +7.0V                                         |

| Voltage on RA4 with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.5V                                               |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0 to +14V                                          |

| Voltage on RA4 with respect to Vss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |

| Total power Dissipation (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0W                                               |

| Maximum Current out of Vss pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |

| Maximum Current into VDD pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 250 mA                                             |

| Input Clamp Current, Iк (Vi <0 or Vi> VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ±20 mA                                             |

| Output Clamp Current, IOK (Vo <0 or Vo>VDD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ±20 mA                                             |

| Maximum Output Current sunk by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25 mA                                              |

| Maximum Output Current sourced by any I/O pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 mA                                              |

| Maximum Current sunk by PORTA and PORTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 200 mA                                             |

| Maximum Current sourced by PORTA and PORTB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 200 mA                                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - $\sum$ IOH} + $\sum$ {(VDD-VOH) = 2000 x {IDD - } \sum | $x \text{ IOH} + \sum (\text{VOI } x \text{ IOL})$ |

2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100<sup>3</sup>/<sub>4</sub> should be used when applying a "low" level to the MCLR pin rather than pulling this pin directly to Vss.

**† NOTICE**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

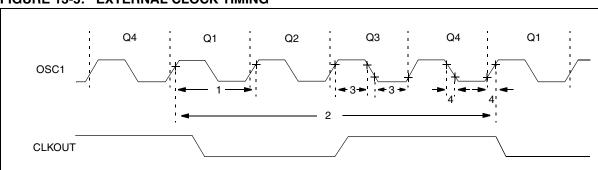

#### 13.5 Timing Diagrams and Specifications

## FIGURE 13-5: EXTERNAL CLOCK TIMING

### TABLE 13-3: EXTERNAL CLOCK TIMING REQUIREMENTS

| Parameter<br>No. | Sym   | Characteristic                   | Min  | Тур† | Max    | Units | Conditions                         |

|------------------|-------|----------------------------------|------|------|--------|-------|------------------------------------|

| 1A               | Fosc  | External CLKIN Frequency         | DC   | _    | 4      | MHz   | XT and RC osc mode, VDD=5.0V       |

|                  |       | (Note 1)                         | DC   | —    | 20     | MHz   | HS osc mode                        |

|                  |       |                                  | DC   | —    | 200    | kHz   | LP osc mode                        |

|                  |       | Oscillator Frequency             | DC   | —    | 4      | MHz   | RC osc mode, VDD=5.0V              |

|                  |       | (Note 1)                         | 0.1  | —    | 4      | MHz   | XT osc mode                        |

|                  |       |                                  | 1    | —    | 20     | MHz   | HS osc mode                        |

|                  |       |                                  | DC   | -    | 200    | kHz   | LP osc mode                        |

| 1                | Tosc  | External CLKIN Period            | 250  | —    | _      | ns    | XT and RC osc mode                 |

|                  |       | (Note 1)                         | 50   | —    | —      | ns    | HS osc mode                        |

|                  |       |                                  | 5    | —    | —      | μs    | LP osc mode                        |

|                  |       | Oscillator Period                | 250  | —    | _      | ns    | RC osc mode                        |

|                  |       | (Note 1)                         | 250  | —    | 10,000 | ns    | XT osc mode                        |

|                  |       |                                  | 50   | —    | 1,000  | ns    | HS osc mode                        |

|                  |       |                                  | 5    | —    | —      | μS    | LP osc mode                        |

| 2                | Тсү   | Instruction Cycle Time (Note 1)  | 200  | —    | DC     | ns    | Tcy=Fosc/4                         |

| 3*               | TosL, | External Clock in (OSC1) High or | 100* | —    | —      | ns    | XT oscillator, Tosc L/H duty cycle |

|                  | TosH  | Low Time                         | 2*   | —    | —      | μs    | LP oscillator, Tosc L/H duty cycle |

|                  |       |                                  | 20*  |      | —      | ns    | HS oscillator, Tosc L/H duty cycle |

| 4*               | TosR, | External Clock in (OSC1) Rise or | 25*  | —    | —      | ns    | XT oscillator                      |

|                  | TosF  | Fall Time                        | 50*  | —    | —      | ns    | LP oscillator                      |

|                  |       |                                  | 15*  | —    | —      | ns    | HS oscillator                      |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1 pin. When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

NOTES:

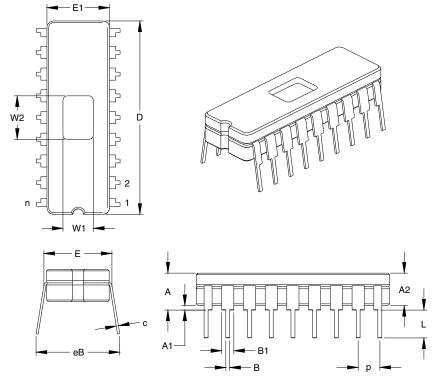

# 14.0 PACKAGING INFORMATION

# 18-Lead Ceramic Dual In-line with Window (JW) – 300 mil (CERDIP)

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging

|                            | Units INCHES* |      |      |      | MILLIMETERS |       |       |

|----------------------------|---------------|------|------|------|-------------|-------|-------|

| Dimensio                   | MIN           | NOM  | MAX  | MIN  | NOM         | MAX   |       |

| Number of Pins             | n             |      | 18   |      |             | 18    |       |

| Pitch                      | р             |      | .100 |      |             | 2.54  |       |

| Top to Seating Plane       | Α             | .170 | .183 | .195 | 4.32        | 4.64  | 4.95  |

| Ceramic Package Height     | A2            | .155 | .160 | .165 | 3.94        | 4.06  | 4.19  |

| Standoff                   | A1            | .015 | .023 | .030 | 0.38        | 0.57  | 0.76  |

| Shoulder to Shoulder Width | E             | .300 | .313 | .325 | 7.62        | 7.94  | 8.26  |

| Ceramic Pkg. Width         | E1            | .285 | .290 | .295 | 7.24        | 7.37  | 7.49  |

| Overall Length             | D             | .880 | .900 | .920 | 22.35       | 22.86 | 23.37 |

| Tip to Seating Plane       | L             | .125 | .138 | .150 | 3.18        | 3.49  | 3.81  |

| Lead Thickness             | С             | .008 | .010 | .012 | 0.20        | 0.25  | 0.30  |

| Upper Lead Width           | B1            | .050 | .055 | .060 | 1.27        | 1.40  | 1.52  |

| Lower Lead Width           | В             | .016 | .019 | .021 | 0.41        | 0.47  | 0.53  |

| Overall Row Spacing        | eB            | .345 | .385 | .425 | 8.76        | 9.78  | 10.80 |

| Window Width               | W1            | .130 | .140 | .150 | 3.30        | 3.56  | 3.81  |

| Window Length              | W2            | .190 | .200 | .210 | 4.83        | 5.08  | 5.33  |

\*Controlling Parameter JEDEC Equivalent: MO-036 Drawing No. C04-010

| Port RB Interrupt                    | 60 |

|--------------------------------------|----|

| PORTA                                |    |

| PORTB                                |    |

| Power Control/Status Register (PCON) | 55 |

| Power-Down Mode (SLEEP)              | 63 |

| Power-On Reset (POR)                 | 54 |

| Power-up Timer (PWRT)                | 54 |

| Prescaler                            |    |

| PRO MATE® II Universal Programmer    | 79 |

| Program Memory Organization          | 11 |

| •                                    |    |

### Q

# R

| 53 |

|----|

| 73 |

| 73 |

| 74 |

| 74 |

| 74 |

|    |

# S

| SEEVAL® Evaluation and Programming System             | 80 |

|-------------------------------------------------------|----|

| Serialized Quick-Turnaround-Production (SQTP) Devices | s5 |

| SLEEP Instruction                                     | 74 |

| Software Simulator (MPLAB-SIM)                        | 78 |

| Special Features of the CPU                           | 49 |

| Special Function Registers                            | 14 |

| Stack                                                 | 20 |

| Status Register                                       | 15 |

| SUBLW Instruction                                     | 75 |

| SUBWF Instruction                                     | 75 |

| SWAPF Instruction                                     | 76 |

#### **T** Timer0

| Timer0                             |

|------------------------------------|

| TIMER0                             |

| TIMER0 (TMR0) Interrupt35          |

| TIMER0 (TMR0) Module               |

| TMR0 with External Clock           |

| Timer1                             |

| Switching Prescaler Assignment     |

| Timing Diagrams and Specifications |

| TMR0 Interrupt                     |

| TRIS Instruction                   |

| TRISA23                            |

| TRISB                              |

| V                                  |

| Voltage Reference Module47         |

| VRCON Register                     |

| W                                  |

| Watchdog Timer (WDT)61             |

| WWW, On-Line Support2              |

| x                                  |

| XORLW Instruction                  |

| XORWF Instruction76                |

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

NOTES: